Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| 201010                     |                                                                             |

|----------------------------|-----------------------------------------------------------------------------|

| Product Status             | Active                                                                      |

| Core Processor             | PIC                                                                         |

| Core Size                  | 8-Bit                                                                       |

| Speed                      | 4MHz                                                                        |

| Connectivity               | -                                                                           |

| Peripherals                | Brown-out Detect/Reset, PWM, WDT                                            |

| Number of I/O              | 13                                                                          |

| Program Memory Size        | 3.5KB (2K x 14)                                                             |

| Program Memory Type        | OTP                                                                         |

| EEPROM Size                | -                                                                           |

| RAM Size                   | 128 × 8                                                                     |

| Voltage - Supply (Vcc/Vdd) | 2.5V ~ 5.5V                                                                 |

| Data Converters            | A/D 4x8b                                                                    |

| Oscillator Type            | External                                                                    |

| Operating Temperature      | 0°C ~ 70°C (TA)                                                             |

| Mounting Type              | Surface Mount                                                               |

| Package / Case             | 20-SSOP (0.209", 5.30mm Width)                                              |

| Supplier Device Package    | 20-SSOP                                                                     |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/pic16lc715t-04-ss |

|                            |                                                                             |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

# 3.0 ARCHITECTURAL OVERVIEW

The high performance of the PIC16CXX family can be attributed to a number of architectural features commonly found in RISC microprocessors. To begin with, the PIC16CXX uses a Harvard architecture, in which, program and data are accessed from separate memories using separate buses. This improves bandwidth over traditional von Neumann architecture in which program and data are fetched from the same memory using the same bus. Separating program and data buses further allows instructions to be sized differently than the 8-bit wide data word. Instruction opcodes are 14-bits wide making it possible to have all single word instructions. A 14-bit wide program memory access bus fetches a 14-bit instruction in a single cycle. A twostage pipeline overlaps fetch and execution of instructions (Example 3-1). Consequently, all instructions (35) execute in a single cycle (200 ns @ 20 MHz) except for program branches.

The table below lists program memory (EPROM) and data memory (RAM) for each PIC16C71X device.

| Device    | Program<br>Memory | Data Memory |

|-----------|-------------------|-------------|

| PIC16C710 | 512 x 14          | 36 x 8      |

| PIC16C71  | 1K x 14           | 36 x 8      |

| PIC16C711 | 1K x 14           | 68 x 8      |

| PIC16C715 | 2K x 14           | 128 x 8     |

The PIC16CXX can directly or indirectly address its register files or data memory. All special function registers, including the program counter, are mapped in the data memory. The PIC16CXX has an orthogonal (symmetrical) instruction set that makes it possible to carry out any operation on any register using any addressing mode. This symmetrical nature and lack of 'special optimal situations' make programming with the PIC16CXX simple yet efficient. In addition, the learning curve is reduced significantly.

PIC16CXX devices contain an 8-bit ALU and working register. The ALU is a general purpose arithmetic unit. It performs arithmetic and Boolean functions between the data in the working register and any register file.

The ALU is 8-bits wide and capable of addition, subtraction, shift and logical operations. Unless otherwise mentioned, arithmetic operations are two's complement in nature. In two-operand instructions, typically one operand is the working register (W register). The other operand is a file register or an immediate constant. In single operand instructions, the operand is either the W register or a file register.

The W register is an 8-bit working register used for ALU operations. It is not an addressable register.

Depending on the instruction executed, the ALU may affect the values of the Carry (C), Digit Carry (DC), and Zero (Z) bits in the STATUS register. The C and DC bits operate as a borrow bit and a digit borrow out bit, respectively, in subtraction. See the SUBLW and SUBWF instructions for examples.

| Pin Name        | DIP<br>Pin# | SSOP<br>Pin# <sup>(4)</sup> | SOIC<br>Pin# | l/O/P<br>Type | Buffer<br>Type                  | Description                                                                                                                                                                                              |

|-----------------|-------------|-----------------------------|--------------|---------------|---------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| OSC1/CLKIN      | 16          | 18                          | 16           | I             | ST/CMOS <sup>(3)</sup>          | Oscillator crystal input/external clock source input.                                                                                                                                                    |

| OSC2/CLKOUT     | 15          | 17                          | 15           | 0             | _                               | Oscillator crystal output. Connects to crystal or resonator in crystal oscillator mode. In RC mode, OSC2 pin outputs CLKOUT which has 1/4 the frequency of OSC1, and denotes the instruction cycle rate. |

| MCLR/Vpp        | 4           | 4                           | 4            | I/P           | ST                              | Master clear (reset) input or programming voltage input. This pin is an active low reset to the device.                                                                                                  |

|                 |             |                             |              |               |                                 | PORTA is a bi-directional I/O port.                                                                                                                                                                      |

| RA0/AN0         | 17          | 19                          | 17           | I/O           | TTL                             | RA0 can also be analog input0                                                                                                                                                                            |

| RA1/AN1         | 18          | 20                          | 18           | I/O           | TTL                             | RA1 can also be analog input1                                                                                                                                                                            |

| RA2/AN2         | 1           | 1                           | 1            | I/O           | TTL                             | RA2 can also be analog input2                                                                                                                                                                            |

| RA3/AN3/VREF    | 2           | 2                           | 2            | I/O           | TTL                             | RA3 can also be analog input3 or analog reference voltage                                                                                                                                                |

| RA4/T0CKI       | 3           | 3                           | 3            | I/O           | ST                              | RA4 can also be the clock input to the Timer0 module. Output is open drain type.                                                                                                                         |

|                 |             |                             |              |               |                                 | PORTB is a bi-directional I/O port. PORTB can be software pro-<br>grammed for internal weak pull-up on all inputs.                                                                                       |

| RB0/INT         | 6           | 7                           | 6            | I/O           | TTL/ST <sup>(1)</sup>           | RB0 can also be the external interrupt pin.                                                                                                                                                              |

| RB1             | 7           | 8                           | 7            | I/O           | TTL                             |                                                                                                                                                                                                          |

| RB2             | 8           | 9                           | 8            | I/O           | TTL                             |                                                                                                                                                                                                          |

| RB3             | 9           | 10                          | 9            | I/O           | TTL                             |                                                                                                                                                                                                          |

| RB4             | 10          | 11                          | 10           | I/O           | TTL                             | Interrupt on change pin.                                                                                                                                                                                 |

| RB5             | 11          | 12                          | 11           | I/O           | TTL                             | Interrupt on change pin.                                                                                                                                                                                 |

| RB6             | 12          | 13                          | 12           | I/O           | TTL/ST <sup>(2)</sup>           | Interrupt on change pin. Serial programming clock.                                                                                                                                                       |

| RB7             | 13          | 14                          | 13           | I/O           | TTL/ST <sup>(2)</sup>           | Interrupt on change pin. Serial programming data.                                                                                                                                                        |

| Vss             | 5           | 4, 6                        | 5            | Р             | —                               | Ground reference for logic and I/O pins.                                                                                                                                                                 |

| Vdd             | 14          | 15, 16                      | 14           | Р             | —                               | Positive supply for logic and I/O pins.                                                                                                                                                                  |

| Legend: I = inp |             | O = outp<br>— = Not         |              |               | /O = input/out<br>TTL = TTL inp | I I                                                                                                                                                                                                      |

Note 1: This buffer is a Schmitt Trigger input when configured as the external interrupt.

2: This buffer is a Schmitt Trigger input when used in serial programming mode.

3: This buffer is a Schmitt Trigger input when configured in RC oscillator mode and a CMOS input otherwise.

4: The PIC16C71 is not available in SSOP package.

#### 4.2.2.2 OPTION REGISTER

# Applicable Devices 710 71 711 715

The OPTION register is a readable and writable register which contains various control bits to configure the TMR0/WDT prescaler, the External INT Interrupt, TMR0, and the weak pull-ups on PORTB.

#### FIGURE 4-8: OPTION REGISTER (ADDRESS 81h, 181h)

| R/W-1    | R/W-1                    | R/W-1       | R/W-1       | R/W-1      | R/W-1        | R/W-1      | R/W-1 |                                                           |

|----------|--------------------------|-------------|-------------|------------|--------------|------------|-------|-----------------------------------------------------------|

| RBPU     | INTEDG                   | TOCS        | T0SE        | PSA        | PS2          | PS1        | PS0   | R = Readable bit                                          |

| bit7     | · · ·                    |             |             |            |              |            | bit0  | W = Writable bit<br>U = Unimplemented bit,<br>read as '0' |

|          |                          |             |             |            |              |            |       | - n = Value at POR reset                                  |

| bit 7:   | RBPU: PC                 | RTB Pull    | -up Enabl   | le bit     |              |            |       |                                                           |

|          | 1 = PORT                 |             |             |            |              |            |       |                                                           |

|          | 0 = PORTE                | 3 pull-ups  | s are enab  | led by ind | ividual port | latch valu | es    |                                                           |

| bit 6:   | INTEDG:                  | nterrupt E  | Edge Sele   | ct bit     |              |            |       |                                                           |

|          | 1 = Interru              | pt on risir | ng edge of  | f RB0/INT  | pin          |            |       |                                                           |

|          | 0 = Interru              | pt on falli | ng edge o   | f RB0/INT  | pin          |            |       |                                                           |

| bit 5:   | TOCS: TM                 | R0 Clock    | Source S    | elect bit  |              |            |       |                                                           |

|          | 1 = Transit              |             |             |            |              |            |       |                                                           |

|          | 0 = Interna              | al instruct | ion cycle ( | clock (CLk | (OUT)        |            |       |                                                           |

| bit 4:   | TOSE: TM                 |             |             |            |              |            |       |                                                           |

|          |                          |             |             |            | on RA4/T0    |            |       |                                                           |

|          | 0 = Increm               | ent on lo   | w-to-high   | transition | on RA4/T00   | JKI pin    |       |                                                           |

| bit 3:   | PSA: Pres                |             | 0           |            |              |            |       |                                                           |

|          | 1 = Presca<br>0 = Presca |             |             |            | modulo       |            |       |                                                           |

|          |                          |             | •           |            | module       |            |       |                                                           |

| bit 2-0: | PS2:PS0:                 | Prescale    | r Rate Sel  | lect bits  |              |            |       |                                                           |

|          | Bit Value                | TMR0 R      | ate WD      | Γ Rate     |              |            |       |                                                           |

|          | 000                      | 1:2         | 1:          |            |              |            |       |                                                           |

|          | 001                      | 1:4         | 1:          |            |              |            |       |                                                           |

|          | 010<br>011               | 1:8         | 1:          |            |              |            |       |                                                           |

|          | 100                      | 1:16        |             | 16         |              |            |       |                                                           |

|          | 101                      | 1:64        | . 1:        | 32         |              |            |       |                                                           |

|          | 110                      | 1 : 12      |             | 64         |              |            |       |                                                           |

|          | 111                      | 1:25        | 6   1       | 128        |              |            |       |                                                           |

|          |                          |             |             |            |              |            |       |                                                           |

|          |                          |             |             |            |              |            |       |                                                           |

Note: To achieve a 1:1 prescaler assignment for the TMR0 register, assign the prescaler to the Watchdog Timer by setting bit PSA (OPTION<3>).

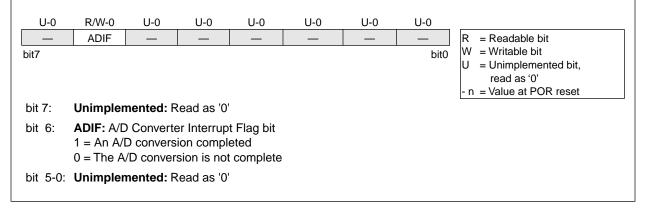

#### 4.2.2.5 PIR1 REGISTER

#### Applicable Devices 710 71 711 715

This register contains the individual flag bits for the Peripheral interrupts.

# **Note:** Interrupt flag bits get set when an interrupt condition occurs regardless of the state of its corresponding enable bit or the global enable bit, GIE (INTCON<7>). User software should ensure the appropriate interrupt flag bits are clear prior to enabling an interrupt.

#### FIGURE 4-11: PIR1 REGISTER (ADDRESS 0Ch)

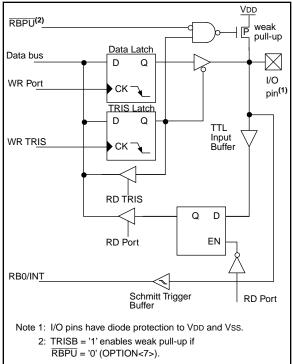

#### 5.2 PORTB and TRISB Registers

PORTB is an 8-bit wide bi-directional port. The corresponding data direction register is TRISB. Setting a bit in the TRISB register puts the corresponding output driver in a hi-impedance input mode. Clearing a bit in the TRISB register puts the contents of the output latch on the selected pin(s).

#### EXAMPLE 5-2: INITIALIZING PORTB

| BCF   | STATUS, RPC | ; |                       |

|-------|-------------|---|-----------------------|

| CLRF  | PORTB       | ; | Initialize PORTB by   |

|       |             | ; | clearing output       |

|       |             | ; | data latches          |

| BSF   | STATUS, RPC | ; | Select Bank 1         |

| MOVLW | 0xCF        | ; | Value used to         |

|       |             | ; | initialize data       |

|       |             | ; | direction             |

| MOVWF | TRISB       | ; | Set RB<3:0> as inputs |

|       |             | ; | RB<5:4> as outputs    |

|       |             | ; | RB<7:6> as inputs     |

Each of the PORTB pins has a weak internal pull-up. A single control bit can turn on all the pull-ups. This is performed by clearing bit  $\overline{\text{RBPU}}$  (OPTION<7>). The weak pull-up is automatically turned off when the port pin is configured as an output. The pull-ups are disabled on a Power-on Reset.

#### FIGURE 5-3: BLOCK DIAGRAM OF RB3:RB0 PINS

Four of PORTB's pins, RB7:RB4, have an interrupt on change feature. Only pins configured as inputs can cause this interrupt to occur (i.e. any RB7:RB4 pin configured as an output is excluded from the interrupt on change comparison). The input pins (of RB7:RB4) are compared with the old value latched on the last read of PORTB. The "mismatch" outputs of RB7:RB4 are OR'ed together to generate the RB Port Change Interrupt with flag bit RBIF (INTCON<0>).

This interrupt can wake the device from SLEEP. The user, in the interrupt service routine, can clear the interrupt in the following manner:

- a) Any read or write of PORTB. This will end the mismatch condition.

- b) Clear flag bit RBIF.

A mismatch condition will continue to set flag bit RBIF. Reading PORTB will end the mismatch condition, and allow flag bit RBIF to be cleared.

This interrupt on mismatch feature, together with software configurable pull-ups on these four pins allow easy interface to a keypad and make it possible for wake-up on key-depression. Refer to the Embedded Control Handbook, *"Implementing Wake-Up on Key Stroke"* (AN552).

| Note: | For the PIC16C71                                 |

|-------|--------------------------------------------------|

|       | if a change on the I/O pin should occur          |

|       | when the read operation is being executed        |

|       | (start of the Q2 cycle), then interrupt flag bit |

|       | RBIF may not get set.                            |

The interrupt on change feature is recommended for wake-up on key depression operation and operations where PORTB is only used for the interrupt on change feature. Polling of PORTB is not recommended while using the interrupt on change feature.

#### FIGURE 8-2: CONFIGURATION WORD, PIC16C710/711

| CP0 C                      | P0 CI                                      | P0 CP0                                                                           | CP0                                   | CP0     | CP0     | BODEN | CP0     | CP0      | PWRTE    | WDTE   | FOSC1 | FOSC0 | Register:      | CONFIG |

|----------------------------|--------------------------------------------|----------------------------------------------------------------------------------|---------------------------------------|---------|---------|-------|---------|----------|----------|--------|-------|-------|----------------|--------|

| bit13                      |                                            | 1                                                                                |                                       |         |         |       |         |          |          |        |       | bit0  | Address        | 2007h  |

| bit 13-7<br>5-4:<br>bit 6: | 1 = Co<br>0 = All<br><b>BODE</b><br>1 = BC | Code prote<br>ode protec<br>memory<br><b>N:</b> Brown<br>OR enable<br>OR disable | ction off<br>is code<br>-out Re<br>ed | protec  |         |       | Fh is w | vritable |          |        |       |       |                |        |

| bit 3:                     | 1 = PV                                     | <b>Ē:</b> Power<br>VRT disal<br>VRT enat                                         | bled                                  | er Ena  | ble bit | (1)   |         |          |          |        |       |       |                |        |

| bit 2:                     | 1 = W                                      | : Watchd<br>DT enable<br>DT disabl                                               | ed                                    | er Enab | le bit  |       |         |          |          |        |       |       |                |        |

| bit 1-0:                   | 11 = F<br>10 = F<br>01 = X                 | 1:FOSC0<br>RC oscilla<br>IS oscillat<br>(T oscillat<br>P oscillat                | tor<br>tor<br>tor                     | ator Se | lection | bits  |         |          |          |        |       |       |                |        |

| Note 1:                    | Ensur                                      | e the Pow                                                                        | er-up T                               | imer is | enable  |       | ne Brov | vn-out l | Reset is | enable | d.    |       | value of bit F | PWRTE. |

#### 2: All of the CP0 bits have to be given the same value to enable the code protection scheme listed.

#### FIGURE 8-3: CONFIGURATION WORD, PIC16C715

| CP1                                                                                                                                                                                                                                         | CP0                                                                                                                               | CP1                                                                                     | CP0                           | CP1                 | CP0       | MPEEN     | BODEN                  | CP1    | CP0   | PWRTE     | WDTE     | FOSC1    | FOSC0      | Register:    | CONFIG |

|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------|-------------------------------|---------------------|-----------|-----------|------------------------|--------|-------|-----------|----------|----------|------------|--------------|--------|

| bit13                                                                                                                                                                                                                                       |                                                                                                                                   |                                                                                         |                               |                     |           |           |                        |        |       |           |          |          | bit0       | Address      | 2007h  |

| bit 13-8 <b>CP1:CP0:</b> Code Protection bits <sup>(2)</sup><br>5-4: 11 = Code protection off<br>10 = Upper half of program memory code protected<br>01 = Upper 3/4th of program memory code protected<br>00 = All memory is code protected |                                                                                                                                   |                                                                                         |                               |                     |           |           |                        |        |       |           |          |          |            |              |        |

| bit 7:                                                                                                                                                                                                                                      | it 7: <b>MPEEN:</b> Memory Parity Error Enable<br>1 = Memory Parity Checking is enabled<br>0 = Memory Parity Checking is disabled |                                                                                         |                               |                     |           |           |                        |        |       |           |          |          |            |              |        |

| bit 6:                                                                                                                                                                                                                                      | 1                                                                                                                                 | BODEN: Brown-out Reset Enable bit <sup>(1)</sup><br>1 = BOR enabled<br>0 = BOR disabled |                               |                     |           |           |                        |        |       |           |          |          |            |              |        |

| bit 3:                                                                                                                                                                                                                                      | 1                                                                                                                                 | <b>WRTE</b> :<br>= PWF<br>= PWF                                                         | RT disa                       | bled                | mer Ei    | nable bit | (1)                    |        |       |           |          |          |            |              |        |

| bit 2:                                                                                                                                                                                                                                      | 1                                                                                                                                 | <b>DTE:</b> \<br>= WDT<br>= WDT                                                         | enabl                         | ed                  | ner En    | able bit  |                        |        |       |           |          |          |            |              |        |

| bit 1-0                                                                                                                                                                                                                                     | 11<br>10<br>01                                                                                                                    | DSC1:<br>L = RC<br>D = HS<br>L = XT<br>D = LP                                           | oscilla<br>oscilla<br>oscilla | ator<br>itor<br>tor | llator \$ | Selectior | n bits                 |        |       |           |          |          |            |              |        |

| Note 7                                                                                                                                                                                                                                      |                                                                                                                                   |                                                                                         |                               |                     |           |           | cally ena<br>ed anytir |        | •     |           | ,        | 0        | ess of the | value of bit | PWRTE. |

|                                                                                                                                                                                                                                             | 2: Al                                                                                                                             | l of the                                                                                | CP1:0                         | CP0 pa              | airs ha   | ve to be  | given the              | e same | value | to enable | e the co | de prote | ection sch | eme listed.  |        |

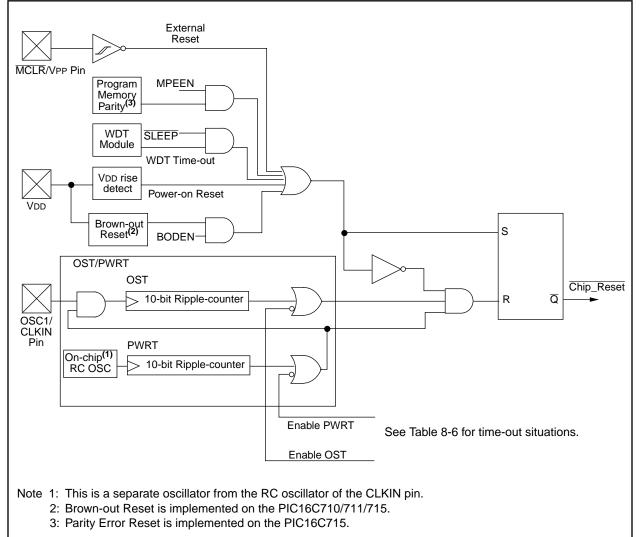

#### 8.3 <u>Reset</u>

# Applicable Devices 710 71 711 715

The PIC16CXX differentiates between various kinds of reset:

- Power-on Reset (POR)

- MCLR reset during normal operation

- MCLR reset during SLEEP

- WDT Reset (normal operation)

- Brown-out Reset (BOR) (PIC16C710/711/715)

- Parity Error Reset (PIC16C715)

Some registers are not affected in any reset condition; their status is unknown on POR and unchanged in any other reset. Most other registers are reset to a "reset state" on Power-on Reset (POR), on the  $\overline{\text{MCLR}}$  and

WDT Reset, on MCLR reset during SLEEP, and Brownout Reset (BOR). They are not affected by a WDT Wake-up, which is viewed as the resumption of normal operation. The TO and PD bits are set or cleared differently in different reset situations as indicated in Table 8-7, Table 8-8 and Table 8-9. These bits are used in software to determine the nature of the reset. See Table 8-10 and Table 8-11 for a full description of reset states of all registers.

A simplified block diagram of the on-chip reset circuit is shown in Figure 8-9.

The PIC16C710/711/715 have a  $\overline{\text{MCLR}}$  noise filter in the  $\overline{\text{MCLR}}$  reset path. The filter will detect and ignore small pulses.

It should be noted that a WDT Reset does not drive  $\overline{\text{MCLR}}$  pin low.

#### FIGURE 8-9: SIMPLIFIED BLOCK DIAGRAM OF ON-CHIP RESET CIRCUIT

| BTFSS             | Bit Test f                 | f, Skip if S                                            | Set                       |         | CALL              | Call Sub                              | oroutine                             |                                                          |                                             |  |  |

|-------------------|----------------------------|---------------------------------------------------------|---------------------------|---------|-------------------|---------------------------------------|--------------------------------------|----------------------------------------------------------|---------------------------------------------|--|--|

| Syntax:           | [ <i>label</i> ] B1        | FSS f,b                                                 |                           |         | Syntax:           | [ label ]                             | CALL                                 | <                                                        |                                             |  |  |

| Operands:         | $0 \le f \le 12$           |                                                         |                           |         | Operands:         | $0 \le k \le 2$                       | $0 \le k \le 2047$                   |                                                          |                                             |  |  |

|                   | 0 ≤ b < 7                  |                                                         |                           |         | Operation:        | (PC)+ 1-                              | → TOS,                               |                                                          |                                             |  |  |

| Operation:        | skip if (f<                | :b>) = 1                                                |                           |         |                   | $k \rightarrow PC <$                  |                                      | 50.40                                                    |                                             |  |  |

| Status Affected:  | None                       | i                                                       |                           |         |                   | ,                                     | 1<4:3>) -                            | $\rightarrow$ PC<12                                      | :11>                                        |  |  |

| Encoding:         | 01                         | 11bb                                                    | bfff                      | ffff    | Status Affected:  | None                                  |                                      |                                                          |                                             |  |  |

| Description:      |                            | register 'f' is                                         |                           | ne next | Encoding:         | 10                                    | 0kkk                                 | kkkk                                                     | kkkk                                        |  |  |

|                   | If bit 'b' is<br>discarded | is execute<br>1', then the<br>and a NOF<br>aking this a | next instru<br>is execute | ed      | Description:      | (PC+1) is<br>eleven bit<br>into PC bi | pushed or<br>immediate<br>ts <10:0>. | st, return a<br>nto the state<br>address is<br>The upper | ck. The<br>s loaded<br><sup>·</sup> bits of |  |  |

| Words:            | 1                          |                                                         |                           |         |                   |                                       |                                      | rom PCLA<br>instruction                                  |                                             |  |  |

| Cycles:           | 1(2)                       |                                                         |                           |         | Words:            | 1                                     |                                      |                                                          |                                             |  |  |

| Q Cycle Activity: | Q1                         | Q2                                                      | Q3                        | Q4      | Cycles:           | 2                                     |                                      |                                                          |                                             |  |  |

|                   | Decode                     | Read<br>register 'f'                                    | Process<br>data           | NOP     | Q Cycle Activity: | Q1                                    | Q2                                   | Q3                                                       | Q4                                          |  |  |

| If Skip:          | (2nd Cyc                   | :le)                                                    |                           |         | 1st Cycle         | Decode                                | Read<br>literal 'k',                 | Process<br>data                                          | Write to<br>PC                              |  |  |

|                   | Q1                         | Q2                                                      | Q3                        | Q4      | 1                 |                                       | Push PC<br>to Stack                  |                                                          |                                             |  |  |

|                   | NOP                        | NOP                                                     | NOP                       | NOP     | 2nd Cycle         | NOP                                   | NOP                                  | NOP                                                      | NOP                                         |  |  |

| Example           | HERE<br>FALSE              |                                                         | FLAG,1<br>PROCESS_        | _CODE   | Example           | HERE                                  | CALL                                 | THERE                                                    |                                             |  |  |

|                   | TRUE                       | •                                                       |                           |         |                   | Before Ir                             |                                      |                                                          |                                             |  |  |

|                   |                            | •                                                       |                           |         |                   | After Ins                             |                                      | Address HE                                               | RE                                          |  |  |

|                   | Before In                  | struction                                               |                           |         |                   |                                       | -                                    | ddress TH                                                |                                             |  |  |

|                   |                            |                                                         | address H                 | IERE    |                   |                                       | TOS = A                              | Address HE                                               | RE+1                                        |  |  |

|                   | After Inst                 | ruction<br>if FLAG<1>                                   | - 0                       |         |                   |                                       |                                      |                                                          |                                             |  |  |

|                   |                            | -                                                       | > = 0,<br>address F≠      | ALSE    |                   |                                       |                                      |                                                          |                                             |  |  |

|                   |                            | if FLAG<1><br>PC =                                      | ,                         |         |                   |                                       |                                      |                                                          |                                             |  |  |

|                   |                            | FU = 1                                                  | address TF                | KUE     |                   |                                       |                                      |                                                          |                                             |  |  |

| NOP               | No Operation |       |      |      |  |  |  |  |  |

|-------------------|--------------|-------|------|------|--|--|--|--|--|

| Syntax:           | [ label ]    | NOP   |      |      |  |  |  |  |  |

| Operands:         | None         |       |      |      |  |  |  |  |  |

| Operation:        | No opera     | ition |      |      |  |  |  |  |  |

| Status Affected:  | None         |       |      |      |  |  |  |  |  |

| Encoding:         | 00           | 0000  | 0xx0 | 0000 |  |  |  |  |  |

| Description:      | No operat    | ion.  |      |      |  |  |  |  |  |

| Words:            | 1            |       |      |      |  |  |  |  |  |

| Cycles:           | 1            |       |      |      |  |  |  |  |  |

| Q Cycle Activity: | Q1           | Q2    | Q3   | Q4   |  |  |  |  |  |

|                   | Decode       | NOP   | NOP  | NOP  |  |  |  |  |  |

| Example           | NOP          |       |      |      |  |  |  |  |  |

| RETFIE            | Return from Interrupt                                              |                                       |                         |                     |  |  |  |  |

|-------------------|--------------------------------------------------------------------|---------------------------------------|-------------------------|---------------------|--|--|--|--|

| Syntax:           | [ label ]                                                          | RETFIE                                |                         |                     |  |  |  |  |

| Operands:         | None                                                               |                                       |                         |                     |  |  |  |  |

| Operation:        | $\begin{array}{l} TOS \to F \\ 1 \to GIE \end{array}$              | PC,                                   |                         |                     |  |  |  |  |

| Status Affected:  | None                                                               |                                       |                         |                     |  |  |  |  |

| Encoding:         | 00                                                                 | 0000                                  | 0000                    | 1001                |  |  |  |  |

| Monda             | and Top of<br>the PC. Int<br>ting Globa<br>(INTCON-<br>instruction | errupts a<br>I Interrupt<br>7>). This | re enabled<br>Enable bi | l by set-<br>t, GIE |  |  |  |  |

| Words:            | 1                                                                  |                                       |                         |                     |  |  |  |  |

| Cycles:           | 2                                                                  |                                       |                         |                     |  |  |  |  |

| Q Cycle Activity: | Q1                                                                 | Q2                                    | Q3                      | Q4                  |  |  |  |  |

| 1st Cycle         | Decode                                                             | NOP                                   | Set the<br>GIE bit      | Pop from the Stack  |  |  |  |  |

| 2nd Cycle         | NOP                                                                | NOP                                   | NOP                     | NOP                 |  |  |  |  |

| Example           | RETFIE                                                             |                                       |                         |                     |  |  |  |  |

Example

After Interrupt PC = TOS GIE = 1

| OPTION           | Load Opt                                                                                           | tion Reg                                       | gister                                               |                                         |

|------------------|----------------------------------------------------------------------------------------------------|------------------------------------------------|------------------------------------------------------|-----------------------------------------|

| Syntax:          | [ label ]                                                                                          | OPTION                                         | ١                                                    |                                         |

| Operands:        | None                                                                                               |                                                |                                                      |                                         |

| Operation:       | $(W)\toOF$                                                                                         | PTION                                          |                                                      |                                         |

| Status Affected: | None                                                                                               |                                                |                                                      |                                         |

| Encoding:        | 00                                                                                                 | 0000                                           | 0110                                                 | 0010                                    |

| Description:     | The conter<br>loaded in the<br>instruction<br>patibility with<br>Since OPT<br>register, the<br>it. | he OPTIC<br>is suppoi<br>ith PIC16<br>ION is a | DN registe<br>rted for co<br>C5X produ<br>readable/v | r. This<br>de com-<br>ucts.<br>vritable |

| Words:           | 1                                                                                                  |                                                |                                                      |                                         |

| Cycles:          | 1                                                                                                  |                                                |                                                      |                                         |

| Example          |                                                                                                    |                                                |                                                      |                                         |

|                  | To mainta<br>with futur<br>not use th                                                              | re PIC16                                       | CXX prod                                             |                                         |

|         |                                            | Standa                                               | rd Operat | ting  | Conditio | ons (un  | less otherwise stated)                                                  |  |  |  |

|---------|--------------------------------------------|------------------------------------------------------|-----------|-------|----------|----------|-------------------------------------------------------------------------|--|--|--|

|         |                                            | Operati                                              | ng temper | atur  |          | ,<br>≤ T | $A \leq +70^{\circ}C$ (commercial)                                      |  |  |  |

|         |                                            |                                                      | •         |       | -40°0    |          | A ≤ +85°C (industrial)                                                  |  |  |  |

| DC CHAP | RACTERISTICS                               | $-40^{\circ}C \leq TA \leq +125^{\circ}C$ (extended) |           |       |          |          |                                                                         |  |  |  |

|         |                                            | Operati<br>Section                                   |           | e Vde | range a  | s descr  | ibed in DC spec Section 11.1 and                                        |  |  |  |

| Param   | Characteristic                             | Sym                                                  | Min       | Тур   | Max      | Units    | Conditions                                                              |  |  |  |

| No.     |                                            | - C.J                                                |           | t     | max      | 0        |                                                                         |  |  |  |

|         | Output Low Voltage                         |                                                      |           | -     |          |          |                                                                         |  |  |  |

| D080    | I/O ports                                  | Vol                                                  | -         | -     | 0.6      | V        | IOL = 8.5 mA, VDD = 4.5V,<br>-40°C to +85°C                             |  |  |  |

| D080A   |                                            |                                                      | -         | -     | 0.6      | V        | IOL = 7.0 mA, VDD = 4.5V,<br>-40°C to +125°C                            |  |  |  |

| D083    | OSC2/CLKOUT (RC osc config)                |                                                      | -         | -     | 0.6      | V        | IOL = 1.6 mA, VDD = 4.5V,<br>-40°C to +85°C                             |  |  |  |

| D083A   |                                            |                                                      | -         | -     | 0.6      | V        | IOL = 1.2 mA, VDD = 4.5V,<br>-40°C to +125°C                            |  |  |  |

|         | Output High Voltage                        |                                                      |           |       |          |          |                                                                         |  |  |  |

| D090    | I/O ports (Note 3)                         | Vон                                                  | Vdd - 0.7 | -     | -        | V        | IOH = -3.0 mA, VDD = 4.5V,<br>-40°C to +85°C                            |  |  |  |

| D090A   |                                            |                                                      | Vdd - 0.7 | -     | -        | V        | ІОН = -2.5 mA, VDD = 4.5V,<br>-40°C to +125°C                           |  |  |  |

| D092    | OSC2/CLKOUT (RC osc config)                |                                                      | Vdd - 0.7 | -     | -        | V        | ІОН = -1.3 mA, VDD = 4.5V,<br>-40°С to +85°С                            |  |  |  |

| D092A   |                                            |                                                      | Vdd - 0.7 | -     | -        | V        | ІОН = -1.0 mA, VDD = 4.5V,<br>-40°C to +125°C                           |  |  |  |

| D130*   | Open-Drain High Voltage                    | Vod                                                  | -         | -     | 14       | V        | RA4 pin                                                                 |  |  |  |

|         | Capacitive Loading Specs on<br>Output Pins |                                                      |           |       |          |          |                                                                         |  |  |  |

| D100    | OSC2 pin                                   | Cosc2                                                | -         | -     | 15       | pF       | In XT, HS and LP modes when<br>external clock is used to drive<br>OSC1. |  |  |  |

| D101    | All I/O pins and OSC2 (in RC mode)         | Сю                                                   | -         | -     | 50       | pF       |                                                                         |  |  |  |

\* These parameters are characterized but not tested.

† Data in "Typ" column is at 5V, 25°C unless otherwise stated. These parameters are for design guidance only and are not tested.

Note 1: In RC oscillator configuration, the OSC1/CLKIN pin is a Schmitt Trigger input. It is not recommended that the PIC16C7X be driven with external clock in RC mode.

2: The leakage current on the MCLR pin is strongly dependent on the applied voltage level. The specified levels represent normal operating conditions. Higher leakage current may be measured at different input voltages.

3: Negative current is defined as current sourced by the pin.

# TABLE 11-6:A/D CONVERTER CHARACTERISTICS:<br/>PIC16C710/711-04 (COMMERCIAL, INDUSTRIAL, EXTENDED)<br/>PIC16C710/711-10 (COMMERCIAL, INDUSTRIAL, EXTENDED)<br/>PIC16LC710/711-04 (COMMERCIAL, INDUSTRIAL, EXTENDED)<br/>PIC16LC710/711-04 (COMMERCIAL, INDUSTRIAL, EXTENDED)

| Param<br>No. | Sym  | Characteristic                                 | Min       | Тур†       | Мах        | Units | Conditions                                                                                              |

|--------------|------|------------------------------------------------|-----------|------------|------------|-------|---------------------------------------------------------------------------------------------------------|

| A01          | NR   | Resolution                                     | —         | _          | 8-bits     | bit   | $VREF=VDD,VSS\leqAIN\leqVREF$                                                                           |

| A02          | EABS | Absolute error                                 | —         | —          | <±1        | LSb   | $VREF=VDD,VSS\leqAIN\leqVREF$                                                                           |

| A03          | EIL  | Integral linearity error                       | _         | _          | < ± 1      | LSb   | $VREF = VDD,  VSS \le AIN \le VREF$                                                                     |

| A04          | Edl  | Differential linearity error                   | _         | _          | < ± 1      | LSb   | $VREF = VDD,  VSS \le AIN \le VREF$                                                                     |

| A05          | Efs  | Full scale error                               | _         | _          | < ± 1      | LSb   | $VREF = VDD,  VSS \le AIN \le VREF$                                                                     |

| A06          | EOFF | Offset error                                   | _         | _          | <±1        | LSb   | $VREF = VDD,  VSS \le AIN \le VREF$                                                                     |

| A10          | —    | Monotonicity                                   | _         | guaranteed | -          | —     | $VSS \leq VAIN \leq VREF$                                                                               |

| A20          | Vref | Reference voltage                              | 2.5V      | _          | Vdd + 0.3  | V     |                                                                                                         |

| A25          | VAIN | Analog input voltage                           | Vss - 0.3 | —          | Vref + 0.3 | V     |                                                                                                         |

| A30          | ZAIN | Recommended impedance of analog voltage source | _         | _          | 10.0       | kΩ    |                                                                                                         |

| A40          | IAD  | A/D conversion current (VDD)                   | _         | 180        | _          | μA    | Average current consumption when A/D is on. (Note 1)                                                    |

| A50          | IREF | VREF input current (Note 2)                    | 10        | _          | 1000       | μA    | During VAIN acquisition.<br>Based on differential of VHOLD to VAIN.<br>To charge CHOLD see Section 7.1. |

|              |      |                                                | —         |            | 10         | μA    | During A/D Conversion cycle                                                                             |

These parameters are characterized but not tested.

\*

† Data in "Typ" column is at 5V, 25°C unless otherwise stated. These parameters are for design guidance only and are not tested.

Note 1: When A/D is off, it will not consume any current other than minor leakage current.

The power-down current spec includes any such leakage from the A/D module.

2: VREF current is from RA3 pin or VDD pin, whichever is selected as reference input.

# Applicable Devices 710 71 711 715

#### 13.2 DC Characteristics: PIC16LC715-04 (Commercial, Industrial)

| DC CHAF               | RACTERISTICS                                                        |               |      | ard Ope<br>ing tem |      | ire 0°                 | itions (unless otherwise stated) $C \leq TA \leq +70^{\circ}C$ (commercial) $0^{\circ}C \leq TA \leq +85^{\circ}C$ (industrial)                                                              |

|-----------------------|---------------------------------------------------------------------|---------------|------|--------------------|------|------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Param<br>No.          | Characteristic                                                      | Sym           | Min  | Тур†               | Max  | Units                  | Conditions                                                                                                                                                                                   |

| D001                  | Supply Voltage                                                      | Vdd           | 2.5  | -                  | 5.5  | V                      | LP, XT, RC osc configuration (DC - 4 MHz)                                                                                                                                                    |

| D002*                 | RAM Data Retention<br>Voltage (Note 1)                              | Vdr           | -    | 1.5                | -    | V                      | Device in SLEEP mode                                                                                                                                                                         |

| D003                  | VDD start voltage to<br>ensure internal<br>Power-on Reset<br>signal | VPOR          | -    | Vss                | -    | V                      | See section on Power-on Reset for details                                                                                                                                                    |

| D004*                 | VDD rise rate to<br>ensure internal<br>Power-on Reset<br>signal     | SVDD          | 0.05 | -                  | -    | V/ms                   | See section on Rower-on Reset for details                                                                                                                                                    |

| D005                  | Brown-out Reset<br>Voltage                                          | Bvdd          | 3.7  | 4.0                | 4.3  | V                      | BODEN configuration bit is enabled                                                                                                                                                           |

| D010                  | Supply Current<br>(Note 2)                                          | IDD           | -    | 2.0                | 3.8  | mA                     | XT, RC osc configuration<br>Fosc = 4 MHz, VDD = 3.0V (Note 4)                                                                                                                                |

| D010A                 |                                                                     |               | -    | 22.5               | 48   | βıΑ                    | LP osc configuration<br>Fosc = 32 kHz, VDD = $3.0V$ , WDT disabled                                                                                                                           |

| D015                  | Brown-out Reset<br>Current (Note 5)                                 | $\Delta$ IBOR | -    | 300*               | 500  | μΑ                     | BOR enabled VDD = 5.0V                                                                                                                                                                       |

| D020<br>D021<br>D021A | Power-down Current<br>(Note 3)                                      | IPD           |      | 7.5<br>0.9<br>0.9  | 30 5 | μ <b>Α</b><br>μΑ<br>μΑ | $VDD = 3.0V$ , WDT enabled, $-40^{\circ}C$ to $+85^{\circ}C$<br>$VDD = 3.0V$ , WDT disabled, $0^{\circ}C$ to $+70^{\circ}C$<br>$VDD = 3.0V$ , WDT disabled, $-40^{\circ}C$ to $+85^{\circ}C$ |

| D023                  | Brown-out Reset<br>Current (Note 5)                                 |               | -    | 300*               | 500  | μA                     | BOR enabled VDD = 5.0V                                                                                                                                                                       |

These parameters are characterized but pot tested.

+ Data in "Typ" column is at 5V, 25°C unless otherwise stated. These parameters are for design guidance only and are not tested.

Note 1: This is the limit to which VDD can be lowered in SLEEP mode without losing RAM data.

2: The supply current is mainly a function of the operating voltage and frequency. Other factors such as I/O pin loading and switching rate, escillator type, internal code execution pattern, and temperature also have an impact on the current consumption.

The test conditions for all IDD measurements in active operation mode are:

ØSC1 = external square wave, from rail to rail; all I/O pins tristated, pulled to VDD

$\overline{MCLR} = VDR; WDT$  enabled/disabled as specified.

3: The power-down current in SLEEP mode does not depend on the oscillator type. Power-down current is measured with the part in SLEEP mode, with all I/O pins in hi-impedance state and tied to VDD and Vss.

- 4: For RC osc configuration, current through Rext is not included. The current through the resistor can be estimated by the formula Ir = VDD/2Rext (mA) with Rext in kOhm.

- 5: The  $\Delta$  current is the additional current consumed when this peripheral is enabled. This current should be added to the base IDD or IPD measurement.

| Param<br>No. | Sym  | Characteristic                       |                    | Min       | Тур†       | Max       | Units    | Conditions                                                                                                                                   |

|--------------|------|--------------------------------------|--------------------|-----------|------------|-----------|----------|----------------------------------------------------------------------------------------------------------------------------------------------|

| A01          | NR   | Resolution                           |                    | _         |            | 8 bits    | bits     | $\label{eq:VREF} \begin{array}{l} VREF = VDD = 5.12V,\\ VSS \leq VAIN \leq VREF \end{array}$                                                 |

| A02          | EABS | Absolute error                       | PIC16 <b>C</b> 71  |           | _          | < ±1      | LSb      | $\begin{array}{l} VREF=VDD=5.12V,\\ VSS\leqVAIN\leqVREF \end{array}$                                                                         |

|              |      |                                      | PIC16 <b>LC</b> 71 | —         | —          | < ±2      | LSb      | VREF = VDD = 3.0V (Note 3)                                                                                                                   |

| A03          | EIL  | Integral linearity error             | PIC16 <b>C</b> 71  | _         | _          | < ±1      | LSb      | $\label{eq:VREF} \begin{array}{l} VREF = VDD = 5.12V,\\ VSS \leq VAIN \leq VREF \end{array}$                                                 |

|              |      |                                      | PIC16 <b>LC</b> 71 | —         | _          | < ±2      | LSb      | VREF = VDD = 3.0V (Note 3)                                                                                                                   |

| A04          | Edl  | Differential linearity error         | PIC16 <b>C</b> 71  |           | _          | < ±1      | LSb      | $\label{eq:VREF} \begin{array}{l} VREF = VDD = 5.12V,\\ VSS \leq VAIN \leq VREF \end{array}$                                                 |

|              |      |                                      | PIC16 <b>LC</b> 71 | —         | _          | < ±2      | LSb      | VREF = VDD = 3.0V (Note 3)                                                                                                                   |

| A05          | EFS  | Full scale error                     | PIC16 <b>C</b> 71  | —         | _          | < ±1      | LSb      | $\begin{array}{l} VREF=VDD=5.12V,\\ VSS\leqVAIN\leqVREF \end{array}$                                                                         |

|              |      |                                      | PIC16 <b>LC</b> 71 | —         | _          | < ±2      | LSb      | VREF = VDD = 3.0V (Note 3)                                                                                                                   |

| A06          | EOFF | Offset error                         | PIC16 <b>C</b> 71  | —         | _          | < ±1      | LSb      | $\begin{array}{l} VREF=VDD=5.12V,\\ VSS\leqVAIN\leqVREF \end{array}$                                                                         |

|              |      |                                      | PIC16 <b>LC</b> 71 | —         | _          | < ±2      | LSb      | VREF = VDD = 3.0V (Note 3)                                                                                                                   |

| A10          | —    | Monotonicity                         |                    | —         | guaranteed | —         | -        | $VSS \leq VAIN \leq VREF$                                                                                                                    |

| A20          | Vref | Reference voltage                    |                    | 3.0V      | —          | Vdd + 0.3 | V        |                                                                                                                                              |

| A25          | VAIN | Analog input voltage                 |                    | Vss - 0.3 | —          | Vref      | V        |                                                                                                                                              |

| A30          | Zain | Recommended impedance voltage source | of analog          | —         | —          | 10.0      | kΩ       |                                                                                                                                              |

| A40          | IAD  | A/D conversion current (VD           | D)                 | —         | 180        | _         | μA       | Average current consump-<br>tion when A/D is on. (Note 1)                                                                                    |

| A50          | IREF | VREF input current (Note 2)          | PIC16 <b>C</b> 71  | 10        | _          | 1000      | μΑ       | During VAIN acquisition.<br>Based on differential of<br>VHOLD to VAIN.<br>To charge CHOLD see<br>Section 7.1.<br>During A/D Conversion cycle |

|              |      |                                      | PIC16 <b>LC</b> 71 | _         | _          | 1         | mA<br>μA | During VAIN acquisition.<br>Based on differential of<br>VHOLD to VAIN.<br>To charge CHOLD see<br>Section 7.1.<br>During A/D Conversion cycle |

#### TABLE 15-6: A/D CONVERTER CHARACTERISTICS

These parameters are characterized but not tested.

† Data in "Typ" column is at 5V, 25°C unless otherwise stated. These parameters are for design guidance only and are not tested.

Note 1: When A/D is off, it will not consume any current other than minor leakage current. The power-down current spec includes any such leakage from the A/D module.

2: VREF current is from RA3 pin or VDD pin, whichever is selected as reference input.

3: These specifications apply if VREF = 3.0V and if VDD  $\ge$  3.0V. VAIN must be between VSS and VREF.

\*

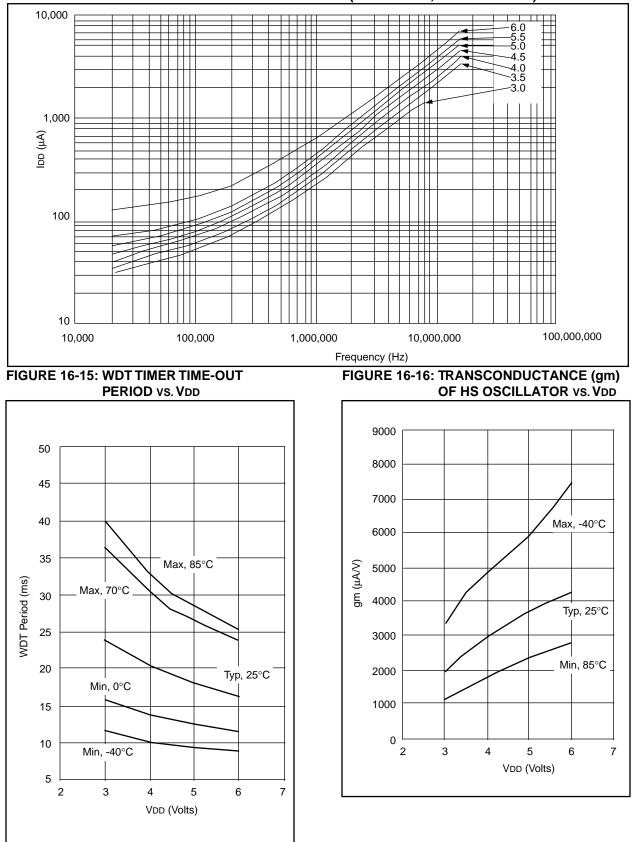

# FIGURE 16-14: MAXIMUM IDD vs. FREQ WITH A/D OFF (EXT CLOCK, -55° TO +125°C)

NOTES:

# **APPENDIX C: WHAT'S NEW**

1. Consolidated all pin compatible 18-pin A/D based devices into one data sheet.

# **APPENDIX D: WHAT'S CHANGED**

- 1. Minor changes, spelling and grammatical changes.

- 2. Low voltage operation on the PIC16LC710/711/ 715 has been reduced from 3.0V to 2.5V.

- 3. Part numbers of the PIC16C70 and PIC16C71A have changed to PIC16C710 and PIC16C711, respectively.

#### I

| I/O Ports                                     |    |

|-----------------------------------------------|----|

| PORTA2                                        |    |

| PORTB2                                        |    |

| Section2                                      |    |

| I/O Programming Considerations                |    |

| ICEPIC Low-Cost PIC16CXXX In-Circuit Emulator |    |

| In-Circuit Serial Programming47, 6            | 37 |

| INDF Register                                 |    |

| Indirect Addressing2                          |    |

| Instruction Cycle1                            |    |

| Instruction Flow/Pipelining1                  |    |

| Instruction Format                            | 36 |

| Instruction Set                               | _  |

| ADDLW7                                        |    |

| ADDWF                                         |    |

| ANDLW                                         |    |

| ANDWF                                         |    |

| BCF                                           |    |

| BSF                                           | '2 |

| BTFSC7                                        |    |

| BTFSS                                         |    |

| CALL                                          | 73 |

| CLRF                                          |    |

| CLRWDT                                        |    |

| COMF                                          |    |

| DECF                                          |    |

| DECFSZ                                        |    |

| GOTO                                          |    |

| INCF                                          |    |

| INCFSZ                                        |    |

| IORLW                                         |    |

| IORWF                                         |    |

| MOVF7                                         |    |

| MOVLW7                                        |    |

| MOVWF7                                        | 78 |

| NOP7                                          | 79 |

| OPTION7                                       | 79 |

| RETFIE7                                       |    |

| RETLW8                                        | 30 |

| RETURN8                                       |    |

| RLF8                                          |    |

| RRF                                           |    |

| SLEEP                                         |    |

| SUBLW                                         |    |

| SUBWF                                         |    |

| SWAPF8                                        |    |

| TRIS                                          |    |

| XORLW                                         |    |

| XORWF                                         |    |

| Section                                       |    |

| INT Interrupt                                 |    |

| INTCON Register                               |    |

| INTE bit                                      |    |

| INTEDG bit                                    |    |

| Internal Sampling Switch (Rss) Impedence      |    |

| Interrupts                                    |    |

| A/D                                           |    |

| External6                                     |    |

| PORTB Change6                                 |    |

| PortB Change6                                 |    |

| RB7:RB4 Port Change2                          |    |

| Section6                                      | 51 |

| TMR06                                         | 32 |

| TMR0 Overflow                                         | 61     |

|-------------------------------------------------------|--------|

| INTF bit                                              |        |

| IRP bit                                               | 17     |

| К                                                     |        |

| KeeLoq <sup>®</sup> Evaluation and Programming Tools  | 87     |