# E·XFL

#### NXP USA Inc. - S912ZVC12F0VKH Datasheet

#### Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Product Status             | Active                                                                 |

|----------------------------|------------------------------------------------------------------------|

| Core Processor             | S12Z                                                                   |

| Core Size                  | 16-Bit                                                                 |

| Speed                      | 32MHz                                                                  |

| Connectivity               | CANbus, I <sup>2</sup> C, SCI, SPI                                     |

| Peripherals                | DMA, POR, PWM, WDT                                                     |

| Number of I/O              | 42                                                                     |

| Program Memory Size        | 128KB (128K x 8)                                                       |

| Program Memory Type        | FLASH                                                                  |

| EEPROM Size                | 2K x 8                                                                 |

| RAM Size                   | 8K x 8                                                                 |

| Voltage - Supply (Vcc/Vdd) | 3.5V ~ 40V                                                             |

| Data Converters            | A/D 16x10b; D/A 1x8b                                                   |

| Oscillator Type            | Internal                                                               |

| Operating Temperature      | -40°C ~ 105°C (TA)                                                     |

| Mounting Type              | Surface Mount                                                          |

| Package / Case             | 64-LQFP Exposed Pad                                                    |

| Supplier Device Package    | 64-LQFP (10x10)                                                        |

| Purchase URL               | https://www.e-xfl.com/product-detail/nxp-semiconductors/s912zvc12f0vkh |

|                            |                                                                        |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

|      | 18.1.3 Features                              |  |

|------|----------------------------------------------|--|

|      | 18.1.4 Modes of Operation                    |  |

| 18.2 | External Signal Description                  |  |

|      | 18.2.1 RXCAN — CAN Receiver Input Pin        |  |

|      | 18.2.2 TXCAN — CAN Transmitter Output Pin    |  |

|      | 18.2.3 CAN System                            |  |

| 18.3 | Memory Map and Register Definition           |  |

|      | 18.3.1 Module Memory Map                     |  |

|      | 18.3.2 Register Descriptions                 |  |

|      | 18.3.3 Programmer's Model of Message Storage |  |

| 18.4 | Functional Description                       |  |

|      | 18.4.1 General                               |  |

|      | 18.4.2 Message Storage                       |  |

|      | 18.4.3 Identifier Acceptance Filter          |  |

|      | 18.4.4 Modes of Operation                    |  |

|      | 18.4.5 Low-Power Options                     |  |

|      | 18.4.6 Reset Initialization                  |  |

|      | 18.4.7 Interrupts                            |  |

| 18.5 | *                                            |  |

|      | 18.5.1 MSCAN initialization                  |  |

|      | 18.5.2 Bus-Off Recovery                      |  |

# Chapter 19 Digital Analog Converter (DAC\_8B5V\_V2)

| 19.1 | Revision History                                        |  |

|------|---------------------------------------------------------|--|

| 19.2 | Introduction                                            |  |

|      | 19.2.1 Features                                         |  |

|      | 19.2.2 Modes of Operation                               |  |

|      | 19.2.3 Block Diagram                                    |  |

| 19.3 | External Signal Description                             |  |

|      | 19.3.1 DACU Output Pin                                  |  |

|      | 19.3.2 AMP Output Pin                                   |  |

|      | 19.3.3 AMPP Input Pin                                   |  |

|      | 19.3.4 AMPM Input Pin                                   |  |

| 19.4 | Memory Map and Register Definition                      |  |

|      | 19.4.1 Register Summary                                 |  |

|      | 19.4.2 Register Descriptions                            |  |

| 19.5 | Functional Description                                  |  |

|      | 19.5.1 Functional Overview                              |  |

|      | 19.5.2 Mode "Off"                                       |  |

|      | 19.5.3 Mode "Operational Amplifier"                     |  |

|      | 19.5.4 Mode "Internal DAC only"                         |  |

|      | 19.5.5 Mode "Unbuffered DAC"                            |  |

|      | 19.5.6 Mode "Unbuffered DAC with Operational Amplifier" |  |

|      | 19.5.7 Mode "Buffered DAC"                              |  |

|      |                                                         |  |

# 1.4.12 Serial Peripheral Interface Module (SPI)

- Configurable 8- or 16-bit data size

- Full-duplex or single-wire bidirectional

- Double-buffered transmit and receive

- Master or slave mode

- MSB-first or LSB-first shifting

- Serial clock phase and polarity options

# **1.4.13** Analog-to-Digital Converter Module (ADC)

- 12-bit resolution

- Up to 16 external channels and 8 internal channels

- Left or right aligned result data

- Continuous conversion mode

- Programmers model with list based command and result storage architecture

- ADC directly writes results to RAM, preventing stall of further conversions

- Internal signals monitored with the ADC module

- VRH, VRL, (VRL+VRH)/2, VSUP monitor, VBG, Temperature Sensor, Port L HVI inputs

- External pins can also be used as digital I/O

- Up to 16 pins can be used as keyboard wake-up interrupt (KWU)

# 1.4.14 Digital-to-Analog Converter Module (DAC)

- 8-bit resolution

- Buffered and unbuffered analog output voltage usable

- Operational amplifier stand alone usable

# 1.4.15 Analog Comparator Module (ACMP)

- 0V to VDDA supply rail-to-rail inputs

- Low offset

- Up to 4 inputs selectable as inverting and non-inverting comparator inputs:

- 2 low-impedance inputs with selectable low pass filter for external pins

- 2 high-impedance inputs with fixed filter for SoC-internal signals

- Selectable hysteresis

- Selectable interrupt on rising edge, falling edge, or rising and falling edges of comparator output

- Option to output comparator signal on an external pin with selectable polarity

- Support for triggering timer input capture events

MC9S12ZVC Family Reference Manual, Rev. 2.0

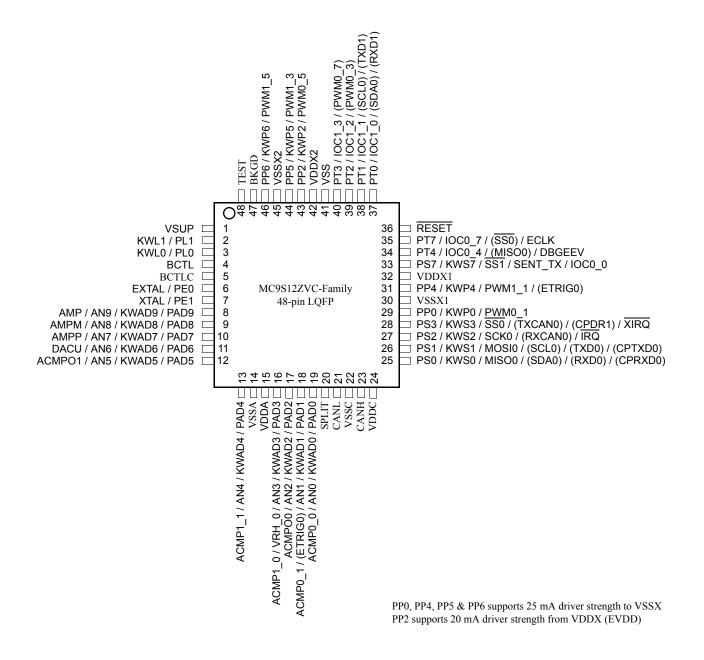

Figure 1-3. Pinout MC9S12ZVC-Family 48-pin LQFP

:

#### Chapter 2 Port Integration Module (S12ZVCPIMV1)

| Global<br>Address | Register<br>Name | Bit 7          | 6       | 5       | 4       | 3       | 2       | 1       | Bit 0   |

|-------------------|------------------|----------------|---------|---------|---------|---------|---------|---------|---------|

| 0x0264            | DDRE             | R 0<br>W       | 0       | 0       | 0       | 0       | 0       | DDRE1   | DDRE0   |

| 0x0265            | Reserved         | R 0<br>W       | 0       | 0       | 0       | 0       | 0       | 0       | 0       |

| 0x0266            | PERE             | R 0<br>W       | 0       | 0       | 0       | 0       | 0       | PERE1   | PERE0   |

| 0x0267            | Reserved         | R 0<br>W       | 0       | 0       | 0       | 0       | 0       | 0       | 0       |

| 0x0268            | PPSE             | R 0<br>W       | 0       | 0       | 0       | 0       | 0       | PPSE1   | PPSE0   |

| 0x0269–<br>0x027F | Reserved         | R 0<br>W       | 0       | 0       | 0       | 0       | 0       | 0       | 0       |

| 0x0280            | PTADH            | R<br>W PTADH7  | PTADH6  | PTADH5  | PTADH4  | PTADH3  | PTADH2  | PTADH1  | PTADH0  |

| 0x0281            | PTADL            | R<br>W PTADL7  | PTADL6  | PTADL5  | PTADL4  | PTADL3  | PTADL2  | PTADL1  | PTADL0  |

| 0x0282            | PTIADH           | R PTIADH7<br>W | PTIADH6 | PTIADH5 | PTIADH4 | PTIADH3 | PTIADH2 | PTIADH1 | PTIADH0 |

| 0x0283            | PTIADL           | R PTIADL7<br>W | PTIADL6 | PTIADL5 | PTIADL4 | PTIADL3 | PTIADL2 | PTIADL1 | PTIADL0 |

| 0x0284            | DDRADH           | R<br>W DDRADH7 | DDRADH6 | DDRADH5 | DDRADH4 | DDRADH3 | DDRADH2 | DDRADH1 | DDRADH0 |

| 0x0285            | DDRADL           | R<br>W DDRADL7 | DDRADL6 | DDRADL5 | DDRADL4 | DDRADL3 | DDRADL2 | DDRADL1 | DDRADL0 |

| 0x0286            | PERADH           | R<br>W PERADH7 | PERADH6 | PERADH5 | PERADH4 | PERADH3 | PERADH2 | PERADH1 | PERADH0 |

| 0x0287            | PERADL           | R<br>W PERADL7 | PERADL6 | PERADL5 | PERADL4 | PERADL3 | PERADL2 | PERADL1 | PERADL0 |

| 0x0288            | PPSADH           | R<br>W PPSADH7 | PPSADH6 | PPSADH5 | PPSADH4 | PPSADH3 | PPSADH2 | PPSADH1 | PPSADH0 |

| 0x0289            | PPSADL           | R<br>W PPSADL7 | PPSADL6 | PPSADL5 | PPSADL4 | PPSADL3 | PPSADL2 | PPSADL1 | PPSADL0 |

MC9S12ZVC Family Reference Manual, Rev. 2.0

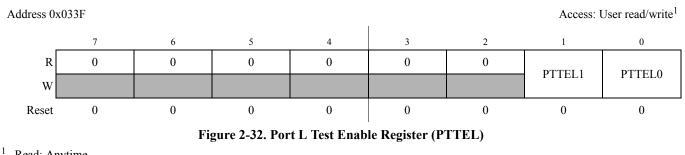

# 2.3.4.12 Port L Test Enable Register (PTTEL)

Read: Anytime Write: Anytime

| Field           | Description                                                                                                                                                                                                                                                                                                                |  |  |

|-----------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|

| 1-0<br>PTTEL1-0 | Port L Test Enable —<br>This hit forces the input buffer of the HVI nin active while using the englog function to support open input detection in run mode                                                                                                                                                                 |  |  |

| FIIELI-0        | This bit forces the input buffer of the HVI pin active while using the analog function to support open input detection in run mode.<br>Refer to Section 2.5.5, "Open Input Detection on PL[1:0] (HVI)"). In stop mode this bit has no effect.<br>Note: In direct mode (PTADIRL=1) the digital input buffer is not enabled. |  |  |

|                 | 1 Input buffer enabled when used with analog function and not in direct mode (PTADIRL=0)<br>0 Input buffer disabled when used with analog function                                                                                                                                                                         |  |  |

# 2.4 Functional Description

# 2.4.1 General

Each pin except BKGD can act as general-purpose I/O. In addition each pin can act as an output or input of a peripheral module.

# 2.4.2 Registers

Table 2-33 lists the implemented configuration bits which are available on each port. These registers except the pin input registers can be written at any time, however a specific configuration might not become active. For example a pullup device does not become active while the port is used as a push-pull output.

Unimplemented bits read zero.

# 2.4.4.3 Over-Current Interrupt and Protection

In case of an over-current condition on PP2 (EVDD1) or PP[6-4,0] (see Section 2.5.3, "Over-Current Protection on PP2 (EVDD1)"" and 2.5.4, "Over-Current Protection on PP[6-4,0]"") the related over-current interrupt flag OCIFP[OCIFP] asserts. This flag generates an interrupt if the enable bit OCIEP[OCIEP] is set.

An asserted flag immediately forces the related output independent of its driving source (peripheral output or port register bit) to its disabled level to protect the device. The flag must be cleared to re-enable the driver.

# 2.4.5 High-Voltage Input

A high-voltage input (HVI) on port L has the following features:

- Input voltage proof up to  $V_{HVI}$

- Digital input function with pin interrupt and wakeup from stop capability

- Analog input function with selectable divider ratio routable to ADC channel. Optional direct input bypassing voltage divider and impedance converter. Capable to wakeup from stop (pin interrupts in run mode not available). Open input detection.

Figure 2-35 shows a block diagram of the HVI.

# NOTE

The term stop mode (STOP) is limited to voltage regulator operating in reduced performance mode (RPM). Refer to "Low Power Modes" section in device overview.

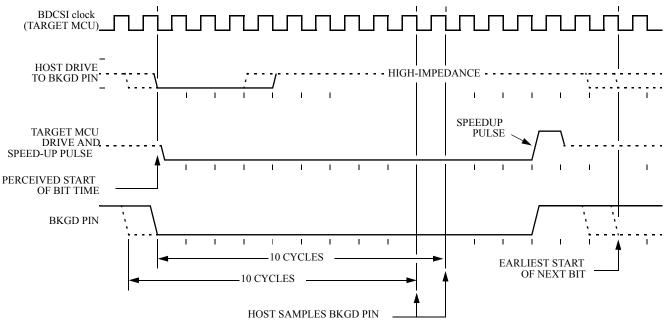

Figure 3-8. BDC Target-to-Host Serial Bit Timing (Logic 0)

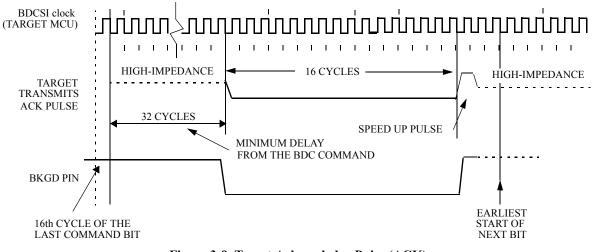

# 3.4.7 Serial Interface Hardware Handshake (ACK Pulse) Protocol

BDC commands are processed internally at the device core clock rate. Since the BDCSI clock can be asynchronous relative to the bus frequency, a handshake protocol is provided so the host can determine when an issued command has been executed. This section describes the hardware handshake protocol.

The hardware handshake protocol signals to the host controller when a BDC command has been executed by the target. This protocol is implemented by a low pulse (16 BDCSI clock cycles) followed by a brief speedup pulse on the BKGD pin, generated by the target MCU when a command, issued by the host, has been successfully executed (see Figure 3-9). This pulse is referred to as the ACK pulse. After the ACK pulse has finished, the host can start the bit retrieval if the last issued command was a read command, or start a new command if the last command was a write command or a control command.

Figure 3-9. Target Acknowledge Pulse (ACK)

# 6.4.3.1 Comparator Match Events

# 6.4.3.1.1 Opcode Address Comparator Match

The comparator is loaded with the address of the selected instruction and the comparator control register INST bit is set. When the opcode reaches the execution stage of the instruction queue a match occurs just before the instruction executes, allowing a breakpoint immediately before the instruction boundary. The comparator address register must contain the address of the first opcode byte for the match to occur. Opcode address matches are data independent thus the RWE and RW bits are ignored. CPU compares are disabled when BDM becomes active.

# 6.4.3.1.2 Data Access Comparator Match

Data access matches are generated when an access occurs at the address contained in the comparator address register. The match can be qualified by the access data and by the access type (read/write). The breakpoint occurs a maximum of 2 instructions after the access in the CPU flow. Note, if a COF occurs between access and breakpoint, the opcode address of the breakpoint can be elsewhere in the memory map.

Opcode fetches are not classed as data accesses. Thus data access matches are not possible on opcode fetches.

# 6.4.3.2 External Event

The DBGEEV input signal can force a state sequencer transition, independent of internal comparator matches. The DBGEEV is an input signal mapped directly to a device pin and configured by the EEVE field in DBGC1. The external events can change the state sequencer state.

If configured to change the state sequencer state, then the external match is mapped to DBGSCRx bits C3SC[1:0]. The DBGEFR bit EEVF is set when an external event occurs.

# 6.4.3.3 Setting The TRIG Bit

Independent of comparator matches it is possible to initiate a breakpoint by writing the TRIG bit in DBGC1 to a logic "1". This forces the state sequencer into the Final State. the transition to Final State is followed immediately by a transition to State0.

Breakpoints, if enabled, are issued on the transition to State0.

# 6.4.3.4 Event Priorities

If simultaneous events occur, the priority is resolved according to Table 6-31. Lower priority events are suppressed. It is thus possible to miss a lower priority event if it occurs simultaneously with an event of a higher priority. The event priorities dictate that in the case of simultaneous matches, the match on the higher comparator channel number (3,1,0) has priority.

If a write access to DBGC1 with the ARM bit position set occurs simultaneously to a hardware disarm from an internal event, then the ARM bit is cleared due to the hardware disarm.

Chapter 9 Analog-to-Digital Converter (ADC12B\_LBA\_V1)

# 9.4.2.9 ADC Error Interrupt Flag Register (ADCEIF)

If one of the following error flags is set the ADC ceases operation:

- IA\_EIF

- CMD\_EIF

- EOL\_EIF

- TRIG EIF

In order to make the ADC operational again an ADC Soft-Reset must be issued which clears above listed error interrupt flags.

The error interrupt flags RSTAR\_EIF and LDOK\_EIF do not cause the ADC to cease operation. If set the ADC continues operation. Each of the two bits can be cleared by writing a value of 1'b1. Both bits are also cleared if an ADC Soft-Reset is issued.

All bits are cleared if bit ADC\_EN is clear. Writing any flag with value 1'b0 does not clear a flag. Writing any flag with value 1'b1 does not set the flag.

Module Base + 0x0008

| _     | 7      | 6                           | 5       | 4        | 3        | 2         | 1        | 0 |

|-------|--------|-----------------------------|---------|----------|----------|-----------|----------|---|

| R     | IA EIF | CMD EIF                     | EOL EIF | Reserved | TRIG EIF | RSTAR EIF | LDOK EIF | 0 |

| W     | IA_EII | CMD_EII                     | LOL_LII | Keseiveu | TKIO_LII | K51AK_EII | LDOK_LII |   |

| Reset | 0      | 0                           | 0       | 0        | 0        | 0         | 0        | 0 |

|       |        | = Unimplemented or Reserved |         |          |          |           |          |   |

Figure 9-12. ADC Error Interrupt Flag Register (ADCEIF)

Read: Anytime

Write:

- Bits RSTAR\_EIF and LDOK\_EIF are writable anytime

- Bits IA\_EIF, CMD\_EIF, EOL\_EIF and TRIG\_EIF are not writable

Table 9-13. ADCEIF Field Descriptions

| Field        | Description                                                                                                                                                                                                                                                                                                                                                                                                      |

|--------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 7<br>IA_EIF  | <b>Illegal Access Error Interrupt Flag</b> — This flag indicates that storing the conversion result caused an illegal access error or conversion command loading from outside system RAM or NVM area occurred.         The ADC ceases operation if this error flag is set (issue of type severe).       0         No illegal access error occurred.       1         An illegal access error occurred.       1    |

| 6<br>CMD_EIF | <ul> <li>Command Value Error Interrupt Flag — This flag indicates that an invalid command is loaded (Any command that contains reserved bit settings) or illegal format setting selected (reserved SRES[2:0] bit settings).</li> <li>The ADC ceases operation if this error flag is set (issue of type severe).</li> <li>Valid conversion command loaded.</li> <li>Invalid conversion command loaded.</li> </ul> |

| 5<br>EOL_EIF | <ul> <li>"End Of List" Error Interrupt Flag — This flag indicates a missing "End Of List" command type in current executed CSL.</li> <li>The ADC ceases operation if this error flag is set (issue of type severe).</li> <li>No "End Of List" error.</li> <li>"End Of List" command type missing in current executed CSL.</li> </ul>                                                                             |

# 9.5.3.3 ADC List Usage and Conversion/Conversion Sequence Flow Description

It is the user's responsibility to make sure that the different lists do not overlap or exceed the system RAM area respectively the CSL does not exceed the NVM area if located in the NVM. The error flag IA\_EIF will be set for accesses done outside the system RAM area and will cause an error interrupt if enabled for lists that are located in the system RAM.

Generic flow for ADC register load at conversion sequence start/restart:

- It is mandatory that the ADC is idle (no ongoing conversion or conversion sequence).

- It is mandatory to have at least one CSL with valid entries. See also Section 9.8.7.2, "Restart CSL execution with currently active CSL or Section 9.8.7.3, "Restart CSL execution with new/other CSL (alternative CSL becomes active CSL) CSL swapping for more details on possible scenarios.

- A Restart Event occurs, which causes the index registers to be cleared (register ADCCIDX and ADCRIDX are cleared) and to point to the top of the corresponding lists (top of active RVL and CSL).

- Load conversion command to background conversion command register 1.

- The control bit(s) RSTA (and LDOK if set) are cleared.

- Wait for Trigger Event to start conversion.

Generic flow for ADC register load during conversion:

- The index registers ADCCIDX is incremented.

- The inactive background command register is loaded with a new conversion command.

Generic flow for ADC result storage at end of conversion:

- Index register ADCRIDX is incremented and the conversion result is stored in system RAM. As soon as the result is successfully stored, any conversion interrupt flags are set accordingly.

- At the conversion boundary the other background command register becomes active and visible in the ADC register map.

- If the last executed conversion command was of type "End Of Sequence", the ADC waits for the Trigger Event.

- If the last executed conversion command was of type "End Of List" and the ADC is configured in "Restart Mode", the ADC sets all related flags and stays idle awaiting a Restart Event to continue.

- If the last executed conversion command was of type "End Of List" and the ADC is configured in "Trigger Mode", the ADC sets all related flags and automatically returns to top of current CSL and is awaiting a Trigger Event to continue.

- If the last executed conversion command was of type "Normal Conversion" the ADC continues command execution in the order of the current CSL (continues conversion).

# Chapter 10 Supply Voltage Sensor - (BATSV3)

| Rev. No.<br>(Item No.) | Data        | Sections Affected                                                                           | Substantial Change(s) |

|------------------------|-------------|---------------------------------------------------------------------------------------------|-----------------------|

| V01.00                 | 15 Dec 2010 | all                                                                                         | Initial Version       |

| V02.00                 | 16 Mar 2011 | 10.3.2.1- added BVLS[1] to support four voltage level10.4.2.1- moved BVHS to register bit 6 |                       |

| V03.00                 | 26 Apr 2011 | all - removed Vsense                                                                        |                       |

| V03.10                 | 04 Oct 2011 | 10.4.2.1 and 10.4.2.2                                                                       | - removed BSESE       |

#### Table 10-1. Revision History Table

# **10.1** Introduction

The BATS module provides the functionality to measure the voltage of the chip supply pin VSUP.

# 10.1.1 Features

The VSUP pin can be routed via an internal divider to the internal Analog to Digital Converter. Independent of the routing to the Analog to Digital Converter, it is possible to route this voltage to a comparator to generate a low or a high voltage interrupt to alert the MCU.

# **10.1.2** Modes of Operation

The BATS module behaves as follows in the system power modes:

1. Run mode

The activation of the VSUP Level Sense Enable (BSUSE=1) or ADC connection Enable (BSUAE=1) closes the path from VSUP pin through the resistor chain to ground and enables the associated features if selected.

2. Stop mode

During stop mode operation the path from the VSUP pin through the resistor chain to ground is opened and the low and high voltage sense features are disabled. The content of the configuration register is unchanged.

| Field      | Description                                                                                                                                                         |

|------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 1<br>BVHIF | <b>BATS Interrupt Flag High Detect</b> — The flag is set to 1 when BVHC status bit changes.                                                                         |

|            | <ol> <li>No change of the BVHC status bit since the last clearing of the flag.</li> <li>BVHC status bit has changed since the last clearing of the flag.</li> </ol> |

| 0<br>BVLIF | <b>BATS Interrupt Flag Low Detect</b> — The flag is set to 1 when BVLC status bit changes.                                                                          |

| D ( Dif    | <ol> <li>No change of the BVLC status bit since the last clearing of the flag.</li> <li>BVLC status bit has changed since the last clearing of the flag.</li> </ol> |

#### Table 10-5. BATIF Register Field Descriptions

# 10.3.2.5 Reserved Register

Figure 10-8. Reserved Register

Read: Anytime Write: Only in special mode

# NOTE

These reserved registers are designed for factory test purposes only and are not intended for general user access. Writing to these registers when in special mode can alter the module's functionality.

# **10.4** Functional Description

# 10.4.1 General

The BATS module allows measuring the voltage on the VSUP pin. The voltage at the VSUP pin can be routed via an internal voltage divider to an internal Analog to Digital Converter Channel. Also the BATS module can be configured to generate a low and high voltage interrupt based on VSUP. The trigger level of the high and low interrupt are selectable.

# 10.4.2 Interrupts

This section describes the interrupt generated by the BATS module. The interrupt is only available in CPU run mode. Entering and exiting CPU stop mode has no effect on the interrupt flags.

To make sure the interrupt generation works properly the bus clock frequency must be higher than the Voltage Warning Low Pass Filter frequency ( $f_{VWLP}$  filter).

# 14.5.3.1 Description of Interrupt Operation

The SCI only originates interrupt requests. The following is a description of how the SCI makes a request and how the MCU should acknowledge that request. The interrupt vector offset and interrupt number are chip dependent. The SCI only has a single interrupt line (SCI Interrupt Signal, active high operation) and all the following interrupts, when generated, are ORed together and issued through that port.

# 14.5.3.1.1 TDRE Description

The TDRE interrupt is set high by the SCI when the transmit shift register receives a byte from the SCI data register. A TDRE interrupt indicates that the transmit data register (SCIDRH/L) is empty and that a new byte can be written to the SCIDRH/L for transmission.Clear TDRE by reading SCI status register 1 with TDRE set and then writing to SCI data register low (SCIDRL).

# 14.5.3.1.2 TC Description

The TC interrupt is set by the SCI when a transmission has been completed. Transmission is completed when all bits including the stop bit (if transmitted) have been shifted out and no data is queued to be transmitted. No stop bit is transmitted when sending a break character and the TC flag is set (providing there is no more data queued for transmission) when the break character has been shifted out. A TC interrupt indicates that there is no transmission in progress. TC is set high when the TDRE flag is set and no data, preamble, or break character is being transmitted. When TC is set, the TXD pin becomes idle (logic 1). Clear TC by reading SCI status register 1 (SCISR1) with TC set and then writing to SCI data register low (SCIDRL).TC is cleared automatically when data, preamble, or break is queued and ready to be sent.

# 14.5.3.1.3 RDRF Description

The RDRF interrupt is set when the data in the receive shift register transfers to the SCI data register. A RDRF interrupt indicates that the received data has been transferred to the SCI data register and that the byte can now be read by the MCU. The RDRF interrupt is cleared by reading the SCI status register one (SCISR1) and then reading SCI data register low (SCIDRL).

# 14.5.3.1.4 OR Description

The OR interrupt is set when software fails to read the SCI data register before the receive shift register receives the next frame. The newly acquired data in the shift register will be lost in this case, but the data already in the SCI data registers is not affected. The OR interrupt is cleared by reading the SCI status register one (SCISR1) and then reading SCI data register low (SCIDRL).

# 14.5.3.1.5 IDLE Description

The IDLE interrupt is set when 10 consecutive logic 1s (if M = 0) or 11 consecutive logic 1s (if M = 1) appear on the receiver input. Once the IDLE is cleared, a valid frame must again set the RDRF flag before an idle condition can set the IDLE flag. Clear IDLE by reading SCI status register 1 (SCISR1) with IDLE set and then reading SCI data register low (SCIDRL).

# 16.4.1.8 Handshaking

The clock synchronization mechanism can be used as a handshake in data transfer. Slave devices may hold the SCL low after completion of one byte transfer (9 bits). In such case, it halts the bus clock and forces the master clock into wait states until the slave releases the SCL line.

# 16.4.1.9 Clock Stretching

The clock synchronization mechanism can be used by slaves to slow down the bit rate of a transfer. After the master has driven SCL low the slave can drive SCL low for the required period and then release it. If the slave SCL low period is greater than the master SCL low period then the resulting SCL bus signal low period is stretched.

# 16.4.1.10 Ten-bit Address

A ten-bit address is indicated if the first 5 bits of the first address byte are 0x11110. The following rules apply to the first address byte.

| SLAVE<br>ADDRESS | R/W BIT | DESCRIPTION                          |

|------------------|---------|--------------------------------------|

| 0000000          | 0       | General call address                 |

| 0000010          | Х       | Reserved for different bus<br>format |

| 0000011          | Х       | Reserved for future purposes         |

| 11111XX          | х       | Reserved for future purposes         |

| 11110XX          | Х       | 10-bit slave addressing              |

Figure 16-13. Definition of bits in the first byte.

The address type is identified by ADTYPE. When ADTYPE is 0, 7-bit address is applied. Reversely, the address is 10-bit address.Generally, there are two cases of 10-bit address.See the Figure 16-14 and Figure 16-15.

| S | Slave Add1st 7bits<br>11110+ADR10+ADR9 | R/W<br>0 | A1 | Slave Add 2nd byte<br>ADR[8:1] | A2 | Data | A3 |  |

|---|----------------------------------------|----------|----|--------------------------------|----|------|----|--|

|---|----------------------------------------|----------|----|--------------------------------|----|------|----|--|

Figure 16-14. A master-transmitter addresses a slave-receiver with a 10-bit address

| S | Slave Add1st 7bits<br>11110+ADR10+ADR9 | R/W<br>0 | A1 | Slave Add 2nd byte<br>ADR[8:1] | A2 | Sr | Slave Add 1st 7bits<br>11110+ADR10+ADR9 | R/W<br>1 | A3 | Data | A4 |

|---|----------------------------------------|----------|----|--------------------------------|----|----|-----------------------------------------|----------|----|------|----|

|   |                                        |          |    | ,<br>,                         |    |    |                                         |          |    |      |    |

### Figure 16-15. A master-receiver addresses a slave-transmitter with a 10-bit address.

In the Figure 16-15, the first two bytes are the similar to Figure 16-14. After the repeated START(Sr), the first slave address is transmitted again, but the R/W is 1, meaning that the slave is acted as a transmitter.

Chapter 16 Inter-Integrated Circuit (IICV3) Block Description

Chapter 18 Scalable Controller Area Network (S12MSCANV3)

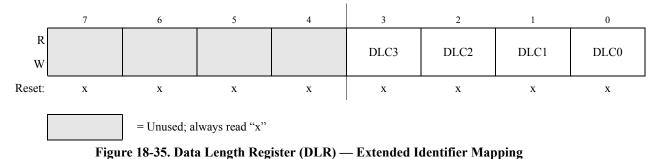

# **18.3.3.3** Data Length Register (DLR)

This register keeps the data length field of the CAN frame.

Module Base + 0x00XC

| Table 18-33. | DLR Register | Field Descriptions |

|--------------|--------------|--------------------|

| 14010 10 00. | DERINGISTER  | I feld Deser phons |

| Field           | Description                                                                                                                                                                                                                                                                                                                                                                                       |

|-----------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 3-0<br>DLC[3:0] | <b>Data Length Code Bits</b> — The data length code contains the number of bytes (data byte count) of the respective message. During the transmission of a remote frame, the data length code is transmitted as programmed while the number of transmitted data bytes is always 0. The data byte count ranges from 0 to 8 for a data frame. Table 18-34 shows the effect of setting the DLC bits. |

#### Table 18-34. Data Length Codes

|      | Data Length Code |      |      |       |  |  |  |  |

|------|------------------|------|------|-------|--|--|--|--|

| DLC3 | DLC2             | DLC1 | DLC0 | Count |  |  |  |  |

| 0    | 0                | 0    | 0    | 0     |  |  |  |  |

| 0    | 0                | 0    | 1    | 1     |  |  |  |  |

| 0    | 0                | 1    | 0    | 2     |  |  |  |  |

| 0    | 0                | 1    | 1    | 3     |  |  |  |  |

| 0    | 1                | 0    | 0    | 4     |  |  |  |  |

| 0    | 1                | 0    | 1    | 5     |  |  |  |  |

| 0    | 1                | 1    | 0    | 6     |  |  |  |  |

| 0    | 1                | 1    | 1    | 7     |  |  |  |  |

| 1    | 0                | 0    | 0    | 8     |  |  |  |  |

# **18.3.3.4** Transmit Buffer Priority Register (TBPR)

This register defines the local priority of the associated message buffer. The local priority is used for the internal prioritization process of the MSCAN and is defined to be highest for the smallest binary number. The MSCAN implements the following internal prioritization mechanisms:

- All transmission buffers with a cleared TXEx flag participate in the prioritization immediately before the SOF (start of frame) is sent.

- The transmission buffer with the lowest local priority field wins the prioritization.

# **Appendix G PIM Electrical Specifications**

# G.1 High-Voltage Inputs (HVI) Electrical Characteristics

#### Table G-1. Static Electrical Characteristics - High Voltage Input Pins - Port L

Characteristics are  $5.5V \le V_{SUP} \le 18 \text{ V}$ ,  $-40^{\circ}C \le T_J \le 175^{\circ}C^1$  unless otherwise noted. Typical values noted reflect the approximate parameter mean at  $T_A = 25^{\circ}C^2$  under nominal conditions unless otherwise noted.

| Num | Ratings                                                                                                                                                                                                                                                                                                             | Symbol                                                               | Min        | Тур                                | Max               | Unit        |

|-----|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------|------------|------------------------------------|-------------------|-------------|

| 25  | Digital Input Threshold<br>• $V_{SUP} > 6.5V$<br>• $5.5V \le V_{SUP} \le 6.5V$                                                                                                                                                                                                                                      | V <sub>TH_HVI</sub>                                                  | 2.8<br>2.0 | 3.5<br>2.5                         | 4.5<br>3.8        | V<br>V      |

| 26  | Input Hysteresis                                                                                                                                                                                                                                                                                                    | V <sub>HYS_HVI</sub>                                                 | _          | 250                                | _                 | mV          |

| 27  | Pin Input Divider Ratio with external series $R_{EXT_HVI}$<br>Ratio = $V_{HVI} / V_{Internal(ADC)}$                                                                                                                                                                                                                 | Ratio <sub>L_HVI</sub><br>Ratio <sub>H_HVI</sub>                     |            | 2<br>6                             |                   |             |

| 28  | $\begin{array}{l} \mbox{Analog Input Matching} \\ \mbox{Absolute Error on } V_{ADC} \\ \mbox{Ompared to } V_{HVI} / \mbox{Ratio}_{L-HVI} \\ (1V < V_{HVI} < 7V) \\ \mbox{Ompared to } V_{HVI} / \mbox{Ratio}_{H-HVI} \\ (3V < V_{HVI} < 21V) \\ \mbox{Direct Mode (PTADIRL=1)} \\ (0.5V < VHVI < 3.5V) \end{array}$ | AIM <sub>L_HVI</sub><br>AIM <sub>H_HVI</sub><br>AIM <sub>D_HVI</sub> | -          | $\pm 2 \\ \pm 2 \\ \pm 2 \\ \pm 2$ | ± 5<br>± 5<br>± 5 | %<br>%<br>% |

| 29  | High Voltage Input Series Resistor<br>Note: Always required externally at HVI pins.                                                                                                                                                                                                                                 | R <sub>EXT_HVI</sub>                                                 | -          | 10                                 | _                 | kΩ          |

| 30  | Enable Uncertainty Time                                                                                                                                                                                                                                                                                             | t <sub>UNC_HVI</sub>                                                 | _          | 1                                  | _                 | μs          |

| 31  | Input capacitance                                                                                                                                                                                                                                                                                                   | C <sub>IN_HVI</sub>                                                  | -          | 8                                  | -                 | pF          |

<sup>1</sup>  $T_J$ : Junction Temperature

<sup>2</sup> T<sub>A</sub>: Ambient Temperature

| Table G-2. Absolute Maximum Ratings | s - High Voltage Input Pins - Port L |

|-------------------------------------|--------------------------------------|

|-------------------------------------|--------------------------------------|

|   | Num | Ratings                        | Symbol           | Min | Тур | Max | Unit |

|---|-----|--------------------------------|------------------|-----|-----|-----|------|

| I | 1   | V <sub>HVI</sub> Voltage Range | V <sub>HVI</sub> | -27 | -   | 42  | V    |

MC9S12ZVC Family Reference Manual, Rev. 2.0

Appendix H ACMP Electrical Specifications

Characteristics noted under conditions  $3.13V \le VDDA \le 5.5V >$ ,  $-40^{\circ}C \le T_J \le 150^{\circ}C^1$  unless otherwise noted. Typical values noted reflect the approximate parameter mean at  $T_A = 25^{\circ}C^2$  under nominal conditions unless otherwise noted.

| Num | Ratings                                                                                                                                                                                                                                                                            | Symbol                   | Min                     | Тур                       | Max                        | Unit                 |

|-----|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------|-------------------------|---------------------------|----------------------------|----------------------|

| 4   | $\begin{array}{l} \mbox{Pad Input Current in } V_{ACMP\_in} \mbox{ range} \\ \bullet \ -40^\circ C \leq T_J \leq 80^\circ C \\ \bullet \ -40^\circ C \leq T_J \leq 150^\circ C \\ \bullet \ -40^\circ C \leq T_J \leq 175^\circ C \\ \mbox{For } 0V < Vpad\_in < VDDA \end{array}$ | I <sub>ACMP_pad_in</sub> | -1<br>-2<br>-3          | -<br>-<br>-               | 1<br>2<br>3                | μΑ<br>μΑ<br>μΑ       |

| 5   | Input Offset<br>• $-40^{\circ}C \le T_J \le 150^{\circ}C$<br>• $-40^{\circ}C \le T_J \le 175^{\circ}C$                                                                                                                                                                             | V <sub>ACMP_offset</sub> | -25<br>-25              | 0<br>0                    | 25<br>25                   | mV<br>mV             |

| 6   | Input Hysteresis in run mode<br>• [ACHYS] = 00<br>• [ACHYS] = 01<br>• [ACHYS] = 10<br>• [ACHYS] = 11                                                                                                                                                                               | V <sub>ACMP_hyst</sub>   | -3<br>-10<br>-30<br>-50 | -12<br>-24<br>-60<br>-125 | -22<br>-40<br>-100<br>-200 | mV<br>mV<br>mV<br>mV |

| 7   | Common Mode Input range<br>• V <sub>ACMP_0</sub><br>• V <sub>ACMP_1</sub><br>• V <sub>acmpi_0</sub><br>• V <sub>acmpi_1</sub>                                                                                                                                                      | V <sub>ACMP_in</sub>     | 0                       | V <sub>DDA</sub> /2       | V <sub>DDA</sub>           | V                    |

| 8   | $\begin{array}{l} Common \ Mode \ Input \ range \\ 150^\circ C \leq T_J \leq 175^\circ C \\ \bullet \ V_{ACMP\_0} \\ \bullet \ V_{ACMP\_1} \\ \bullet \ V_{acmpi\_0} \\ \bullet \ V_{acmpi\_1} \end{array}$                                                                        | V <sub>ACMP_in</sub>     | 0                       | V <sub>DDA</sub> /2       | V <sub>DDA</sub>           | V                    |

<sup>1</sup> T<sub>J</sub>: Junction Temperature

# Appendix M Ordering Information

Customers can choose either the mask-specific partnumber or the generic, mask-independent partnumber. Ordering a mask-specific partnumber enables the customer to specify which particular maskset they receive whereas ordering the generic partnumber means that the currently preferred maskset (which may change over time) is shipped. In either case, the marking on the device always shows the generic, mask-independent partnumber and the mask set number. The below figure illustrates the structure of a typical mask-specific ordering number.

# N.23 0x0800-0x083F CAN0

| Register<br>Name   |        | Bit 7  | 6          | 5              | 4       | 3       | 2       | 1      | Bit 0  |

|--------------------|--------|--------|------------|----------------|---------|---------|---------|--------|--------|

| 0x0800<br>CANCTL0  | R<br>W | RXFRM  | RXACT      | CSWAI          | SYNCH   | TIME    | WUPE    | SLPRQ  | INITRQ |

| 0x0001<br>CANCTL1  | R<br>W | CANE   | CLKSRC     | LOOPB          | LISTEN  | BORM    | WUPM    | SLPAK  | INITAK |

| 0x0802<br>CANBTR0  | R<br>W | SJW1   | SJW0       | BRP5           | BRP4    | BRP3    | BRP2    | BRP1   | BRP0   |

| 0x0803<br>CANBTR1  | R<br>W | SAMP   | TSEG22     | TSEG21         | TSEG20  | TSEG13  | TSEG12  | TSEG11 | TSEG10 |

| 0x0804<br>CANRFLG  | R<br>W | WUPIF  | CSCIF      | RSTAT1         | RSTAT0  | TSTAT1  | TSTAT0  | OVRIF  | RXF    |

| 0x0805<br>CANRIER  | R<br>W | WUPIE  | CSCIE      | RSTATE1        | RSTATE0 | TSTATE1 | TSTATE0 | OVRIE  | RXFIE  |

| 0x0806<br>CANTFLG  | R<br>W | 0      | 0          | 0              | 0       | 0       | TXE2    | TXE1   | TXE0   |

| 0x0807<br>CANTIER  | R<br>W | 0      | 0          | 0              | 0       | 0       | TXEIE2  | TXEIE1 | TXEIE0 |

| 0x0808<br>CANTARQ  | R<br>W | 0      | 0          | 0              | 0       | 0       | ABTRQ2  | ABTRQ1 | ABTRQ0 |

| 0x0809<br>CANTAAK  | R<br>W | 0      | 0          | 0              | 0       | 0       | ABTAK2  | ABTAK1 | ABTAK0 |

| 0x080A<br>CANTBSEL | R<br>W | 0      | 0          | 0              | 0       | 0       | TX2     | TX1    | TX0    |

| 0x080B<br>CANIDAC  | R<br>W | 0      | 0          | IDAM1          | IDAM0   | 0       | IDHIT2  | IDHIT1 | IDHIT0 |

| 0x080C<br>Reserved | R<br>W | 0      | 0          | 0              | 0       | 0       | 0       | 0      | 0      |

| 0x000D<br>CANMISC  | R<br>W | 0      | 0          | 0              | 0       | 0       | 0       | 0      | BOHOLD |

| 0x080E<br>CANRXERR | R<br>W | RXERR7 | RXERR6     | RXERR5         | RXERR4  | RXERR3  | RXERR2  | RXERR1 | RXERR0 |

|                    | [      |        | = Unimplem | ented or Reser | rved    |         |         |        |        |