# E·XFL

# Details

#### Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

| Product Status             | Active                                                                  |

|----------------------------|-------------------------------------------------------------------------|

| Core Processor             | S12Z                                                                    |

| Core Size                  | 16-Bit                                                                  |

| Speed                      | 32MHz                                                                   |

| Connectivity               | CANbus, I <sup>2</sup> C, SCI, SPI                                      |

| Peripherals                | DMA, POR, PWM, WDT                                                      |

| Number of I/O              | 42                                                                      |

| Program Memory Size        | 192KB (192K x 8)                                                        |

| Program Memory Type        | FLASH                                                                   |

| EEPROM Size                | 2K x 8                                                                  |

| RAM Size                   | 12K x 8                                                                 |

| Voltage - Supply (Vcc/Vdd) | 3.5V ~ 40V                                                              |

| Data Converters            | A/D 16x10b; D/A 1x8b                                                    |

| Oscillator Type            | Internal                                                                |

| Operating Temperature      | -40°C ~ 105°C (TA)                                                      |

| Mounting Type              | Surface Mount                                                           |

| Package / Case             | 64-LQFP Exposed Pad                                                     |

| Supplier Device Package    | 64-LQFP (10x10)                                                         |

| Purchase URL               | https://www.e-xfl.com/product-detail/nxp-semiconductors/s912zvc19f0vkhr |

|                            |                                                                         |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

- State sequencer control

- State transitions forced by comparator matches

- State transitions forced by software write to TRIGState transitions forced by an external event

- The following types of breakpoints

- CPU breakpoint entering active BDM on breakpoint (BDM)

- CPU breakpoint executing SWI on breakpoint (SWI)

# 1.4.2 Embedded Memory

### **1.4.2.1** Memory Access Integrity

- Illegal address detection

- ECC support on embedded NVM and system RAM

### 1.4.2.2 Flash

On-chip flash memory on the MC9S12ZVC-Family on the features the following:

- Up to 192Kbytes of program flash memory

- Automated program and erase algorithm

- Protection scheme to prevent accidental program or erase

# 1.4.2.3 EEPROM

- 2 Kbytes EEPROM

- 16 data bits plus 6 syndrome ECC (error correction code) bits allow single bit error correction and double fault detection

- Erase sector size 4 bytes

- Automated program and erase algorithm

- User margin level setting for reads

# 1.4.2.4 SRAM

• 12 Kbytes of general-purpose RAM with ECC

— Single bit error correction and double bit error detection code based on 16-bit data words

# 1.4.3 Clocks, Reset and Power Management Unit (CPMU)

- Real time interrupt (RTI)

- Clock monitor, supervising the correct function of the oscillator (CM)

- Computer operating properly (COP) watchdog

- Configurable as window COP for enhanced failure detection

- Can be initialized out of reset using option bits located in flash memory

Read: Anytime Write: Anytime, write 1 to clear

1

| Field       | Description                                                                                                                                                                                                                                                                                                               |

|-------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 6<br>OCIFP6 | Over-Current Interrupt Flag —<br>This flag asserts if an over-current condition is detected on PP6 (Section 2.4.4.3, "Over-Current Interrupt and Protection"").<br>Writing a logic "1" to the corresponding bit field clears the flag.<br>1 PP6 over-current event occurred<br>0 No PP6 over-current event occurred       |

| 5<br>OCIFP5 | Over-Current Interrupt Flag —<br>This flag asserts if an over-current condition is detected on PP5 (Section 2.4.4.3, "Over-Current Interrupt and Protection"").<br>Writing a logic "1" to the corresponding bit field clears the flag.<br>1 PP5 over-current event occurred<br>0 No PP5 over-current event occurred       |

| 4<br>OCIFP4 | Over-Current Interrupt Flag —<br>This flag asserts if an over-current condition is detected on PP4 (Section 2.4.4.3, "Over-Current Interrupt and Protection"").<br>Writing a logic "1" to the corresponding bit field clears the flag.<br>1 PP4 over-current event occurred<br>0 No PP4 over-current event occurred       |

| 2<br>OCIFP2 | Over-Current Interrupt Flag —<br>This flag asserts if an over-current condition is detected on EVDD1 (Section 2.4.4.3, "Over-Current Interrupt and Protection"").<br>Writing a logic "1" to the corresponding bit field clears the flag.<br>1 EVDD1 over-current event occurred<br>0 No EVDD1 over-current event occurred |

| 0<br>OCIFP0 | Over-Current Interrupt Flag —<br>This flag asserts if an over-current condition is detected on PP0 (Section 2.4.4.3, "Over-Current Interrupt and Protection"").<br>Writing a logic "1" to the corresponding bit field clears the flag.<br>1 PP0 over-current event occurred<br>0 No PP0 over-current event occurred       |

### Table 2-23. Port P Over-Current Interrupt Flag Register

Table 6-22 shows the effect for RWE and RW on the comparison conditions. These bits are ignored if INST is set, as matches based on instructions reaching the execution stage are data independent.

| RWE Bit | RW Bit | RW Signal | Comment                   |

|---------|--------|-----------|---------------------------|

| 0       | х      | 0         | RW not used in comparison |

| 0       | х      | 1         | RW not used in comparison |

| 1       | 0      | 0         | Write match               |

| 1       | 0      | 1         | No match                  |

| 1       | 1      | 0         | No match                  |

| 1       | 1      | 1         | Read match                |

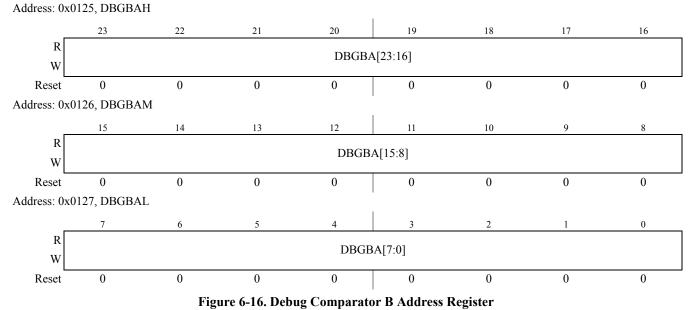

### 6.3.2.13 Debug Comparator B Address Register (DBGBAH, DBGBAM, DBGBAL)

Read: Anytime.

Write: If DBG not armed.

### Table 6-23. DBGBAH, DBGBAM, DBGBAL Field Descriptions

| Field                     | Description                                                                                                                                                                                                                                                                                                 |

|---------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 23–16<br>DBGBA<br>[23:16] | Comparator Address Bits [23:16]— These comparator address bits control whether the comparator compares the address bus bits [23:16] to a logic one or logic zero.<br>0 Compare corresponding address bit to a logic zero<br>1 Compare corresponding address bit to a logic one                              |

| 15–0<br>DBGBA<br>[15:0]   | <ul> <li>Comparator Address Bits[15:0]— These comparator address bits control whether the comparator compares the address bus bits [15:0] to a logic one or logic zero.</li> <li>0 Compare corresponding address bit to a logic zero</li> <li>1 Compare corresponding address bit to a logic one</li> </ul> |

#### MC9S12ZVC Family Reference Manual, Rev. 2.0

Chapter 9 Analog-to-Digital Converter (ADC12B\_LBA\_V1)

# 9.4.2 **Register Descriptions**

This section describes in address order all the ADC12B\_LBA registers and their individual bits.

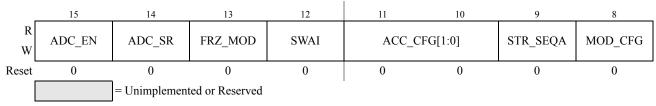

# 9.4.2.1 ADC Control Register 0 (ADCCTL\_0)

Module Base + 0x0000

Figure 9-4. ADC Control Register 0 (ADCCTL\_0)

Read: Anytime

Write:

- Bits ADC\_EN, ADC\_SR, FRZ\_MOD and SWAI writable anytime

- Bits MOD\_CFG, STR\_SEQA and ACC\_CFG[1:0] writable if bit ADC\_EN clear or bit SMOD\_ACC set

| Field         | Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

|---------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 15<br>ADC_EN  | <ul> <li>ADC Enable Bit — This bit enables the ADC (e.g. sample buffer amplifier etc.) and controls accessibility of ADC register bits. When this bit gets cleared any ongoing conversion sequence will be aborted and pending results or the result of current conversion gets discarded (not stored). The ADC cannot be re-enabled before any pending action or action in process is finished or aborted, which could take up to a maximum latency time of t<sub>DISABLE</sub> (see device reference manual for more details).</li> <li>Because internal components of the ADC are turned on/off with this bit, the ADC requires a recovery time period (t<sub>REC</sub>) after ADC is enabled until the first conversion can be launched via a trigger.</li> <li>0 ADC disabled.</li> <li>1 ADC enabled.</li> </ul>                                                                                                                                                       |

| 14<br>ADC_SR  | <ul> <li>ADC Soft-Reset — This bit causes an ADC Soft-Reset if set after a severe error occurred (see list of severe errors in Section 9.4.2.9, "ADC Error Interrupt Flag Register (ADCEIF) that causes the ADC to cease operation). It clears all overrun flags and error flags and forces the ADC state machine to its idle state. It also clears the Command Index Register, the Result Index Register, and the CSL_SEL and RVL_SEL bits (to be ready for a new control sequence to load new command and start execution again from top of selected CSL).</li> <li>A severe error occurs if an error flag is set which cause the ADC to cease operation. In order to make the ADC operational again an ADC Soft-Reset must be issued.</li> <li>Once this bit is set it can not be cleared by writing any value. It is cleared only by ADC hardware after the Soft-Reset has been executed.</li> <li>No ADC Soft-Reset issued.</li> <li>I Issue ADC Soft-Reset.</li> </ul> |

| 13<br>FRZ_MOD | Freeze Mode Configuration — This bit influences conversion flow during Freeze Mode.         0       ADC continues conversion in Freeze Mode.         1       ADC freezes the conversion at next conversion boundary at Freeze Mode entry.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

| 12<br>SWAI    | Wait Mode Configuration — This bit influences conversion flow during Wait Mode.         0       ADC continues conversion in Wait Mode.         1       ADC halts the conversion at next conversion boundary at Wait Mode entry.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

### Table 9-2. ADCCTL\_0 Field Descriptions

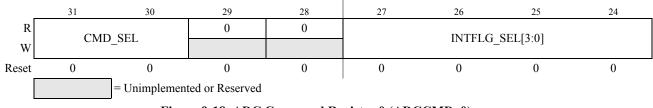

# 9.4.2.15 ADC Command Register 0 (ADCCMD\_0)

Module Base + 0x0014

Figure 9-18. ADC Command Register 0 (ADCCMD\_0)

Read: Anytime

Write: Only writable if bit SMOD ACC is set

(see also Section 9.4.2.2, "ADC Control Register 1 (ADCCTL\_1) bit SMOD\_ACC description for more details)

| Field                 | Description                                                                                                                                                                                                                                                     |

|-----------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 31-30<br>CMD_SEL[1:0] | <b>Conversion Command Select Bits</b> — These bits define the type of current conversion described in Table 9-20.                                                                                                                                               |

|                       | <b>Conversion Interrupt Flag Select Bits</b> — These bits define which interrupt flag is set in the ADCIFH/L register at the end of current conversion. The interrupt flags ADCIF[15:1] are selected via binary coded bits INTFLG_SEL[3:0]. See also Table 9-21 |

### NOTE

If bit SMOD\_ACC is set modifying this register must be done carefully - only when no conversion and conversion sequence is ongoing.

| CMD_SEL[1] | CMD_SEL[0] | Conversion Command Type Description                                                                                                                                   |

|------------|------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 0          | 0          | Normal Conversion                                                                                                                                                     |

| 0          | 1          | End Of Sequence<br>(Wait for Trigger to execute next sequence or for a Restart)                                                                                       |

| 1          | 0          | End Of List<br>(Automatic wrap to top of CSL<br>and Continue Conversion)                                                                                              |

| 1          | 1          | End Of List<br>(Wrap to top of CSL and:<br>- In "Restart Mode" wait for Restart Event followed by a Trigger<br>- In "Trigger Mode" wait for Trigger or Restart Event) |

#### Table 9-20. Conversion Command Type Select

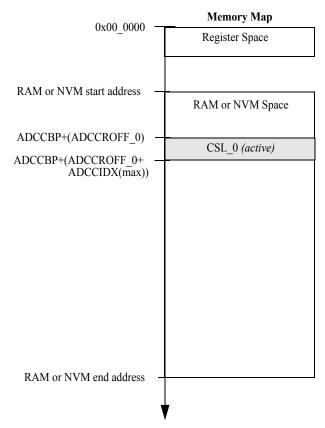

CSL\_SEL = 1'b0 (forced by CSL\_BMOD)

Note: Address register names in () are not absolute addresses instead they are a sample offset or sample index

#### Figure 9-32. Command Sequence List Schema in Single Buffer Mode

While the ADC is enabled, one CSL is active (indicated by bit CSL\_SEL) and the corresponding list should not be modified anymore. At the same time the alternative CSL can be modified to prepare the ADC for new conversion sequences in CSL double buffered mode. When the ADC is enabled, the command address registers (ADCCBP, ADCCROFF\_0/2, ADCCIDX) are read only and register ADCCIDX is under control of the ADC.

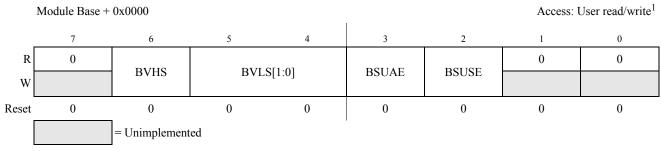

# **10.3.2.1 BATS Module Enable Register (BATE)**

#### Figure 10-3. BATS Module Enable Register (BATE)

Read: Anytime

1

Write: Anytime

| Field            | Description                                                                                                                                                                                                                                                                                                                                              |

|------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 6<br>BVHS        | <ul> <li>BATS Voltage High Select — This bit selects the trigger level for the Voltage Level High Condition (BVHC).</li> <li>0 Voltage level V<sub>HBI1</sub> is selected</li> <li>1 Voltage level V<sub>HBI2</sub> is selected</li> </ul>                                                                                                               |

| 5:4<br>BVLS[1:0] | <ul> <li>BATS Voltage Low Select — This bit selects the trigger level for the Voltage Level Low Condition (BVLC).</li> <li>00 Voltage level V<sub>LBI1</sub> is selected</li> <li>01 Voltage level V<sub>LBI2</sub> is selected</li> <li>10 Voltage level V<sub>LBI3</sub> is selected</li> <li>11 Voltage level V<sub>LBI4</sub> is selected</li> </ul> |

| 3<br>BSUAE       | <ul> <li>BATS VSUP ADC Connection Enable — This bit connects the VSUP pin through the resistor chain to ground and connects the ADC channel to the divided down voltage.</li> <li>0 ADC Channel is disconnected</li> <li>1 ADC Channel is connected</li> </ul>                                                                                           |

| 2<br>BSUSE       | <ul> <li>BATS VSUP Level Sense Enable — This bit connects the VSUP pin through the resistor chain to ground and enables the Voltage Level Sense features measuring BVLC and BVHC.</li> <li>0 Level Sense features disabled</li> <li>1 Level Sense features enabled</li> </ul>                                                                            |

### Table 10-2. BATE Field Description

### NOTE

When opening the resistors path to ground by changing BSUSE or BSUAE then for a time  $T_{EN\_UNC}$  + two bus cycles the measured value is invalid. This is to let internal nodes be charged to correct value. BVHIE, BVLIE might be cleared for this time period to avoid false interrupts.

- Clock prescaling.

- 16-bit counter.

- 16-bit pulse accumulator on channel 7.

# 11.1.2 Modes of Operation

Stop: Timer is off because clocks are stopped.

Freeze: Timer counter keeps on running, unless TSFRZ in TSCR1 is set to 1.

- Wait: Counters keeps on running, unless TSWAI in TSCR1 is set to 1.

- Normal: Timer counter keep on running, unless TEN in TSCR1 is cleared to 0.

# 11.1.3 Block Diagrams

#### Chapter 11 Timer Module (TIM16B8CV3) Block Description

#### Table 11-4. OC7M Field Descriptions

| Field            | Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

|------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 7:0<br>OC7M[7:0] | <ul> <li>Output Compare 7 Mask — A channel 7 event, which can be a counter overflow when TTOV[7] is set or a successful output compare on channel 7, overrides any channel 6:0 compares. For each OC7M bit that is set, the output compare action reflects the corresponding OC7D bit.</li> <li>0 The corresponding OC7Dx bit in the output compare 7 data register will not be transferred to the timer port on a channel 7 event, even if the corresponding pin is setup for output compare.</li> <li>1 The corresponding OC7Dx bit in the output compare 7 data register will be transferred to the timer port on a channel 7 event.</li> <li>Note: The corresponding channel must also be setup for output compare (IOSx = 1 and OCPDx = 0) for data to be transferred from the output compare 7 data register to the timer port.</li> </ul> |

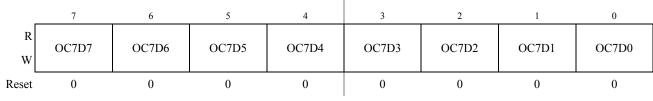

# 11.3.2.4 Output Compare 7 Data Register (OC7D)

1.

Module Base + 0x0003

Figure 11-9. Output Compare 7 Data Register (OC7D)

Read: Anytime

Write: Anytime

### Table 11-5. OC7D Field Descriptions

| Field     | Description                                                                                                                                                                    |

|-----------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 7:0       | Output Compare 7 Data — A channel 7 event, which can be a counter overflow when TTOV[7] is set or a successful                                                                 |

| OC7D[7:0] | output compare on channel 7, can cause bits in the output compare 7 data register to transfer to the timer port data register depending on the output compare 7 mask register. |

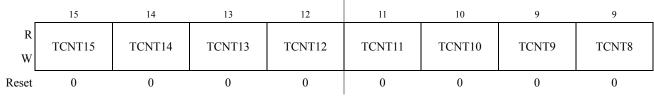

### 11.3.2.5 Timer Count Register (TCNT)

Module Base + 0x0004

Figure 11-10. Timer Count Register High (TCNTH)

MC9S12ZVC Family Reference Manual, Rev. 2.0

Chapter 13 Pulse-Width Modulator (S12PWM8B8CV2)

- The counter is written (counter resets to \$00)

- The channel is disabled

In this way, the output of the PWM will always be either the old waveform or the new waveform, not some variation in between. If the channel is not enabled, then writes to the period register will go directly to the latches as well as the buffer.

### NOTE

Reads of this register return the most recent value written. Reads do not necessarily return the value of the currently active period due to the double buffering scheme.

See Section 13.4.2.3, "PWM Period and Duty" for more information.

To calculate the output period, take the selected clock source period for the channel of interest (A, B, SA, or SB) and multiply it by the value in the period register for that channel:

• Left aligned output (CAEx = 0)

PWMx Period = Channel Clock Period \* PWMPERx

• Center Aligned Output (CAEx = 1)

PWMx Period = Channel Clock Period \* (2 \* PWMPERx)

For boundary case programming values, please refer to Section 13.4.2.8, "PWM Boundary Cases".

Module Base + 0x0014 = PWMPER0, 0x0015 = PWMPER1, 0x0016 = PWMPER2, 0x0017 = PWMPER3 Module Base + 0x0018 = PWMPER4, 0x0019 = PWMPER5, 0x001A = PWMPER6, 0x001B = PWMPER7

| _      | 7     | 6 | 5 | 4 | 3 | 2 | 1 | 0     |

|--------|-------|---|---|---|---|---|---|-------|

| R<br>W | Bit 7 | 6 | 5 | 4 | 3 | 2 | 1 | Bit 0 |

| Reset  | 1     | 1 | 1 | 1 | 1 | 1 | 1 | 1     |

### Figure 13-13. PWM Channel Period Registers (PWMPERx)

<sup>1</sup> This register is available only when the corresponding channel exists and is reserved if that channel does not exist. Writes to a reserved register have no functional effect. Reads from a reserved register return zeroes.

### Read: Anytime

Write: Anytime

# 13.3.2.12 PWM Channel Duty Registers (PWMDTYx)

There is a dedicated duty register for each channel. The value in this register determines the duty of the associated PWM channel. The duty value is compared to the counter and if it is equal to the counter value a match occurs and the output changes state.

The duty registers for each channel are double buffered so that if they change while the channel is enabled, the change will NOT take effect until one of the following occurs:

- The effective period ends

- The counter is written (counter resets to \$00)

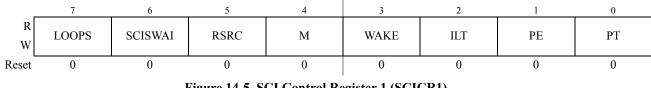

# 14.3.2.2 SCI Control Register 1 (SCICR1)

Module Base + 0x0002

Figure 14-5. SCI Control Register 1 (SCICR1)

Read: Anytime, if AMAP = 0.

Write: Anytime, if AMAP = 0.

### NOTE

This register is only visible in the memory map if AMAP = 0 (reset condition).

#### Table 14-3. SCICR1 Field Descriptions

| Field        | Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

|--------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 7<br>LOOPS   | <ul> <li>Loop Select Bit — LOOPS enables loop operation. In loop operation, the RXD pin is disconnected from the SCI and the transmitter output is internally connected to the receiver input. Both the transmitter and the receiver must be enabled to use the loop function.</li> <li>0 Normal operation enabled</li> <li>1 Loop operation enabled</li> <li>The receiver input is determined by the RSRC bit.</li> </ul>                                                                                                                                                                |

| 6<br>SCISWAI | <ul> <li>SCI Stop in Wait Mode Bit — SCISWAI disables the SCI in wait mode.</li> <li>0 SCI enabled in wait mode</li> <li>1 SCI disabled in wait mode</li> </ul>                                                                                                                                                                                                                                                                                                                                                                                                                           |

| 5<br>RSRC    | Receiver Source Bit — When LOOPS = 1, the RSRC bit determines the source for the receiver shift register input. See Table 14-4.         0       Receiver input internally connected to transmitter output         1       Receiver input connected externally to transmitter                                                                                                                                                                                                                                                                                                              |

| 4<br>M       | Data Format Mode Bit — MODE determines whether data characters are eight or nine bits long.         0       One start bit, eight data bits, one stop bit         1       One start bit, nine data bits, one stop bit                                                                                                                                                                                                                                                                                                                                                                      |

| 3<br>WAKE    | Wakeup Condition Bit — WAKE determines which condition wakes up the SCI: a logic 1 (address mark) in the most significant bit position of a received data character or an idle condition on the RXD pin.         0       Idle line wakeup         1       Address mark wakeup                                                                                                                                                                                                                                                                                                             |

| 2<br>ILT     | Idle Line Type Bit — ILT determines when the receiver starts counting logic 1s as idle character bits. The counting begins either after the start bit or after the stop bit. If the count begins after the start bit, then a string of logic 1s preceding the stop bit may cause false recognition of an idle character. Beginning the count after the stop bit avoids false idle character recognition, but requires properly synchronized transmissions.         0       Idle character bit count begins after start bit         1       Idle character bit count begins after stop bit |

#### Chapter 14 Serial Communication Interface (S12SCIV6)

| Field   | Description                                                                                                                                                                                                                                                                                                                                                                             |

|---------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 1<br>PE | <ul> <li>Parity Enable Bit — PE enables the parity function. When enabled, the parity function inserts a parity bit in the most significant bit position.</li> <li>0 Parity function disabled</li> <li>1 Parity function enabled</li> </ul>                                                                                                                                             |

| 0<br>PT | <ul> <li>Parity Type Bit — PT determines whether the SCI generates and checks for even parity or odd parity. With even parity, an even number of 1s clears the parity bit and an odd number of 1s sets the parity bit. With odd parity, an odd number of 1s clears the parity bit and an even number of 1s sets the parity bit.</li> <li>0 Even parity</li> <li>1 Odd parity</li> </ul> |

### Table 14-3. SCICR1 Field Descriptions (continued)

#### Table 14-4. Loop Functions

| LOOPS | RSRC | Function                                                                 |

|-------|------|--------------------------------------------------------------------------|

| 0     | х    | Normal operation                                                         |

| 1     | 0    | Loop mode with transmitter output internally connected to receiver input |

| 1     | 1    | Single-wire mode with TXD pin connected to receiver input                |

#### Chapter 16 Inter-Integrated Circuit (IICV3) Block Description

without generating STOP condition; generate an interrupt to CPU and set the IBAL to indicate that the attempt to engage the bus is failed. When considering these cases, the slave service routine should test the IBAL first and the software should clear the IBAL bit if it is set.

Chapter 18 Scalable Controller Area Network (S12MSCANV3)

| Register<br>Name   |        | Bit 7  | 6      | 5       | 4       | 3       | 2       | 1      | Bit 0  |

|--------------------|--------|--------|--------|---------|---------|---------|---------|--------|--------|

| 0x0000<br>CANCTL0  | R<br>W | RXFRM  | RXACT  | CSWAI   | SYNCH   | TIME    | WUPE    | SLPRQ  | INITRQ |

| 0x0001<br>CANCTL1  | R<br>W | CANE   | CLKSRC | LOOPB   | LISTEN  | BORM    | WUPM    | SLPAK  | INITAK |

| 0x0002<br>CANBTR0  | R<br>W | SJW1   | SJW0   | BRP5    | BRP4    | BRP3    | BRP2    | BRP1   | BRP0   |

| 0x0003<br>CANBTR1  | R<br>W | SAMP   | TSEG22 | TSEG21  | TSEG20  | TSEG13  | TSEG12  | TSEG11 | TSEG10 |

| 0x0004<br>CANRFLG  | R<br>W | WUPIF  | CSCIF  | RSTAT1  | RSTAT0  | TSTAT1  | TSTAT0  | OVRIF  | RXF    |

| 0x0005<br>CANRIER  | R<br>W | WUPIE  | CSCIE  | RSTATE1 | RSTATE0 | TSTATE1 | TSTATE0 | OVRIE  | RXFIE  |

| 0x0006<br>CANTFLG  | R<br>W | 0      | 0      | 0       | 0       | 0       | TXE2    | TXE1   | TXE0   |

| 0x0007<br>CANTIER  | R<br>W | 0      | 0      | 0       | 0       | 0       | TXEIE2  | TXEIE1 | TXEIE0 |

| 0x0008<br>CANTARQ  | R<br>W | 0      | 0      | 0       | 0       | 0       | ABTRQ2  | ABTRQ1 | ABTRQ0 |

| 0x0009<br>CANTAAK  | R<br>W | 0      | 0      | 0       | 0       | 0       | ABTAK2  | ABTAK1 | ABTAK0 |

| 0x000A<br>CANTBSEL | R<br>W | 0      | 0      | 0       | 0       | 0       | TX2     | TX1    | TX0    |

| 0x000B<br>CANIDAC  | R<br>W | 0      | 0      | IDAM1   | IDAM0   | 0       | IDHIT2  | IDHIT1 | IDHIT0 |

| 0x000C<br>Reserved | R<br>W | 0      | 0      | 0       | 0       | 0       | 0       | 0      | 0      |

| 0x000D<br>CANMISC  | R<br>W | 0      | 0      | 0       | 0       | 0       | 0       | 0      | BOHOLD |

| 0x000E<br>CANRXERR | R<br>W | RXERR7 | RXERR6 | RXERR5  | RXERR4  | RXERR3  | RXERR2  | RXERR1 | RXERR0 |

= Unimplemented or Reserved

Figure 18-3. MSCAN Register Summary

MC9S12ZVC Family Reference Manual, Rev. 2.0

#### Chapter 18 Scalable Controller Area Network (S12MSCANV3)

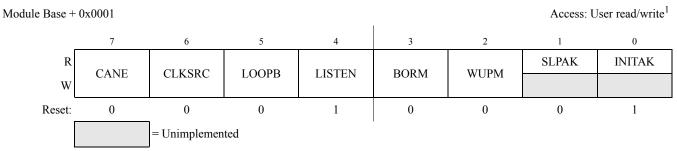

#### Figure 18-5. MSCAN Control Register 1 (CANCTL1)

<sup>1</sup> Read: Anytime

Write: Anytime in initialization mode (INITRQ = 1 and INITAK = 1), except CANE which is write once in normal and anytime in special system operation modes when the MSCAN is in initialization mode (INITRQ = 1 and INITAK = 1)

| Field       | Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |  |  |  |  |  |  |  |

|-------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|--|--|--|

| 7<br>CANE   | MSCAN Enable         0       MSCAN module is disabled         1       MSCAN module is enabled                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |  |  |  |  |  |  |  |

| 6<br>CLKSRC | MSCAN Clock Source — This bit defines the clock source for the MSCAN module (only for systems with a clock generation module; Section 18.4.3.2, "Clock System," and Section Figure 18-43., "MSCAN Clocking Scheme,").<br>0 MSCAN clock source is the oscillator clock<br>1 MSCAN clock source is the bus clock                                                                                                                                                                                                                                                                                                                                                                                                                                               |  |  |  |  |  |  |  |

| 5<br>LOOPB  | <ul> <li>Loopback Self Test Mode — When this bit is set, the MSCAN performs an internal loopback which can be used for self test operation. The bit stream output of the transmitter is fed back to the receiver internally. The RXCAN input is ignored and the TXCAN output goes to the recessive state (logic 1). The MSCAN behaves as it does normally when transmitting and treats its own transmitted message as a message received from a remote node. In this state, the MSCAN ignores the bit sent during the ACK slot in the CAN frame acknowledge field to ensure proper reception of its own message. Both transmit and receive interrupts are generated.</li> <li>0 Loopback self test disabled</li> <li>1 Loopback self test enabled</li> </ul> |  |  |  |  |  |  |  |

| 4<br>LISTEN | Listen Only Mode — This bit configures the MSCAN as a CAN bus monitor. When LISTEN is set, all valid CAN messages with matching ID are received, but no acknowledgement or error frames are sent out (see Section 18.4.4.4, "Listen-Only Mode"). In addition, the error counters are frozen. Listen only mode supports applications which require "hot plugging" or throughput analysis. The MSCAN is unable to transmit any messages when listen only mode is active.<br>0 Normal operation<br>1 Listen only mode activated                                                                                                                                                                                                                                 |  |  |  |  |  |  |  |

| 3<br>BORM   | Bus-Off Recovery Mode — This bit configures the bus-off state recovery mode of the MSCAN. Refer to Section 18.5.2,         "Bus-Off Recovery," for details.         0       Automatic bus-off recovery (see Bosch CAN 2.0A/B protocol specification)         1       Bus-off recovery upon user request                                                                                                                                                                                                                                                                                                                                                                                                                                                      |  |  |  |  |  |  |  |

| 2<br>WUPM   | Wake-Up Mode — If WUPE in CANCTL0 is enabled, this bit defines whether the integrated low-pass filter is applied to protect the MSCAN from spurious wake-up (see Section 18.4.5.5, "MSCAN Sleep Mode").         0       MSCAN wakes up on any dominant level on the CAN bus         1       MSCAN wakes up only in case of a dominant pulse on the CAN bus that has a length of T <sub>wup</sub>                                                                                                                                                                                                                                                                                                                                                             |  |  |  |  |  |  |  |

#### Table 18-3. CANCTL1 Register Field Descriptions

For microcontrollers without a clock and reset generator (CRG), CANCLK is driven from the crystal oscillator (oscillator clock).

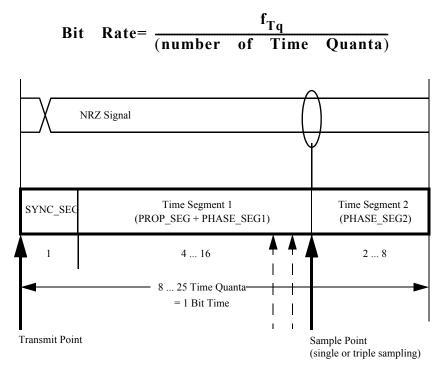

A programmable prescaler generates the time quanta (Tq) clock from CANCLK. A time quantum is the atomic unit of time handled by the MSCAN.

Eqn. 18-2

$$f_{Tq} = \frac{f_{CANCLK}}{(Prescaler value)}$$

A bit time is subdivided into three segments as described in the Bosch CAN 2.0A/B specification. (see Figure 18-44):

- SYNC\_SEG: This segment has a fixed length of one time quantum. Signal edges are expected to happen within this section.

- Time Segment 1: This segment includes the PROP\_SEG and the PHASE\_SEG1 of the CAN standard. It can be programmed by setting the parameter TSEG1 to consist of 4 to 16 time quanta.

- Time Segment 2: This segment represents the PHASE\_SEG2 of the CAN standard. It can be programmed by setting the TSEG2 parameter to be 2 to 8 time quanta long.

Eqn. 18-3

Figure 18-44. Segments within the Bit Time

# 22.4.7.4 Read Once Command

The Read Once command provides read access to a reserved 64 byte field (8 phrases) located in the nonvolatile information register of P-Flash. The Read Once field is programmed using the Program Once command described in <st-blue>Section 22.4.7.6 Program Once Command. The Read Once command must not be executed from the Flash block containing the Program Once reserved field to avoid code runaway.

| Register | FCCOB Parameters                         |  |  |  |  |  |  |

|----------|------------------------------------------|--|--|--|--|--|--|

| FCCOB0   | 0x04 Not Required                        |  |  |  |  |  |  |

| FCCOB1   | Read Once phrase index (0x0000 - 0x0007) |  |  |  |  |  |  |

| FCCOB2   | Read Once word 0 value                   |  |  |  |  |  |  |

| FCCOB3   | Read Once word 1 value                   |  |  |  |  |  |  |

| FCCOB4   | Read Once word 2 value                   |  |  |  |  |  |  |

| FCCOB5   | Read Once word 3 value                   |  |  |  |  |  |  |

Table 22-38. Read Once Command FCCOB Requirements

Upon clearing CCIF to launch the Read Once command, a Read Once phrase is fetched and stored in the FCCOB indexed register. The CCIF flag will set after the Read Once operation has completed. Valid phrase index values for the Read Once command range from 0x0000 to 0x0007. During execution of the Read Once command, any attempt to read addresses within P-Flash block will return invalid data.

| Register | Error Bit | Error Condition                                                         |

|----------|-----------|-------------------------------------------------------------------------|

|          |           | Set if CCOBIX[2:0] != 001 at command launch                             |

|          | ACCERR    | Set if command not available in current mode (see Table 22-28)          |

| FSTAT    |           | Set if an invalid phrase index is supplied                              |

| FSIAI    | FPVIOL    | None                                                                    |

|          | MGSTAT1   | Set if any errors have been encountered during the read                 |

|          | MGSTAT0   | Set if any non-correctable errors have been encountered during the read |

### 22.4.7.5 Program P-Flash Command

The Program P-Flash operation will program a previously erased phrase in the P-Flash memory using an embedded algorithm.

### CAUTION

A P-Flash phrase must be in the erased state before being programmed. Cumulative programming of bits within a Flash phrase is not allowed.

#### Chapter 22 192 KB Flash Module (S12ZFTMRZ192K2KV2)

in the Flash memory via the Memory Controller. If the keys presented in the Verify Backdoor Access Key command match the backdoor keys stored in the Flash memory, the SEC bits in the FSEC register (see Table 22-10) will be changed to unsecure the MCU. Key values of 0x0000 and 0xFFFF are not permitted as backdoor keys. While the Verify Backdoor Access Key command is active, P-Flash memory and EEPROM memory will not be available for read access and will return invalid data.

The user code stored in the P-Flash memory must have a method of receiving the backdoor keys from an external stimulus. This external stimulus would typically be through one of the on-chip serial ports.

If the KEYEN[1:0] bits are in the enabled state (see <st-blue>Section 22.3.2.2 Flash Security Register (FSEC)), the MCU can be unsecured by the backdoor key access sequence described below:

- 1. Follow the command sequence for the Verify Backdoor Access Key command as explained in <st-blue>Section 22.4.7.11 Verify Backdoor Access Key Command

- 2. If the Verify Backdoor Access Key command is successful, the MCU is unsecured and the SEC[1:0] bits in the FSEC register are forced to the unsecure state of 10

The Verify Backdoor Access Key command is monitored by the Memory Controller and an illegal key will prohibit future use of the Verify Backdoor Access Key command. A reset of the MCU is the only method to re-enable the Verify Backdoor Access Key command. The security as defined in the Flash security byte (0xFF\_FE0F) is not changed by using the Verify Backdoor Access Key command sequence. The backdoor keys stored in addresses 0xFF\_FE00-0xFF\_FE07 are unaffected by the Verify Backdoor Access Key command sequence. The verify Backdoor Access Key command sequence has no effect on the program and erase protections defined in the Flash protection register, FPROT.

After the backdoor keys have been correctly matched, the MCU will be unsecured. After the MCU is unsecured, the sector containing the Flash security byte can be erased and the Flash security byte can be reprogrammed to the unsecure state, if desired. In the unsecure state, the user has full control of the contents of the backdoor keys by programming addresses 0xFF\_FE00-0xFF\_FE07 in the Flash configuration field.

# 22.5.2 Unsecuring the MCU in Special Single Chip Mode using BDM

A secured MCU can be unsecured in special single chip mode using an automated procedure described in Section 22.4.7.7.1, "Erase All Pin", For a complete description about how to activate that procedure please look into the Reference Manual.

# 22.5.3 .Mode and Security Effects on Flash Command Availability

The availability of Flash module commands depends on the MCU operating mode and security state as shown in Table 22-28.

# 22.6 Initialization

On each system reset the flash module executes an initialization sequence which establishes initial values for the Flash Block Configuration Parameters, the FPROT and DFPROT protection registers, and the FOPT and FSEC registers. The initialization routine reverts to built-in default values that leave the module

### Figure L-3. 64 LQFP Exposed Pad Package

| Image: Control of the state of the sta |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | _                                                                                                                                                                                                                                                                                                                                                                                        | MECHANICAL D                                                                                                                                                                                                                                                  | UTLINES                                                                                                                                                   | DOCUMENT NO                                                                                          | 98ASA10763D                                                                    |

|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------|

| UNDERSEMBLY AND ADDRESSIONS       DID NOT SCALE THIS DRAWING       REV: B         NOTES:       1. DIMENSIONS ARE IN MILLIMETERS.         2. INTERPRET DIMENSIONS AND TOLERANCES PER ASME Y14.5M-1994.         AD DATUMS A, B AND D TO BE DETERMINED AT DATUM PLANE H.         AD DIMENSIONS TO BE DETERMINED AT SEATING PLANE C.         M DIMENSION DOES NOT INCLUDE DAMBAR PROTRUSION. ALLOWABLE DAMBAR PROTRUSION SHALL NOT CAUSE THE LEAD WIDTH TO EXCEED THE MAXIMUM DIMENSION BY MORE THAN 0.08 MM. DAMBAR CANNOT BE LOCATED ON THE LOW PRINCIPSION NOT ON MM.         M DIMENSIONS DO NOT INCLUDE MOULD PROTRUSION. ALLOWABLE PROTRUSION NOT MM.         M DIMENSIONS DO NOT INCLUDE MOULD PROTRUSION. ALLOWABLE PROTRUSION NOT MM.         M DIMENSIONS DO NOT INCLUDE MOULD PROTRUSION. ALLOWABLE PROTRUSION IS 0.25 MM PER SIDE. DIMENSIONS ARE MAXIMUM PLASTIC BODY SIZE DIMENSIONS INCLUDING MOLD MISMATCH.         M EXACT SHAPE OF EACH CORNER IS OPTIONAL.         M THESE DIMENSIONS APPLY TO THE FLAT SECTION OF THE LEAD BETWEEN 0.10 MM AND 0.25 MM FROM THE LEAD TP.         M HATCHED AREA TO BE KEEP OUT ZONE FOR PCB ROUTING.         ITILE:       LQFP, 10 X 10 X 1.4 PKG, 0.5 PITCH, 64LD, 5.0 PITCH, 64LD, 6.5 PITCH, 64LD, 7.5 PITCH, 64LD, 7                                                                                                                                                                                                                                                                                                                                                             | <b>*</b> *fi                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | semiconductor                                                                                                                                                                                                                                                                                                                                                                            |                                                                                                                                                                                                                                                               |                                                                                                                                                           | PAGE:                                                                                                | 1899                                                                           |

| <ul> <li>INTERPRET DIMENSIONS AND TOLERANCES PER ASME Y14.5M-1994.</li> <li>ATUMS A, B AND D TO BE DETERMINED AT DATUM PLANE H.</li> <li>DIMENSION DOES NOT INCLUDE DAMEAR THROTRUSION. ALLOWABLE DAMBAR PROTRUSION SHALL NOT CAUSE THE LEAD WIDTH TO EXCEED THE MAXIMUM DIMENSION BY MORE THAN 0.08 MM. DAMBAR CANNOT BE LOCATED ON THE LOWER RADIUS OR THE FOOT. MINIMUM SPACE BETWEEN PROTRUSION AND ADJACENT LEAD OR PROTRUSION 0.07 MM.</li> <li>DIMENSIONS DO NOT INCLUDE MOLD PROTRUSION. ALLOWABLE PROTRUSION IS 0.25 MM PER SIDE. DIMENSIONS ARE MAXIMUM PLASTIC BODY SIZE DIMENSIONS INCLUDING MOLD MISMATCH.</li> <li>EXACT SHAPE OF EACH CORNER IS OPTIONAL.</li> <li>EXACT SHAPE OF EACH CORNER IS OPTIONAL.</li> <li>THESE DIMENSIONS APPLY TO THE FLAT SECTION OF THE LEAD BETWEEN 0.10 MM AND 0.25 MM FROM THE LEAD TP.</li> <li>HATCHED AREA TO BE KEEP OUT ZONE FOR PCB ROUTING.</li> </ul>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | ELECTRONIC VERSIONS ARE<br>DIRECTLY FROM THE DOCUMEN                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | UNCONTROLLED EXCEPT WHEN ACCESSED<br>T CONTROL REPOSITORY, PRINTED VERSIONS                                                                                                                                                                                                                                                                                                              | DO NOT SCALE TH                                                                                                                                                                                                                                               | IS DRAWING                                                                                                                                                | REV∶                                                                                                 | В                                                                              |

| 0.5 PITCH, 64LD,<br>6.1 × 6.1 EXPOSED PAD                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | NOTES:<br>1. DIMEN<br>2. INTER<br>3. DATU<br>4. DIMEN<br>4. DIMEN<br>4. DIMEN<br>5. DIMEN | UNCONTRALED EXCEPT WHEN DOCESSED<br>AND STANFED CONTROLED COPY IN RED<br>ISIONS ARE IN MILLIN<br>PRET DIMENSIONS AI<br>MS A, B AND D TO<br>NSIONS TO BE DETER<br>USION DOES NOT INCL<br>L NOT CAUSE THE L<br>NOT CAUSE THE L<br>NOOS MM. DAMBAR<br>UM SPACE BETWEEN<br>NSIONS DO NOT INCL<br>SIDE. DIMENSIONS AI<br>ATCH.<br>T SHAPE OF EACH C<br>E DIMENSIONS APPLY<br>MM FROM THE LEAD | METERS.<br>ND TOLERANCES PER<br>BE DETERMINED AT<br>MINED AT SEATING R<br>LUDE DAMBAR PROT<br>LEAD WIDTH TO EXCE<br>CANNOT BE LOCATE<br>I PROTRUSION AND /<br>UDE MOLD PROTRUSION<br>RE MAXIMUM PLASTIC<br>CORNER IS OPTIONAL<br>( TO THE FLAT SECT<br>) TIP. | ASME Y14.5M<br>DATUM PLANE<br>PLANE C.<br>RUSION. ALLOV<br>ED THE MAXIM<br>D ON THE LOV<br>ADJACENT LEA<br>ON. ALLOWABL<br>C BODY SIZE D<br>ION OF THE LI | I-1994.<br>H.<br>MUM DIMENSION<br>WER RADIUS OR<br>D OR PROTRUSI<br>LE PROTRUSION<br>DIMENSIONS INCL | PROTRUSION<br>BY MORE<br>THE FOOT.<br>ON 0.07 MM.<br>IS 0.25 MM<br>LUDING MOLD |