Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

#### Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| 2014110                    |                                                                         |

|----------------------------|-------------------------------------------------------------------------|

| Product Status             | Active                                                                  |

| Core Processor             | S12Z                                                                    |

| Core Size                  | 16-Bit                                                                  |

| Speed                      | 32MHz                                                                   |

| Connectivity               | CANbus, I <sup>2</sup> C, SCI, SPI                                      |

| Peripherals                | DMA, POR, PWM, WDT                                                      |

| Number of I/O              | 28                                                                      |

| Program Memory Size        | 64KB (64K x 8)                                                          |

| Program Memory Type        | FLASH                                                                   |

| EEPROM Size                | 1K x 8                                                                  |

| RAM Size                   | 4K x 8                                                                  |

| Voltage - Supply (Vcc/Vdd) | 3.5V ~ 40V                                                              |

| Data Converters            | A/D 10x10b; D/A 1x8b                                                    |

| Oscillator Type            | Internal                                                                |

| Operating Temperature      | -40°C ~ 105°C (TA)                                                      |

| Mounting Type              | Surface Mount                                                           |

| Package / Case             | 48-LQFP                                                                 |

| Supplier Device Package    | 48-LQFP (7x7)                                                           |

| Purchase URL               | https://www.e-xfl.com/product-detail/nxp-semiconductors/s912zvc64f0vlfr |

|                            |                                                                         |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

# 3.1.1 Glossary

| Table 3-2. | Glossary Of Terms |

|------------|-------------------|

|            |                   |

| Term  | Definition                                                                                               |

|-------|----------------------------------------------------------------------------------------------------------|

| DBG   | On chip Debug Module                                                                                     |

| BDM   | Active Background Debug Mode                                                                             |

| СРИ   | S12Z CPU                                                                                                 |

| SSC   | Special Single Chip Mode (device operating mode                                                          |

| NSC   | Normal Single Chip Mode (device operating mode)                                                          |

| BDCSI | Background Debug Controller Serial Interface. This refers to the single pin BKGD serial interface.       |

| EWAIT | Optional S12 feature which allows external devices to delay external accesses until deassertion of EWAIT |

## **3.1.2** Features

The BDC includes these distinctive features:

- Single-wire communication with host development system

- SYNC command to determine communication rate

- Genuine non-intrusive handshake protocol

- Enhanced handshake protocol for error detection and stop mode recognition

- Active out of reset in special single chip mode

- Most commands not requiring active BDM, for minimal CPU intervention

- Full global memory map access without paging

- Simple flash mass erase capability

## **3.1.3** Modes of Operation

S12 devices feature power modes (run, wait, and stop) and operating modes (normal single chip, special single chip). Furthermore, the operation of the BDC is dependent on the device security status.

### 3.1.3.1 BDC Modes

The BDC features module specific modes, namely disabled, enabled and active. These modes are dependent on the device security and operating mode. In active BDM the CPU ceases execution, to allow BDC system access to all internal resources including CPU internal registers.

### **3.1.3.2** Security and Operating mode Dependency

In device run mode the BDC dependency is as follows

• Normal modes, unsecure device

General BDC operation available. The BDC is disabled out of reset.

# 3.4.3 Clock Source

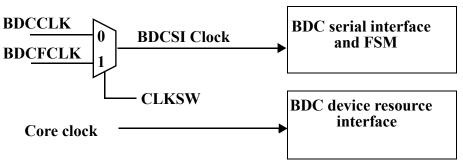

The BDC clock source can be mapped to a constant frequency clock source or a PLL based fast clock. The clock source for the BDC is selected by the CLKSW bit as shown in Figure 3-5. The BDC internal clock is named BDCSI clock. If BDCSI clock is mapped to the BDCCLK by CLKSW then the serial interface communication is not affected by bus/core clock frequency changes. If the BDC is mapped to BDCFCLK then the clock is connected to a PLL derived source at device level (typically bus clock), thus can be subject to frequency changes in application. Debugging through frequency changes requires SYNC pulses to re-synchronize. The sources of BDCCLK and BDCFCLK are specified at device level.

BDC accesses of internal device resources always use the device core clock. Thus if the ACK handshake protocol is not enabled, the clock frequency relationship must be taken into account by the host.

When changing the clock source via the CLKSW bit a minimum delay of 150 cycles at the initial clock speed must elapse before a SYNC can be sent. This guarantees that the start of the next BDC command uses the new clock for timing subsequent BDC communications.

Figure 3-5. Clock Switch

# **3.4.4 BDC Commands**

BDC commands can be classified into three types as shown in Table 3-7.

Table 3-7. BDC Command Types

| Command Type     | Secure Status         | BDC<br>Status          | CPU Status | Command Set                                                                                                                                  |

|------------------|-----------------------|------------------------|------------|----------------------------------------------------------------------------------------------------------------------------------------------|

| Always-available | Secure or<br>Unsecure | Enabled or<br>Disabled | _          | <ul> <li>Read/write access to BDCCSR</li> <li>Mass erase flash memory using ERASE_FLASH</li> <li>SYNC</li> <li>ACK enable/disable</li> </ul> |

## 6.4.3.1 Comparator Match Events

### 6.4.3.1.1 Opcode Address Comparator Match

The comparator is loaded with the address of the selected instruction and the comparator control register INST bit is set. When the opcode reaches the execution stage of the instruction queue a match occurs just before the instruction executes, allowing a breakpoint immediately before the instruction boundary. The comparator address register must contain the address of the first opcode byte for the match to occur. Opcode address matches are data independent thus the RWE and RW bits are ignored. CPU compares are disabled when BDM becomes active.

### 6.4.3.1.2 Data Access Comparator Match

Data access matches are generated when an access occurs at the address contained in the comparator address register. The match can be qualified by the access data and by the access type (read/write). The breakpoint occurs a maximum of 2 instructions after the access in the CPU flow. Note, if a COF occurs between access and breakpoint, the opcode address of the breakpoint can be elsewhere in the memory map.

Opcode fetches are not classed as data accesses. Thus data access matches are not possible on opcode fetches.

## 6.4.3.2 External Event

The DBGEEV input signal can force a state sequencer transition, independent of internal comparator matches. The DBGEEV is an input signal mapped directly to a device pin and configured by the EEVE field in DBGC1. The external events can change the state sequencer state.

If configured to change the state sequencer state, then the external match is mapped to DBGSCRx bits C3SC[1:0]. The DBGEFR bit EEVF is set when an external event occurs.

## 6.4.3.3 Setting The TRIG Bit

Independent of comparator matches it is possible to initiate a breakpoint by writing the TRIG bit in DBGC1 to a logic "1". This forces the state sequencer into the Final State. the transition to Final State is followed immediately by a transition to State0.

Breakpoints, if enabled, are issued on the transition to State0.

## 6.4.3.4 Event Priorities

If simultaneous events occur, the priority is resolved according to Table 6-31. Lower priority events are suppressed. It is thus possible to miss a lower priority event if it occurs simultaneously with an event of a higher priority. The event priorities dictate that in the case of simultaneous matches, the match on the higher comparator channel number (3,1,0) has priority.

If a write access to DBGC1 with the ARM bit position set occurs simultaneously to a hardware disarm from an internal event, then the ARM bit is cleared due to the hardware disarm.

Several examples of PLL divider settings are shown in Table 8-32. The following rules help to achieve optimum stability and shortest lock time:

- Use lowest possible  $f_{VCO}$  /  $f_{REF}$  ratio (SYNDIV value).

- Use highest possible REFCLK frequency  $f_{REF}$ .

| f <sub>osc</sub> | REFDIV[3:0] | f <sub>REF</sub> | REFFRQ[1:0] | SYNDIV[5:0] | f <sub>VCO</sub> | VCOFRQ[1:0] | POSTDIV[4:0] | f <sub>PLL</sub> | f <sub>bus</sub> |

|------------------|-------------|------------------|-------------|-------------|------------------|-------------|--------------|------------------|------------------|

| off              | \$00        | 1MHz             | 00          | \$18        | 50MHz            | 01          | \$03         | 12.5MHz          | 6.25MHz          |

| off              | \$00        | 1MHz             | 00          | \$18        | 50MHz            | 01          | \$00         | 50MHz            | 25MHz            |

| 4MHz             | \$00        | 4MHz             | 01          | \$05        | 48MHz            | 00          | \$00         | 48MHz            | 24MHz            |

### Table 8-32. Examples of PLL Divider Settings

The phase detector inside the PLL compares the feedback clock (FBCLK = VCOCLK/(SYNDIV+1)) with the reference clock (REFCLK = (IRC1M or OSCCLK)/(REFDIV+1)). Correction pulses are generated based on the phase difference between the two signals. The loop filter alters the DC voltage on the internal filter capacitor, based on the width and direction of the correction pulse which leads to a higher or lower VCO frequency.

The user must select the range of the REFCLK frequency (REFFRQ[1:0] bits) and the range of the VCOCLK frequency (VCOFRQ[1:0] bits) to ensure that the correct PLL loop bandwidth is set.

The lock detector compares the frequencies of the FBCLK and the REFCLK. Therefore the speed of the lock detector is directly proportional to the reference clock frequency. The circuit determines the lock condition based on this comparison. So e.g. a failure in the reference clock will cause the PLL not to lock.

If PLL LOCK interrupt requests are enabled, the software can wait for an interrupt request and for instance check the LOCK bit. If interrupt requests are disabled, software can poll the LOCK bit continuously (during PLL start-up) or at periodic intervals. In either case, only when the LOCK bit is set, the VCOCLK will have stabilized to the programmed frequency.

- The LOCK bit is a read-only indicator of the locked state of the PLL.

- The LOCK bit is set when the VCO frequency is within the tolerance,  $\Delta_{Lock}$ , and is cleared when the VCO frequency is out of the tolerance,  $\Delta_{unl}$ .

- Interrupt requests can occur if enabled (LOCKIE = 1) when the lock condition changes, toggling the LOCK bit.

In case of loss of reference clock (e.g. IRCCLK) the PLL will not lock or if already locked, then it will unlock. The frequency of the VCOCLK will be very low and will depend on the value of the VCOFRQ[1:0] bits.

Chapter 9 Analog-to-Digital Converter (ADC12B\_LBA\_V1)

# 9.2.1 Modes of Operation

### 9.2.1.1 Conversion Modes

This architecture provides single, multiple, or continuous conversion on a single channel or on multiple channels based on the Command Sequence List.

## 9.2.1.2 MCU Operating Modes

### • MCU Stop Mode

Before issuing an MCU Stop Mode request the ADC should be idle (no conversion or conversion sequence or Command Sequence List ongoing).

If a conversion, conversion sequence, or CSL is in progress when an MCU Stop Mode request is issued, a Sequence Abort Event occurs automatically and any ongoing conversion finish. After the Sequence Abort Event finishes, if the STR\_SEQA bit is set (STR\_SEQA=1), then the conversion result is stored and the corresponding flags are set. If the STR\_SEQA bit is cleared (STR\_SEQA=0), then the conversion result is not stored and the corresponding flags are not set. The microcontroller then enters MCU Stop Mode without SEQAD\_IF being set. Alternatively, the Sequence Abort Event can be issued by software before an MCU Stop Mode request. As soon as flag SEQAD\_IF is set the MCU Stop Mode request can be is issued. With the occurrence of the MCU Stop Mode Request until exit from Stop Mode all flow control signals (RSTA, SEQA, LDOK, TRIG) are cleared.

After exiting MCU Stop Mode, the following happens in the order given with expected event(s) depending on the conversion flow control mode:

- In ADC conversion flow control mode "Trigger Mode" a Restart Event is expected to simultaneously set bits TRIG and RSTA, causing the ADC to execute the Restart Event (CMD\_IDX and RVL\_IDX cleared) followed by the Trigger Event. The Restart Event can be generated automatically after exit from MCU Stop Mode if bit AUT\_RSTA is set.

- In ADC conversion flow control mode "Restart Mode", a Restart Event is expected to set bit RSTA only (ADC already aborted at MCU Stop Mode entry hence bit SEQA must not be set simultaneously) causing the ADC to execute the Restart Event (CDM\_IDX and RVL\_IDX cleared). The Restart Event can be generated automatically after exit from MCU Stop Mode if bit AUT\_RSTA is set.

- The RVL buffer select (RVL\_SEL) is not changed if a CSL is in process at MCU Stop Mode request. Hence the same buffer will be used after exit from Stop Mode that was used when the Stop Mode request occurred.

RVL SEL = 1'b0 (forced by bit RVL BMOD)

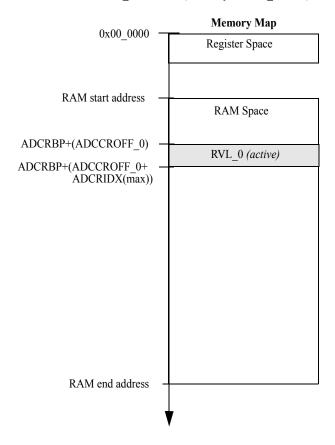

Note: Address register names in () are not absolute addresses instead they are a sample offset or sample index

#### Figure 9-34. Result Value List Schema in Single Buffer Mode

While ADC is enabled, one Result Value List is active (indicated by bit RVL\_SEL). The conversion Result Value List can be read anytime. When the ADC is enabled the conversion result address registers (ADCRBP, ADCCROFF\_0/1, ADCRIDX) are read only and register ADCRIDX is under control of the ADC.

A conversion result is always stored as 16bit entity in unsigned data representation. Left and right justification inside the entity is selected via the DJM control bit. Unused bits inside an entity are stored zero.

| Conversion Resolution<br>(SRES[1:0]) | Left Justified Result<br>(DJM = 1'b0) | Right Justified Result<br>(DJM = 1'b1) |

|--------------------------------------|---------------------------------------|----------------------------------------|

| 8 bit                                | {Result[7:0],8'b00000000}             | {8'b0000000,Result[7:0]}               |

| 10 bit                               | {Result[9:0],6'b000000}               | {6'b000000,Result[9:0]}                |

| 12 bit                               | {Result[11:0],4'b0000}                | {4'b0000,Result[11:0]}                 |

| Table 9-32. Conversion Result Justifica | tion Overview |

|-----------------------------------------|---------------|

|-----------------------------------------|---------------|

Chapter 9 Analog-to-Digital Converter (ADC12B\_LBA\_V1)

## 9.6 Resets

At reset the ADC12B\_LBA is disabled and in a power down state. The reset state of each individual bit is listed within Section 9.4.2, "Register Descriptions" which details the registers and their bit-fields.

## 9.7 Interrupts

The ADC supports three types of interrupts:

- Conversion Interrupt

- Sequence Abort Interrupt

- Error and Conversion Flow Control Issue Interrupt

Each of the interrupt types is associated with individual interrupt enable bits and interrupt flags.

## 9.7.1 ADC Conversion Interrupt

The ADC provides one conversion interrupt associated to 16 interrupt enable bits with dedicated interrupt flags. The 16 interrupt flags consist of:

- 15 conversion interrupt flags which can be associated to any conversion completion.

- One additional interrupt flag which is fixed to the "End Of List" conversion command type within the active CSL.

The association of the conversion number with the interrupt flag number is done in the conversion command.

## 9.7.2 ADC Sequence Abort Done Interrupt

The ADC provides one sequence abort done interrupt associated with the sequence abort request for conversion flow control. Hence, there is only one dedicated interrupt flag and interrupt enable bit for conversion sequence abort and it occurs when the sequence abort is done.

| Field      | Description                                                                                                                                                         |

|------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 1<br>BVHIF | <b>BATS Interrupt Flag High Detect</b> — The flag is set to 1 when BVHC status bit changes.                                                                         |

|            | <ol> <li>No change of the BVHC status bit since the last clearing of the flag.</li> <li>BVHC status bit has changed since the last clearing of the flag.</li> </ol> |

| 0<br>BVLIF | <b>BATS Interrupt Flag Low Detect</b> — The flag is set to 1 when BVLC status bit changes.                                                                          |

| D ( Dif    | <ol> <li>No change of the BVLC status bit since the last clearing of the flag.</li> <li>BVLC status bit has changed since the last clearing of the flag.</li> </ol> |

### Table 10-5. BATIF Register Field Descriptions

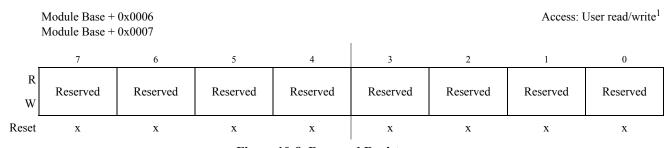

## 10.3.2.5 Reserved Register

Figure 10-8. Reserved Register

Read: Anytime Write: Only in special mode

### NOTE

These reserved registers are designed for factory test purposes only and are not intended for general user access. Writing to these registers when in special mode can alter the module's functionality.

# **10.4** Functional Description

## 10.4.1 General

The BATS module allows measuring the voltage on the VSUP pin. The voltage at the VSUP pin can be routed via an internal voltage divider to an internal Analog to Digital Converter Channel. Also the BATS module can be configured to generate a low and high voltage interrupt based on VSUP. The trigger level of the high and low interrupt are selectable.

## 10.4.2 Interrupts

This section describes the interrupt generated by the BATS module. The interrupt is only available in CPU run mode. Entering and exiting CPU stop mode has no effect on the interrupt flags.

To make sure the interrupt generation works properly the bus clock frequency must be higher than the Voltage Warning Low Pass Filter frequency ( $f_{VWLP}$  filter).

| PAMOD | PEDGE | Pin Action                                   |

|-------|-------|----------------------------------------------|

| 0     | 0     | Falling edge                                 |

| 0     | 1     | Rising edge                                  |

| 1     | 0     | Div. by 64 clock enabled with pin high level |

| 1     | 1     | Div. by 64 clock enabled with pin low level  |

| Table | 11-19. | Pin | Action |

|-------|--------|-----|--------|

|-------|--------|-----|--------|

### NOTE

If the timer is not active (TEN = 0 in TSCR), there is no divide-by-64 because the  $\div$ 64 clock is generated by the timer prescaler.

| Table 11-20. Timer Clock Selection | Table | 11-20. | Timer | Clock | Selection |

|------------------------------------|-------|--------|-------|-------|-----------|

|------------------------------------|-------|--------|-------|-------|-----------|

| CLK1 | CLK0 | Timer Clock                                      |

|------|------|--------------------------------------------------|

| 0    | 0    | Use timer prescaler clock as timer counter clock |

| 0    | 1    | Use PACLK as input to timer counter clock        |

| 1    | 0    | Use PACLK/256 as timer counter clock frequency   |

| 1    | 1    | Use PACLK/65536 as timer counter clock frequency |

For the description of PACLK please refer Figure 11-30.

If the pulse accumulator is disabled (PAEN = 0), the prescaler clock from the timer is always used as an input clock to the timer counter. The change from one selected clock to the other happens immediately after these bits are written.

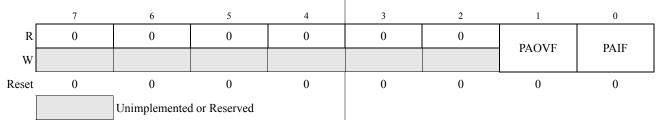

# 11.3.2.16 Pulse Accumulator Flag Register (PAFLG)

1.

Module Base + 0x0021

Figure 11-25. Pulse Accumulator Flag Register (PAFLG)

## Read: Anytime

Write: Anytime

When the TFFCA bit in the TSCR register is set, any access to the PACNT register will clear all the flags in the PAFLG register. Timer module or Pulse Accumulator must stay enabled (TEN=1 or PAEN=1) while clearing these bits.

Chapter 13 Pulse-Width Modulator (S12PWM8B8CV2)

- The counter is written (counter resets to \$00)

- The channel is disabled

In this way, the output of the PWM will always be either the old waveform or the new waveform, not some variation in between. If the channel is not enabled, then writes to the period register will go directly to the latches as well as the buffer.

### NOTE

Reads of this register return the most recent value written. Reads do not necessarily return the value of the currently active period due to the double buffering scheme.

See Section 13.4.2.3, "PWM Period and Duty" for more information.

To calculate the output period, take the selected clock source period for the channel of interest (A, B, SA, or SB) and multiply it by the value in the period register for that channel:

• Left aligned output (CAEx = 0)

PWMx Period = Channel Clock Period \* PWMPERx

• Center Aligned Output (CAEx = 1)

PWMx Period = Channel Clock Period \* (2 \* PWMPERx)

For boundary case programming values, please refer to Section 13.4.2.8, "PWM Boundary Cases".

Module Base + 0x0014 = PWMPER0, 0x0015 = PWMPER1, 0x0016 = PWMPER2, 0x0017 = PWMPER3 Module Base + 0x0018 = PWMPER4, 0x0019 = PWMPER5, 0x001A = PWMPER6, 0x001B = PWMPER7

| _      | 7     | 6 | 5 | 4 | 3 | 2 | 1 | 0     |

|--------|-------|---|---|---|---|---|---|-------|

| R<br>W | Bit 7 | 6 | 5 | 4 | 3 | 2 | 1 | Bit 0 |

| Reset  | 1     | 1 | 1 | 1 | 1 | 1 | 1 | 1     |

### Figure 13-13. PWM Channel Period Registers (PWMPERx)

<sup>1</sup> This register is available only when the corresponding channel exists and is reserved if that channel does not exist. Writes to a reserved register have no functional effect. Reads from a reserved register return zeroes.

### Read: Anytime

Write: Anytime

## 13.3.2.12 PWM Channel Duty Registers (PWMDTYx)

There is a dedicated duty register for each channel. The value in this register determines the duty of the associated PWM channel. The duty value is compared to the counter and if it is equal to the counter value a match occurs and the output changes state.

The duty registers for each channel are double buffered so that if they change while the channel is enabled, the change will NOT take effect until one of the following occurs:

- The effective period ends

- The counter is written (counter resets to \$00)

To determine the value of a data bit and to detect noise, recovery logic takes samples at RT8, RT9, and RT10. Table 14-18 summarizes the results of the data bit samples.

| RT8, RT9, and RT10 Samples | Data Bit Determination | Noise Flag |

|----------------------------|------------------------|------------|

| 000                        | 0                      | 0          |

| 001                        | 0                      | 1          |

| 010                        | 0                      | 1          |

| 011                        | 1                      | 1          |

| 100                        | 0                      | 1          |

| 101                        | 1                      | 1          |

| 110                        | 1                      | 1          |

| 111                        | 1                      | 0          |

Table 14-18. Data Bit Recovery

### NOTE

The RT8, RT9, and RT10 samples do not affect start bit verification. If any or all of the RT8, RT9, and RT10 start bit samples are logic 1s following a successful start bit verification, the noise flag (NF) is set and the receiver assumes that the bit is a start bit (logic 0).

To verify a stop bit and to detect noise, recovery logic takes samples at RT8, RT9, and RT10. Table 14-19 summarizes the results of the stop bit samples.

| RT8, RT9, and RT10 Samples | Framing Error Flag | Noise Flag |

|----------------------------|--------------------|------------|

| 000                        | 1                  | 0          |

| 001                        | 1                  | 1          |

| 010                        | 1                  | 1          |

| 011                        | 0                  | 1          |

| 100                        | 1                  | 1          |

| 101                        | 0                  | 1          |

| 110                        | 0                  | 1          |

| 111                        | 0                  | 0          |

Table 14-19. Stop Bit Recovery

## 14.5.3.1 Description of Interrupt Operation

The SCI only originates interrupt requests. The following is a description of how the SCI makes a request and how the MCU should acknowledge that request. The interrupt vector offset and interrupt number are chip dependent. The SCI only has a single interrupt line (SCI Interrupt Signal, active high operation) and all the following interrupts, when generated, are ORed together and issued through that port.

## 14.5.3.1.1 TDRE Description

The TDRE interrupt is set high by the SCI when the transmit shift register receives a byte from the SCI data register. A TDRE interrupt indicates that the transmit data register (SCIDRH/L) is empty and that a new byte can be written to the SCIDRH/L for transmission.Clear TDRE by reading SCI status register 1 with TDRE set and then writing to SCI data register low (SCIDRL).

## 14.5.3.1.2 TC Description

The TC interrupt is set by the SCI when a transmission has been completed. Transmission is completed when all bits including the stop bit (if transmitted) have been shifted out and no data is queued to be transmitted. No stop bit is transmitted when sending a break character and the TC flag is set (providing there is no more data queued for transmission) when the break character has been shifted out. A TC interrupt indicates that there is no transmission in progress. TC is set high when the TDRE flag is set and no data, preamble, or break character is being transmitted. When TC is set, the TXD pin becomes idle (logic 1). Clear TC by reading SCI status register 1 (SCISR1) with TC set and then writing to SCI data register low (SCIDRL).TC is cleared automatically when data, preamble, or break is queued and ready to be sent.

## 14.5.3.1.3 RDRF Description

The RDRF interrupt is set when the data in the receive shift register transfers to the SCI data register. A RDRF interrupt indicates that the received data has been transferred to the SCI data register and that the byte can now be read by the MCU. The RDRF interrupt is cleared by reading the SCI status register one (SCISR1) and then reading SCI data register low (SCIDRL).

## 14.5.3.1.4 OR Description

The OR interrupt is set when software fails to read the SCI data register before the receive shift register receives the next frame. The newly acquired data in the shift register will be lost in this case, but the data already in the SCI data registers is not affected. The OR interrupt is cleared by reading the SCI status register one (SCISR1) and then reading SCI data register low (SCIDRL).

## 14.5.3.1.5 IDLE Description

The IDLE interrupt is set when 10 consecutive logic 1s (if M = 0) or 11 consecutive logic 1s (if M = 1) appear on the receiver input. Once the IDLE is cleared, a valid frame must again set the RDRF flag before an idle condition can set the IDLE flag. Clear IDLE by reading SCI status register 1 (SCISR1) with IDLE set and then reading SCI data register low (SCIDRL).

### NOTE

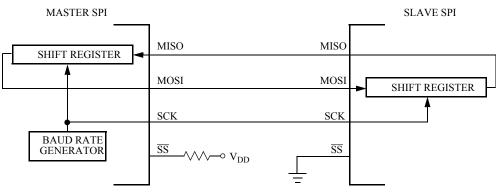

When peripherals with duplex capability are used, take care not to simultaneously enable two receivers whose serial outputs drive the same system slave's serial data output line.

As long as no more than one slave device drives the system slave's serial data output line, it is possible for several slaves to receive the same transmission from a master, although the master would not receive return information from all of the receiving slaves.

If the CPHA bit in SPI control register 1 is clear, odd numbered edges on the SCK input cause the data at the serial data input pin to be latched. Even numbered edges cause the value previously latched from the serial data input pin to shift into the LSB or MSB of the SPI shift register, depending on the LSBFE bit.

If the CPHA bit is set, even numbered edges on the SCK input cause the data at the serial data input pin to be latched. Odd numbered edges cause the value previously latched from the serial data input pin to shift into the LSB or MSB of the SPI shift register, depending on the LSBFE bit.

When CPHA is set, the first edge is used to get the first data bit onto the serial data output pin. When CPHA is clear and the  $\overline{SS}$  input is low (slave selected), the first bit of the SPI data is driven out of the serial data output pin. After the nth<sup>1</sup> shift, the transfer is considered complete and the received data is transferred into the SPI data register. To indicate transfer is complete, the SPIF flag in the SPI status register is set.

### NOTE

A change of the bits CPOL, CPHA, SSOE, LSBFE, MODFEN, SPC0, or BIDIROE with SPC0 set in slave mode will corrupt a transmission in progress and must be avoided.

## **15.4.3** Transmission Formats

During an SPI transmission, data is transmitted (shifted out serially) and received (shifted in serially) simultaneously. The serial clock (SCK) synchronizes shifting and sampling of the information on the two serial data lines. A slave select line allows selection of an individual slave SPI device; slave devices that are not selected do not interfere with SPI bus activities. Optionally, on a master SPI device, the slave select line can be used to indicate multiple-master bus contention.

Figure 15-11. Master/Slave Transfer Block Diagram

MC9S12ZVC Family Reference Manual, Rev. 2.0

<sup>1.</sup> n depends on the selected transfer width, please refer to Section 15.3.2.2, "SPI Control Register 2 (SPICR2)

Chapter 15 Serial Peripheral Interface (S12SPIV5)

### 15.4.7.5.2 SPIF

SPIF occurs when new data has been received and copied to the SPI data register. After SPIF is set, it does not clear until it is serviced. SPIF has an automatic clearing process, which is described in Section 15.3.2.4, "SPI Status Register (SPISR)".

### 15.4.7.5.3 SPTEF

SPTEF occurs when the SPI data register is ready to accept new data. After SPTEF is set, it does not clear until it is serviced. SPTEF has an automatic clearing process, which is described in Section 15.3.2.4, "SPI Status Register (SPISR)".

## 16.4.1.5 Repeated START Signal

As shown in Figure 16-10, a repeated START signal is a START signal generated without first generating a STOP signal to terminate the communication. This is used by the master to communicate with another slave or with the same slave in different mode (transmit/receive mode) without releasing the bus.

## 16.4.1.6 Arbitration Procedure

The Inter-IC bus is a true multi-master bus that allows more than one master to be connected on it. If two or more masters try to control the bus at the same time, a clock synchronization procedure determines the bus clock, for which the low period is equal to the longest clock low period and the high is equal to the shortest one among the masters. The relative priority of the contending masters is determined by a data arbitration procedure, a bus master loses arbitration if it transmits logic 1 while another master transmits logic 0. The losing masters immediately switch over to slave receive mode and stop driving SDA output. In this case the transition from master to slave mode does not generate a STOP condition. Meanwhile, a status bit is set by hardware to indicate loss of arbitration.

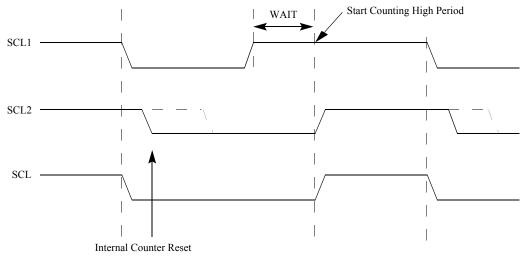

## 16.4.1.7 Clock Synchronization

Because wire-AND logic is performed on SCL line, a high-to-low transition on SCL line affects all the devices connected on the bus. The devices start counting their low period and as soon as a device's clock has gone low, it holds the SCL line low until the clock high state is reached. However, the change of low to high in this device clock may not change the state of the SCL line if another device clock is within its low period. Therefore, synchronized clock SCL is held low by the device with the longest low period. Devices with shorter low periods enter a high wait state during this time (see Figure 16-11). When all devices concerned have counted off their low period, the synchronized clock SCL line is released and pulled high. There is then no difference between the device clocks and the state of the SCL line and all the devices start counting their high periods. The first device to complete its high period pulls the SCL line low again.

Figure 16-12. IIC-Bus Clock Synchronization

#### Chapter 16 Inter-Integrated Circuit (IICV3) Block Description

If a master receiver wants to terminate a data transfer, it must inform the slave transmitter by not acknowledging the last byte of data which can be done by setting the transmit acknowledge bit (TXAK) before reading the 2nd last byte of data. Before reading the last byte of data, a STOP signal must be generated first. The following is an example showing how a STOP signal is generated by a master receiver.

| MASR   | DEC  | RXCNT      | ;DECREASE THE RXCNT               |

|--------|------|------------|-----------------------------------|

|        | BEQ  | ENMASR     | ;LAST BYTE TO BE READ             |

|        | MOVB | RXCNT,D1   | CHECK SECOND LAST BYTE            |

|        | DEC  | D1         | ;TO BE READ                       |

|        | BNE  | NXMAR      | ;NOT LAST OR SECOND LAST          |

| LAMAR  | BSET | IBCR,#\$08 | ;SECOND LAST, DISABLE ACK         |

|        |      |            | ;TRANSMITTING                     |

|        | BRA  | NXMAR      |                                   |

| ENMASR | BCLR | IBCR,#\$20 | ;LAST ONE, GENERATE 'STOP' SIGNAL |

| NXMAR  | MOVB | IBDR,RXBUF | ;READ DATA AND STORE              |

|        | RTI  |            |                                   |

### 16.7.1.5 Generation of Repeated START

At the end of data transfer, if the master continues to want to communicate on the bus, it can generate another START signal followed by another slave address without first generating a STOP signal. A program example is as shown.

| RESTART | BSET | IBCR,#\$04    | ;ANOTHER START (RESTART)             |

|---------|------|---------------|--------------------------------------|

|         | MOVB | CALLING, IBDR | ;TRANSMIT THE CALLING ADDRESS;D0=R/W |

### 16.7.1.6 Slave Mode

In the slave interrupt service routine, the module addressed as slave bit (IAAS) should be tested to check if a calling of its own address has just been received. If IAAS is set, software should set the transmit/receive mode select bit (Tx/Rx bit of IBCR) according to the R/W command bit (SRW). Writing to the IBCR clears the IAAS automatically. Note that the only time IAAS is read as set is from the interrupt at the end of the address cycle where an address match occurred, interrupts resulting from subsequent data transfers will have IAAS cleared. A data transfer may now be initiated by writing information to IBDR, for slave transmits, or dummy reading from IBDR, in slave receive mode. The slave will drive SCL low in-between byte transfers, SCL is released when the IBDR is accessed in the required mode.

In slave transmitter routine, the received acknowledge bit (RXAK) must be tested before transmitting the next byte of data. Setting RXAK means an 'end of data' signal from the master receiver, after which it must be switched from transmitter mode to receiver mode by software. A dummy read then releases the SCL line so that the master can generate a STOP signal.

## 16.7.1.7 Arbitration Lost

If several masters try to engage the bus simultaneously, only one master wins and the others lose arbitration. The devices which lost arbitration are immediately switched to slave receive mode by the hardware. Their data output to the SDA line is stopped, but SCL continues to be generated until the end of the byte during which arbitration was lost. An interrupt occurs at the falling edge of the ninth clock of this transfer with IBAL=1 and MS/SL=0. If one master attempts to start transmission while the bus is being engaged by another master, the hardware will inhibit the transmission; switch the MS/SL bit from 1 to 0

#### Chapter 17 CAN Physical Layer (S12CANPHYV3)

| Field       | Description                                                                                                                                                                                                                                  |

|-------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 4<br>CPVFIE | <b>CAN Physical Layer Voltage-Failure Interrupt Enable</b><br>If enabled, the CAN Physical Layer generates an interrupt if any of the CAN Physical Layer voltage failure interrupt flags assert.                                             |

|             | 0 Voltage failure interrupt is disabled<br>1 Voltage failure interrupt is enabled                                                                                                                                                            |

| 3<br>CPDTIE | <ul> <li>CPTXD-Dominant Timeout Interrupt Enable</li> <li>If enabled, the CAN Physical Layer generates an interrupt if the CPTXD-dominant timeout interrupt flag asserts.</li> <li>0 CPTXD-dominant timeout interrupt is disabled</li> </ul> |

|             | 1 CPTXD-dominant timeout interrupt is enabled                                                                                                                                                                                                |

| 0<br>CPOCIE | <b>CAN Physical Layer Over-current Interrupt Enable</b><br>If enabled, the CAN Physical Layer generates an interrupt if any of the CAN Physical Layer over-current interrupt flags assert.                                                   |

|             | 0 Over-current interrupt is disabled<br>1 Over-current interrupt is enabled                                                                                                                                                                  |

### Table 17-7. CPIE Register Field Descriptions

# 17.4.2.8 CAN Physical Layer Interrupt Flag Register (CPIF)

| Module Ba | Module Base + 0x0007 Access: User read/write <sup>1</sup> |        |        |        |        |   |        |        |  |  |

|-----------|-----------------------------------------------------------|--------|--------|--------|--------|---|--------|--------|--|--|

|           | 7                                                         | 6      | 5      | 4      | 3      | 2 | 1      | 0      |  |  |

| R<br>W    | CHVHIF                                                    | CHVLIF | CLVHIF | CLVLIF | CPDTIF | 0 | CHOCIF | CLOCIF |  |  |

| Reset     | 0                                                         | 0      | 0      | 0      | 0      | 0 | 0      | 0      |  |  |

Figure 17-9. CAN Physical Layer Interrupt Flag Register (CPIF)

<sup>1</sup> Read: Anytime

Write: Anytime, write 1 to clear

If any of the flags is asserted an error interrupt is pending if enabled. A flag can be cleared by writing a logic level 1 to the corresponding bit location. Writing a 0 has no effect.

### Table 17-8. CPIF Register Field Descriptions

| Field       | Description                                                                                                                                                                                                                            |

|-------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 7<br>CHVHIF | <ul> <li>CANH Voltage Failure High Interrupt Flag</li> <li>This flag is set to 1 when the CPCHVH bit in the CAN Physical Layer Status Register (CPSR) changes.</li> <li>0 No change in CPCHVH</li> <li>1 CPCHVH has changed</li> </ul> |

| 6<br>CHVLIF | <ul> <li>CANH Voltage Failure Low Interrupt Flag</li> <li>This flag is set to 1 when the CPCHVL bit in the CAN Physical Layer Status Register (CPSR) changes.</li> <li>0 No change in CPCHVL</li> <li>1 CPCHVL has changed</li> </ul>  |

MC9S12ZVC Family Reference Manual, Rev. 2.0

| Syntax         | Description                                                                                                                                                        |

|----------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| SYNC_SEG       | System expects transitions to occur on the CAN bus during this period.                                                                                             |

| Transmit Point | A node in transmit mode transfers a new value to the CAN bus at this point.                                                                                        |

| Sample Point   | A node in receive mode samples the CAN bus at this point. If the three samples per bit option is selected, then this point marks the position of the third sample. |

The synchronization jump width (see the Bosch CAN 2.0A/B specification for details) can be programmed in a range of 1 to 4 time quanta by setting the SJW parameter.

The SYNC\_SEG, TSEG1, TSEG2, and SJW parameters are set by programming the MSCAN bus timing registers (CANBTR0, CANBTR1) (see Section 18.3.2.3, "MSCAN Bus Timing Register 0 (CANBTR0)" and Section 18.3.2.4, "MSCAN Bus Timing Register 1 (CANBTR1)").

Table 18-36 gives an overview of the Bosch CAN 2.0A/B specification compliant segment settings and the related parameter values.

### NOTE

It is the user's responsibility to ensure the bit time settings are in compliance with the CAN standard.

| Time Segment 1 | TSEG1 | Time Segment 2 | TSEG2 | Synchronization<br>Jump Width | SJW |

|----------------|-------|----------------|-------|-------------------------------|-----|

| 510            | 49    | 2              | 1     | 12                            | 01  |

| 4 11           | 310   | 3              | 2     | 13                            | 02  |

| 512            | 411   | 4              | 3     | 14                            | 03  |

| 613            | 512   | 5              | 4     | 14                            | 03  |

| 714            | 613   | 6              | 5     | 14                            | 03  |

| 815            | 714   | 7              | 6     | 14                            | 03  |

| 916            | 815   | 8              | 7     | 14                            | 03  |

Table 18-36. Bosch CAN 2.0A/B Compliant Bit Time Segment Settings

## **18.4.4** Modes of Operation

### **18.4.4.1** Normal System Operating Modes

The MSCAN module behaves as described within this specification in all normal system operating modes. Write restrictions exist for some registers.

# N.8 0x0400-0x042F TIM1

| Register<br>Name             |        | Bit 7  | 6      | 5      | 4      | 3         | 2         | 1         | Bit 0     |

|------------------------------|--------|--------|--------|--------|--------|-----------|-----------|-----------|-----------|

| 0x0400<br>TIOS               | R<br>W |        |        |        |        | IOS3      | IOS2      | IOS1      | IOS0      |

| 0x0401<br>CFORC              | R<br>W | 0      | 0      | 0      | 0      | 0<br>FOC3 | 0<br>FOC2 | 0<br>FOC1 | 0<br>FOC0 |

| 0x0402<br>Reserved<br>0x0403 | R<br>R |        |        |        |        | FOCS      | F0C2      | FOCI      | FOCO      |

| Reserved                     | К      |        |        |        |        |           |           |           |           |

| 0x0404<br>TCNTH              | R<br>W | TCNT15 | TCNT14 | TCNT13 | TCNT12 | TCNT11    | TCNT10    | TCNT9     | TCNT8     |

| 0x0405<br>TCNTL              | R<br>W | TCNT7  | TCNT6  | TCNT5  | TCNT4  | TCNT3     | TCNT2     | TCNT1     | TCNT0     |

| 0x0406<br>TSCR1              | R<br>W | TEN    | TSWAI  | TSFRZ  | TFFCA  | PRNT      | 0         | 0         | 0         |

| 0x0407<br>TTOV               | R<br>W |        |        |        |        | TOV3      | TOV2      | TOV1      | TOV0      |

| 0x0408<br>TCTL1              | R<br>W |        |        |        |        |           |           |           |           |

| 0x0409<br>TCTL2              | R<br>W | OM3    | OL3    | OM2    | OL2    | OM1       | OL1       | OM0       | OL0       |

| 0x040A<br>TCTL3              | R<br>W |        |        |        |        |           |           |           |           |

| 0x040B<br>TCTL4              | R<br>W | EDG3B  | EDG3A  | EDG2B  | EDG2A  | EDG1B     | EDG1A     | EDG0B     | EDG0A     |

| 0x040C<br>TIE                | R<br>W |        |        |        |        | C3I       | C2I       | C1I       | C0I       |

| 0x040D<br>TSCR2              | R<br>W | TOI    | 0      | 0      | 0      |           | PR2       | PR1       | PR0       |

| 0x040E<br>TFLG1              | R<br>W |        |        |        |        | C3F       | C2F       | C1F       | C0F       |

| 0x040F<br>TFLG2              | R<br>W | TOF    | 0      | 0      | 0      | 0         | 0         | 0         | 0         |

| 0x0410-0x041F                | R<br>W | Bit 15 | Bit 14 | Bit 13 | Bit 12 | Bit 11    | Bit 10    | Bit 9     | Bit 8     |

| TCxH–TCxL <sup>1</sup>       | R<br>W | Bit 7  | Bit 6  | Bit 5  | Bit 4  | Bit 3     | Bit 2     | Bit 1     | Bit 0     |

| 0x0420–0x042B<br>Reserved    | R<br>W |        |        |        |        |           |           |           |           |

| 0x042C<br>OCPD               | R<br>W |        |        |        |        | OCPD3     | OCPD2     | OCPD1     | OCPD0     |

| 0x042D<br>Reserved           | R      |        |        |        |        |           |           |           |           |

| 0x042E<br>PTPSR              | R<br>W | PTPS7  | PTPS6  | PTPS5  | PTPS4  | PTPS3     | PTPS2     | PTPS1     | PTPS0     |

MC9S12ZVC Family Reference Manual, Rev. 2.0

### How to Reach Us:

**Home Page:**

nxp.com

Web Support

nxp.com/support

Information in this document is provided solely to enable system and software implementers to use NXP products. There are no express or implied copyright licenses granted hereunder to design or fabricate any integrated circuits based on the information in this document. NXP reserves the right to make changes without further notice to any products herein.

NXP makes no warranty, representation, or guarantee regarding the suitability of its products for any particular purpose, nor does NXP assume any liability arising out of the application or use of any product or circuit, and specifically disclaims any and all liability, including without limitation consequential or incidental damages. "Typical" parameters that may be provided in NXP data sheets and/or specifications can and do vary in different applications, and actual performance may vary over time. All operating parameters, including "typicals," must be validated for each customer application by customer's technical experts. NXP does not convey any license under its patent rights nor the rights of others. NXP sells products pursuant to standard terms and conditions of sale, which can be found at the following address: nxp.com/SalesTermsandConditions.

NXP, the NXP logo, NXP SECURE CONNECTIONS FOR A SMARTER WORLD, COOLFLUX, EMBRACE, GREENCHIP, HITAG, I2C BUS, ICODE, JCOP, LIFE VIBES, MIFARE, MIFARE CLASSIC, MIFARE DESFire, MIFARE PLUS, MIFARE FLEX, MANTIS, MIFARE ULTRALIGHT, MIFARE4MOBILE, MIGLO, NTAG, ROADLINK, SMARTLX, SMARTMX, STARPLUG, TOPFET, TRENCHMOS, UCODE, Freescale, the Freescale logo, AltiVec, C-5, CodeTEST, CodeWarrior, ColdFire, ColdFire+, C-Ware, the Energy Efficient Solutions logo, Kinetis, Layerscape, MagniV, mobileGT, PEG, PowerQUICC, Processor Expert, QorIQ, QorIQ Qonverge, Ready Play, SafeAssure, the SafeAssure logo, StarCore, Symphony, VortiQa, Vybrid, Airfast, BeeKit, BeeStack, CoreNet, Flexis, MXC, Platform in a Package, QUICC Engine, SMARTMOS, Tower, TurboLink, and UMEMS are trademarks of NXP B.V. All other product or service names are the property of their respective owners. ARM, AMBA, ARM Powered, Artisan, Cortex, Jazelle, Keil, SecurCore, Thumb, TrustZone, and µVision are registered trademarks of ARM Limited (or its subsidiaries) in the EU and/or elsewhere. ARM7, ARM9, ARM11, big.LITTLE, CoreLink, CoreSight, DesignStart, Mali, mbed, NEON, POP, Sensinode, Socrates, ULINK and Versatile are trademarks of ARM Limited (or its subsidiaries) in the EU and/or elsewhere. All rights reserved. Oracle and Java are registered trademarks of Oracle and/or its affiliates. The Power Architecture and Power.org word marks and the Power and Power.org logos and related marks are trademarks and service marks licensed by Power.org. © 2018 NXP B.V.