Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

-XF

| Product Status             | Active                                                                     |

|----------------------------|----------------------------------------------------------------------------|

| Core Processor             | PIC                                                                        |

| Core Size                  | 8-Bit                                                                      |

| Speed                      | 64MHz                                                                      |

| Connectivity               | I <sup>2</sup> C, LINbus, SPI, UART/USART                                  |

| Peripherals                | Brown-out Detect/Reset, DMA, HLVD, POR, PWM, WDT                           |

| Number of I/O              | 25                                                                         |

| Program Memory Size        | 64KB (32K x 16)                                                            |

| Program Memory Type        | FLASH                                                                      |

| EEPROM Size                | 1K x 8                                                                     |

| RAM Size                   | 4K x 8                                                                     |

| Voltage - Supply (Vcc/Vdd) | 2.3V ~ 5.5V                                                                |

| Data Converters            | A/D 24x12b; D/A 1x5b                                                       |

| Oscillator Type            | Internal                                                                   |

| Operating Temperature      | -40°C ~ 125°C (TA)                                                         |

| Mounting Type              | Surface Mount                                                              |

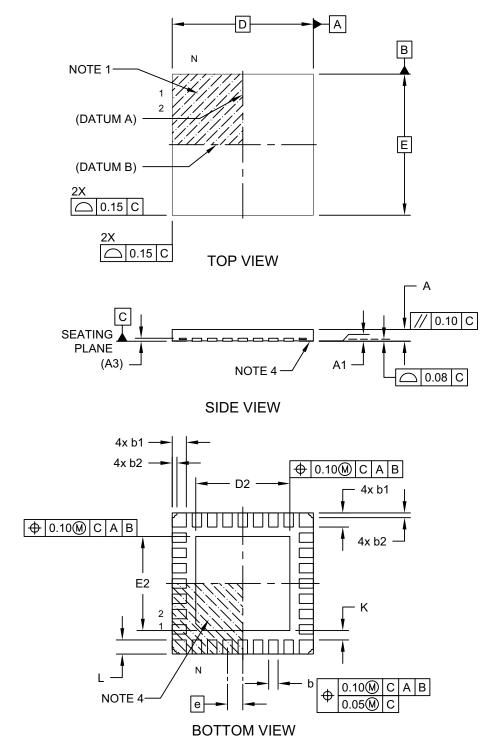

| Package / Case             | 28-VQFN Exposed Pad                                                        |

| Supplier Device Package    | 28-QFN (6x6)                                                               |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/pic18f26k42-e-ml |

|                            |                                                                            |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

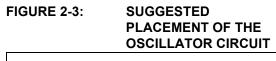

#### 2.5 External Oscillator Pins

Many microcontrollers have options for at least two oscillators: a high-frequency primary oscillator and a low-frequency secondary oscillator (refer to Section 7.0 "Oscillator Module (with Fail-Safe Clock Monitor)" for details).

The oscillator circuit should be placed on the same side of the board as the device. Place the oscillator circuit close to the respective oscillator pins with no more than 0.5 inch (12 mm) between the circuit components and the pins. The load capacitors should be placed next to the oscillator itself, on the same side of the board.

Use a grounded copper pour around the oscillator circuit to isolate it from surrounding circuits. The grounded copper pour should be routed directly to the MCU ground. Do not run any signal traces or power traces inside the ground pour. Also, if using a two-sided board, avoid any traces on the other side of the board where the crystal is placed.

Layout suggestions are shown in Figure 2-3. In-line packages may be handled with a single-sided layout that completely encompasses the oscillator pins. With fine-pitch packages, it is not always possible to completely surround the pins and components. A suitable solution is to tie the broken guard sections to a mirrored ground layer. In all cases, the guard trace(s) must be returned to ground.

In planning the application's routing and I/O assignments, ensure that adjacent port pins, and other signals in close proximity to the oscillator, are benign (i.e., free of high frequencies, short rise and fall times, and other similar noise).

For additional information and design guidance on oscillator circuits, refer to these Microchip application notes, available at the corporate website (www.microchip.com):

- AN826, "Crystal Oscillator Basics and Crystal Selection for rfPIC<sup>™</sup> and PICmicro<sup>®</sup> Devices"

- AN849, "Basic PICmicro<sup>®</sup> Oscillator Design"

- AN943, "Practical PICmicro<sup>®</sup> Oscillator Analysis and Design"

- AN949, "Making Your Oscillator Work"

#### 2.6 Unused I/Os

Unused I/O pins should be configured as outputs and driven to a logic low state. Alternatively, connect a 1 k $\Omega$  to 10 k $\Omega$  resistor to Vss on unused pins and drive the output to logic low.

#### 3.1 System Arbitration

The System Arbiter resolves memory access between the System Level Selections (i.e., Main, Interrupt Service Routine) and Peripheral Selection (i.e., DMA and Scanner) based on user-assigned priorities. Each of the system level and peripheral selections has its own priority selection registers. Memory access priority is resolved using the number written to the corresponding Priority registers, 0 being the highest priority and 4 the lowest. The default priorities are listed in Table 3-1.

In case the user wants to change priorities, ensure each Priority register is written with a unique value from 0 to 4.

| Sele         | Priority register<br>Reset value |   |

|--------------|----------------------------------|---|

| System Level | ISR                              | 0 |

|              | MAIN                             | 1 |

| Peripheral   | DMA1                             | 2 |

|              | DMA2                             | 3 |

|              | SCANNER                          | 4 |

TABLE 3-1: DEFAULT PRIORITIES

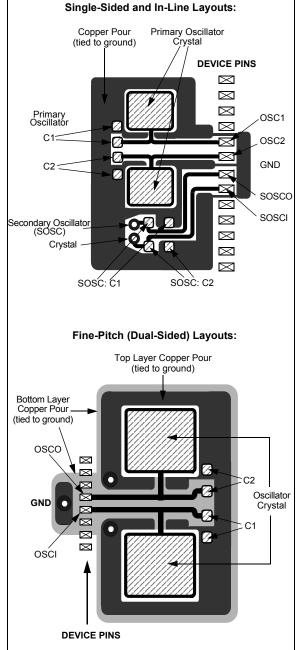

## 6.4 Low-Power Brown-out Reset (LPBOR)

The Low-Power Brown-out Reset (LPBOR) provides an additional BOR circuit for low power operation. Refer to Figure 6-2 to see how the BOR interacts with other modules.

The LPBOR is used to monitor the external VDD pin. When too low of a voltage is detected, the device is held in Reset.

#### 6.4.1 ENABLING LPBOR

The LPBOR is controlled by the LPBOREN bit of Configuration Word 2L. When the device is erased, the LPBOR module defaults to disabled.

#### 6.4.1.1 LPBOR Module Output

The output of the LPBOR module is a signal indicating whether or not a Reset is to be asserted. This signal is OR'd together with the Reset signal of the BOR module to provide the generic BOR signal, which goes to the PCON0 register and to the power control block.

### 6.5 MCLR

The MCLR is an optional external input that can reset the device. The MCLR function is controlled by the MCLRE bit of Configuration Words and the LVP bit of Configuration Words (Table 6-2). The RMCLR bit in the PCON0 register will be set to '0' if a MCLR Reset has occurred.

TABLE 6-2:MCLR CONFIGURATION

| MCLRE | LVP | MCLR     |

|-------|-----|----------|

| х     | 1   | Enabled  |

| 1     | 0   | Enabled  |

| 0     | 0   | Disabled |

#### 6.5.1 MCLR ENABLED

When MCLR is enabled and the pin is held low, the device is held in Reset. The MCLR pin is connected to VDD through an internal weak pull-up.

The device has a noise filter in the  $\overline{\text{MCLR}}$  Reset path. The filter will detect and ignore small pulses.

| Note: | An                               | internal   | Reset  | event   | (RESET    |  |  |  |

|-------|----------------------------------|------------|--------|---------|-----------|--|--|--|

|       | instr                            | uction, BC | DR, WW | DT, POF | R stack), |  |  |  |

|       | does not drive the MCLR pin low. |            |        |         |           |  |  |  |

#### 6.5.2 MCLR DISABLED

When MCLR is disabled, the MCLR pin becomes inputonly and pin functions such as internal weak pull-ups are under software control. See Section 16.1 "I/O Priorities" for more information.

#### 6.6 Windowed Watchdog Timer (WWDT) Reset

The Windowed Watchdog Timer generates a Reset if the firmware does not issue a CLRWDT instruction within the time-out period or window set. The TO and PD bits in the STATUS register and the RWDT bit in the PCON0 register are changed to indicate a WWDT Reset. The WDTWV bit in the PCON0 register indicates if the WDT Reset has occurred due to a time out or a window violation. See Section 11.0 "Windowed Watchdog Timer (WWDT)" for more information.

#### 6.7 RESET Instruction

A RESET instruction will cause a device Reset. The  $\overline{RI}$  bit in the PCON0 register will be set to '0'. See Table 6-3 for default conditions after a RESET instruction has occurred.

#### 6.8 Stack Overflow/Underflow Reset

The device can reset when the Stack Overflows or Underflows. The STKOVF or STKUNF bits of the PCON0 register indicate the Reset condition. These Resets are enabled by setting the STVREN bit in Configuration Words. See Section 4.2.5 "Return Address Stack" for more information.

#### 6.9 Programming Mode Exit

Upon exit of Programming mode, the device will behave as if a POR occurred.

### 6.10 Power-up Timer (PWRT)

The Power-up Timer provides a selected time-out duration on POR or Brown-out Reset.

The device is held in Reset as long as PWRT is active. The PWRT delay allows additional time for the VDD to rise to an acceptable level. The Power-up Timer is selected by setting the PWRTS<1:0> Configuration bits, appropriately.

The Power-up Timer starts after the release of the POR and BOR/LPBOR if enabled, as shown in Figure 6-1.

| R-q/q           | R-q/q     | R-q/q                                                                                                                                 | R-q/q           | R-q/q             | R-q/q             | U-0            | R-q/q        |  |  |

|-----------------|-----------|---------------------------------------------------------------------------------------------------------------------------------------|-----------------|-------------------|-------------------|----------------|--------------|--|--|

| EXTOR           | HFOR      | MFOR                                                                                                                                  | LFOR            | SOR               | ADOR              | —              | PLLR         |  |  |

| bit 7           |           |                                                                                                                                       |                 |                   |                   |                | bit (        |  |  |

|                 |           |                                                                                                                                       |                 |                   |                   |                |              |  |  |

| Legend:         |           |                                                                                                                                       |                 |                   |                   |                |              |  |  |

| R = Readabl     |           | W = Writable                                                                                                                          |                 |                   | mented bit, read  |                |              |  |  |

| u = Bit is unc  | changed   | x = Bit is unk                                                                                                                        | nown            | -n/n = Value      | at POR and BO     | R/Value at all | other Resets |  |  |

| '1' = Bit is se | et        | '0' = Bit is cle                                                                                                                      | ared            | q = Reset va      | alue is determine | ed by hardware | 9            |  |  |

|                 |           |                                                                                                                                       |                 |                   |                   |                |              |  |  |

| bit 7           |           | XTOSC (external<br>oscillator is ready                                                                                                |                 | eady bit          |                   |                |              |  |  |

|                 |           | oscillator is not er                                                                                                                  |                 | ot vet ready to l | be used           |                |              |  |  |

| bit 6           |           | INTOSC Oscillate                                                                                                                      |                 |                   |                   |                |              |  |  |

|                 |           |                                                                                                                                       |                 |                   |                   |                |              |  |  |

|                 | 0 = The c | scillator is not er                                                                                                                   | abled, or is no | ot yet ready to l | be used           |                |              |  |  |

| bit 5           |           | MFOR: MFINTOSC Oscillator Ready                                                                                                       |                 |                   |                   |                |              |  |  |

|                 |           | scillator is ready                                                                                                                    |                 |                   |                   |                |              |  |  |

|                 |           | oscillator is not er                                                                                                                  |                 | ot yet ready to l | be used           |                |              |  |  |

| bit 4           |           | LFOR: LFINTOSC Oscillator Ready bit                                                                                                   |                 |                   |                   |                |              |  |  |

|                 |           | <ul> <li>1 = The oscillator is ready to be used</li> <li>0 = The oscillator is not enabled, or is not yet ready to be used</li> </ul> |                 |                   |                   |                |              |  |  |

| bit 3           |           | ondary (Timer1) (                                                                                                                     |                 |                   | Je useu           |                |              |  |  |

| JILO            |           |                                                                                                                                       |                 |                   |                   |                |              |  |  |

|                 |           |                                                                                                                                       |                 |                   |                   |                |              |  |  |

| bit 2           | ADOR: AD  | ADOR: ADC Oscillator Ready bit                                                                                                        |                 |                   |                   |                |              |  |  |

|                 |           | oscillator is ready                                                                                                                   |                 |                   |                   |                |              |  |  |

|                 | 0 = The o | oscillator is not er                                                                                                                  | nabled, or is n | ot yet ready to   | be used           |                |              |  |  |

| bit 1           | Unimplem  | Unimplemented: Read as '0'                                                                                                            |                 |                   |                   |                |              |  |  |

| bit 0           | PLLR: PLL | is Ready bit                                                                                                                          |                 |                   |                   |                |              |  |  |

|                 |           | PLL is ready to b                                                                                                                     | e used          |                   |                   |                |              |  |  |

|                 | 0 = The F |                                                                                                                                       |                 |                   |                   |                |              |  |  |

#### REGISTER 7-4: OSCSTAT: OSCILLATOR STATUS REGISTER 1

#### 14.5 CRC Check Value

The CRC check value will be located in the CRCACC registers after the CRC calculation has finished. The check value will depend on two mode settings of the CRCCON0 register: ACCM and SHIFTM. When the ACCM bit is set, the CRC module augments the data with a number of zeros equal to the length of the polynomial to align the final check value. When the ACCM bit is not set, the CRC will stop at the end of the data. A number of zeros equal to the length of the polynomial can then be entered into CRCDAT to find the same check value as augmented mode. Alternatively, the expected check value can be entered at this point to make the final result equal '0'.

When the CRC check value is computed with the SHIFTM bit set, selecting LSb first, and the ACCM bit is also set, then the final value in the CRCACC registers will be reversed such that the LSb will be in the MSb position and vice versa. This is the expected check value in bit reversed form. If you are creating a check value to be appended to a data stream, then a bit reversal must be performed on the final value to achieve the correct checksum. You can use the CRC to do this reversal by the following method:

- Save the CRCACC value in user RAM space

- Clear the CRCACC registers

- Clear the CRCXOR registers

- Write the saved CRCACC value to the CRCDAT input.

The properly oriented check value will be in the CRCACC registers as the result.

### 14.6 CRC Interrupt

The CRC will generate an interrupt when the BUSY bit transitions from 1 to 0. The CRCIF Interrupt Flag is set every time the BUSY bit transitions, regardless of whether or not the CRC interrupt is enabled. The CRCIF bit can only be cleared in software.

#### 14.7 Configuring the CRC

The following steps illustrate how to properly configure the CRC.

- Determine if the automatic program memory scan will be used with the scanner or manual calculation through the SFR interface and perform the actions specified in Section 14.4 "CRC Data Sources", depending on which decision was made.

- 2. If desired, seed a starting CRC value into the CRCACCH/L registers.

- 3. Program the CRCXORH/L registers with the desired generator polynomial.

- Program the DLEN<3:0> bits of the CRCCON1 register with the length of the data word - 1 (refer to Example 14-1). This determines how many times the shifter will shift into the accumulator for each data word.

- 5. Program the PLEN<3:0> bits of the CRCCON1 register with the length of the polynomial -2 (refer to Example 14-1).

- 6. Determine whether shifting in trailing zeros is desired and set the ACCM bit of the CRCCON0 register appropriately.

- 7. Likewise, determine whether the MSb or LSb should be shifted first and write the SHIFTM bit of the CRCCON0 register appropriately.

- 8. Write the GO bit of the CRCCON0 register to begin the shifting process.

- 9a. If manual SFR entry is used, monitor the FULL bit of the CRCCON0 register. When FULL = 0, another word of data can be written to the CRCDATH/L registers, keeping in mind that CRCDATH should be written first if the data has more than eight bits, as the shifter will begin upon the CRCDATL register being written.

- 9b. If the scanner is used, the scanner will automatically load words into the CRCDATH/L registers as needed, as long as the GO bit is set.

- 10a. If manual entry is used, monitor the CRCIF (and BUSY bit to determine when the completed CRC calculation can be read from CRCACCH/L registers.

- 10b.If using the memory scanner, monitor the SCANIF (or the GO bit) for the scanner to finish pushing information into the CRCDAT registers. After the scanner is completed, monitor the BUSY bit to determine that the CRC has been completed and the check value can be read from the CRCACC registers. If both the interrupt flags are set and the BUSY and GO bits are cleared, the completed CRC calculation can be read from the CRCACCH/L registers.

#### 15.9.4 TRANSFER FROM SFR TO GPR

The following visual reference describes the sequence of events when copying ADC results to a GPR location. The ADC Interrupt Flag can be chosen as the Source Hardware trigger, the Source address can be set to point to the ADC Result registers at 3EEF, the Destination address can be set to point to any GPR location of our choice (Example 0x100).

#### FIGURE 15-8: SFR SPACE TO GPR SPACE TRANSFER

| Instruction<br>Clock       |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |  |

|----------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|

| EN                         |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |  |

| SIRQEN                     |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |  |

| Source Hardware<br>Trigger |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |  |

| DGO                        |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |  |

| DMAxSPTR                   | Ox3EEF         Ox3EF0         S         Ox3EEF         Ox3EEF         Ox3EEF         S         S         S         S         S         S         S         S         S         S         S         S         S         S         S         S         S         S         S         S         S         S         S         S         S         S         S         S         S         S         S         S         S         S         S         S         S         S         S         S         S         S         S         S         S         S         S         S         S         S         S         S         S         S         S         S         S         S         S         S         S         S         S         S         S         S         S         S         S         S         S         S         S         S         S         S         S         S         S         S         S         S         S         S         S         S         S         S         S         S         S         S         S         S         S         S         S         S         S         S </th <th></th>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |  |

| DMAxDPTR                   | 0x100         0x101         ( 0x102         0x103         ( 0x103)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |  |

| DMAxSCNT                   |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |  |

| DMAxDCNT                   |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |  |

| DMA STATE                  | $ \left( \begin{array}{c} \text{IDLE} \end{array} \right) \left( SR^{(1)} \right) DW^{(2)} \left( SR^$ |  |

| DMAxSCNTIF                 |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |  |

| DMAxDCNTIF -               | <u>}</u>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |  |

|                            | DMAxSSA 0x3EEF DMAxDSA 0x100                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |  |

|                            | DMAxSSZ 0x2 DMAxDSZ 0xA                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |  |

|                            | SMODE 0x1 DMODE 0x1                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |  |

| Note 1:                    | SR - Source Read                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |  |

| 2:                         | DW - Destination Write                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |  |

| R/W-0/0        | -                                    | R/W-0/0                                                     | R/W-0/0           | R/W-0/0                    | R/W-0/0           | R/W-0/0          | R/W-0/0          |

|----------------|--------------------------------------|-------------------------------------------------------------|-------------------|----------------------------|-------------------|------------------|------------------|

| PSYNC          |                                      | CKSYNC                                                      | r\/vv-0/U         | FX/VV-0/U                  | MODE<4:0>         | N/ VV-U/U        | FX/VV-0/U        |

| bit 7          | CRFUL                                | CKSTNC                                                      |                   |                            | NODE~4.02         |                  | bit 0            |

|                |                                      |                                                             |                   |                            |                   |                  | DILU             |

| Legend:        |                                      |                                                             |                   |                            |                   |                  |                  |

| R = Reada      | ble bit                              | W = Writable                                                | bit               | U = Unimpler               | mented bit, read  | d as '0'         |                  |

| u = Bit is u   | nchanged                             | x = Bit is unkr                                             | nown              | -n/n = Value a             | at POR and BC     | R/Value at all   | other Resets     |

| '1' = Bit is s | •                                    | '0' = Bit is clea                                           | ared              |                            |                   |                  |                  |

|                |                                      |                                                             |                   |                            |                   |                  |                  |

| bit 7          | 1 = TxTMR                            | erx Prescaler S<br>Prescaler Outpu<br>Prescaler Outpu       | ut is synchroni   | zed to Fosc/4              |                   |                  |                  |

| bit 6          | 1 = Falling e                        | erx Clock Polar<br>dge of input clo<br>dge of input clo     | ck clocks time    | er/prescaler               |                   |                  |                  |

| bit 5          | 1 = ON regis                         | merx Clock Syn<br>ster bit is synchi<br>ster bit is not syn | ronized to T21    | MR_clk input               | put               |                  |                  |

| bit 4-0        |                                      | Timerx Contro                                               |                   | ion bits <sup>(6, 7)</sup> |                   |                  |                  |

| Note 1:        | Setting this bit er                  | nsures that read                                            | ling TxTMR w      | ill return a valid         | data value.       |                  |                  |

| 2:             | When this bit is '                   | 1', Timer2 cann                                             | ot operate in S   | Sleep mode.                |                   |                  |                  |

| 3:             | CKPOL should n                       | ot be changed                                               | while ON = 1.     |                            |                   |                  |                  |

| 4:             | Setting this bit er                  | nsures glitch-fre                                           | e operation w     | hen the ON is e            | enabled or disa   | bled.            |                  |

| 5:             | When this bit is s set.              | set then the time                                           | er operation wi   | ill be delayed by          | y two TxTMR ir    | nput clocks afte | er the ON bit is |

| 6:             | Unless otherwise affecting the value |                                                             | modes start u     | upon ON = 1 a              | nd stop upon (    | ON = 0 (stops    | occur without    |

| 7.             |                                      |                                                             | ala ali ala ara T |                            | and of the energy | ational manada   |                  |

#### REGISTER 22-6: TxHLT: TIMERx HARDWARE LIMIT CONTROL REGISTER

7: When TxTMR = TxPR, the next clock clears TxTMR, regardless of the operating mode.

© 2017 Microchip Technology Inc.

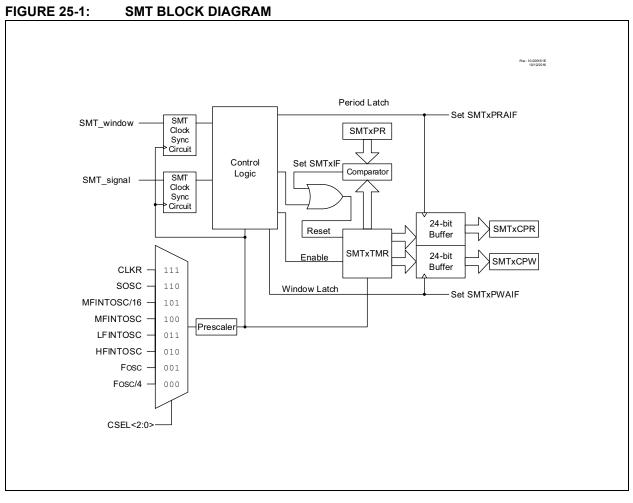

#### 25.6.8 CAPTURE MODE

This mode captures the Timer value based on a rising or falling edge on the SMTWINx input and triggers an interrupt. This mimics the capture feature of a CCP module. The timer begins incrementing upon the GO bit being set, and updates the value of the SMT1CPR register on each rising edge of SMTWINx, and updates the value of the CPW register on each falling edge of the SMTWINx. The timer is not reset by any hardware conditions in this mode and must be reset by software, if desired. See Figure 25-16 and Figure 25-17.

| R/W/HC-0/0       | R/W-0/0                                                         | U-0                                                        | U-0           | R/W-0/0        | R/W-0/0         | R/W-0/0        | R/W-0/0      |  |  |

|------------------|-----------------------------------------------------------------|------------------------------------------------------------|---------------|----------------|-----------------|----------------|--------------|--|--|

| GO               | REPEAT                                                          |                                                            |               |                | MODE            | <3:0>          |              |  |  |

| bit 7            |                                                                 |                                                            |               |                |                 |                | bit (        |  |  |

| Legend:          |                                                                 |                                                            |               |                |                 |                |              |  |  |

| HC = Bit is clea | ared by hardv                                                   | vare                                                       |               | HS = Bit is se | t by hardware   |                |              |  |  |

| R = Readable     | bit                                                             | W = Writable                                               | bit           | U = Unimplen   | nented bit, rea | d as '0'       |              |  |  |

| u = Bit is unch  | anged                                                           | x = Bit is unkr                                            | iown          | -n/n = Value a | at POR and BC   | R/Value at all | other Resets |  |  |

| '1' = Bit is set |                                                                 | '0' = Bit is clea                                          | ared          | q = Value dep  | ends on condi   | tion           |              |  |  |

|                  |                                                                 |                                                            |               |                |                 |                |              |  |  |

| bit 7            | 1 = Increme                                                     | ta Acquisition bit<br>nting, acquiring<br>nting, acquiring | data is enabl |                |                 |                |              |  |  |

| bit 6            | 1 = Repeat I                                                    | MT Repeat Acqu<br>Data Acquisition<br>cquisition mode      | mode is ena   |                |                 |                |              |  |  |

| bit 5-4          | Unimpleme                                                       | nted: Read as '                                            | )'            |                |                 |                |              |  |  |