Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

#### Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Product Status             | Active                                                                     |

|----------------------------|----------------------------------------------------------------------------|

| Core Processor             | PIC                                                                        |

| Core Size                  | 8-Bit                                                                      |

| Speed                      | 64MHz                                                                      |

| Connectivity               | I <sup>2</sup> C, LINbus, SPI, UART/USART                                  |

| Peripherals                | Brown-out Detect/Reset, DMA, HLVD, POR, PWM, WDT                           |

| Number of I/O              | 25                                                                         |

| Program Memory Size        | 64KB (64K x 8)                                                             |

| Program Memory Type        | FLASH                                                                      |

| EEPROM Size                | 1K x 8                                                                     |

| RAM Size                   | 4K x 8                                                                     |

| Voltage - Supply (Vcc/Vdd) | 2.3V ~ 5.5V                                                                |

| Data Converters            | A/D 24x12b; D/A 1x5b                                                       |

| Oscillator Type            | Internal                                                                   |

| Operating Temperature      | -40°C ~ 125°C (TA)                                                         |

| Mounting Type              | Surface Mount                                                              |

| Package / Case             | 28-UQFN Exposed Pad                                                        |

| Supplier Device Package    | 28-UQFN (6x6)                                                              |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/pic18f26k42-e-mx |

|                            |                                                                            |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

| ENAIVIFLE IS  | -4. VVNI       |                             |                                       |

|---------------|----------------|-----------------------------|---------------------------------------|

|               | MOVLW          | D'64′                       | ; number of bytes in erase block      |

|               | MOVWF          | COUNTER                     |                                       |

|               | MOVLW          | BUFFER ADDR HIGH            | ; point to buffer                     |

|               | MOVWF          | FSR0H                       |                                       |

|               | MOVLW          | BUFFER_ADDR_LOW             |                                       |

|               | MOVWF          | FSROL                       |                                       |

|               | MOVLW          | CODE_ADDR_UPPER             | ; Load TBLPTR with the base           |

|               | MOVWF          | TBLPTRU                     | ; address of the memory block         |

|               | MOVLW          | CODE_ADDR_HIGH              |                                       |

|               | MOVWF          | TBLPTRH                     |                                       |

|               | MOVLW          | CODE_ADDR_LOW               |                                       |

|               | MOVWF          | TBLPTRL                     |                                       |

| READ_BLOCK    |                |                             |                                       |

|               | TBLRD*+        |                             | ; read into TABLAT, and inc           |

|               | MOVF           | TABLAT, W                   | ; get data                            |

|               | MOVWF          | POSTINCO                    | ; store data                          |

|               | DECFSZ         | COUNTER                     | ; done?                               |

|               | BRA            | READ_BLOCK                  | ; repeat                              |

| MODIFY_WORD   |                |                             |                                       |

|               | MOVLW          |                             | ; point to buffer                     |

|               | MOVWF          | FSROH                       |                                       |

|               | MOVLW          | BUFFER_ADDR_LOW             |                                       |

|               | MOVWF          | FSROL<br>NEW DATA LOW       | · undate huffer word                  |

|               | MOVLW<br>MOVWF | NEW_DATA_LOW<br>POSTINC0    | ; update buffer word                  |

|               | MOVLW          | NEW DATA HIGH               |                                       |

|               | MOVHW          | INDF0                       |                                       |

| ERASE BLOCK   |                | INDIO                       |                                       |

|               | MOVLW          | CODE ADDR UPPER             | ; load TBLPTR with the base           |

|               | MOVWF          | TBLPTRU                     | ; address of the memory block         |

|               | MOVLW          | CODE ADDR HIGH              | ,                                     |

|               | MOVWF          | TBLPTRH                     |                                       |

|               | MOVLW          | CODE ADDR LOW               |                                       |

|               | MOVWF          | TBLPTRL                     |                                       |

|               | BCF            | NVMCON1, REG0               | ; point to Program Flash Memory       |

|               | BSF            | NVMCON1, REG1               | ; point to Program Flash Memory       |

|               | BSF            | NVMCON1, WREN               | ; enable write to memory              |

|               | BSF            | NVMCON1, FREE               | ; enable Erase operation              |

|               | BCF            | INTCONO, GIE                | ; disable interrupts                  |

|               | MOVLW          | 55h                         |                                       |

| Required      | MOVWF          | NVMCON2                     | ; write 55h                           |

| Sequence      | MOVLW          | AAh                         |                                       |

|               | MOVWF          | NVMCON2                     | ; write OAAh                          |

|               | BSF            | NVMCON1, WR                 | ; start erase (CPU stall)             |

|               | BSF            | INTCON0, GIE                | ; re-enable interrupts                |

|               | TBLRD*-        |                             | ; dummy read decrement                |

|               | MOVLW          | BUFFER_ADDR_HIGH            | ; point to buffer                     |

|               | MOVWF          | FSROH                       |                                       |

|               | MOVLW          | BUFFER_ADDR_LOW             |                                       |

| מסדקר סווביהה | MOVWF          | FSROL                       |                                       |

| WRITE_BUFFE   | _              | BlockSizo                   | · number of butes in holding register |

|               | MOVLW          | BlockSize<br>COUNTER        | ; number of bytes in holding register |

|               | MOVWF          |                             | ; number of write blocks in 64 bytes  |

|               | MOVLW<br>MOVWF | D'64'/BlockSize<br>COUNTER2 | , number of wirde procks in 04 bytes  |

|               | PIO V W P      | COUNTRIVE                   |                                       |

| 1             |                |                             |                                       |

#### EXAMPLE 13-4: WRITING TO PROGRAM FLASH MEMORY

| U-0            | R/W-0/0                  | R/W-0/0            | R/W-0/0          | U-0               | U-0             | R/W-0/0         | R/W-0/0       |  |  |

|----------------|--------------------------|--------------------|------------------|-------------------|-----------------|-----------------|---------------|--|--|

|                | SLEW                     | PU<                | :1:0>            | —                 | —               | TH<             | :1:0>         |  |  |

| bit 7          | ·                        |                    |                  |                   |                 |                 | bit 0         |  |  |

|                |                          |                    |                  |                   |                 |                 |               |  |  |

| Legend:        |                          |                    |                  |                   |                 |                 |               |  |  |

| R = Readat     | ole bit                  | W = Writable       | bit              | U = Unimpler      | mented bit, rea | id as '0'       |               |  |  |

| u = Bit is ur  | nchanged                 | x = Bit is unkr    | nown             | -n/n = Value      | at POR and B    | OR/Value at all | other Resets  |  |  |

| '1' = Bit is s | et                       | '0' = Bit is cle   | ared             | HS = Hardware set |                 |                 |               |  |  |

|                |                          |                    |                  |                   |                 |                 |               |  |  |

| bit 7          | Unimpleme                | nted: Read as '    | 0'               |                   |                 |                 |               |  |  |

| bit 6          | SLEW: I <sup>2</sup> C s | pecific slew rate  | e limiting is en | abled             |                 |                 |               |  |  |

|                |                          | ecific slew rate I | imiting is enab  | led. Standard     | pad slew limiti | ng is disabled. | The SLRxy bit |  |  |

|                | is ignor                 |                    | oto, on oblod/   |                   | Duchit          |                 |               |  |  |

|                |                          | rd GPIO Slew F     |                  | JISADIEU VIA SL   | RXY DIL.        |                 |               |  |  |

| bit 5-4        | 11 = Reser               | C Pull-up Select   | ion dits         |                   |                 |                 |               |  |  |

|                |                          | urrent of standa   | rd weak pull-u   | p                 |                 |                 |               |  |  |

|                |                          | rent of standard   | •                |                   |                 |                 |               |  |  |

|                | 00 = Stand               | ard GPIO weak      | pull-up, enabl   | ed via WPUxy      | bit             |                 |               |  |  |

| bit 3-2        | Unimpleme                | nted: Read as '    | 0'               |                   |                 |                 |               |  |  |

| bit 1-0        |                          | C Input Thresho    |                  | ts                |                 |                 |               |  |  |

|                |                          | is 3.0 (1.35 V) ii |                  |                   |                 |                 |               |  |  |

|                |                          | is 2.0 (2.1 V) inp |                  |                   |                 |                 |               |  |  |

|                |                          | ecific input thre  | 510105           |                   |                 |                 |               |  |  |

### REGISTER 16-9: RxyI2C: I<sup>2</sup>C PAD Rxy CONTROL REGISTER

00 = Standard GPIO Input pull-up, enabled via INLVLxy registers

| Name                  | Bit 7 | Bit 6 | Bit 5   | Bit 4 | Bit 3 | Bit 2 | Bit 1   | Bit 0 |

|-----------------------|-------|-------|---------|-------|-------|-------|---------|-------|

| RB1I2C                | _     | SLEW  | PU<1:0> |       | —     | —     | TH<1:0> |       |

| RB2I2C                | _     | SLEW  | PU<1:0> |       | —     | _     | TH<     | 1:0>  |

| RC3I2C                | _     | SLEW  | PU<     | 1:0>  | —     | —     | TH<     | 1:0>  |

| RC4I2C                | _     | SLEW  | PU<     | 1:0>  | —     | —     | TH<     | 1:0>  |

| RD0I2C <sup>(1)</sup> | _     | SLEW  | PU<1:0> |       | —     | _     | TH<     | 1:0>  |

| RD1I2C <sup>(1)</sup> | _     | SLEW  | PU<1:0> |       | —     | —     | TH<     | 1:0>  |

#### TABLE 16-10: I2C PAD CONTROL REGISTERS

**Note 1:** Unimplemented in PIC18(L)F26/27K42.

| REGISTER      | 21-2: IXGC                                          | UN: HMER                                                          | X GATE CO                        | NIROL REGIS                                                                       | IER                                |                  |       |

|---------------|-----------------------------------------------------|-------------------------------------------------------------------|----------------------------------|-----------------------------------------------------------------------------------|------------------------------------|------------------|-------|

| R/W-0/u       | R/W-0/u                                             | R/W-0/u                                                           | R/W-0/u                          | R/W-0/u                                                                           | R-x                                | U-0              | U-0   |

| GE            | GPOL                                                | GTM                                                               | GSPM                             | GGO/DONE                                                                          | GVAL                               | _                | _     |

| bit 7         |                                                     |                                                                   |                                  |                                                                                   |                                    |                  | bit 0 |

|               |                                                     |                                                                   |                                  |                                                                                   |                                    |                  |       |

| Legend:       |                                                     |                                                                   |                                  |                                                                                   |                                    |                  |       |

| R = Readable  | e bit                                               | W = Writable                                                      | bit                              | U = Unimpleme                                                                     | nted bit, read as                  | s 'O'            |       |

| -n = Value at | POR                                                 | '1' = Bit is se                                                   | t                                | '0' = Bit is cleare                                                               | ed                                 | x = Bit is unkno | own   |

| bit 7         | If TMRxON =   1 = Timerx   0 = Timerx   If TMRxON = | counting is co<br>is always cour                                  | ntrolled by th                   | e Timerx gate fur                                                                 | nction                             |                  |       |

| bit 6         | 1 = Timerx                                          |                                                                   | -high (Timerx                    | counts when gat                                                                   |                                    |                  |       |

| bit 5         | 1 = Timerx<br>0 = Timerx                            | Gate Toggle I<br>Gate Toggle m<br>Gate Toggle m<br>Flip Flop Togg | node is enabl<br>node is disabl  | ed and Toggle flip                                                                | p-flop is cleared                  |                  |       |

| bit 4         | 1 = Timerx                                          | rx Gate Single<br>Gate Single P<br>Gate Single P                  | ulse mode is                     | enabled and is co                                                                 | ontrolling Timer                   | gate)            |       |

| bit 3         | 1 = Timerx<br>0 = Timerx                            | Gate Single P<br>Gate Single P                                    | ulse Acquisiti<br>ulse Acquisiti | Acquisition Status<br>on is ready, waitii<br>on has completed<br>(GSPM is cleared | ng for an edge<br>d or has not bee | n started.       |       |

| bit 2         | Indicates the                                       | rx Gate Currer<br>current state o<br>y Timerx Gate                | of the Timerx                    | gate that could b<br>RxGE)                                                        | e provided to TN                   | MRxH:TMRxL       |       |

| bit 1-0       | Unimpleme                                           | nted: Read as                                                     | ʻ0 <b>'</b>                      |                                                                                   |                                    |                  |       |

|               |                                                     |                                                                   |                                  |                                                                                   |                                    |                  |       |

#### REGISTER 21-2: TxGCON: TIMERx GATE CONTROL REGISTER

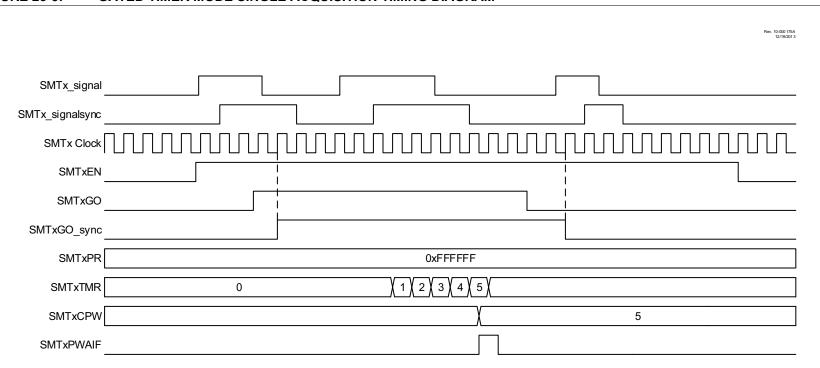

#### FIGURE 25-5: GATED TIMER MODE SINGLE ACQUISITION TIMING DIAGRAM

#### 25.6.9 COUNTER MODE

This mode increments the timer on each pulse of the SMT1\_signal input. This mode is asynchronous to the SMT clock and uses the SMT1\_signal as a time source. The SMT1CPW register will be updated with the current SMT1TMR value on the rising edge of the SMT1WIN input. See Figure 25-18.

#### FIGURE 25-18: COUNTER MODE TIMING DIAGRAM

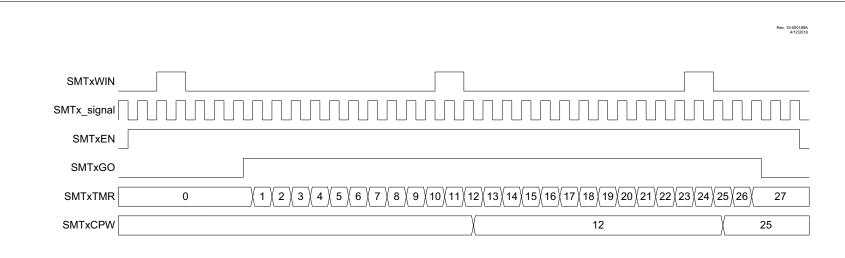

#### 25.6.10 GATED COUNTER MODE

This mode counts pulses on the SMT1\_signal input, gated by the SMT1WIN input. It begins incrementing the timer upon seeing a rising edge of the SMT1WIN input and updates the SMT1CPW register upon a falling edge on the SMT1WIN input. See Figure 25-19 and Figure 25-20.

### 26.7 Rising Edge and Reverse Dead Band

In Half-Bridge mode, the rising edge dead band delays the turn-on of the CWGxA output after the rising edge of the CWG data input. In Full-Bridge mode, the reverse dead-band delay is only inserted when changing directions from Forward mode to Reverse mode, and only the modulated output CWGxB is affected.

The CWGxDBR register determines the duration of the dead-band interval on the rising edge of the input source signal. This duration is from 0 to 64 periods of the CWG clock.

Dead band is always initiated on the edge of the input source signal. A count of zero indicates that no dead band is present.

If the input source signal reverses polarity before the dead-band count is completed, then no signal will be seen on the respective output.

The CWGxDBR register value is double-buffered. When EN = 0 (Register 26-1), the buffer is loaded when CWGxDBR is written. If EN = 1, then the buffer will be loaded at the rising edge following the first falling edge of the data input, after the LD bit (Register 26-1) is set. Refer to Figure 26-12 for an example.

### 26.8 Falling Edge and Forward Dead Band

In Half-Bridge mode, the falling edge dead band delays the turn-on of the CWGxB output at the falling edge of the CWG data input. In Full-Bridge mode, the forward dead-band delay is only inserted when changing directions from Reverse mode to Forward mode, and only the modulated output CWGxD is affected.

The CWGxDBF register determines the duration of the dead-band interval on the falling edge of the input source signal. This duration is from zero to 64 periods of CWG clock.

Dead-band delay is always initiated on the edge of the input source signal. A count of zero indicates that no dead band is present.

If the input source signal reverses polarity before the dead-band count is completed, then no signal will be seen on the respective output.

The CWGxDBF register value is double-buffered. When EN = 0 (Register 26-1), the buffer is loaded when CWGxDBF is written. If EN = 1, then the buffer will be loaded at the rising edge following the first falling edge of the data input after the LD (Register 26-1) is set. Refer to Figure 26-13 for an example.

| FIGURE 31-5:                        | ASYNCHRONOUS RECE                                                                       | EPTION                   |                     |                        |           |

|-------------------------------------|-----------------------------------------------------------------------------------------|--------------------------|---------------------|------------------------|-----------|

| RX pin                              | Start<br>bit bit 0 bit 1 Sto                                                            | p Start<br>bit bit 0 / / | Xlast bit/ Stop bit | Stop                   |           |

| Rcv Shift<br>Reg<br>Rcv Buffer Reg. | ↓ ↓ ↓ ↓ ↓ ↓ ↓ ↓ ↓ ↓ ↓ ↓ ↓ ↓ ↓ ↓ ↓ ↓ ↓                                                   | <u> </u>                 | Word 2<br>UxRXB     | <u></u>                |           |

| RXIDL -                             |                                                                                         | <u> </u>                 | i~i                 | <u>}</u>               |           |

| Read Rcv<br>Buffer Reg.<br>UxRXB —  | <u>}                                </u>                                                | <u>} </u>                |                     | <u>}</u>               | ų         |

| UxRXIF<br>(Interrupt Flag)  -       | j                                                                                       | <u> </u>                 |                     |                        |           |

| RXFOIF bit                          |                                                                                         | <u> </u>                 |                     | <u></u> ز              |           |

|                                     |                                                                                         |                          |                     | Cleared by so          | oftware ) |

|                                     | iming diagram shows three words appearing<br>eived, causing the RXFOIF (FIFO overrun) b |                          |                     | ead before the third w | /ord      |

### 31.3 Asynchronous Address Mode

A special Address Detection mode is available for use when multiple receivers share the same transmission line, such as in RS-485 systems.

When Asynchronous Address mode is enabled, all data is transmitted and received as 9-bit characters. The 9th bit determines whether the character is an address or data. When the 9th bit is set, the eight Least Significant bits are the address. When the 9th bit is clear, the Least Significant bits are data. In either case, the 9th bit is stored in PERIF when the byte is written to the receive FIFO. When PERIE is also set, the RXIF will be suppressed, thereby suspending DMA transfers allowing software to process the received address.

An address character will enable all receivers that match the address and disable all other receivers. Once a receiver is enabled, all non-address characters will be received until an address character is received that does not match.

#### 31.3.1 ADDRESS MODE TRANSMIT

The UART transmitter is enabled for asynchronous address operation by configuring the following control bits:

- TXEN = 1

- MODE<3:0> = 0100

- UxBRGH:L = desired baud rate

- RxyPPS = code for desired output pin

- ON = 1

Addresses are sent by writing to the UxP1L register. This transmits the written byte with the 9th bit set, which indicates that the byte is an address.

Data is sent by writing to the UxTXB register. This transmits the written byte with the 9th bit cleared, which indicates that the byte is data.

To send data to a particular device on the transmission bus, first transmit the address of the intended device. All subsequent data will be accepted only by that device until an address of another device is transmitted.

Writes to UxP1L take precedence over writes to UxTXB. When both the UxP1L and UxTXB registers are written while the TSR is busy, the next byte to be transmitted will be from UxP1L.

To ensure that all data intended for one device is sent before the address is changed, wait until the TXMTIF bit is high before writing UxP1L with the new address.

### 31.3.2 ADDRESS MODE RECEIVE

The UART receiver is enabled for asynchronous address operation by configuring the following control bits:

- RXEN = 1

- MODE<3:0> = 0100

- UxBRGH:L = desired baud rate

- RXPPS = code for desired input pin

- Input pin ANSEL bit = 0

- UxP2L = receiver address

- UxP3L = address mask

- ON = 1

In Address mode, no data will be transferred to the input FIFO until a valid address is received. This is the default state. Any of the following conditions will cause the UART to revert to the default state:

- ON = 0

- RXEN = 0

- · Received address does not match

When a character with the 9th bit set is received, the Least Significant eight bits of that character will be qualified by the values in the UxP2L and UxP3L registers.

The byte is XOR'd with UxP2L then AND'd with UxP3L. A match occurs when the result is 0h, in which case, the unaltered received character is stored in the receive FIFO, thereby setting the UxRXIF interrupt bit. The 9th bit is stored in the corresponding PERIF bit, identifying this byte as an address.

An address match also enables the receiver for all data such that all subsequent characters without the 9th bit set will be stored in the receive FIFO.

When the 9th bit is set and a match does not occur, the character is not stored in the receive FIFO and all subsequent data is ignored.

The UxP3L register mask allows a range of addresses to be accepted. Software can then determine the subaddress of the range by processing the received address character.

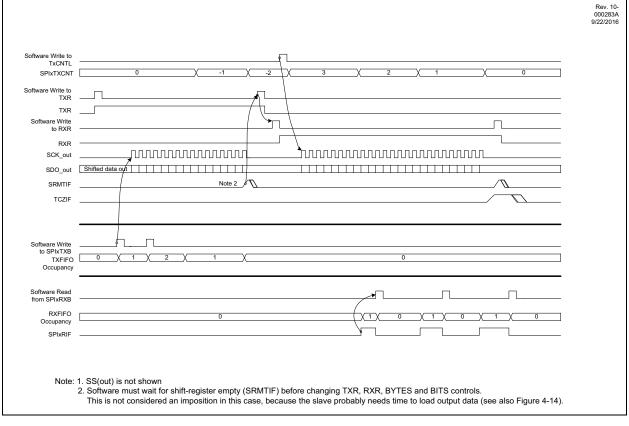

#### 32.5.3 RECEIVE ONLY MODE

When RXR is set and TXR is clear, the SPI master is in Receive Only mode. In this mode, data transfers when the RXFIFO is not full and the Transfer Counter is nonzero. In this mode, writing a value to SPIxTCNTL will start the clocks for transfer. The clocks will suspend while the RXFIFO is full and cease when the SPIxTCNT reaches zero (see Section 32.4 "Transfer Counter"). If there is any data in the TXFIFO, the first data written to the TXFIFO will be transmitted on each data exchange, although the TXFIFO occupancy will not change, meaning that the same message will be sent on each transmission. If there is no data in the TXFIFO, the most recently received data will instead be transmitted. Figure 32-5 shows an example of sending a command using Section 32.5.2 "Transmit Only Mode" and then receiving a byte of data using this mode.

#### 32.5.4 TRANSFER OFF MODE

When both TXR and RXR are cleared, the SPI master is in Transfer Off mode. In this mode, SCK will not toggle and no data is exchanged. However, writes to SPIxTXB will be transferred to the TXFIFO which will be transmitted if the TXR bit is set.

#### 33.3.2 BYTE FORMAT

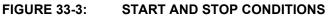

All communication in  $I^2C$  is done in 9-bit segments. A byte is sent from a master to a slave or vice-versa, followed by an Acknowledge bit sent by the receiver. After the 8th falling edge of the SCL line, the device transmitting data on the SDA line releases control of that pin to an input, and reads in an acknowledge value on the next clock pulse. The clock signal is provided by the master. Data is valid to change while the SCL line is low, and sampled on the rising edge of the clock. Changes on the SDA line while the SCL line is high define Start and Stop conditions on the bus which are explained further in the chapter.

#### 33.3.3 SDA AND SCL PINS

The user must configure these pins as open-drain inputs. This is done by clearing the appropriate TRIS bits and setting the appropriate and ODCON bits. The user may also select the input threshold, slew-rate and internal pull-up settings using the Rxyl2C control registers (Register 16-9).

#### 33.3.4 SDA HOLD TIME

The hold time of the SDA pin is selected by the SDAHT<1:0> bits of the I2CxCON2 register. Hold time is the time SDA is held valid after the falling edge of SCL. A longer hold time setting may help on buses with large capacitance.

#### 33.3.5 START CONDITION

The I<sup>2</sup>C specification defines a Start condition as a transition of SDA line from a high to a low state while SCL line is high. A Start condition is always generated by the master and signifies the transition of the bus from an Idle to an Active state. Figure 33-3 shows waveforms for Start conditions. Master hardware waits for the BFRE bit of I2CxSTAT0 to be set, before asserting a Start condition on the SCL and SDA lines. If two masters assert a start at the same time, a collision will occur during the addressing phase.

#### 33.3.6 STOP CONDITION

A Stop condition is a transition of the SDA line from low to high while the SCL line is high. Figure 33-3 shows waveforms for Stop conditions.

| Note: | At least one SCL low time must appear    |  |  |  |  |  |  |  |  |  |

|-------|------------------------------------------|--|--|--|--|--|--|--|--|--|

|       | before a Stop is valid. Therefore if the |  |  |  |  |  |  |  |  |  |

|       | SDA line goes low then high again while  |  |  |  |  |  |  |  |  |  |

|       | the SCL line is high, only the Start     |  |  |  |  |  |  |  |  |  |

|       | condition is detected.                   |  |  |  |  |  |  |  |  |  |

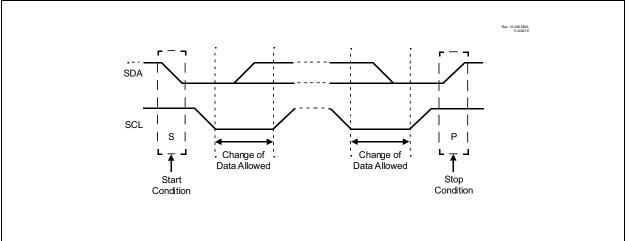

#### FIGURE 33-7: $I^{2}C$ SLAVE, 7-BIT ADDRESS, RECEPTION WITH I2CxCNT (ACKTIE = 1, ADRIE = 0, WRIE = 0)

PIC18(L)F26/27/45/46/47/55/56/57K42

#### 36.1.5 INTERRUPTS

The ADC module allows for the ability to generate an interrupt upon completion of an Analog-to-Digital conversion. The ADC Interrupt Flag is the ADIF bit in the PIRx register. The ADC Interrupt Enable is the ADIE bit in the PIEx register. The ADIF bit must be cleared in software.

- **Note 1:** The ADIF bit is set at the completion of every conversion, regardless of whether or not the ADC interrupt is enabled.

- **2:** The ADC operates during Sleep only when the FRC oscillator is selected.

This interrupt can be generated while the device is operating or while in Sleep. If the device is in Sleep, the interrupt will wake up the device. Upon waking from Sleep, the next instruction following the SLEEP instruction is always executed. If the user is attempting to wake up from Sleep and resume in-line code execution, the ADIE bit of the PIEx register and the GIE bits of the INTCON0 register must both be set. If all these bits are set, the execution will switch to the Interrupt Service Routine.

#### 36.1.6 RESULT FORMATTING

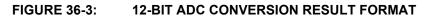

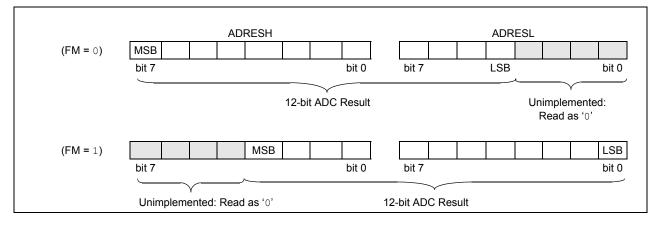

The 12-bit ADC conversion result can be supplied in two formats, left justified or right justified. The FM bits of the ADCON0 register controls the output format.

Figure 36-3 shows the two output formats.

Writes to the ADRES register pair are always right justified regardless of the selected format mode. Therefore, data read after writing to ADRES when ADFRM0 = 0 will be shifted left four places.

© 2017 Microchip Technology Inc.

DS40001919B-page 608

### 41.2.2 EXTENDED INSTRUCTION SET

| ADDULNK          | Add Lite                                                                                       | eral to FS                          | SR2 and                                                                          | Return                                                       |  |  |  |  |

|------------------|------------------------------------------------------------------------------------------------|-------------------------------------|----------------------------------------------------------------------------------|--------------------------------------------------------------|--|--|--|--|

| Syntax:          | ADDULNK k                                                                                      |                                     |                                                                                  |                                                              |  |  |  |  |

| Operands:        | $0 \le k \le 63$                                                                               | 3                                   |                                                                                  |                                                              |  |  |  |  |

| Operation:       | FSR2 + k                                                                                       | $x \rightarrow FSR2$                | ,                                                                                |                                                              |  |  |  |  |

|                  | $(TOS) \rightarrow$                                                                            | PC                                  |                                                                                  |                                                              |  |  |  |  |

| Status Affected: | None                                                                                           |                                     |                                                                                  |                                                              |  |  |  |  |

| Encoding:        | 1110                                                                                           | 1000                                | 11kk                                                                             | kkkk                                                         |  |  |  |  |

| Description:     | contents<br>executed<br>TOS.<br>The instru-<br>execute;<br>the secon<br>This may<br>case of th | be though<br>ne ADDFSI<br>3 (binary | A RETURN<br>g the PC v<br>es two cyc<br>performed<br>ht of as a<br>R instruction | r is then<br>with the<br>cles to<br>during<br>special<br>on, |  |  |  |  |

| Words:           | 1                                                                                              |                                     |                                                                                  |                                                              |  |  |  |  |

| Cycles:          | 2                                                                                              |                                     |                                                                                  |                                                              |  |  |  |  |

#### Q Cycle Activity:

| Q1        | Q1 Q2       |           | Q4        |

|-----------|-------------|-----------|-----------|

| Decode    | Read        | Process   | Write to  |

|           | literal 'k' | Data      | FSR       |

| No        | No          | No        | No        |

| Operation | Operation   | Operation | Operation |

Example: ADDULNK 23h

| Before Instru   | ction |       |

|-----------------|-------|-------|

| FSR2            | =     | 03FFh |

| PC              | =     | 0100h |

| After Instructi | ion   |       |

| FSR2            | =     | 0422h |

| PC              | =     | (TOS) |

|                 |       |       |

**Note:** All PIC18 instructions may take an optional label argument preceding the instruction mnemonic for use in symbolic addressing. If a label is used, the instruction syntax then becomes: {label} instruction argument(s).

| Address          | Name    | Bit 7 | Bit 6 | Bit 5  | Bit 4  | Bit 3   | Bit 2    | Bit 1 | Bit 0 | Register<br>on page |

|------------------|---------|-------|-------|--------|--------|---------|----------|-------|-------|---------------------|

| 3FA1h            | T4HLT   | PSYNC | CKPOL | CKSYNC |        | •       | MODE     |       |       | 339                 |

| 3FA0h            | T4CON   | ON    |       | CKPS   |        |         | OU       | ITPS  |       | 338                 |

| 3F9Fh            | T4PR    |       |       |        | P      | R4      |          |       |       | 337                 |

| 3F9Eh            | T4TMR   |       |       |        | T      | /IR4    |          |       |       | 337                 |

| 3F9Dh            | T5CLK   |       |       |        | (      | CS      |          |       |       | 335                 |

| 3F9Ch            | T5GATE  |       |       |        | G      | SS      |          |       |       | 316                 |

| 3F9Bh            | T5GCON  | GE    | GPOL  | GTM    | GSPM   | GGO     | GVAL     | —     | _     | 314                 |

| 3F9Ah            | T5CON   | —     | _     | СК     | PS     | _       | NOT_SYNC | RD16  | ON    | 338                 |

| 3F99h            | TMR5H   |       |       |        | ΤN     | IR5H    |          |       |       | 317                 |

| 3F98h            | TMR5L   |       |       |        | ΤN     | 1R5L    |          |       |       | 317                 |

| 3F97h            | T6RST   | —     | _     | —      |        |         | RSEL     |       |       | 336                 |

| 3F96h            | T6CLK   | —     | _     | _      | _      |         | (        | CS    |       | 315                 |

| 3F95h            | T6HLT   | PSYNC | CKPOL | CKSYNC |        |         | MODE     |       |       | 339                 |

| 3F94h            | T6CON   | ON    |       | CKPS   |        |         | OU       | ITPS  |       | 338                 |

| 3F93h            | T6PR    |       |       |        | P      | R6      |          |       |       | 337                 |

| 3F92h            | T6TMR   |       |       |        | T      | MR6     |          |       |       | 337                 |

| 3F91h -<br>3F80h | _       |       |       |        | Unimpl | emented |          |       |       |                     |

| 3F7Fh            | CCP1CAP |       |       |        | C      | TS      |          |       |       | 352                 |

| 3F7Eh            | CCP1CON | EN    | _     | OUT    | FMT    |         | M        | DDE   |       | 350                 |

| 3F7Dh            | CCPR1H  |       |       |        | F      | RH      |          |       |       | 353                 |

| 3F7Ch            | CCPR1L  |       |       |        | I      | RL      |          |       |       | 352                 |

| 3F7Bh            | CCP2CAP |       |       |        | C      | TS      |          |       |       | 352                 |

| 3F7Ah            | CCP2CON | EN    | _     | OUT    | FMT    |         | M        | DDE   |       | 350                 |

| 3F79h            | CCPR2H  |       |       |        | F      | RH      |          |       |       | 353                 |

| 3F78h            | CCPR2L  |       |       |        | I      | RL      |          |       |       | 352                 |

| 3F77h            | CCP3CAP |       |       |        | C      | TS      |          |       |       | 352                 |

| 3F76h            | CCP3CON | EN    | _     | OUT    | FMT    |         | M        | DDE   |       | 350                 |

| 3F75h            | CCPR3H  |       | •     |        | F      | RH      |          |       |       | 353                 |

| 3F74h            | CCPR3L  |       |       |        | I      | RL      |          |       |       | 352                 |

| 3F73h            | CCP4CAP |       |       |        | C      | TS      |          |       |       | 352                 |

| 3F72h            | CCP4CON | EN    | _     | OUT    | FMT    |         | М        | DDE   |       | 350                 |

| 3F71h            | CCPR4H  |       | •     |        | F      | RH      |          |       |       | 353                 |

| 3F70h            | CCPR4L  |       |       |        |        | RL      |          |       |       | 352                 |

| 3F6Fh            | _       |       |       |        | Unimpl | emented |          |       |       |                     |

| 3F6Eh            | PWM5CON | EN    | _     | OUT    | POL    |         | _        |       | _     | 358                 |

| 3F6Dh            | PWM5DCH | DC9   | DC8   | DC7    | DC6    | DC5     | DC4      | DC3   | DC2   | 360                 |

| 3F6Dh            | PWM5DCH |       |       |        | C      | C8      |          |       |       | 360                 |

| 3F6Ch            | PWM5DCL | DC1   | DC0   | _      | _      | _       | _        | —     | —     | 360                 |

| 3F6Ch            | PWM5DCL | D     | С     | _      | _      | _       | _        | _     | _     | 360                 |

| 3F6Bh            |         |       |       |        | Unimpl | emented |          |       |       |                     |

| 3F6Ah            | PWM6CON | EN    | _     | OUT    | POL    |         | _        | _     | _     | 358                 |

| 3F69h            | PWM6DCH | D     | C9    | DC7    | DC6    | DC5     | DC4      | DC3   | DC2   | 360                 |

| 3F69h            | PWM6DCH |       |       |        | [      | DC DC   |          |       |       | 360                 |

| 3F68h            | PWM6DCL | DC1   | DC0   | _      | _      | _       | _        | —     | —     | 360                 |

| 3F68h            | PWM6DCL | D     | С     | _      | _      | _       | _        | —     | _     | 360                 |

| 3F67h            |         |       |       |        | Unimpl | emented |          |       |       |                     |

#### TABLE 42-1:REGISTER FILE SUMMARY FOR PIC18(L)F26/27/45/46/47/55/56/57K42 DEVICES

Legend: x = unknown, u = unchanged, — = unimplemented, q = value depends on condition

Note 1: Unimplemented in LF devices.

2: Unimplemented in PIC18(L)F26/27K42.

3: Unimplemented on PIC18(L)F26/27/45/46/47K42 devices.

4: Unimplemented in PIC18(L)F45/55K42.

| Address          | Name                   | Bit 7 | Bit 6  | Bit 5     | Bit 4   | Bit 3  | Bit 2  | Bit 1 | Bit 0 | Register<br>on page |  |

|------------------|------------------------|-------|--------|-----------|---------|--------|--------|-------|-------|---------------------|--|

| 3BFEh            | DMA1AIRQ               | _     |        | •         | •       | AIRQ   |        |       |       | 256                 |  |

| 3BFDh            | DMA1CON1               | EN    | SIRQEN | DGO       | —       | _      | AIRQEN |       | XIP   | 249                 |  |

| 3BFCh            | DMA1CON0               | DN    | 10DE   | DSTP      | SN      | 1R     | SMC    | DDE   | SSTP  | 248                 |  |

| 3BFBh            | DMA1SSAU               | _     | _      |           | •       |        | SSA    |       |       | 251                 |  |

| 3BFAh            | DMA1SSAH               |       | SSA    |           |         |        |        |       |       |                     |  |

| 3BF9h            | DMA1SSAL               |       | SSA    |           |         |        |        |       |       |                     |  |

| 3BF8h            | DMA1SSZH               | _     | _      | — — — SSZ |         |        |        |       |       |                     |  |

| 3BF7h            | DMA1SSZL               |       |        |           | SS      | SZ     |        |       |       | 252                 |  |

| 3BF6h            | DMA1SPTRU              | _     | _      |           |         | S      | SPTR   |       |       | 252                 |  |

| 3BF5h            | DMA1SPTRH              |       |        |           | SP      | TR     |        |       |       | 251                 |  |

| 3BF4h            | DMA1SPTRL              |       |        | SPTR      |         |        |        |       |       |                     |  |

| 3BF3h            | DMA1SCNTH              | _     | _      | _         | —       |        | S      | CNT   |       | 253                 |  |

| 3BF2h            | DMA1SCNTL              |       |        |           | SC      | NT     |        |       |       | 253                 |  |

| 3BF1h            | DMA1DSAH               |       |        |           | DS      | SA     |        |       |       | 254                 |  |

| 3BF0h            | DMA1DSAL               |       |        |           | SS      | 6A     |        |       |       | 253                 |  |

| 3BEFh            | DMA1DSZH               | _     | _      | _         | _       |        | D      | SZ    |       | 255                 |  |

| 3BEEh            | DMA1DSZL               |       |        |           | DS      | SZ     |        |       |       | 255                 |  |

| 3BEDh            | DMA1DPTRH              |       |        |           | DP      | TR     |        |       |       | 254                 |  |

| 3BECh            | DMA1DPTRL              |       |        |           | DP      | TR     |        |       |       | 254                 |  |

| 3BEBh            | DMA1DCNTH              | _     | _      | _         | _       |        | D      | CNT   |       | 256                 |  |

| 3BEAh            | DMA1DCNTL              |       |        |           | DC      | NT     |        |       |       | 255                 |  |

| 3BE9h            | DMA1BUF                |       |        |           | BL      | JF     |        |       |       | 250                 |  |

| 3BE8h -<br>3BE0h | —                      |       |        |           | Unimple | mented |        |       |       |                     |  |

| 3BDFh            | DMA2SIRQ               | _     |        |           |         | SIRQ   |        |       |       | 256                 |  |

| 3BDEh            | DMA2AIRQ               | _     |        |           |         | AIRQ   |        |       |       | 256                 |  |

| 3BDDh            | DMA2CON1               | EN    | SIRQEN | DGO       | _       | _      | AIRQEN | _     | XIP   | 249                 |  |

| 3BDCh            | DMA2CON0               | DN    | 10DE   | DSTP      | SN      | 1R     | SMC    | DDE   | SSTP  | 248                 |  |

| 3BDBh            | DMA2SSAU               | _     | _      |           |         |        | SSA    |       |       | 251                 |  |

| 3BDAh            | DMA2SSAH               |       |        |           | SS      | SA     |        |       |       | 250                 |  |

| 3BD9h            | DMA2SSAL               |       |        |           | SS      | SA     |        |       |       | 250                 |  |

| 3BD8h            | DMA2SSZH               | _     | _      | _         | _       |        | S      | SZ    |       | 252                 |  |

| 3BD7h            | DMA2SSZL               |       |        |           | SS      | SZ     |        |       |       | 252                 |  |

| 3BD6h            | DMA2SPTRU              | _     | _      |           |         | S      | SPTR   |       |       | 252                 |  |

| 3BD5h            | DMA2SPTRH              |       |        |           | SP      | TR     |        |       |       | 251                 |  |

| 3BD4h            | DMA2SPTRL              |       |        |           | SP      | TR     |        |       |       | 251                 |  |

| 3BD3h            | DMA2SCNTH              | —     | _      | _         | —       |        | S      | CNT   |       | 253                 |  |

| 3BD2h            | DMA2SCNTL              |       |        |           | SC      | NT     |        |       |       | 253                 |  |

| 3BD1h            | DMA2DSAH               |       |        |           | DS      | SA     |        |       |       | 254                 |  |

| 3BD0h            | DMA2DSAL               |       |        |           | SS      | SA     |        |       |       | 253                 |  |

| 3BCFh            | DMA2DSZH               | _     | _      |           |         |        | C      | SZ    |       | 255                 |  |

| 3BCEh            | DMA2DSZL               |       |        |           | DS      | SZ     |        |       |       | 255                 |  |

| 3BCDh            | DMA2DPTRH              |       |        |           | DP      | TR     |        |       |       | 254                 |  |

| 3BCCh            | DMA2DPTRL              |       |        |           | DP      | TR     |        |       |       | 254                 |  |

|                  | DMAODONITU             |       | _      | _         | _       |        | D      | CNT   |       | 256                 |  |

| 3BCBh            | DMA2DCNTH              |       |        |           |         |        |        |       |       |                     |  |

| 3BCBh<br>3BCAh   | DMA2DCNTH<br>DMA2DCNTL |       |        |           | DC      | NT     |        |       |       | 255                 |  |

#### TABLE 42-1:REGISTER FILE SUMMARY FOR PIC18(L)F26/27/45/46/47/55/56/57K42 DEVICES

Legend: x = unknown, u = unchanged, — = unimplemented, q = value depends on condition

Note 1: Unimplemented in LF devices.

2: Unimplemented in PIC18(L)F26/27K42.

3: Unimplemented on PIC18(L)F26/27/45/46/47K42 devices.

4: Unimplemented in PIC18(L)F45/55K42.

### TABLE 44-15: ANALOG-TO-DIGITAL CONVERTER (ADC) ACCURACY SPECIFICATIONS<sup>(1,2)</sup>:

| <mark>Operating Conditions (unless otherwise stated)</mark><br>VDD = 3.0V, TA = 25°C, TAD = 1μs |        |                                                   |        |      |        |       |                                   |

|-------------------------------------------------------------------------------------------------|--------|---------------------------------------------------|--------|------|--------|-------|-----------------------------------|

| Param<br>No.                                                                                    | Sym.   | Characteristic                                    | Min.   | Тур† | Max.   | Units | Conditions                        |

| AD01                                                                                            | NR     | Resolution                                        | —      | _    | 12     | bit   | $\wedge$                          |

| AD02                                                                                            | EIL    | Integral Error                                    | _      | ±0.1 | ±2.0   | LSb   | ADCREF+ = 3.0V, ADCREF- $\neq 0$  |

| AD03                                                                                            | Edl    | Differential Error                                | _      | ±0.1 | ±1.0   | LSb   | ADCREF+ = 3.0V, ADCREF-= $\rho V$ |

| AD04                                                                                            | EOFF   | Offset Error                                      | _      | 0.5  | 6.0    | LSb   | ADCREF+ = 3.0V, ADCREF-= 0V       |

| AD05                                                                                            | Egn    | Gain Error                                        | _      | ±0.2 | ±6.0   | LSb   | ADCREF+ = 3.0V, ADCREF-= 0V       |

| AD06                                                                                            | VADREF | ADC Reference Voltage<br>(ADREF+ - ADREF-)        | 1.8    |      | Vdd    | V     |                                   |

| AD07                                                                                            | VAIN   | Full-Scale Range                                  | ADREF- | _    | ADREF+ | V     |                                   |

| AD08                                                                                            | Zain   | Recommended Impedance of<br>Analog Voltage Source | —      | 1    | —      | kΩ    |                                   |

| AD09                                                                                            | Rvref  | ADC Voltage Reference Ladder<br>Impedance         | —      | 50   | —      | kΩ    | Note 3                            |

\* These parameters are characterized but not tested.

+ Data in "Typ" column is at 3.0V, 25°C unless otherwise stated. These parameters are for design guidance only and are not tested.

Note 1: Total Absolute Error is the sum of the offset, gain and integral non-linearity (INL) errors.

2: The ADC conversion result never decreases with an increase in the input and has no missing codes.

3: This is the impedance seen by the VREF pads when the external reference pads are selected.

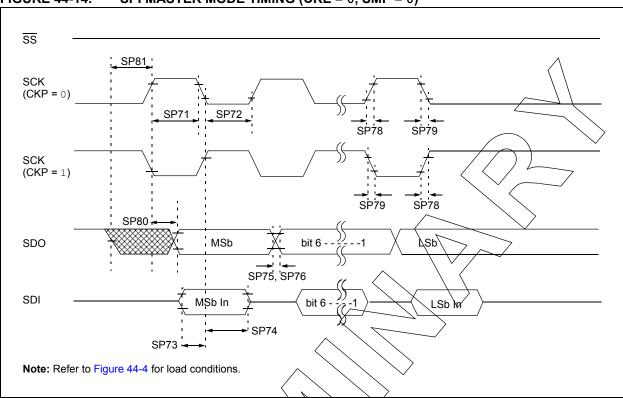

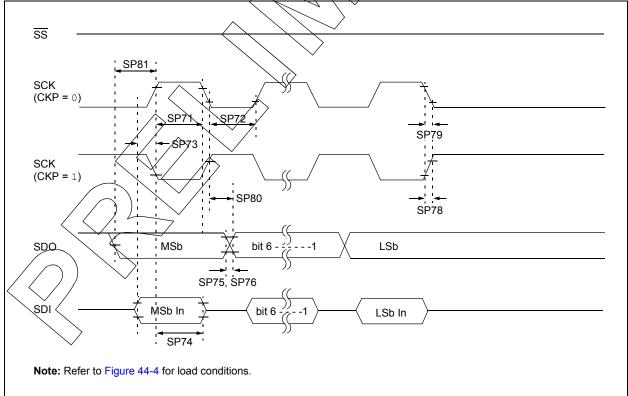

#### FIGURE 44-14: SPI MASTER MODE TIMING (CKE = 0, SMP = 0)

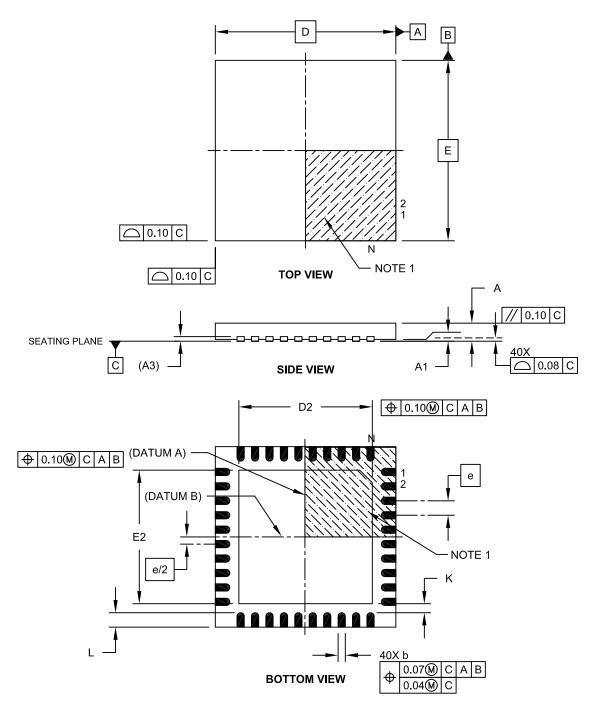

### 40-Lead Ultra Thin Plastic Quad Flat, No Lead Package (MV) – 5x5x0.5 mm Body [UQFN]

Microchip Technology Drawing C04-156A Sheet 1 of 2