Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Details                    |                                                                            |

|----------------------------|----------------------------------------------------------------------------|

| Product Status             | Active                                                                     |

| Core Processor             | PIC                                                                        |

| Core Size                  | 8-Bit                                                                      |

| Speed                      | 64MHz                                                                      |

| Connectivity               | I <sup>2</sup> C, LINbus, SPI, UART/USART                                  |

| Peripherals                | Brown-out Detect/Reset, DMA, HLVD, POR, PWM, WDT                           |

| Number of I/O              | 25                                                                         |

| Program Memory Size        | 64KB (32K x 16)                                                            |

| Program Memory Type        | FLASH                                                                      |

| EEPROM Size                | 1K x 8                                                                     |

| RAM Size                   | 4K x 8                                                                     |

| Voltage - Supply (Vcc/Vdd) | 2.3V ~ 5.5V                                                                |

| Data Converters            | A/D 24x12b; D/A 1x5b                                                       |

| Oscillator Type            | Internal                                                                   |

| Operating Temperature      | -40°C ~ 125°C (TA)                                                         |

| Mounting Type              | Surface Mount                                                              |

| Package / Case             | 28-SSOP (0.209", 5.30mm Width)                                             |

| Supplier Device Package    | 28-SSOP                                                                    |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/pic18f26k42-e-ss |

|                            |                                                                            |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

### TABLE 4-4: SPECIAL FUNCTION REGISTER MAP FOR PIC18(L)F26/27/45/46/47/55/56/57K42 DEVICES BANK 63

| 3FFPh         TOSU         3FDrh         LINDF2         3FBrh         LATE <sup>10</sup> 3FPrh         TAPR         3F7Fb         CCPTCAP         3F3Fb         NCO1CLK         3F1Fh         SMT1CONI           3FFEn         TOSL         3FDDr         POSTDEC2         3FBDr         LATE <sup>10</sup> 3F90h         TSCLK         3F7Dr         CCPTMRS0         3F8Eh         CCOTMCU         3F1Dr         SMT1CONI           3FFCh         STRPTR         3FDDr         POSTDEC2         3FBH         LATE         3F90h         TSCATE         3F7Dr         CCPR1H         3F5Dr                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | _     |          |       |                      |       |                     |       |        |       |         |       |          |       |          | _     |          |

|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------|----------|-------|----------------------|-------|---------------------|-------|--------|-------|---------|-------|----------|-------|----------|-------|----------|

| 3FFDR         TOSL         3FDDR         POSTDEC2         3FBDR         LATD <sup>12/1</sup> 3F9DR         TSCLK         3F7DR         CCPR1H         3F5DR         3F3DR         NCOTINCU         3F1DR         SMTTPRU           3FFBR         POLATU         3FDC         PRECINZ         3F9C/L         CCPR1L         3F2C/L         CCPR1L         3F2C/L         SF3DR         CCPCAP         3F3DR         NCOTINCU         3F1BR         SF1DR         SF1DR         SF2C/L         SF3DR         CCPR1L         3F2C/L         SF3DR         SF1DR         SF3DR         SF3DR         SF3DR         CCPR2L         3F3DR         NCOTINCU         3F1DR         SF1DR                                                                                                                                                                                                                                | 3FFFh | TOSU     | 3FDFh | INDF2                | 3FBFh | LATF <sup>(3)</sup> | 3F9Fh | T4PR   | 3F7Fh | CCP1CAP | 3F5Fh | CCPTMRS1 | 3F3Fh | NCO1CLK  | 3F1Fh | SMT1CON1 |

| 3FFch         STKPTR         SFCh         PECIN2         3FECh         LATC         SFCh         TSGCON         SFCh         CCPRL         3FECh         —         SFCh         MCO1NCH         3F1ch         SMT1PRH           3FFAB         PCLATU         3FDAA         FSR2H         3FBAB         LATA         3F9AF         TSGCON         3F7Ah         CCP2CAP         3F5Ah         NCO1NCH         3F1Ah         SMT1PRH           3FFAB         PCLATH         3FDAA         FSR2L         3FBB         TOCON1         3F9BH         TMRSH         3F7Ah         CCP2CON         3F5Ah         NCO1ACCH         3F19H         SMT1CPWL           3FFAB         TBLPTRH         3FDAH         IATA         3F9AH         TMRSH         3F7Ah         CCP2CAN         3F5Ah         NCO1ACCH         3F19H         SMT1CPWL           3FFAH         TBLPTRH         3FDAH         INTASEH         3F7Ah         CCP3CAN         3F5Ah         CWG1ASU         3F3Ah         NCO1ACCH         3F19H         SMT1CPRL           3FFAH         TBLPTRH         3FDAH         INTASEH         3F7Ah         CCP3CAN         3F5Ah         CWG1OND         3F3Ah         -         3F17h         SMT1TMRH         SF5h         CWG1DBF         <                                                                                                                                                                                                                                                          | 3FFEh | TOSH     | 3FDEh | POSTINC2             | 3FBEh | ==                  | 3F9Eh | T4TMR  | 3F7Eh | CCP1CON | 3F5Eh | CCPTMRS0 | 3F3Eh | NCO1CON  | 3F1Eh | SMT1CON0 |

| 3FFBR         PCLATU         3F0BR         FULSW2         3F6BR         LATB         3F6BR         CCP2CAP         3F6BR         —         3F3BR         NCO1IACCL         3F1BR         SMT1PRL           3FFAR         PCLATH         3FDAR         FSR2L         3F6BR         LATA         367AR         TGCON         3F7AR         CCP2CON         3F5AR         CWG1AS1         3F3BR         NCO1ACCL         3F1AR         SMT1PRU           3FFAR         TBLPRTU         3FD9R         STATUS         3FBBR         TMRSL         3F7AR         CCPR2L         3F5BR         CWG1AS0         3F3BR         NCO1ACCL         3F1BR         SMT1PRU           3FFAR         TBLPTRH         3FDAR         VTBASEL         3FBR         TMROL         3F9R         TGRST         3F5AR         CCP3CAP         3F5AR         CWG1AS1         3F3BR         NCO1ACCL         3F1BR         SMT1PRL           3FF6R         TBLPTRL         3FD6R         VTBASEL         3F8BR         TMROL         3F9R         TGRST         3F5AR         CWG1AS1         3F3BR         NCO1ACCL         3F1BR         SMT1PRL           3FF6R         TBLPTRL         3FD6R         VTBASEL         3F6BR         TGRST         SF5AR         CWG1AS1                                                                                                                                                                                                                                                             | 3FFDh | TOSL     | 3FDDh | POSTDEC2             | 3FBDh | LATD <sup>(2)</sup> | 3F9Dh | T5CLK  | 3F7Dh | CCPR1H  | 3F5Dh | —        | 3F3Dh | NCO1INCU | 3F1Dh | SMT1PRU  |

| 3FFAR         PCLATH         3FDAR         FSR2H         3FBAR         LATA         3F9AR         TGCON         3F7AR         CCP2CON         3F5AR         CWG1AST         3F3AR         NC01ACCU         3F1AR         SMT1CPWU           3FF8R         TBLPRTU         3FD9BR         TATUS         3F9BR         TOCON0         3F99R         TMR8H         3F79R         CCPR2L         3F59R         CWG1AST         3F39R         NC01ACCU         3F19R         SMT1CPWU           3FF8R         TBLPTRH         3FD0R         TVTBASEU         3FB7         TMR0H         3F97F         TGRST         3F77R         CCP3CAP         3F57R         CWG1C0N1         3F37R         -         3F16R         SMT1CPWU           3FF6R         TBLPTRL         3FD6R         TVTBASEU         3F86F         TMR0L         3F96F         T6CLK         3F76R         CCP3CAP         3F57R         CWG1DBR         3F34R         -         3F16R         SMT1CPWU           3FF6R         TBLPTRL         3FD6H         TVTBASEU         3F86F         TMR0L         3F96F         TMCLK         3F76R         CCP3CAP         3F53R         CWG1DBR         3F34R         -         3F16R         SMT1CPWL           3FF6R         TBODH                                                                                                                                                                                                                                                                  | 3FFCh | STKPTR   | 3FDCh | PRECIN2              | 3FBCh | LATC                | 3F9Ch | T5GATE | 3F7Ch | CCPR1L  | 3F5Ch | —        | 3F3Ch | NCO1INCH | 3F1Ch | SMT1PRH  |

| SF9n         PCL         SF0n         FSR2L         SF9n         TOCON1         SF9n         TMREH         SF9n         CCPR2H         SF9n         CWG1AS1         SF3n         NCO1ACCH         SF1n         SMT1CPWL           3FF8n         TBLPTRH         3F00n         STATUS         SF8n         TMROH         3F9n         TGRST         3F7n         CCPR2L         3F5n         CWG1AS0         3F3n                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | 3FFBh | PCLATU   | 3FDBh | PLUSW2               | 3FBBh | LATB                | 3F9Bh | T5GCON | 3F7Bh | CCP2CAP | 3F5Bh | —        | 3F3Bh | NCO1INCL | 3F1Bh | SMT1PRL  |

| 3FF8h         TBLPRTU         3FD8h         STATUS         3FB8h         TOCON0         3F98h         TMREL         3F78h         CCCPR2L         3F68h         CWG1ASO         3F38h         NCO1ACCL         3F18h         SMT1CPWL           3FF7h         TBLPTRH         3FD6h         NTBASEL         3F66h         TMROL         3F96h         TGCLK         3F76h         CCP3CAP         3F55h         CWG1C0N0         3F36h         —         3F16h         SMT1CPRU           3FF6h         TABLAT         3FD6h         NTBASEL         3F68h         T1CLK         3F96h         T6CLX         3F76h         CCP3CAP         3F55h         CWG1DBF         3F35h         —         3F16h         SMT1CPRL           3FF3h         TBADA         VTLOCK         3F84h         T1GCNN         3F93h         T6PR         3F73h         CCP4CAP         3F53h         CWG1DBF         3F3h         —         3F11h         SMT1TRRL           3FF3h         PRODL         3FD3h         INTCON1         3F82h         T1GCNN         3F93h         T6PR         3F73h         CCP4CAP         3F53h         CWG1LK         3F32h         —         3F11h         SMT1TRRL           3FF0h         PCON1         3FD1h         TMR1H </td <td>3FFAh</td> <td>PCLATH</td> <td>3FDAh</td> <td>FSR2H</td> <td>3FBAh</td> <td>LATA</td> <td>3F9Ah</td> <td>T5CON</td> <td>3F7Ah</td> <td>CCP2CON</td> <td>3F5Ah</td> <td>CWG1STR</td> <td>3F3Ah</td> <td>NCO1ACCU</td> <td>3F1Ah</td> <td>SMT1CPWU</td> | 3FFAh | PCLATH   | 3FDAh | FSR2H                | 3FBAh | LATA                | 3F9Ah | T5CON  | 3F7Ah | CCP2CON | 3F5Ah | CWG1STR  | 3F3Ah | NCO1ACCU | 3F1Ah | SMT1CPWU |

| 3FF/h         TBLPTRH         3FD/h         IVTBASEU         3FB/h         TMR0H         3F9/h         T6RST         3F7/h         CCP3CAP         3F5/h         CWG1CON1         3F3/h                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | 3FF9h | PCL      | 3FD9h | FSR2L                | 3FB9h | T0CON1              | 3F99h | TMR5H  | 3F79h | CCPR2H  | 3F59h | CWG1AS1  | 3F39h | NCO1ACCH | 3F19h | SMT1CPWH |

| 3FF6h         TBLPTRL         3F0h         IVTBASEL         3F6h         TMR0L         3F9h         T6CLK         3F7h         CCP3CON         3F6h         CWG1CON0         3F3h                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | 3FF8h | TBLPRTU  | 3FD8h | STATUS               | 3FB8h | T0CON0              | 3F98h | TMR5L  | 3F78h | CCPR2L  | 3F58h | CWG1AS0  | 3F38h | NCO1ACCL | 3F18h | SMT1CPWL |

| 3FF5h       TABLAT       3FD5h       IVTBASEL       3FB5h       T1CLK       3F95h       T6HLT       3F75h       CCPR3H       3F55h       CWG1DBF       3F35h       —       3F15h       SMT1CPRL         3FF3h       PRODH       3FD3h       INTCON1       3FB3h       T1GC0N       3F93h       T6PR       3F73h       CCP4C0N       3F33h       —       3F13h       SMT1TMRU         3FF3h       PRODL       3FD3h       INTCON0       3FB3h       T1GCN       3F93h       T6PR       3F73h       CCP4CON       3F53h       —       3F13h       SMT1TMRU         3FF3h       PCON1       3FD1h       —       3FB1h       TMR1H       3F93h       —       3F71h       CCP4CON       3F51h       CWG1CLK       3F32h       —       3F12h       SMT1TMRU         3FF1h       PCON1       3FD1h       —       3F60h       T1R1L       3F90h       —       3F70h       CCP4CON       3F51h       CWG2STR       3F30h       —       3F12h       SMT1TMRU         3FF1h       PCON1       3FD1h       —       3F60h       T1R1L       3F90h       —       3F70h       CCP4CON       3F2h       —       3F0h       —       3F0h       —       3F0h <td>3FF7h</td> <td>TBLPTRH</td> <td>3FD7h</td> <td>IVTBASEU</td> <td>3FB7h</td> <td>TMR0H</td> <td>3F97h</td> <td>T6RST</td> <td>3F77h</td> <td>CCP3CAP</td> <td>3F57h</td> <td>CWG1CON1</td> <td>3F37h</td> <td>—</td> <td>3F17h</td> <td>SMT1CPRU</td>                                                                                                           | 3FF7h | TBLPTRH  | 3FD7h | IVTBASEU             | 3FB7h | TMR0H               | 3F97h | T6RST  | 3F77h | CCP3CAP | 3F57h | CWG1CON1 | 3F37h | —        | 3F17h | SMT1CPRU |

| 3FF4h         PRODH         3F04h         IVTLOCK         3F84h         T1GATE         3F94h         T6CON         3F74h         CCPR3L         3F54h         CWG1DBR         3F34h                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | 3FF6h | TBLPTRL  | 3FD6h | IVTBASEH             | 3FB6h | TMR0L               | 3F96h | T6CLK  | 3F76h | CCP3CON | 3F56h | CWG1CON0 | 3F36h | —        | 3F16h | SMT1CPRH |

| 3FF3h         PRODL         3FD3h         INTCON1         3FB3h         T1GCON         3F93h         T6PR         3F73h         CCP4CAP         3F53h         CWG1ISM         3F33h                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | 3FF5h | TABLAT   | 3FD5h | IVTBASEL             | 3FB5h | T1CLK               | 3F95h | T6HLT  | 3F75h | CCPR3H  | 3F55h | CWG1DBF  | 3F35h | —        | 3F15h | SMT1CPRL |

| 3FP2h                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | 3FF4h | PRODH    | 3FD4h | IVTLOCK              | 3FB4h | T1GATE              | 3F94h | T6CON  | 3F74h | CCPR3L  | 3F54h | CWG1DBR  | 3F34h | —        | 3F14h | SMT1TMRU |

| 3FF1h       PCON1       3F01h                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | 3FF3h | PRODL    | 3FD3h | INTCON1              | 3FB3h | T1GCON              | 3F93h | T6PR   | 3F73h | CCP4CAP | 3F53h | CWG1ISM  | 3F33h | —        | 3F13h | SMT1TMRH |

| 3FF0h       PCON0       3FD0h       —       3F80h       TMR1L       3F90h       —       3F70h       CCPR4L       3F50h       CWG2AS1       3F30h       —       3F10h       —         3FEFh       INDF0       3FCFh       PORTF <sup>[3]</sup> 3FAFh       T2RST       3F8Fh       —       3F6Fh       —       3F4Fh       CWG2AS0       3F2Fh       —       3F0h       —       3F4Fh       CWG2AS1       3F30h       —       3F0h       —       3F0h       —       3F0h       —       3F0h       —       3F4Fh       CWG2CON1       3F2Fh       —       3F0h       —       3F0h       —       3F0h       —       3F6h       PWM5DCH       3F4h       CWG2CON1       3F2ch       —       3F0h       —       3F0h       —       3F0h       —       3F6h       PWM5DCH       3F4h       CWG2DBF       3F2h       —       3F0h       —       3F0h       —       3F6h       PWM5DCH       3F4h       CWG2DBF       3F2h       —       3F0h       …       3F6h       …       3F4Bh       CWG2DBF       3F2h       …                                                                                                                                                                                                                                                                                                                                                                               | 3FF2h | —        | 3FD2h | INTCON0              | 3FB2h | T1CON               | 3F92h | T6TMR  | 3F72h | CCP4CON | 3F52h | CWG1CLK  | 3F32h | —        | 3F12h | SMT1TMRL |

| 3FEFh       INDF0       3FCFh       PORTF <sup>(3)</sup> 3FAFh       T2RST       3F8Fh       -       3F6Fh       -       3F4Fh       CWG2AS0       3F2Fh       -       3F0Fh       -         3FEEh       POSTINC0       3FCEh       PORTE       3FAEh       T2CLK       3F8Eh       -       3F6Eh       PWM5CON       3F4Eh       CWG2CON1       3F2Fh       -       3F0Eh       -         3FEDh       POSTDEC0       3FCDh       PORTD <sup>(2)</sup> 3FACh       T2LLT       3F8Dh       -       3F6Ch       PWM5DCH       3F4Ch       CWG2CON0       3F2Dh       -       3F0Dh       -         3FEDh       PORTD       3FACh       T2CN       3F8Ch       -       3F6Ch       PWM5DCH       3F4Ch       CWG2DBF       3F2Dh       -       3F0Dh       -                                                                                                                                                                                                                                                                                                                                                                            | 3FF1h | PCON1    | 3FD1h | —                    | 3FB1h | TMR1H               | 3F91h | —      | 3F71h | CCPR4H  | 3F51h | CWG2STR  | 3F31h | —        | 3F11h | —        |

| 3FEEh       POSTINC0       3FCh       PORTE       3FAEh       T2CLK       3F8Eh       -       3F6Eh       PWM5CON       3F4Eh       CWG2CON1       3F2Eh       -       3F0Eh       -         3FEDh       POSTDEC0       3FCDh       PORTD <sup>[2]</sup> 3FADh       T2HLT       3F8Dh       -       3F6Dh       PWM5DCH       3F4Dh       CWG2CON0       3F2Dh       -       3F0Dh       -         3FECh       PRECIN0       3FCCh       PORTC       3FACh       T2CON       3F8Ch       -       3F6Ch       PWM5DCL       3F4Ch       CWG2DBF       3F2Dh       -       3F0Dh       -         3FEBh       PLUSW0       3FCAh       PORTB       3FABh       T2PR       3F8Bh       -       3F6Bh       -       3F4Bh       CWG2DBR       3F2Ah       -       3F0Bh       -       3F6Bh       -       3F4Bh       CWG2DBR       3F2Ah       -       3F0Bh       -       3F6Bh       - </td <td>3FF0h</td> <td>PCON0</td> <td>3FD0h</td> <td>—</td> <td>3FB0h</td> <td>TMR1L</td> <td>3F90h</td> <td>—</td> <td>3F70h</td> <td>CCPR4L</td> <td>3F50h</td> <td>CWG2AS1</td> <td>3F30h</td> <td>—</td> <td>3F10h</td> <td>—</td>                                                                                                                                 | 3FF0h | PCON0    | 3FD0h | —                    | 3FB0h | TMR1L               | 3F90h | —      | 3F70h | CCPR4L  | 3F50h | CWG2AS1  | 3F30h | —        | 3F10h | —        |

| 3FEDh       POSTDEC0       3FCDh       PORTD <sup>(2)</sup> 3FADh       T2HLT       3F8Dh       —       3F6Dh       PWM5DCH       3F4Dh       CWG2CON0       3F2Dh       —       3F0Dh       —         3FECh       PRECIN0       3FCCh       PORTC       3FACh       T2CON       3F8Ch       —       3F6Ch       PWM5DCL       3F4Ch       CWG2DBF       3F2Dh       —       3F0Dh       —         3FEBh       PLUSW0       3FCBh       PORTB       3FABh       T2PR       3F8Bh       —       3F6Bh       —       3F4Bh       CWG2DBF       3F2Dh       —       3F0Dh       —         3FEAh       FSR0H       3FCAh       PORTA       3FAAh       T2TMR       3F8Ah       —       3F6Ah       PWM6CON       3F4Ah       CWG2DBR       3F2Ah       —       3F0Ah       —       3F0Ah       —       3F6Ah       PWM6CON       3F4Ah       CWG2DSM       3F2Ah       —       3F0Ah       —       3F0Ah       —       3F6Bh       —       3F6Ah       PWM6DCL       3F4Ah       CWG3DSTR       3F2Ah       —       3F0Ah       —       3F0Ah       —       3F6Bh       PWM6DCL       3F4Ah       CWG3STR       3F2Ah       —       3F0Ah       —                                                                                                                                                                                                                                                                                                                                                                 | 3FEFh | INDF0    | 3FCFh | PORTF <sup>(3)</sup> | 3FAFh | T2RST               | 3F8Fh | —      | 3F6Fh | —       | 3F4Fh | CWG2AS0  | 3F2Fh | —        | 3F0Fh | —        |

| 3FECh       PRECINO       3FCch       PORTC       3FACh       T2CON       3F8Ch       —       3F6Ch       PWM5DCL       3F4Ch       CWG2DBF       3F2Ch       —       3F0Ch       —         3FEBh       PLUSW0       3FCBh       PORTB       3FABh       T2PR       3F8Bh       —       3F6Bh       —       3F4Bh       CWG2DBF       3F2Bh       —       3F0Bh       —       3F0Bh       —       3F0Bh       —       3F4Bh       CWG2DBR       3F2Bh       —       3F0Bh       —       3F0Bh       —       3F6Bh       —       3F6Bh       —       3F6Bh       —       3F4Bh       CWG2DBR       3F2Bh       —       3F0Bh       —       3F6Bh       PWM6DCL       3F4Bh       CWG2DLK       3F2Bh       —       3F0Bh       —       3F6Bh       —       3F6Bh       PWM6DCL       3F4Bh       CWG3DSTR       3F2Bh       …       3F0Bh       …       3F6Bh       …       3F6Bh       PWM6DCL       3F4Bh       CWG3AS1       3F2                                                                                                                                                                                                                                                                                                                                                                    | 3FEEh | POSTINC0 | 3FCEh | PORTE                | 3FAEh | T2CLK               | 3F8Eh | —      | 3F6Eh | PWM5CON | 3F4Eh | CWG2CON1 | 3F2Eh | —        | 3F0Eh | —        |

| 3FEBh       PLUSW0       3FCBh       PORTB       3FABh       T2PR       3F8Bh       -       3F6Bh       -       3F4Bh       CWG2DBR       3F2Bh       -       3F0Bh       -         3FEAh       FSR0H       3FCAh       PORTA       3FAAh       T2TMR       3F8Ah       -       3F6Ah       PWM6CON       3F4Ah       CWG2DBR       3F2Bh       -       3F0Ah                                                                                                                                                                                                                                                                                                                                                                                                 | 3FEDh | POSTDEC0 | 3FCDh | PORTD <sup>(2)</sup> | 3FADh | T2HLT               | 3F8Dh | —      | 3F6Dh | PWM5DCH | 3F4Dh | CWG2CON0 | 3F2Dh | —        | 3F0Dh | —        |

| 3FEAh       FSR0H       3FCAh       PORTA       3FAAh       T2TMR       3F8Ah       -       3F6Ah       PWM6CON       3F4Ah       CWG2ISM       3F2Ah       -       3F0Ah       -       3F0Ah       -       3F6Ah       PWM6CON       3F4Ah       CWG2ISM       3F2Ah       -       3F0Ah       -       3F0Ah       -       3F6Ah       PWM6DCH       3F4Ah       CWG2ISM       3F2Ah       -       3F0Ah       -       3F0Ah       -       3F0Ah       -       3F6Ah       PWM6DCH       3F4Ah       CWG2ISM       3F2Ah       -       3F0Ah       -       3F0Ah       -       3F0Ah       -       3F0Ah       -       3F0Ah       -       3F0Ah       -       3F6Ah       PWM6DCH       3F4Ah       CWG3CIK       3F2Ah       -       3F0Ah       -       3F0Ah       -       3F6Ah       PWM6DCL       3F4Ah       CWG3STR       3F2Ah       -       3F0Ah       -       3F6Ah       PWM6DCL       3F4Ah       CWG3STR       3F2Ah       -       3F0Ah       -       3F6Ah       -       3F6Ah       PWM7DCN       3F4Ah       CWG3AS0       3F2Ah       -       3F0Ah       -       3F6Ah       PWM7DCH       3F4Ah       CWG3CON1       3F2Ah       -                                                                                                                                                                                                                                                                                                                                                    | 3FECh | PRECIN0  | 3FCCh | PORTC                | 3FACh | T2CON               | 3F8Ch | —      | 3F6Ch | PWM5DCL | 3F4Ch | CWG2DBF  | 3F2Ch | —        | 3F0Ch | —        |

| 3FE9h       FSR0L       3FC9h       —       3FA9h       T3CLK       3F89h       —       3F69h       PWM6DCH       3F49h       CWG2CLK       3F29h       —       3F09h       —         3FE8h       WREG       3FC8h       —       3FA8h       T3GATE       3F88h       —       3F68h       PWM6DCL       3F48h       CWG3STR       3F28h       —       3F08h       …       3F08h       …       3F08h       <                                                                                                                                                                                                                                                                                                                                                                                           | 3FEBh | PLUSW0   | 3FCBh | PORTB                | 3FABh | T2PR                | 3F8Bh | —      | 3F6Bh | —       | 3F4Bh | CWG2DBR  | 3F2Bh | —        | 3F0Bh | —        |

| 3FE8h         WREG         3FC8h         —         3FA8h         T3GATE         3F88h         —         3F68h         PWM6DCL         3F48h         CWG3STR         3F28h         —         3F08h         —           3FE7h         INDF1         3FC7h         TRISF <sup>(3)</sup> 3FA7h         T3GC0N         3F87h         —         3F67h         —         3F47h         CWG3STR         3F28h         —         3F07h         —           3FE6h         POSTINC1         3FC6h         TRISE <sup>(2)</sup> 3FA6h         T3CON         3F86h         —         3F66h         PWM7CON         3F46h         CWG3AS0         3F26h         —         3F06h         —           3FE5h         POSTDEC1         3FC5h         TRISD <sup>(2)</sup> 3FA6h         TMR3H         3F85h         —         3F65h         PWM7CON         3F46h         CWG3AS0         3F26h         —         3F05h         —           3FE4h         PRECIN1         3FC4h         TRISC         3FA4h         TMR3L         3F84h         —         3F64h         PWM7DCL         3F44h         CWG3CON0         3F24h         —         3F04h         —           3FE3h         PLUSW1         3FC3h         TRISB         3FA3h         <                                                                                                                                                                                                                                                                               | 3FEAh | FSR0H    | 3FCAh | PORTA                | 3FAAh | T2TMR               | 3F8Ah | —      | 3F6Ah | PWM6CON | 3F4Ah | CWG2ISM  | 3F2Ah | —        | 3F0Ah | —        |

| 3FE7h         INDF1         3FC7h         TRISF <sup>(3)</sup> 3FA7h         T3GCON         3F87h         —         3F67h         —         3F47h         CWG3AS1         3F27h         —         3F07h         —           3FE6h         POSTINC1         3FC6h         TRISE <sup>(2)</sup> 3FA6h         T3CON         3F86h         —         3F66h         PWM7CON         3F46h         CWG3AS0         3F26h         —         3F06h         —           3FE5h         POSTDEC1         3FC5h         TRISD <sup>(2)</sup> 3FA5h         TMR3H         3F85h         —         3F65h         PWM7DCH         3F45h         CWG3AS0         3F26h         —         3F05h         —           3FE4h         PRECIN1         3FC4h         TRISC         3FA4h         TMR3L         3F84h         —         3F64h         PWM7DCL         3F44h         CWG3CON0         3F24h         —         3F04h         —           3FE3h         PLUSW1         3FC3h         TRISB         3FA3h         T4RST         3F83h         —         3F63h                                                                                                                                                                                                                                                                                   | 3FE9h | FSR0L    |       | _                    | 3FA9h |                     | 3F89h | _      | 3F69h | PWM6DCH | 3F49h | CWG2CLK  |       | _        | 3F09h | _        |

| 3FE6h         POSTINC1         3FC6h         TRISE <sup>(2)</sup> 3FA6h         T3CON         3F86h         —         3F66h         PWM7CON         3F46h         CWG3AS0         3F26h         —         3F06h         —           3F55h         POSTDEC1         3FC5h         TRISD <sup>(2)</sup> 3FA5h         TMR3H         3F85h         —         3F65h         PWM7DCH         3F45h         CWG3AS0         3F26h         —         3F05h         —           3FE4h         PRECIN1         3FC4h         TRISC         3FA4h         TMR3L         3F84h         —         3F64h         PWM7DCL         3F44h         CWG3CON0         3F24h         —         3F04h         —           3FE3h         PLUSW1         3FC3h         TRISB         3FA3h         T4RST         3F83h         —         3F63h                                                                                                                                                                                                                                                                                       | 3FE8h | WREG     | 3FC8h |                      | 3FA8h | T3GATE              | 3F88h | _      | 3F68h | PWM6DCL | 3F48h | CWG3STR  |       | _        | 3F08h | _        |

| 3FE5h         POSTDEC1         3FC5h         TRISD <sup>(2)</sup> 3FA5h         TMR3H         3F85h         —         3F65h         PWM7DCH         3F45h         CWG3CON1         3F25h         —         3F05h         —           3FE4h         PRECIN1         3FC4h         TRISC         3FA4h         TMR3L         3F84h         —         3F64h         PWM7DCL         3F44h         CWG3CON0         3F24h         —         3F04h         —           3FE3h         PLUSW1         3FC3h         TRISB         3FA3h         T4RST         3F83h         —         3F63h         —         3F63h         GWG3DBF         3F23h         SMT1WIN         3F03h         —           3FE2h         FSR1H         3FC2h         TRISA         3FA2h         T4CLK         3F82h         —         3F62h         PWM8CON         3F42h         CWG3DBR         3F22h         SMT1SIG         3F02h         —                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | 3FE7h | INDF1    | 3FC7h |                      | 3FA7h | T3GCON              | 3F87h | —      | 3F67h | —       | 3F47h | CWG3AS1  | 3F27h | —        | 3F07h | —        |

| 3FE4h         PRECIN1         3FC4h         TRISC         3FA4h         TMR3L         3F84h         —         3F64h         PWM7DCL         3F44h         CWG3CON0         3F24h         —         3F04h         —           3FE3h         PLUSW1         3FC3h         TRISB         3FA3h         T4RST         3F83h         —         3F63h         —         3F63h         CWG3DBF         3F23h         SMT1WIN         3F03h         —           3FE2h         FSR1H         3FC2h         TRISA         3FA2h         T4CLK         3F82h         —         3F62h         PWM8CON         3F42h         CWG3DBR         3F22h         SMT1SIG         3F02h         —                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | 3FE6h | POSTINC1 | 3FC6h | TRISE <sup>(2)</sup> | 3FA6h | T3CON               | 3F86h | —      | 3F66h | PWM7CON | 3F46h | CWG3AS0  | 3F26h | —        | 3F06h | —        |

| 3FE3h         PLUSW1         3FC3h         TRISB         3FA3h         T4RST         3F83h          3F63h          3F43h         CWG3DBF         3F23h         SMT1WIN         3F03h            3FE2h         FSR1H         3FC2h         TRISA         3FA2h         T4CLK         3F82h          3F62h         PWM8CON         3F42h         CWG3DBR         3F22h         SMT1SIG         3F02h                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | 3FE5h | POSTDEC1 | 3FC5h | TRISD <sup>(2)</sup> | 3FA5h | TMR3H               | 3F85h | —      | 3F65h | PWM7DCH | 3F45h | CWG3CON1 | 3F25h | —        | 3F05h | —        |

| 3FE2h FSR1H 3FC2h TRISA 3FA2h T4CLK 3F82h — 3F62h PWM8CON 3F42h CWG3DBR 3F22h SMT1SIG 3F02h —                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | 3FE4h | PRECIN1  | 3FC4h | TRISC                | 3FA4h | TMR3L               | 3F84h | —      | 3F64h | PWM7DCL | 3F44h | CWG3CON0 | 3F24h | —        | 3F04h | —        |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | 3FE3h | PLUSW1   |       | TRISB                | 3FA3h | T4RST               | 3F83h | _      | 3F63h | _       | 3F43h | CWG3DBF  | 3F23h | SMT1WIN  | 3F03h | —        |

| 3FE1h FSR1L 3FC1h — 3FA1h T4HLT 3F81h — 3F61h PWM8DCH 3F41h CWG3ISM 3F21h SMT1CLK 3F01h —                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | 3FE2h | FSR1H    | 3FC2h | TRISA                | 3FA2h | -                   | 3F82h | _      | 3F62h |         | 3F42h | CWG3DBR  | 3F22h | SMT1SIG  | 3F02h | —        |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | -     | -        |       | _                    | 3FA1h |                     | 3F81h | _      | 3F61h | PWM8DCH |       | CWG3ISM  | 3F21h | SMT1CLK  | 3F01h | _        |

| 3FE0h BSR 3FC0h — 3FA0h T4CON 3F80h — 3F60h PWM8DCL 3F40h CWG3CLK 3F20h SMT1STAT 3F00h —                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | 3FE0h | -        |       |                      | 3FA0h | T4CON               | 3F80h | _      | 3F60h | PWM8DCL | 3F40h | CWG3CLK  | 3F20h | SMT1STAT | 3F00h | —        |

Legend: Unimplemented data memory locations and registers, read as '0'.

Note 1: Unimplemented in LF devices.

2: Unimplemented in PIC18(L)F26/27K42.

**3:** Unimplemented in PIC18(L)F26/27/45/46/47K42.

#### 6.1 **Power-on Reset (POR)**

The POR circuit holds the device in Reset until VDD has reached an acceptable level for minimum operation. Slow rising VDD, fast operating speeds or analog performance may require greater than minimum VDD. The PWRT, BOR or MCLR features can be used to extend the start-up period until all device operation conditions have been met.

### 6.2 Brown-out Reset (BOR)

The BOR circuit holds the device in Reset when VDD reaches a selectable minimum level. Between the POR and BOR, complete voltage range coverage for execution protection can be implemented.

The Brown-out Reset module has four operating modes controlled by the BOREN<1:0> bits in Configuration Words. The four operating modes are:

- · BOR is always on

- BOR is off when in Sleep

- BOR is controlled by software

- BOR is always off

Refer to Table 6-1 for more information.

The Brown-out Reset voltage level is selectable by configuring the BORV<1:0> bits in Configuration Words.

A VDD noise rejection filter prevents the BOR from triggering on small events. If VDD falls below VBOR for a duration greater than parameter TBORDC, the device will reset. See Table 44-13 for more information.

#### 6.2.1 BOR IS ALWAYS ON

When the BOREN bits of Configuration Words are programmed to '11', the BOR is always on. The device start-up will be delayed until the BOR is ready and VDD is higher than the BOR threshold.

BOR protection is active during Sleep. The BOR does not delay wake-up from Sleep.

#### 6.2.2 BOR IS OFF IN SLEEP

When the BOREN bits of Configuration Words are programmed to '10', the BOR is on, except in Sleep. The device start-up will be delayed until the BOR is ready and VDD is higher than the BOR threshold.

BOR protection is not active during Sleep. The device wake-up will be delayed until the BOR is ready.

### 6.2.3 BOR CONTROLLED BY SOFTWARE

When the BOREN bits of Configuration Words are programmed to '01', the BOR is controlled by the SBOREN bit of the BORCON register. The device startup is not delayed by the BOR ready condition or the VDD level.

BOR protection begins as soon as the BOR circuit is ready. The status of the BOR circuit is reflected in the BORRDY bit of the BORCON register.

BOR protection is unchanged by Sleep.

#### 6.2.4 BOR AND BULK ERASE

BOR is forced ON during PFM Bulk Erase operations to make sure that a safe erase voltage is maintained for a successful erase cycle.

During Bulk Erase, the BOR is enabled at 2.45V for F and LF devices, even if it is configured to some other value. If VDD falls, the erase cycle will be aborted, but the device will not be reset.

### 9.2 Interrupt Vector Table (IVT)

The interrupt controller supports an Interrupt Vector Table (IVT) that contains the vector address location for each interrupt request source.

The Interrupt Vector Table (IVT) resides in program memory, starting at address location determined by the IVTBASE registers; refer to Register 9-36, Register 9-37 and Register 9-38 for details. The IVT contains 68 vectors, one for each source of interrupt. Each interrupt vector location contains the starting address of the associated Interrupt Service Routine (ISR).

The MVECEN bit in Configuration Word 2L controls the availability of the vector table.

#### 9.2.1 INTERRUPT VECTOR TABLE BASE ADDRESS (IVTBASE)

The start address of the vector table is user programmable through the IVTBASE registers. The user must ensure the start address is such that it can encompass the entire vector table inside the program memory.

Each vector address is a 16-bit word (or two address locations on PIC18 devices). So for n interrupt sources, there are 2n address locations necessary to hold the table starting from IVTBASE as the first location. So the staring address of IVTBASE should be chosen such that the address range form IVTBASE to (IVTBASE +2n-1) can be encompassed inside the program flash memory.

For example, the K42 devices have the highest vector number: 81. So IVTBASE should be chosen such that (IVTBASE + 0xA1) is less than the last memory location in program flash memory.

A programmable vector table base address is useful in situations to switch between different sets of vector tables, depending on the application. It can also be used when the application program needs to update the existing vector table (vector address values).

Note: It is required that the user assign an even address to the IVTBASE register for correct operation.

## 9.2.2 INTERRUPT VECTOR TABLE CONTENTS

#### MVECEN = 0

When MVECEN = 0, the address location pointed by the IVTBASE registers has a GOTO instruction for a high priority interrupt. Similarly, the corresponding low priority vector location also has a GOTO instruction, which is executed in case of a low priority interrupt.

#### MVECEN = 1

When MVECEN = 1, the value in the vector table of each interrupt, points to the address location of the first instruction of the interrupt service routine.

ISR Location = Interrupt Vector Table entry << 2.

#### 9.2.3 INTERRUPT VECTOR TABLE (IVT) ADDRESS CALCULATION

#### MVECEN = 0

When the MVECEN bit in Configuration Word 2L (Register 5-3) is cleared, the address pointed by IVTBASE registers is used as the high priority interrupt vector address. The low priority interrupt vector address is offset eight instruction words from the address in IVTBASE registers.

For PIC18 devices the IVTBASE registers default to 00 0008h, the high priority interrupt vector address will be 00 0008h and the low priority interrupt vector address will be 00 0018h.

#### MVECEN = 1

Each interrupt has a unique vector number associated with it as defined in Table 9-2. This vector number is used for calculating the location of the interrupt vector for a particular interrupt source.

Interrupt Vector Address = IVTBASE + (2\*Vector Number).

This calculated Interrupt Vector Address value is stored in the IVTAD<20:0> registers when an interrupt is received (Registers 9-39 through 9-41).

User-assigned software priority assigned using the IPRx registers does not affect address calculation and is only used to resolve concurrent interrupts.

If for any reason the address of the ISR could not be fetched from the vector table, it will cause the system to reset and clear the memory execution violation flag (MEMV bit) in PCON1 register (Register 6-3). This occurs due to any one of the following:

- The entry for the interrupt in the vector table lies outside the executable PFM area (SAF area is non-executable when SAFEN = 1).

- ISR pointed by the vector table lies outside the executable PFM area (SAF area is nonexecutable when SAFEN = 1).

|       | ••• | ••••• |       |       |           |       | -     |

|-------|-----|-------|-------|-------|-----------|-------|-------|

| U-0   | U-0 | U-0   | R-0/0 | R-0/0 | R-0/0     | R-0/0 | R-0/0 |

| _     | _   | —     |       |       | AD<20:16> |       |       |

| bit 7 | ·   |       |       |       |           |       | bit 0 |

|       |     |       |       |       |           |       |       |

|       |     |       |       |       |           |       |       |

#### REGISTER 9-39: IVTADU: INTERRUPT VECTOR TABLE ADDRESS UPPER REGISTER

| Legend:              |                      |                                                       |

|----------------------|----------------------|-------------------------------------------------------|

| R = Readable bit     | W = Writable bit     | U = Unimplemented bit, read as '0'                    |

| u = Bit is unchanged | x = Bit is unknown   | -n/n = Value at POR and BOR/Value at all other Resets |

| '1' = Bit is set     | '0' = Bit is cleared |                                                       |

bit 7-5 Unimplemented: Read as '0'

bit 4-0 AD<20:16>: Interrupt Vector Table Address bits

#### REGISTER 9-40: IVTADH: INTERRUPT VECTOR TABLE ADDRESS HIGH REGISTER

| R-0/0    | R-0/0 | R-0/0 | R-0/0 | R-0/0 | R-0/0 | R-0/0 | R-0/0 |  |  |  |

|----------|-------|-------|-------|-------|-------|-------|-------|--|--|--|

| AD<15:8> |       |       |       |       |       |       |       |  |  |  |

| bit 7    |       |       |       |       |       |       | bit 0 |  |  |  |

|          |       |       |       |       |       |       |       |  |  |  |

| Legend:              |                      |                                                       |

|----------------------|----------------------|-------------------------------------------------------|

| R = Readable bit     | W = Writable bit     | U = Unimplemented bit, read as '0'                    |

| u = Bit is unchanged | x = Bit is unknown   | -n/n = Value at POR and BOR/Value at all other Resets |

| '1' = Bit is set     | '0' = Bit is cleared |                                                       |

bit 7-0 AD<15:8>: Interrupt Vector Table Address bits

#### REGISTER 9-41: IVTADL: INTERRUPT VECTOR TABLE ADDRESS LOW REGISTER

| R-0/0                                                                                         | R-0/0       | R-0/0          | R-0/0 | R-1/1                              | R-0/0 | R-0/0 | R-0/0 |  |  |  |  |

|-----------------------------------------------------------------------------------------------|-------------|----------------|-------|------------------------------------|-------|-------|-------|--|--|--|--|

|                                                                                               |             |                | AD<   | <7:0>                              |       |       |       |  |  |  |  |

| bit 7                                                                                         | bit 7 bit 0 |                |       |                                    |       |       |       |  |  |  |  |

|                                                                                               |             |                |       |                                    |       |       |       |  |  |  |  |

| Legend:                                                                                       |             |                |       |                                    |       |       |       |  |  |  |  |

| R = Readable bi                                                                               | t           | W = Writable b | bit   | U = Unimplemented bit, read as '0' |       |       |       |  |  |  |  |

| u = Bit is unchanged x = Bit is unknown -n/n = Value at POR and BOR/Value at all other Resets |             |                |       |                                    |       |       |       |  |  |  |  |

bit 7-0 AD<7:0>: Interrupt Vector Table Address bits

'0' = Bit is cleared

'1' = Bit is set

#### REGISTER 13-5: NVMDAT: DATA EEPROM MEMORY DATA

| R/W-0/0         | R/W-0/0 | R/W-0/0           | R/W-0/0 | R/W-0/0                            | R/W-0/0 | R/W-0/0 | R/W-0/0 |  |  |

|-----------------|---------|-------------------|---------|------------------------------------|---------|---------|---------|--|--|

|                 |         |                   | DAT     | <7:0>                              |         |         |         |  |  |

| bit 7           |         |                   |         |                                    |         |         | bit 0   |  |  |

|                 |         |                   |         |                                    |         |         |         |  |  |

| Legend:         |         |                   |         |                                    |         |         |         |  |  |

| R = Readable    | bit     | W = Writable I    | bit     | U = Unimplemented bit, read as '0' |         |         |         |  |  |

| x = Bit is unkn | own     | '0' = Bit is clea | ared    | '1' = Bit is set                   |         |         |         |  |  |

| -n = Value at F | POR     |                   |         |                                    |         |         |         |  |  |

bit 7-0 **DAT<7:0>:** The value of the data memory word returned from NVMADR after a Read command, or the data written by a Write command.

## TABLE 13-4: SUMMARY OF REGISTERS ASSOCIATED WITH NONVOLATILE MEMORY CONTROL

| Name                   | Bit 7       | Bit 6          | Bit 5 | Bit 4 | Bit 3 | Bit 2 | Bit 1 | Bit 0 | Register<br>on Page |  |

|------------------------|-------------|----------------|-------|-------|-------|-------|-------|-------|---------------------|--|

| NVMCON1                | REG<1:0>    |                | —     | FREE  | WRERR | WREN  | WR    | RD    | 210                 |  |

| NVMCON2                |             | Unlock Pattern |       |       |       |       |       |       |                     |  |

| NVMADRL                |             | NVMADR<7:0>    |       |       |       |       |       |       |                     |  |

| NVMADRH <sup>(1)</sup> | —           | —              | —     | _     | —     | —     | NVMA  | 211   |                     |  |

| NVMDAT                 | NVMDAT<7:0> |                |       |       |       |       |       |       |                     |  |

Legend: — = unimplemented, read as '0'. Shaded bits are not used during EEPROM access.

\*Page provides register information.

**Note 1:** The NVMADRH register is not implemented on PIC18(L)F45/55K42.

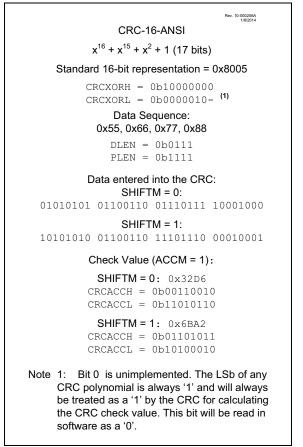

## 14.2 CRC Functional Overview

The CRC module can be used to detect bit errors in the program memory using the built-in memory scanner or through user input RAM memory. The CRC module can accept up to a 16-bit polynomial with up to a 16-bit seed value. A CRC calculated check value (or checksum) will then be generated into the CRCACC<15:0> registers for user storage. The CRC module uses an XOR shift register implementation to perform the polynomial division required for the CRC calculation.

#### EXAMPLE 14-1: CRC EXAMPLE

# PIC18(L)F26/27/45/46/47/55/56/57K42

#### **REGISTER 15-15: DMAxDSAH: DMAx DESTINATION START ADDRESS HIGH REGISTER**

|           |         | -       | -       |         |         |         |         |  |  |  |

|-----------|---------|---------|---------|---------|---------|---------|---------|--|--|--|

| R/W-0/0   | R/W-0/0 | R/W-0/0 | R/W-0/0 | R/W-0/0 | R/W-0/0 | R/W-0/0 | R/W-0/0 |  |  |  |

| DSA<15:8> |         |         |         |         |         |         |         |  |  |  |

| bit 7     |         |         |         |         |         |         | bit 0   |  |  |  |

|           |         |         |         |         |         |         |         |  |  |  |

|           |         |         |         |         |         |         |         |  |  |  |

| Legend:                                                     |                  |                        |                                            |  |  |  |  |  |

|-------------------------------------------------------------|------------------|------------------------|--------------------------------------------|--|--|--|--|--|

| R = Readable bit                                            | W = Writable bit | U = Unimplemented bit, | U = Unimplemented bit, read as '0'         |  |  |  |  |  |

| -n/n = Value at POR and<br>BOR/Value at all other<br>Resets | 1 = bit is set   | 0 = bit is cleared     | x = bit is unknown<br>u = bit is unchanged |  |  |  |  |  |

bit 7-0 DSA<15:8>: Destination Start Address bits

#### **REGISTER 15-16: DMAxDPTRL: DMAx DESTINATION POINTER LOW REGISTER**

| R-0       | R-0 | R-0 | R-0 | R-0 | R-0 | R-0 | R-0   |  |  |  |  |

|-----------|-----|-----|-----|-----|-----|-----|-------|--|--|--|--|

| DPTR<7:0> |     |     |     |     |     |     |       |  |  |  |  |

| bit 7     |     |     |     |     |     |     | bit 0 |  |  |  |  |

|           |     |     |     |     |     |     |       |  |  |  |  |

|           |     |     |     |     |     |     |       |  |  |  |  |

| Legend:                                                     |                  |                             |                                            |

|-------------------------------------------------------------|------------------|-----------------------------|--------------------------------------------|

| R = Readable bit                                            | W = Writable bit | U = Unimplemented bit, read | as '0'                                     |

| -n/n = Value at POR and<br>BOR/Value at all other<br>Resets | 1 = bit is set   | 0 = bit is cleared          | x = bit is unknown<br>u = bit is unchanged |

bit 7-0 DPTR<7:0>: Current Destination Address Pointer

#### **REGISTER 15-17: DMAxDPTRH: DMAx DESTINATION POINTER HIGH REGISTER**

| R-0        | R-0 | R-0 | R-0 | R-0 | R-0 | R-0 | R-0   |  |  |  |

|------------|-----|-----|-----|-----|-----|-----|-------|--|--|--|

| DPTR<15:8> |     |     |     |     |     |     |       |  |  |  |

| bit 7      |     |     |     |     |     |     | bit 0 |  |  |  |

| Legend:                                                     |                  |                           |                                            |

|-------------------------------------------------------------|------------------|---------------------------|--------------------------------------------|

| R = Readable bit                                            | W = Writable bit | U = Unimplemented bit, re | ead as '0'                                 |

| -n/n = Value at POR and<br>BOR/Value at all other<br>Resets | 1 = bit is set   | 0 = bit is cleared        | x = bit is unknown<br>u = bit is unchanged |

bit 7-0 **DPTR<15:8>:** Current Destination Address Pointer

© 2017 Microchip Technology Inc.

### 16.4 Register Definitions: Port Control

### **REGISTER 16-1: PORTx: PORTx REGISTER<sup>(1)</sup>**

| R/W-x/u          | R/W-x/u      | R/W-x/u           | R/W-x/u     | R/W-x/u         | R/W-x/u  | R/W-x/u | R/W-x/u |

|------------------|--------------|-------------------|-------------|-----------------|----------|---------|---------|

| Rx7              | Rx6          | Rx5               | Rx4         | Rx3             | Rx2      | Rx1     | Rx0     |

| bit 7            |              |                   |             |                 |          | •       | bit 0   |

|                  |              |                   |             |                 |          |         |         |

| Legend:          |              |                   |             |                 |          |         |         |

| R = Readable     | bit          | W = Writable      | bit         | U = Unimplen    | d as '0' |         |         |

| '1' = Bit is set |              | '0' = Bit is clea | ared        | x = Bit is unkr |          |         |         |

| -n/n = Value at  | t POR and BO | R/Value at all o  | ther Resets |                 |          |         |         |

bit 7-0 **Rx<7:0>:** Rx7:Rx0 Port I/O Value bits 1 = Port pin is ≥ VIH

$0 = Port pin is \le VIL$

**Note 1:** Writes to PORTx are actually written to the corresponding LATx register. Reads from PORTx register return actual I/O pin values.

#### TABLE 16-2: PORT REGISTERS

| Name                 | Bit 7              | Bit 6              | Bit 5 | Bit 4 | Bit 3              | Bit 2              | Bit 1              | Bit 0              |

|----------------------|--------------------|--------------------|-------|-------|--------------------|--------------------|--------------------|--------------------|

| PORTA                | RA7                | RA6                | RA5   | RA4   | RA3                | RA2                | RA1                | RA0                |

| PORTB                | RB7 <sup>(1)</sup> | RB6 <sup>(1)</sup> | RB5   | RB4   | RB3                | RB2                | RB1                | RB0                |

| PORTC                | RC7                | RC6                | RC5   | RC4   | RC3                | RC2                | RC1                | RC0                |

| PORTD <sup>(3)</sup> | RD7                | RD6                | RD5   | RD4   | RD3                | RD2                | RD1                | RD0                |

| PORTE                | _                  | _                  | _     | _     | RE3 <sup>(2)</sup> | RE2 <sup>(3)</sup> | RE1 <sup>(3)</sup> | RE0 <sup>(3)</sup> |

| PORTF <sup>(4)</sup> | RF7                | RF6                | RF5   | RF4   | RF3                | RF2                | RF1                | RF0                |

Note 1: Bits RB6 and RB7 read '1' while in Debug mode.

**2:** Bit PORTE3 is read-only, and will read '1' when MCLRE = 1 (Master Clear enabled).

**3:** Unimplemented in PIC18(L)F26/27K42.

**4:** Unimplemented in PIC18(L)F26/27/45/46/47K42.

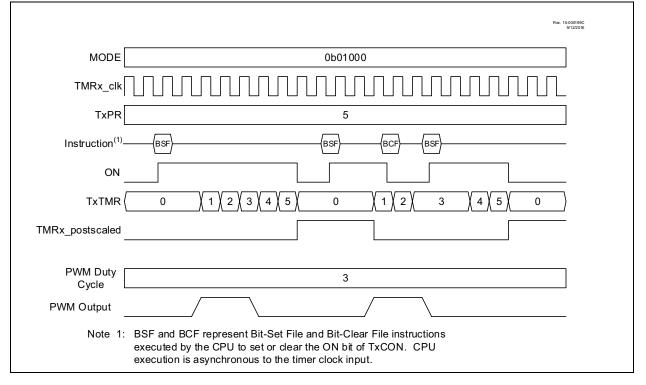

#### 22.5.5 SOFTWARE START ONE-SHOT MODE

In One-Shot mode, the timer resets and the ON bit is cleared when the timer value matches the T2PR period value. The ON bit must be set by software to start another timer cycle. Setting MODE<4:0> = 01000 selects One-Shot mode which is illustrated in Figure 22-8. In the example, ON is controlled by BSF and BCF instructions. In the first case, a BSF instruction sets ON and the counter runs to completion and clears ON. In the second case, a BSF instruction starts the cycle, BCF/BSF instructions turn the counter off and on during the cycle, and then it runs to completion.

When One-Shot mode is used in conjunction with the CCP PWM operation, the PWM pulse drive starts concurrent with setting the ON bit. Clearing the ON bit while the PWM drive is active will extend the PWM drive. The PWM drive will terminate when the timer value matches the CCPRx pulse width value. The PWM drive will remain off until software sets the ON bit to start another cycle. If software clears the ON bit after the CCPRx match but before the T2PR match then the PWM drive will be extended by the length of time the ON bit remains cleared. Another timing cycle can only be initiated by setting the ON bit after it has been cleared by a T2PR period count match.

FIGURE 22-8: SOFTWARE START ONE-SHOT MODE TIMING DIAGRAM (MODE = 01000)

#### 25.6.4 HIGH AND LOW MEASURE MODE

This mode measures the high and low pulse time of the SMTSIGx relative to the SMT clock. It begins incrementing the SMT1TMR on a rising edge on the SMTSIGx input, then updates the SMT1CPW register with the value and resets the SMT1TMR on a falling edge, starting to increment again. Upon observing another rising edge, it updates the SMT1CPR register with its current value and once again resets the SMT1TMR value and begins incrementing again. See Figure 25-8 and Figure 25-9.

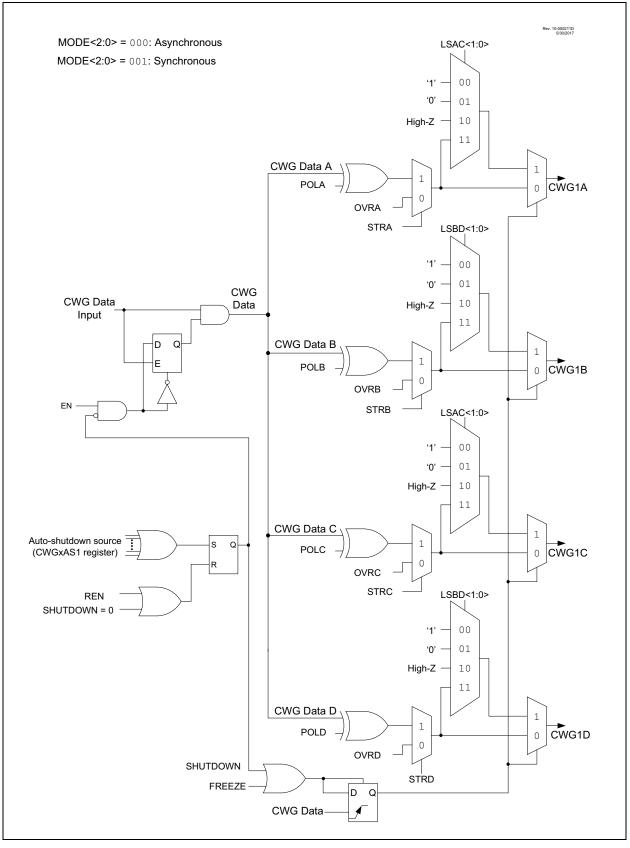

#### FIGURE 26-11: SIMPLIFIED CWG BLOCK DIAGRAM (OUTPUT STEERING MODES)

## 27.7 Register Definitions: CLC Control

| R/W-0/0        | U-0                                                                                                                 | R-0/0                                  | R/W-0/0      | R/W-0/0         | R/W-0/0          | R/W-0/0          | R/W-0/0     |  |  |  |  |

|----------------|---------------------------------------------------------------------------------------------------------------------|----------------------------------------|--------------|-----------------|------------------|------------------|-------------|--|--|--|--|