#### Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Details                    |                                                                            |

|----------------------------|----------------------------------------------------------------------------|

| Product Status             | Active                                                                     |

| Core Processor             | PIC                                                                        |

| Core Size                  | 8-Bit                                                                      |

| Speed                      | 64MHz                                                                      |

| Connectivity               | I <sup>2</sup> C, LINbus, SPI, UART/USART                                  |

| Peripherals                | Brown-out Detect/Reset, DMA, HLVD, POR, PWM, WDT                           |

| Number of I/O              | 25                                                                         |

| Program Memory Size        | 128KB (64K x 16)                                                           |

| Program Memory Type        | FLASH                                                                      |

| EEPROM Size                | 1K x 8                                                                     |

| RAM Size                   | 8K x 8                                                                     |

| Voltage - Supply (Vcc/Vdd) | 2.3V ~ 5.5V                                                                |

| Data Converters            | A/D 24x12b; D/A 1x5b                                                       |

| Oscillator Type            | Internal                                                                   |

| Operating Temperature      | -40°C ~ 125°C (TA)                                                         |

| Mounting Type              | Through Hole                                                               |

| Package / Case             | 28-DIP (0.300", 7.62mm)                                                    |

| Supplier Device Package    | 28-SPDIP                                                                   |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/pic18f27k42-e-sp |

|                            |                                                                            |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

| REGISTER 5     | -7: CONF                                              | <b>GURATION V</b>                                       | VORD 4L (3                | 0 0006h)            |                 |                    |       |  |

|----------------|-------------------------------------------------------|---------------------------------------------------------|---------------------------|---------------------|-----------------|--------------------|-------|--|

| R/W-1          | U-1                                                   | U-1                                                     | R/W-1                     | R/W-1               | R/W-1           | R/W-1              | R/W-1 |  |

| WRTAPP (1)     | VRTAPP <sup>(1)</sup> — — <u>SAFEN</u> <sup>(1)</sup> |                                                         |                           | BBEN <sup>(1)</sup> |                 | BBSIZE<2:0> (2     | 2)    |  |

| bit 7          |                                                       | ·                                                       |                           |                     |                 |                    | bit C |  |

| [              |                                                       |                                                         |                           |                     |                 |                    |       |  |

| Legend:        |                                                       |                                                         |                           |                     |                 |                    |       |  |

| R = Readable   | bit                                                   | W = Writable                                            | bit                       | U = Unimple         | mented bit, rea | ad as '1'          |       |  |

| -n = Value for | blank device                                          | '1' = Bit is set                                        | t                         | '0' = Bit is cle    | ared            | x = Bit is unknown |       |  |

| bit 7          | 1 = Applicat                                          | plication Block<br>ion Block is NO<br>ion Block is writ | T write-protec            |                     |                 |                    |       |  |

| bit 6-5        | Unimplemen                                            | ted: Read as '1                                         | ,<br>-                    |                     |                 |                    |       |  |

| bit 4          | <b>SAFEN:</b> Stor<br>1 = SAF is c<br>0 = SAF is e    |                                                         | Enable bit <sup>(1)</sup> |                     |                 |                    |       |  |

| bit 3          | 1 = Boot Blo                                          | Block Enable bi<br>ock disabled<br>ock enabled          | <sub>t</sub> (1)          |                     |                 |                    |       |  |

|                |                                                       |                                                         |                           |                     |                 |                    |       |  |

bit 2-0 BBSIZE<2:0>: Boot Block Size Selection bits<sup>(2)</sup> Refer to Table 5-1.

- Note 1: Bits are implemented as sticky bits. Once protection is enabled through ICSP<sup>™</sup> or a self-write, it can only be reset through a Bulk Erase.

- 2: BBSIZE<2:0> bits can only be changed when BBEN = 1. Once BBEN = 0, BBSIZE<2:0> can only be changed through a Bulk Erase.

| BBEN | BBSIZE<2:0> | Boot Block Size | END_ADDRESS_BOOT | Device Size <sup>(1)</sup> |        |     |  |  |

|------|-------------|-----------------|------------------|----------------------------|--------|-----|--|--|

| DDEN | BB3IZE Z.02 | (words)         | END_ADDRESS_BOOT | 16k                        | 32k    | 64k |  |  |

| 1    | XXX         | 0               | _                | Х                          | Х      | Х   |  |  |

| 0    | 111         | 512             | 00 03FFh         | Х                          | Х      | Х   |  |  |

| 0    | 110         | 1024            | 00 07FFh         | Х                          | Х      | Х   |  |  |

| 0    | 101         | 2048            | 00 0FFFh         | Х                          | Х      | Х   |  |  |

| 0    | 100         | 4096            | 00 1FFFh         | Х                          | Х      | Х   |  |  |

| 0    | 011         | 8192            | 00 3FFFh         | Х                          | Х      | Х   |  |  |

| 0    | 010         | 16384           | 00 7FFFh         | _                          | Х      | Х   |  |  |

| 0    | 001         | 32768           | 00 FFFFh         |                            | Note 2 | Х   |  |  |

| 0    | 000         | 32768           | 00 FFFFh         | _                          | _      | _   |  |  |

#### TABLE 5-1: BOOT BLOCK SIZE BITS

Note 1: For each device, the quoted device size specification is listed in Table 4-1.

2: The maximum boot block size is half the user program memory size. All selections higher than the maximum size default to maximum boot block size of half PFM. For example, all settings of BBSIZE = 000 through BBSIZE = 010, default to a boot block size of 16 kW on a 32 kW device.

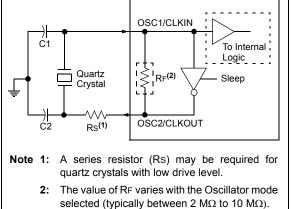

## FIGURE 7-3: QUARTZ CRYSTAL OPERATION (LP, XT OR HS MODE) PIC® MCU

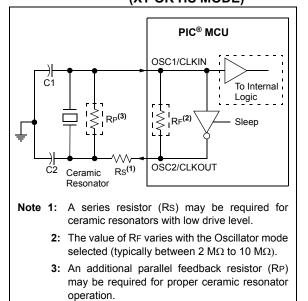

#### FIGURE 7-4: CERAMIC RESONATOR OPERATION (XT OR HS MODE)

## 7.2.1.3 Oscillator Start-up Timer (OST)

If the oscillator module is configured for LP, XT or HS modes, the Oscillator Start-up Timer (OST) counts 1024 oscillations from OSC1. This occurs following a Power-on Reset (POR), or a wake-up from Sleep. The OST ensures that the oscillator circuit, using a quartz crystal resonator or ceramic resonator, has started and is providing a stable system clock to the oscillator module.

## 7.2.1.4 4x PLL

The oscillator module contains a 4x PLL that can be used with the external clock sources to provide a system clock source. The input frequency for the PLL must fall within specifications. See the PLL Clock Timing Specifications in Table 44-11.

The PLL can be enabled for use by one of two methods:

- 1. Program the RSTOSC bits in the Configuration Word 1 to 010 (enable EXTOSC with 4x PLL).

- 2. Write the NOSC bits in the OSCCON1 register to 010 (enable EXTOSC with 4x PLL).

## 9.3 Interrupt Priority

The final priority level for any pending source of interrupt is determined first by the user-assigned priority of that source in the IPRx register, then by the natural order priority within the IVT. The sections below detail the operation of Interrupt priorities.

### 9.3.1 USER (SOFTWARE) PRIORITY

User-assigned interrupt priority is enabled by setting the IPEN bit in the INTCON0 register (Register 9-1). Each peripheral interrupt source can be assigned a high or low priority level by the user. The userassignable interrupt priority control bits for each interrupt are located in the IPRx registers (Registers 9-25 through 9-35).

The interrupts are serviced based on predefined interrupt priority scheme defined below.

- Interrupts set by the user as high-priority interrupt have higher precedence of execution. High-priority interrupts will override a low-priority request when:

- a) A low priority interrupt has been requested or its request is already pending.

- b) A low- and high-priority interrupt are triggered concurrently, i.e., on the same instruction cycle<sup>(1)</sup>.

- c) A low-priority interrupt was requested and the corresponding Interrupt Service Routine is currently executing. In this case, the lower priority interrupt routine will complete executing after the high-priority interrupt has been serviced<sup>(2)</sup>.

- 2. Interrupts set by the user as a low priority have the lower priority of execution and are preempted by any high-priority interrupt.

- Interrupts defined with the same software priority cannot preempt or interrupt each other. Concurrent pending interrupts with the same user priority are resolved using the natural order priority. (when MVECEN = ON) or in the order the interrupt flag bits are polled in the ISR (when MVECEN = OFF).

- Note 1: When a high priority interrupt preempts a concurrent low priority interrupt, the GIEL bit may be cleared in the high priority Interrupt Service Routine. If the GIEL bit is cleared, the low priority interrupt will NOT be serviced even if it was originally requested. The corresponding interrupt flag needs to be cleared in user code.

- 2: When a high priority interrupt is requested while a low priority Interrupt Service Routine is executing, the GIEL bit may be cleared in the high priority Interrupt Service Routine. The pending low priority interrupt will resume even if the GIEL bit is cleared.

| U-0     | R/W <sup>(3)</sup> -q/q <sup>(1)</sup> R/W <sup>(3)</sup> -q/q <sup>(1)</sup> R/W <sup>(3)</sup> -q/q <sup>(1)</sup> | U-0 | R/W <sup>(4)</sup> -q/q <sup>(2)</sup> | R/W <sup>(4)</sup> _q/q <sup>(2)</sup> | R/W <sup>(4)</sup> -q/q <sup>(2)</sup> |

|---------|----------------------------------------------------------------------------------------------------------------------|-----|----------------------------------------|----------------------------------------|----------------------------------------|

| -       | CS<2:0>                                                                                                              | _   |                                        | WINDOW<2:0>                            |                                        |

| bit 7   |                                                                                                                      |     |                                        |                                        | bit 0                                  |

|         |                                                                                                                      |     |                                        |                                        |                                        |

| Legend: |                                                                                                                      |     |                                        |                                        |                                        |

#### REGISTER 11-2: WDTCON1: WATCHDOG TIMER CONTROL REGISTER 1

| Legena.              |                      |                                                       |

|----------------------|----------------------|-------------------------------------------------------|

| R = Readable bit     | W = Writable bit     | U = Unimplemented bit, read as '0'                    |

| u = Bit is unchanged | x = Bit is unknown   | -n/n = Value at POR and BOR/Value at all other Resets |

| '1' = Bit is set     | '0' = Bit is cleared | q = Value depends on condition                        |

#### bit 7 Unimplemented: Read as '0'

bit 6-4 **CS<2:0>:** Watchdog Timer Clock Select bits

- 111 = Reserved •

- •

- •

- 011 = Reserved

- 010 = SOSC

- 001 = MFINTOSC 31.25 kHz

- 000 = LFINTOSC 31 kHz

- bit 3 Unimplemented: Read as '0'

### bit 2-0 WINDOW<2:0>: Watchdog Timer Window Select bits

| WINDOW<2:0> | Window delay<br>Percent of time | Window opening<br>Percent of time |

|-------------|---------------------------------|-----------------------------------|

| 111         | N/A                             | 100                               |

| 110         | 12.5                            | 87.5                              |

| 101         | 25                              | 75                                |

| 100         | 37.5                            | 62.5                              |

| 011         | 50                              | 50                                |

| 010         | 62.5                            | 37.5                              |

| 001         | 75                              | 25                                |

| 000         | 87.5                            | 12.5                              |

Note 1: If WDTCCS <2:0> in CONFIG3H = 111, the Reset value of CS<2:0> is 000.

2: The Reset value of WINDOW<2:0> is determined by the value of WDTCWS<2:0> in the CONFIG3H register.

**3:** If WDTCCS<2:0> in CONFIG3H  $\neq$  111, these bits are read-only.

4: If WDTCWS<2:0> in CONFIG3H  $\neq$  111, these bits are read-only.

Example 12-3 shows the sequence to do a 16 x 16 unsigned multiplication. Equation 12-1 shows the algorithm that is used. The 32-bit result is stored in four registers (RES<3:0>).

#### EQUATION 12-1: 16 x 16 UNSIGNED MULTIPLICATION ALGORITHM

| RES3:RES0 | = |                                          |

|-----------|---|------------------------------------------|

|           | = | $(ARG1H \bullet ARG2H \bullet 2^{16}) +$ |

|           |   | $(ARG1H \bullet ARG2L \bullet 2^8) +$    |

|           |   | $(ARG1L \bullet ARG2H \bullet 2^8) +$    |

|           |   | $(ARG1L \bullet ARG2L)$                  |

|           |   |                                          |

### EXAMPLE 12-3: 16 x 16 UNSIGNED MULTIPLY ROUTINE

|   | MOVF<br>MULWF |                                            | ; ARG1L * ARG2L-><br>; PRODH:PRODL<br>; |

|---|---------------|--------------------------------------------|-----------------------------------------|

| ; |               | PRODL, RESO                                | ;                                       |

|   | MOVF<br>MULWF | ARG1H, W<br>ARG2H                          | ; ARG1H * ARG2H-><br>; PRODH:PRODL      |

|   |               | PRODH, RES3<br>PRODL, RES2                 | ;                                       |

| ; | MOVF<br>MULWF | ARG1L, W<br>ARG2H                          | ; ARG1L * ARG2H-><br>; PRODH:PRODL      |

|   | MOVF          | PRODL, W<br>RES1, F<br>PRODH, W<br>RES2, F | ; Add cross<br>; products<br>;          |

| ; | CLRF          |                                            | ;;                                      |

|   | MULWF         |                                            | ;<br>; ARG1H * ARG2L-><br>; PRODH:PRODL |

|   | ADDWF<br>MOVF | - /                                        | ;<br>; Add cross<br>; products          |

|   | CLRF          | RES2, F<br>WREG<br>RES3, F                 | ;<br>;<br>;                             |

Example 12-4 shows the sequence to do a 16 x 16 signed multiply. Equation 12-2 shows the algorithm used. The 32-bit result is stored in four registers (RES<3:0>). To account for the sign bits of the arguments, the MSb for each argument pair is tested and the appropriate subtractions are done.

### EQUATION 12-2: 16 x 16 SIGNED MULTIPLICATION ALGORITHM

| RES3:RES0 = ARG1H:ARG1L • ARG2H:ARG2L                           |

|-----------------------------------------------------------------|

| $= (ARG1H \bullet ARG2H \bullet 2^{16}) +$                      |

| $(ARG1H \bullet ARG2L \bullet 2^8) +$                           |

| $(ARG1L \bullet ARG2H \bullet 2^8) +$                           |

| $(ARG1L \bullet ARG2L) +$                                       |

| $(-1 \bullet ARG2H < 7 > \bullet ARG1H:ARG1L \bullet 2^{16}) +$ |

| $(-1 \bullet ARG1H < 7 > \bullet ARG2H: ARG2L \bullet 2^{16})$  |

|                                                                 |

### EXAMPLE 12-4: 16 x 16 SIGNED MULTIPLY ROUTINE

|                | liitee        |                                        |

|----------------|---------------|----------------------------------------|

| MOVF           | ARG1L, W      |                                        |

| MULWF          | ARG2L         | ; ARG1L * ARG2L ->                     |

|                |               | ; PRODH:PRODL                          |

| MOVFF          | PRODH, RES1   | ;                                      |

| MOVFF          | PRODL, RESO   | ;                                      |

| ;              | ,             | ,                                      |

| MOVF           | ARG1H, W      |                                        |

| MULWF          |               | ; ARG1H * ARG2H ->                     |

| TIODWI         | 1110211       | ; PRODH:PRODL                          |

| MOVEE          | PRODH, RES3   | ;                                      |

| MOVFF          | PRODL, RES2   | ;                                      |

| ;              | 110000, 11002 | ,                                      |

| MOVF           | ARG1L, W      |                                        |

|                | ARG2H         | ; ARG1L * ARG2H ->                     |

| PIOLIWE        | ANGZII        | ; PRODH:PRODL                          |

| MOVF           | PRODL, W      | ;                                      |

| ADDWF          | RES1, F       | ,<br>; Add cross                       |

| MOVF           | PRODH, W      | ; products                             |

| ADDWFC         | RES2, F       | ; produces                             |

| CLRF           | WREG          |                                        |

|                | RES3, F       | ;                                      |

| ;              | KESS, F       | ,                                      |

|                | ARG1H, W      |                                        |

| MULWF          | ARG2L         | ;<br>; ARG1H * ARG2L ->                |

| PIOTIME        | ANGZU         | ; PRODH:PRODL                          |

| MOVF           | PRODL, W      | ;                                      |

| ADDWF          | RES1, F       | ,<br>; Add cross                       |

| MOVF           | PRODH, W      | ; products                             |

|                | RES2, F       | ;                                      |

| CLRF           | WREG          | ;                                      |

| -              | RES3, F       | ;                                      |

| ;              | 1000, 1       | ,                                      |

|                | ARG2H, 7      | ; ARG2H:ARG2L neg?                     |

| BRA            | SIGN ARG1     | ; ARG2H:ARG2L neg?<br>; no, check ARG1 |

| MOVF           | ARG1L, W      | ;                                      |

| SUBWF          | RES2          | ;                                      |

| MOVE           | ARG1H, W      | ;                                      |

| SUBWFB         |               | ,                                      |

| ;              | 1(100         |                                        |

| ,<br>SIGN ARG1 |               |                                        |

| BTFSS          | ARG1H, 7      | ; ARG1H:ARG1L neg?                     |

| BRA            | CONT CODE     | ; no, done                             |

| MOVE           | ARG2L, W      | ;                                      |

| SUBWF          | RES2          | ;                                      |

| MOVE           | ARG2H, W      | ;                                      |

| SUBWFB         |               | ,                                      |

|                | 1             |                                        |

| ,<br>CONT CODE |               |                                        |

| :              |               |                                        |

| •              |               |                                        |

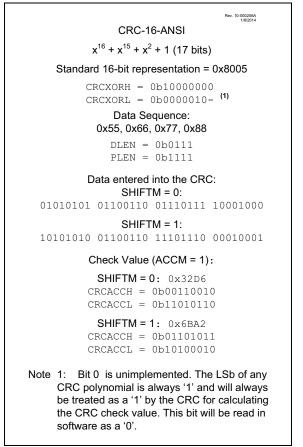

## 14.2 CRC Functional Overview

The CRC module can be used to detect bit errors in the program memory using the built-in memory scanner or through user input RAM memory. The CRC module can accept up to a 16-bit polynomial with up to a 16-bit seed value. A CRC calculated check value (or checksum) will then be generated into the CRCACC<15:0> registers for user storage. The CRC module uses an XOR shift register implementation to perform the polynomial division required for the CRC calculation.

### EXAMPLE 14-1: CRC EXAMPLE

|                      | PPS Input  | Default Pin         | Register              |       |                                        |   |   | In | put Ava              | ilable fro | m Selecte | ed POR | Тх |   |   |   |   |

|----------------------|------------|---------------------|-----------------------|-------|----------------------------------------|---|---|----|----------------------|------------|-----------|--------|----|---|---|---|---|

| Peripheral           | Register   | Selection at<br>POR | Reset Value<br>at POR | PIC18 | PIC18(L)F26/27K42 PIC18(L)F45/46/47K42 |   |   |    | PIC18(L)F55/56/57K42 |            |           |        |    |   |   |   |   |

| Interrupt 0          | INTOPPS    | RB0                 | 0b0 1000              | А     | В                                      | _ | А | В  | _                    | —          | —         | Α      | В  | — | _ |   | — |

| Interrupt 1          | INT1PPS    | RB1                 | 0b0 1001              | А     | В                                      | — | А | В  | _                    | —          | —         | _      | В  | — | D | _ | - |

| Interrupt 2          | INT2PPS    | RB2                 | 0b0 1010              | А     | В                                      | — | А | В  | —                    | —          | —         | _      | В  | — | - | — | F |

| Timer0 Clock         | TOCKIPPS   | RA4                 | 0b0 0100              | А     | В                                      | — | А | В  | _                    | —          | —         | А      | _  | — | _ | _ | F |

| Timer1 Clock         | T1CKIPPS   | RC0                 | 0b1 0000              | А     | _                                      | С | Α |    | С                    | —          | —         | _      | _  | С | _ | E | - |

| Timer1 Gate          | T1GPPS     | RB5                 | 0b0 1101              | _     | В                                      | С | _ | В  | С                    | —          | —         | _      | В  | С | _ | _ | - |

| Timer3 Clock         | T3CKIPPS   | RC0                 | 0b1 0000              | _     | В                                      | С | _ | В  | С                    | —          | —         | -      | _  | С | _ | E | - |

| Timer3 Gate          | T3GPPS     | RC0                 | 0b1 0000              | А     | —                                      | С | Α | _  | С                    | —          | —         | Α      | _  | С | _ | — |   |

| Timer5 Clock         | T5CKIPPS   | RC2                 | 0b1 0010              | А     | _                                      | С | А | _  | С                    |            |           | _      | _  | С | _ | E | _ |

| Timer5 Gate          | T5GPPS     | RB4                 | 0b0 1100              | _     | В                                      | С | _ | В  | -                    | D          | —         | —      | В  | — | D |   | _ |

| Timer2 Clock         | T2INPPS    | RC3                 | 0b1 0011              | А     | —                                      | С | Α | _  | С                    | _          | —         | А      | _  | С | _ |   | _ |

| Timer4 Clock         | T4INPPS    | RC5                 | 0b1 0101              | _     | В                                      | С | _ | В  | С                    | _          | —         | _      | В  | С | _ |   | _ |

| Timer6 Clock         | T6INPPS    | RB7                 | 0b0 1111              | _     | В                                      | С | _ | В  | -                    | D          | _         | —      | В  | _ | D | _ | _ |

| CCP1                 | CCP1PPS    | RC2                 | 0b1 0010              | _     | В                                      | С | _ | В  | С                    | _          | _         | —      |    | С | _ | _ | F |

| CCP2                 | CCP2PPS    | RC1                 | 0b1 0001              | _     | В                                      | С |   | В  | С                    | _          | _         | —      |    | С | _ | _ | F |

| CCP3                 | CCP3PPS    | RB5                 | 0b0 1101              | _     | В                                      | С | _ | В  | _                    | D          | _         | —      | В  | _ | D | _ | _ |

| CCP4                 | CCP4PPS    | RB0                 | 0b0 1000              | _     | В                                      | С | _ | В  | _                    | D          | _         | —      | В  | _ | D | _ | _ |

| SMT1 Window          | SMT1WINPPS | RC0                 | 0b1 0000              | _     | В                                      | С |   | В  | С                    | —          | —         | _      | _  | С | _ |   | F |

| SMT1 Signal          | SMT1SIGPPS | RC1                 | 0b1 0001              | _     | В                                      | С |   | В  | С                    | _          | _         | —      |    | С | _ | _ | F |

| CWG1                 | CWG1PPS    | RB0                 | 0b0 1000              | _     | В                                      | С | _ | В  | _                    | D          | _         | —      | В  | _ | D | _ | _ |

| CWG2                 | CWG2PPS    | RB1                 | 0b0 1001              | _     | В                                      | С |   | В  | _                    | D          | _         | —      | В  | _ | D | _ | _ |

| CWG3                 | CWG3PPS    | RB2                 | 0b0 1010              | _     | В                                      | С | _ | В  | _                    | D          | _         | —      | В  | _ | D | _ | _ |

| DSM1 Carrier<br>Low  | MD1CARLPPS | RA3                 | 0b0 0011              | А     | _                                      | С | A | —  |                      | D          | —         | A      | —  | — | D | — | - |

| DSM1 Carrier<br>High | MD1CARHPPS | RA4                 | 0b0 0100              | А     | —                                      | С | A | —  |                      | D          | —         | A      | —  | — | D | — | — |

| DSM1 Source          | MD1SRCPPS  | RA5                 | 0b0 0101              | А     | _                                      | С | А | —  | _                    | D          | _         | А      |    | _ | D | _ | _ |

| CLCx Input 1         | CLCIN0PPS  | RA0                 | 0000 0000             | А     | —                                      | С | А | _  | С                    | —          | —         | Α      | —  | С | _ | — | — |

| CLCx Input 2         | CLCIN1PPS  | RA1                 | 0b0 0001              | А     | —                                      | С | А | _  | С                    | —          | —         | Α      | —  | С | _ | — | — |

| CLCx Input 3         | CLCIN2PPS  | RB6                 | 0b0 1110              | _     | В                                      | С | — | В  | -                    | D          | —         | _      | В  | — | D | — | — |

| CLCx Input 4         | CLCIN3PPS  | RB7                 | 0b0 1111              | _     | В                                      | С |   | В  |                      | D          | _         | _      | В  | _ | D | _ | _ |

## TABLE 17-1: PPS INPUT REGISTER DETAILS

| Name  | Bit 7  | Bit 6  | Bit 5  | Bit 4  | Bit 3                 | Bit 2  | Bit 1  | Bit 0  |

|-------|--------|--------|--------|--------|-----------------------|--------|--------|--------|

| IOCAP | IOCAP7 | IOCAP6 | IOCAP5 | IOCAP4 | IOCAP3                | IOCAP2 | IOCAP1 | IOCAP0 |

| IOCAN | IOCAN7 | IOCAN6 | IOCAN5 | IOCAN4 | IOCAN3                | IOCAN2 | IOCAN1 | IOCAN0 |

| IOCAF | IOCAF7 | IOCAF6 | IOCAF5 | IOCAF4 | IOCAF3                | IOCAF2 | IOCAF1 | IOCAF0 |

| IOCBP | IOCBP7 | IOCBP6 | IOCBP5 | IOCBP4 | IOCBP3                | IOCBP2 | IOCBP1 | IOCBP0 |

| IOCBN | IOCBN7 | IOCBN6 | IOCBN5 | IOCBN4 | IOCBN3                | IOCBN2 | IOCBN1 | IOCBN0 |

| IOCBF | IOCBF7 | IOCBF6 | IOCBF5 | IOCBF4 | IOCBF3                | IOCBF2 | IOCBF1 | IOCBF0 |

| IOCCP | IOCCP7 | IOCCP6 | IOCCP5 | IOCCP4 | IOCCP3                | IOCCP2 | IOCCP1 | IOCCP0 |

| IOCCN | IOCCN7 | IOCCN6 | IOCCN5 | IOCCN4 | IOCCN3                | IOCCN2 | IOCCN1 | IOCCN0 |

| IOCCF | IOCCF7 | IOCCF6 | IOCCF5 | IOCCF4 | IOCCF3                | IOCCF2 | IOCCF1 | IOCCF0 |

| IOCEP | —      | _      | _      | _      | IOCEP3 <sup>(1)</sup> | _      | —      | —      |

| IOCEN | —      | —      | _      | —      | IOCEN3 <sup>(1)</sup> |        | —      |        |

| IOCEF |        | _      | _      |        | IOCEF3 <sup>(1)</sup> | _      | _      |        |

#### TABLE 18-1: IOC REGISTERS

Note 1: If MCLRE = 1 or LVP = 1, RE3 port functionality is disabled and IOC on RE3 is not available.

#### TABLE 18-2: SUMMARY OF REGISTERS ASSOCIATED WITH INTERRUPT-ON-CHANGE

| Name  | Bit 7  | Bit 6  | Bit 5  | Bit 4  | Bit 3  | Bit 2  | Bit 1  | Bit 0  | Register<br>on Page |

|-------|--------|--------|--------|--------|--------|--------|--------|--------|---------------------|

| IOCxF | IOCxF7 | IOCxF6 | IOCxF5 | IOCxF4 | IOCxF3 | IOCxF2 | IOCxF1 | IOCxF0 | 287                 |

| IOCxN | IOCxN7 | IOCxN6 | IOCxN5 | IOCxN4 | IOCxN3 | IOCxN2 | IOCxN1 | IOCxN0 | 287                 |

| IOCxP | IOCxP7 | IOCxP6 | IOCxP5 | IOCxP4 | IOCxP3 | IOCxP2 | IOCxP1 | IOCxP0 | 287                 |

Legend: — = unimplemented location, read as '0'. Shaded cells are not used by interrupt-on-change.

## 20.8 Register Definitions: Timer0 Control

| R/W-0/0         | U-0                                                                                                                                                                                                                                                                 | R-0                                                                                                                                                                                                                                                                                                | R/W-0/0         | R/W-0/0            | R/W-0/0          | R/W-0/0          | R/W-0/0      |

|-----------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------|--------------------|------------------|------------------|--------------|

| EN              |                                                                                                                                                                                                                                                                     | OUT                                                                                                                                                                                                                                                                                                | MD16            |                    | OUTP             | S<3:0>           |              |

| bit 7           |                                                                                                                                                                                                                                                                     |                                                                                                                                                                                                                                                                                                    | 1               |                    |                  |                  | bit (        |

|                 |                                                                                                                                                                                                                                                                     |                                                                                                                                                                                                                                                                                                    |                 |                    |                  |                  |              |

| Legend:         |                                                                                                                                                                                                                                                                     |                                                                                                                                                                                                                                                                                                    |                 |                    |                  |                  |              |

| R = Readab      | le bit                                                                                                                                                                                                                                                              | W = Writable                                                                                                                                                                                                                                                                                       | e bit           | U = Unimpler       | mented bit, read | l as '0'         |              |

| u = Bit is und  | changed                                                                                                                                                                                                                                                             | x = Bit is unk                                                                                                                                                                                                                                                                                     | nown            | -n/n = Value a     | at POR and BO    | R/Value at all c | other Resets |

| '1' = Bit is se | et                                                                                                                                                                                                                                                                  | '0' = Bit is cle                                                                                                                                                                                                                                                                                   | eared           |                    |                  | TPS<3:0>         |              |

| bit 7           |                                                                                                                                                                                                                                                                     | dule is enabled                                                                                                                                                                                                                                                                                    |                 | )<br>west power mo | de               |                  |              |

| bit 6           | Unimplemer                                                                                                                                                                                                                                                          | nted: Read as                                                                                                                                                                                                                                                                                      | 'O'             |                    |                  |                  |              |

| bit 5           | OUT: TMR0<br>TMR0 output                                                                                                                                                                                                                                            | Output bit (rea<br>t bit                                                                                                                                                                                                                                                                           | d-only)         |                    |                  |                  |              |

| bit 4           | 1 = TMR0 is                                                                                                                                                                                                                                                         | 0 Operating as<br>a 16-bit timer<br>an 8-bit timer                                                                                                                                                                                                                                                 | 16-Bit Timer S  | Select bit         |                  |                  |              |

| bit 3-0         | OUTPS<3:0:<br>1111 = 1:16<br>1110 = 1:15<br>1101 = 1:14<br>1100 = 1:13<br>1011 = 1:12<br>1010 = 1:11<br>1001 = 1:10<br>1000 = 1:9 F<br>0111 = 1:8 F<br>0110 = 1:7 F<br>0101 = 1:6 F<br>0100 = 1:5 F<br>0011 = 1:4 F<br>0010 = 1:3 F<br>0011 = 1:4 F<br>0010 = 1:1 F | Postscaler<br>Postscaler<br>Postscaler<br>Postscaler<br>Postscaler<br>Postscaler<br>Postscaler<br>Postscaler<br>Postscaler<br>Postscaler<br>Postscaler<br>Postscaler<br>Postscaler<br>Postscaler<br>Postscaler<br>Postscaler<br>Postscaler<br>Postscaler<br>Postscaler<br>Postscaler<br>Postscaler | ut Postscaler ( | Divider) Select    | bits             |                  |              |

## REGISTER 20-1: T0CON0: TIMER0 CONTROL REGISTER 0

| R/W-0/0         | R/W-1/1                                                                                                           | R/W-0/0                                               | R/W-1/1                          | R/W-0/0                        | R/W-1/1          | R/W-0/0     | R/W-1/1 |  |

|-----------------|-------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------|----------------------------------|--------------------------------|------------------|-------------|---------|--|

| C4TSE           | :L<1:0>                                                                                                           | C3TSE                                                 | EL<1:0>                          | C2TSE                          | EL<1:0>          | C1TSE       | :L<1:0> |  |

| bit 7           |                                                                                                                   |                                                       |                                  |                                |                  |             | bit 0   |  |

|                 | C4TSEL<1:0> C3TSEL<1:0> C2TSEL<1:0> C1TSEL<br>:<br>adable bit W = Writable bit U = Unimplemented bit, read as '0' |                                                       |                                  |                                |                  |             |         |  |

| Legend:         |                                                                                                                   |                                                       |                                  |                                |                  |             |         |  |

| R = Readable    | bit                                                                                                               | W = Writable                                          | bit                              | U = Unimplen                   | nented bit, read | as '0'      |         |  |

| -n = Value at F | POR                                                                                                               | '1' = Bit is set                                      | •                                |                                |                  |             |         |  |

| bit 7-6         | 11 = CCP4 is<br>10 = CCP4 is<br>01 = CCP4 is                                                                      | s based off Tin<br>s based off Tin<br>s based off Tin | ner5 in Captur<br>ner3 in Captur | e/Compare mo<br>e/Compare mo   | de and Timer4    | in PWM mode |         |  |

| bit 5-4         | 11 = CCP3 is<br>10 = CCP3 is<br>01 = CCP3 is                                                                      | s based off Tin<br>s based off Tin<br>s based off Tin | ner5 in Captur<br>ner3 in Captur | e/Compare mo<br>e/Compare mo   | de and Timer4    | in PWM mode |         |  |

| bit 3-2         | 11 = CCP2 is<br>10 = CCP2 is<br>01 = CCP2 is                                                                      | based off Tim<br>based off Tim<br>based off Tim       | er5 in Capture<br>er3 in Capture | e/Compare mod<br>e/Compare mod | le and Timer4 i  | n PWM mode  |         |  |

| bit 1-0         | 11 = CCP1 is<br>10 = CCP1 is                                                                                      | based off Tim<br>based off Tim<br>based off Tim       | er5 in Capture<br>er3 in Capture | e/Compare mod<br>e/Compare mod | le and Timer4 i  | n PWM mode  |         |  |

#### REGISTER 23-2: CCPTMRS0: CCP TIMERS CONTROL REGISTER 0

© 2016-2017 Microchip Technology Inc

Preliminary

## 29.0 ZERO-CROSS DETECTION (ZCD) MODULE

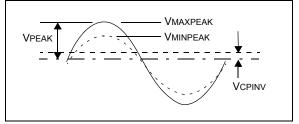

The ZCD module detects when an A/C signal crosses through the ground potential. The actual zero-crossing threshold is the zero-crossing reference voltage, VCPINV, which is typically 0.75V above ground.

The connection to the signal to be detected is through a series current-limiting resistor. The module applies a current source or sink to the ZCD pin to maintain a constant voltage on the pin, thereby preventing the pin voltage from forward biasing the ESD protection diodes. When the applied voltage is greater than the reference voltage, the module sinks current. When the applied voltage is less than the reference voltage, the module sources current. The current source and sink action keeps the pin voltage constant over the full range of the applied voltage. The ZCD module is shown in the simplified block diagram Figure 29-2.

The ZCD module is useful when monitoring an A/C waveform for, but not limited to, the following purposes:

- A/C period measurement

- Accurate long term time measurement

- Dimmer phase delayed drive

- Low EMI cycle switching

## 29.1 External Resistor Selection

The ZCD module requires a current-limiting resistor in series with the external voltage source. The impedance and rating of this resistor depends on the external source peak voltage. Select a resistor value that will drop all of the peak voltage when the current through the resistor is nominally 300  $\mu$ A. Refer to Equation 29-1 and Figure 29-1. Make sure that the ZCD I/O pin internal weak pull-up is disabled so it does not interfere with the current source and sink.

#### EQUATION 29-1: EXTERNAL RESISTOR

$$RSERIES = \frac{VPEAK}{3 \times 10^{-4}}$$

FIGURE 29-1: EXTERNA

| R/S/C-1/1        | R/S/C-0/0                      | R/W/S-0/0                              | R/W/S-0/0         | R/S/C-0/0        | R/W/S-0/0        | R/W/S-0/0        | R/W/S-0/0   |

|------------------|--------------------------------|----------------------------------------|-------------------|------------------|------------------|------------------|-------------|

| TXMTIF           | PERIF                          | ABDOVF                                 | CERIF             | FERIF            | RXBKIF           | RXFOIF           | TXCIF       |

| bit 7            |                                |                                        |                   |                  |                  |                  | bit 0       |

|                  |                                |                                        |                   |                  |                  |                  |             |

| Legend:          |                                |                                        |                   |                  |                  |                  |             |

| R = Readable     | bit                            | W = Writable                           | bit               | U = Unimpler     | mented bit, reac | l as '0'         |             |

| u = Bit is unch  | anged                          | x = Bit is unkr                        | nown              | -n/n = Value a   | at POR and BO    | R/Value at all o | ther Resets |

| '1' = Bit is set |                                | '0' = Bit is clea                      | ared              | S = Hardware     | e set            | C = Hardware     | clear       |

| h:+ 7            |                                | namit Chift Dag                        | inten Enertia las | termunt Elea hit |                  |                  |             |

| bit 7            |                                | nsmit Shift Reg<br>t shift register is |                   |                  |                  |                  |             |

|                  |                                | shift register is                      |                   |                  | (13)             |                  |             |

| bit 6            | PERIF: Parity                  | / Error Interrupt                      | Flag bit          |                  |                  |                  |             |

|                  | LIN and Parit                  | y modes:                               |                   |                  |                  | 3                |             |

|                  |                                | oyte at top of in<br>oyte at top of in |                   |                  | tv error         |                  |             |

|                  | DALI Device                    | •                                      |                   | ·                | ,                |                  |             |

|                  |                                | oyte at top of in<br>oyte at top of in |                   |                  |                  |                  |             |

|                  | Address mod                    |                                        |                   |                  |                  |                  |             |

|                  |                                | oyte at top of in<br>oyte at top of in |                   |                  | S                |                  |             |

|                  | <u>Other modes</u><br>Not used | :                                      |                   |                  |                  |                  |             |

| bit 5            | ABDOVF: AL                     | uto-baud Detect                        | t Overflow Inte   | errupt Flag bit  |                  |                  |             |

|                  | DALI mode:                     |                                        |                   |                  |                  |                  |             |

|                  |                                | measurement o<br>low during Star       |                   |                  |                  |                  |             |

|                  | Other modes                    | :                                      |                   |                  |                  |                  |             |

|                  |                                | e generator ove<br>e generator has     |                   |                  | ection sequence  | 9                |             |

| bit 4            | CERIF: Chec                    | ksum Error Inte                        | errupt Flag bit   | (LIN mode onl    | y)               |                  |             |

|                  | 1 = Checksu                    | im error                               |                   |                  |                  |                  |             |

|                  | 0 = No checl                   |                                        |                   |                  |                  |                  |             |

| bit 3            |                                | ing Error Interro                      |                   |                  |                  |                  |             |

|                  |                                | byte at top of in<br>byte at top of in |                   |                  | ning error       |                  |             |

| bit 2            | RXBKIF: Bre                    | ak Reception I                         | nterrupt Flag b   | oit              |                  |                  |             |

|                  | 1 = Break de                   |                                        |                   |                  |                  |                  |             |

|                  | 0 = No Breal                   | k detected                             |                   |                  |                  |                  |             |

| bit 1            |                                | ceive FIFO Ove                         | -                 | Flag bit         |                  |                  |             |

|                  |                                | FIFO has overf<br>FIFO has not o       |                   |                  |                  |                  |             |

| hit O            |                                |                                        |                   | 4                |                  |                  |             |

| bit 0            | I AUIF: Irans                  | smit Collision In                      | terrupt Flag bl   | IL               |                  |                  |             |

|                  | 1 - Tranarsit                  | tod word is not                        | aqual to the      | ord received a   | during transmiss | vion             |             |

## REGISTER 31-4: UXERRIR: UART ERROR INTERRUPT FLAG REGISTER

#### **REGISTER 36-18:** ADRESH: ADC RESULT REGISTER HIGH, FM = 0

| R/W-x/u          | R/W-x/u | R/W-x/u             | R/W-x/u | R/W-x/u        | R/W-x/u          | R/W-x/u        | R/W-x/u      |

|------------------|---------|---------------------|---------|----------------|------------------|----------------|--------------|

|                  |         |                     | ADRE    | S<11:4>        |                  |                |              |

| bit 7            |         |                     |         |                |                  |                | bit 0        |

|                  |         |                     |         |                |                  |                |              |

| Legend:          |         |                     |         |                |                  |                |              |

| R = Readable I   | bit     | W = Writable bit    | :       | U = Unimpler   | nented bit, read | d as '0'       |              |

| u = Bit is uncha | anged   | x = Bit is unknow   | wn      | -n/n = Value a | at POR and BC    | R/Value at all | other Resets |

| '1' = Bit is set |         | '0' = Bit is cleare | ed      |                |                  |                |              |

bit 7-0 **ADRES<11:4>**: ADC Result Register bits Upper eight bits of 12-bit conversion result.

#### **REGISTER 36-19:** ADRESL: ADC RESULT REGISTER LOW, FM = 0

| R/W-x/u | R/W-x/u | R/W-x/u | R/W-x/u | U-0 | U-0 | U-0 | U-0   |

|---------|---------|---------|---------|-----|-----|-----|-------|

|         | ADRES   | 6<3:0>  |         | —   | —   | —   | —     |

| bit 7   |         |         |         |     |     |     | bit 0 |

| Legend:              |                      |                                                       |

|----------------------|----------------------|-------------------------------------------------------|

| R = Readable bit     | W = Writable bit     | U = Unimplemented bit, read as '0'                    |

| u = Bit is unchanged | x = Bit is unknown   | -n/n = Value at POR and BOR/Value at all other Resets |

| '1' = Bit is set     | '0' = Bit is cleared |                                                       |

bit 7-4 ADRES<3:0>: ADC Result Register bits. Lower four bits of 12-bit conversion result.

bit 3-0 Reserved

## 41.0 INSTRUCTION SET SUMMARY

PIC18(L)F26/27/45/46/47/55/56/57K42 devices incorporate the standard set of PIC18 core instructions, as well as an extended set of instructions, for the optimization of code that is recursive or that utilizes a software stack. The extended set is discussed later in this section.

## 41.1 Standard Instruction Set

The standard PIC18 instruction set adds many enhancements to the previous PIC<sup>®</sup> MCU instruction sets, while maintaining an easy migration from these PIC<sup>®</sup> MCU instruction sets. Most instructions are a single program memory word (16 bits), but there are four instructions that require two-program memory locations and two that require three-program memory locations.

Each single-word instruction is a 16-bit word divided into an opcode, which specifies the instruction type and one or more operands, which further specify the operation of the instruction.

The instruction set is highly orthogonal and is grouped into four basic categories:

- Byte-oriented operations

- Bit-oriented operations

- · Literal operations

- Control operations

The PIC18 instruction set summary in Table 41-3 lists **byte-oriented**, **bit-oriented**, **literal** and **control** operations. Table 41-1 shows the opcode field descriptions.

Most **byte-oriented** instructions have three operands:

- 1. The file register (specified by 'f')

- 2. The destination of the result (specified by 'd')

- 3. The accessed memory (specified by 'a')

The file register designator 'f' specifies which file register is to be used by the instruction. The destination designator 'd' specifies where the result of the operation is to be placed. If 'd' is zero, the result is placed in the WREG register. If 'd' is one, the result is placed in the file register specified in the instruction.

All bit-oriented instructions have three operands:

- 1. The file register (specified by 'f')

- 2. The bit in the file register (specified by 'b')

- 3. The accessed memory (specified by 'a')

The bit field designator 'b' selects the number of the bit affected by the operation, while the file register designator 'f' represents the number of the file in which the bit is located. The literal instructions may use some of the following operands:

- A literal value to be loaded into a file register (specified by 'k')

- The desired FSR register to load the literal value into (specified by 'f')

- No operand required (specified by '—')

The control instructions may use some of the following operands:

- A program memory address (specified by 'n')

- The mode of the CALL or RETURN instructions (specified by 's')

- The mode of the table read and table write instructions (specified by 'm')

- No operand required (specified by '—')

All instructions are a single word, except for four double-word instructions. These instructions were made double-word to contain the required information in 32 bits. In the second word, the four MSbs are '1's. If this second word is executed as an instruction (by itself), it will execute as a NOP.

All single-word instructions are executed in a single instruction cycle, unless a conditional test is true or the program counter is changed as a result of the instruction. In these cases, the execution takes two instruction cycles, with the additional instruction cycle(s) executed as a NOP.

The double-word instructions execute in two instruction cycles.

One instruction cycle consists of four oscillator periods. Thus, for an oscillator frequency of 4 MHz, the normal instruction execution time is 1  $\mu$ s. If a conditional test is true, or the program counter is changed as a result of an instruction, the instruction execution time is 2  $\mu$ s. Two-word branch instructions (if true) would take 3  $\mu$ s.

Figure 41-1 shows the general formats that the instructions can have. All examples use the convention 'nnh' to represent a hexadecimal number.

The Instruction Set Summary, shown in Table 41-3, lists the standard instructions recognized by the Microchip Assembler (MPASM<sup>TM</sup>).

Section 41.1.1 "Standard Instruction Set" provides a description of each instruction.

| Mnemonic,<br>Operands |                                 | Description                               | Cycles     | 16-  | Bit Inst     | ruction V | Vord | Status          | Notes |

|-----------------------|---------------------------------|-------------------------------------------|------------|------|--------------|-----------|------|-----------------|-------|

| Opera                 | nds                             | Description                               | Cycles     | MSb  |              |           | LSb  | Affected        | Notes |

| BYTE-ORIE             | INTED FI                        | LE REGISTER INSTRUCTIONS                  |            |      |              |           |      |                 |       |

| ADDWF                 | f, d ,a                         | Add WREG and f                            | 1          | 0010 | 01da         | ffff      | ffff | C, DC, Z, OV, N |       |

| ADDWFC                | f, d, a                         | Add WREG and Carry bit to f               | 1          | 0010 | 00da         | ffff      | ffff | C, DC, Z, OV, N |       |

| ANDWF                 | f, d, a                         | AND WREG with f                           | 1          | 0001 | 01da         | ffff      | ffff | Z, N            |       |

| CLRF                  | f, a                            | Clear f                                   | 1          | 0110 | 101a         | ffff      | ffff | Z               |       |

| COMF                  | f, d, a                         | Complement f                              | 1          | 0001 | 11da         | ffff      | ffff | Z, N            |       |

| DECF                  | f, d, a                         | Decrement f                               | 1          | 0000 | 01da         | ffff      | ffff | C, DC, Z, OV, N |       |

| INCF                  | f, d, a                         | Increment f                               | 1          | 0010 | 10da         | ffff      | ffff | C, DC, Z, OV, N |       |

| IORWF                 | f, d, a                         | Inclusive OR WREG with f                  | 1          | 0001 | 00da         | ffff      | ffff | Z, N            |       |

| MOVF                  | f, d, a                         | Move f to WREG or f                       | 1          | 0101 | 00da         | ffff      | ffff | Z, N            |       |

| MOVFF                 | f <sub>s</sub> , f <sub>d</sub> | Move f <sub>s</sub> (source) to 1st word  | 2          | 1100 | ffff         | ffff      | ffff | None            | 2, 3  |

|                       | ° u                             | f <sub>d</sub> (destination) 2nd word     |            | 1111 | ffff         | ffff      | ffff |                 |       |

| MOVFFL                | f <sub>s</sub> , f <sub>d</sub> | Move f <sub>s</sub> (source) to           | 3          | 0000 | 0000         | 0110      | ffff | None            | 2     |

|                       | 3. u                            | g (full destination)                      |            | 1111 | ffff         | ffff      | ffgg |                 |       |

|                       |                                 | f <sub>d</sub> (full destination)3rd word |            | 1111 | dddd         | gggg      | aaaa |                 |       |

| MOVWF                 | f, a                            | Move WREG to f                            | 1          | 0110 | 111a         | ffff      | ffff | None            |       |

| MULWF                 | f, a                            | Multiply WREG with f                      | 1          | 0000 | 001a         | ffff      | ffff | None            |       |

| NEGF                  | f, a                            | Negate f                                  | 1          | 0110 | 110a         | ffff      | ffff | C, DC, Z, OV, N |       |

| RLCF                  | f, d, a                         | Rotate Left f through Carry               | 1          | 0011 | 01da         | ffff      | ffff | C, Z, N         |       |

| RLNCF                 | f, d, a                         | Rotate Left f (No Carry)                  | 1          | 0100 | 01da         | ffff      | ffff | Z, N            |       |

| RRCF                  | f, d, a                         | Rotate Right f through Carry              | 1          | 0011 | 01da<br>00da | ffff      | ffff | C, Z, N         |       |

| RRNCF                 |                                 | Rotate Right f (No Carry)                 | 1          |      |              |           | ffff | Z, N            |       |

|                       | f, d, a                         | Set f                                     |            | 0100 | 00da         | ffff      |      |                 |       |

| SETF                  | f, a                            |                                           | 1          | 0110 | 100a         | ffff      | ffff | None            |       |

| SUBFWB                | f, d, a                         | Subtract f from WREG with<br>borrow       | 1          | 0101 | 01da         | ffff      | ffff | C, DC, Z, OV, N |       |

| SUBWF                 | f, d, a                         | Subtract WREG from f                      | 1          | 0101 | 11da         | ffff      | ffff | C, DC, Z, OV, N |       |

| SUBWFB                | f, d, a                         | Subtract WREG from f with                 | 1          | 0101 | 10da         | ffff      | ffff | C, DC, Z, OV, N |       |

|                       |                                 | borrow                                    |            |      |              |           |      |                 |       |

| SWAPF                 | f, d, a                         | Swap nibbles in f                         | 1          | 0011 | 10da         | ffff      | ffff | None            |       |

| XORWF                 | f, d, a                         | Exclusive OR WREG with f                  | 1          | 0001 |              | ffff      | ffff | Z, N            |       |

| BYTE-ORIE             |                                 |                                           |            |      |              |           |      |                 |       |

| CPFSEQ                | f, a                            | Compare f with WREG, skip =               | 1 (2 or 3) | 0110 | 001a         | ffff      | ffff | None            | 1     |

| CPFSGT                | f, a                            | Compare f with WREG, skip >               | 1 (2 or 3) | 0110 | 010a         | ffff      | ffff | None            | 1     |

| CPFSLT                | f, a                            | Compare f with WREG, skip <               | 1 (2 or 3) | 0110 | 000a         | ffff      | ffff | None            | 1     |

| DECFSZ                | f, d, a                         | Decrement f, Skip if 0                    | 1 (2 or 3) | 0010 | 11da         | ffff      | ffff | None            | 1     |

| DCFSNZ                | f, d, a                         | Decrement f, Skip if Not 0                | 1 (2 or 3) |      | 11da         | ffff      | ffff | None            | 1     |

| INCFSZ                | f, d, a                         | Increment f, Skip if 0                    | 1 (2 or 3) |      | 11da         | ffff      | ffff | None            | 1     |

| INFSNZ                | f, d, a                         | Increment f, Skip if Not 0                | 1 (2 or 3) |      | 10da         | ffff      | ffff | None            | 1     |

| TSTFSZ                | f, a                            | Test f, skip if 0                         | 1 (2 or 3) |      | 011a         | ffff      | ffff | None            | 1     |

|                       |                                 |                                           | . (2 0. 0) | 0110 | 0110         |           |      |                 |       |

| BCF                   | f, b, a                         | Bit Clear f                               | 1          | 1001 | bbba         | ffff      | ffff | None            |       |

| BSF                   | f, b, a                         | Bit Set f                                 | 1          |      | bbba         | ffff      | ffff | None            |       |

| BTG                   | f, d, a                         | Bit Toggle f                              | 1          | 0111 |              | ffff      | ffff | None            |       |

|                       |                                 | PINSTRUCTIONS                             |            |      |              |           |      |                 | 1     |

| BTFSC                 | f, b, a                         | Bit Test f, Skip if Clear                 | 1 (2 or 3) | 1011 | bbba         | ffff      | ffff | None            | 1     |

| BTFSS                 | f, b, a                         | Bit Test f, Skip if Set                   | 1 (2 or 3) |      |              | ffff      | ffff | None            | 1     |

#### TABLE 41-2: INSTRUCTION SET

Note 1: If Program Counter (PC) is modified or a conditional test is true, the instruction requires an additional cycle. The extra cycle is executed as a NOP.

2: Some instructions are multi word instructions. The second/third words of these instructions will be decoded as a NOP, unless the first word of the instruction retrieves the information embedded in these 16-bits. This ensures that all program memory locations have a valid instruction.

3: f<sub>s</sub> and f<sub>d</sub> do not cover the full memory range. 2 MSBs of bank selection are forced to 'b00 to limit the range of these instructions to lower 4k addressing space.

| Address          | Name     | Bit 7  | Bit 6 | Bit 5  | Bit 4   | Bit 3   | Bit 2  | Bit 1  | Bit 0 | Regist<br>on pag |

|------------------|----------|--------|-------|--------|---------|---------|--------|--------|-------|------------------|

| 3EE8h            | ADACCL   |        |       |        | AC      | C       |        |        |       | 631              |

| 3EE7h            | ADFLTRH  |        |       |        | FL      | TR      |        |        |       | 627              |

| 3EE6h            | ADFLTRL  |        |       |        | FL      | TR      |        |        |       | 627              |

| 3EE5h            | ADSTPTH  |        |       |        | ST      | PT      |        |        |       | 632              |

| 3EE4h            | ADSTPTL  |        |       |        | ST      | PT      |        |        |       | 632              |

| 3EE3h            | ADERRH   |        |       |        | EF      | RR      |        |        |       | 633              |

| 3EE2h            | ADERRL   |        |       |        | EF      | RR      |        |        |       | 633              |

| 3EE1h            | ADUTHH   |        |       |        | U       | ſĦ      |        |        |       | 634              |

| 3EE0h            | ADUTHL   |        |       |        | U       | ſĦ      |        |        |       | 634              |

| 3EDFh            | ADLTHH   |        |       |        | LT      | Ή       |        |        |       | 633              |

| 3EDEh            | ADLTHL   |        |       |        | LT      | Ή       |        |        |       | 634              |

| 3EDDh -<br>3ED8h | _        |        |       |        | Unimple | emented |        |        |       |                  |

| 3ED7h            | ADCP     | ON     | _     | _      | _       | _       | _      | _      | CPRDY | 636              |

| 3ED6h -<br>3ECBh | _        |        |       |        | Unimple | emented |        |        |       |                  |

| 3ECAh            | HLVDCON1 | _      | _     | _      | _       |         | 5      | SEL    |       | 658              |

| 3EC9h            | HLVDCON0 | EN     |       | OUT    | RDY     | _       | —      | INTH   | INTL  | 657              |

| 3EC8h -<br>3EC4h | -        |        |       |        | Unimple | emented |        |        |       |                  |

| 3EC3h            | ZCDCON   | SEN    | _     | OUT    | POL     | _       | _      | INTP   | INTN  | 462              |

| 3EC2h            | _        |        |       |        | Unimple | emented |        |        | •     |                  |

| 3EC1h            | FVRCON   | EN     | RDY   | TSEN   | TSRNG   | CDA     | FVR    | A      | DFVR  | 597              |

| 3EC0h            | CMOUT    | _      | _     | _      |         | _       | _      | C2OUT  | C10UT | 650              |

| 3EBFh            | CM1PCH   | _      | _     | _      | _       | _       |        | PCH    | •     | 650              |

| 3EBEh            | CM1NCH   | _      | _     | _      | _       | _       |        | NCH    |       | 649              |

| 3EBDh            | CM1CON1  | _      | _     | _      | _       | _       | _      | INTP   | INTN  | 649              |

| 3EBCh            | CM1CON0  | EN     | OUT   | _      | POL     | _       | _      | HYS    | SYNC  | 648              |

| 3EBBh            | CM2PCH   | _      | _     | _      | _       | _       |        | PCH    | •     | 650              |

| 3EBAh            | CM2NCH   |        | _     |        | _       |         |        | NCH    |       | 649              |

| 3EB9h            | CM2CON1  |        |       | _      | _       | _       | _      | INTP   | INTN  | 649              |

| 3EB8h            | CM2CON0  | EN     | OUT   | _      | POL     | _       | _      | HYS    | SYNC  | 648              |

| 3EB7h -<br>3E9Fh | _        |        |       |        | Unimple | emented |        |        |       |                  |

| 3E9Eh            | DAC1CON0 | EN     | _     | OE1    | OE2     | P       | SS     | _      | NSS   | 640              |

| 3E9Dh            | _        |        |       |        | Unimple | mented  |        |        |       |                  |

| 3E9Ch            | DAC1CON1 | _      | _     | _      |         |         | DATA   |        |       | 641              |

| 3E9Bh -<br>3DFBh | —        |        |       |        | Unimple | mented  |        |        |       |                  |

| 3DFAh            | U1ERRIE  | TXMTIE | PERIE | ABDOVE | CERIE   | FERIE   | RXBKIE | RXFOIE | TXCIE | 502              |

| 3DF9h            | U1ERRIR  | TXMTIF | PERIF | ABDOVF | CERIF   | FERIF   | RXBKIF | RXFOIF | TXCIF | 501              |

| 3DF8h            | U1UIR    | WUIF   | ABDIF | _      | _       | _       | ABDIE  | —      | —     | 503              |

| 3DF7h            | U1FIFO   | TXWRE  | STPMD | TXBE   | TXBF    | RXIDL   | XON    | RXBE   | RXBF  | 504              |

| 3DF6h            | U1BRGH   |        |       |        | BR      | GH      |        |        |       | 505              |

| 3DF5h            | U1BRGL   |        |       |        | BR      | GL      |        |        |       | 505              |

| 3DF4h            | U1CON2   | RUNOVF | RXPOL | ST     | ΓP      | C0EN    | TXPOL  | F      | LO    | 500              |

| 3DF3h            | U1CON1   | ON     | _     | _      | WUE     | RXBIMD  | _      | BRKOVR | SENDB | 499              |

| 3DF2h            | U1CON0   | BRGS   | ABDEN | TXEN   | RXEN    |         |        | ODE    |       | 498              |

| 3DF1h            | U1P3H    | _      | _     | _      | _       |         | _      |        | P3H   | 509              |

#### **TABLE 42-1**: REGISTER FILE SUMMARY FOR PIC18(L)F26/27/45/46/47/55/56/57K42 DEVICES

x = unknown, u = unchanged, — = unimplemented, q = value depends on condition Legend: Note

1: Unimplemented in LF devices.

2: Unimplemented in PIC18(L)F26/27K42.

Unimplemented on PIC18(L)F26/27/45/46/47K42 devices. 3:

Unimplemented in PIC18(L)F45/55K42. 4:

## APPENDIX A: REVISION HISTORY

## Revision A (6/2017)

Initial release of the document.

### Revision B (12/2017)

Standard operating conditions updated in Section 44.0, Electrical Specifications. Other minor corrections.