#### Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Details                    |                                                                            |

|----------------------------|----------------------------------------------------------------------------|

| Product Status             | Active                                                                     |

| Core Processor             | PIC                                                                        |

| Core Size                  | 8-Bit                                                                      |

| Speed                      | 64MHz                                                                      |

| Connectivity               | I <sup>2</sup> C, LINbus, SPI, UART/USART                                  |

| Peripherals                | Brown-out Detect/Reset, DMA, HLVD, POR, PWM, WDT                           |

| Number of I/O              | 25                                                                         |

| Program Memory Size        | 128KB (64K x 16)                                                           |

| Program Memory Type        | FLASH                                                                      |

| EEPROM Size                | 1K x 8                                                                     |

| RAM Size                   | 8K x 8                                                                     |

| Voltage - Supply (Vcc/Vdd) | 2.3V ~ 5.5V                                                                |

| Data Converters            | A/D 24x12b; D/A 1x5b                                                       |

| Oscillator Type            | Internal                                                                   |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                          |

| Mounting Type              | Through Hole                                                               |

| Package / Case             | 28-DIP (0.300", 7.62mm)                                                    |

| Supplier Device Package    | 28-SPDIP                                                                   |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/pic18f27k42-i-sp |

|                            |                                                                            |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

### REGISTER 3-4: DMA2PR: DMA2 PRIORITY REGISTER

| U-0   | U-0 | U-0 | U-0 | U-0 | R/W-0/0 | R/W-1/1     | R/W-1/1 |

|-------|-----|-----|-----|-----|---------|-------------|---------|

| —     | —   | —   | —   | _   | [       | DMA2PR<2:0> |         |

| bit 7 |     |     |     |     |         |             | bit 0   |

#### Legend:

| R = Readable bit     | W = Writable bit   | U = Unimplemented bit, read as '0'                    |

|----------------------|--------------------|-------------------------------------------------------|

| u = Bit is unchanged | x = Bit is unknown | -n/n = Value at POR and BOR/Value at all other Resets |

| 1 = bit is set       | 0 = bit is cleared | HS = Hardware set                                     |

#### bit 7-3 Unimplemented: Read as '0'

bit 2-0 DMA2PR<2:0>: DMA2 Priority Selection bits

### REGISTER 3-5: SCANPR: SCANNER PRIORITY REGISTER

| U-0   | U-0 | U-0 | U-0 | U-0 | R/W-1/1 | R/W-0/0     | R/W-0/0 |

|-------|-----|-----|-----|-----|---------|-------------|---------|

| —     | —   | —   | _   | —   |         | SCANPR<2:0> |         |

| bit 7 |     |     |     |     |         |             | bit 0   |

| Legend:              |                    |                                                       |

|----------------------|--------------------|-------------------------------------------------------|

| R = Readable bit     | W = Writable bit   | U = Unimplemented bit, read as '0'                    |

| u = Bit is unchanged | x = Bit is unknown | -n/n = Value at POR and BOR/Value at all other Resets |

| 1 = bit is set       | 0 = bit is cleared | HS = Hardware set                                     |

#### bit 7-3 Unimplemented: Read as '0'

bit 2-0 SCANPR<2:0>: Scanner Priority Selection bits

### REGISTER 3-6: PRLOCK: PRIORITY LOCK REGISTER

| U-0   | U-0 | U-0 | U-0 | U-0 | U-0 | U-0 | R/W-0/0  |

|-------|-----|-----|-----|-----|-----|-----|----------|

| —     | —   | —   | —   | —   | —   | —   | PRLOCKED |

| bit 7 |     |     |     |     |     |     | bit 0    |

| Legend:              |                    |                                                       |

|----------------------|--------------------|-------------------------------------------------------|

| R = Readable bit     | W = Writable bit   | U = Unimplemented bit, read as '0'                    |

| u = Bit is unchanged | x = Bit is unknown | -n/n = Value at POR and BOR/Value at all other Resets |

| 1 = bit is set       | 0 = bit is cleared | HS = Hardware set                                     |

bit 7-1 Unimplemented: Read as '0'

bit 0 PRLOCKED: PR Register Lock bit<sup>(1, 2)</sup>

0 = Priority Registers can be modified by write operations; Peripherals do not have access to the memory

1 = Priority Registers are locked and cannot be written; Peripherals have access to the memory

- Note 1: The PRLOCKED bit can only be set or cleared after the unlock sequence.

- 2: If PR1WAY = 1, the PRLOCKED bit cannot be cleared after it has been set. A device Reset will clear the bit and allow one more set.

### TABLE 4-7: SPECIAL FUNCTION REGISTER MAP FOR PIC18(L)F26/27/45/46/47/55/56/57K42 DEVICES BANK 60

| 3CFFh | —       | 3CDFh | — | 3CBFh | — | 3C9Fh | — | 3C7Fh |          | 3C5Fh | CLC4GLS3 | 3C3Fh | — | 3C1Fh | — |

|-------|---------|-------|---|-------|---|-------|---|-------|----------|-------|----------|-------|---|-------|---|

| 3CFEh | MD1CARH | 3CDEh | — | 3CBEh | — | 3C9Eh | — | 3C7Eh | CLCDATA0 | 3C5Eh | CLC4GLS2 | 3C3Eh | — | 3C1Eh | _ |

| 3CFDh | MD1CARL | 3CDDh | — | 3CBDh | — | 3C9Dh | — | 3C7Dh | CLC1GLS3 | 3C5Dh | CLC4GLS1 | 3C3Dh | — | 3C1Dh | _ |

| 3CFCh | MD1SRC  | 3CDCh | — | 3CBCh | _ | 3C9Ch | — | 3C7Ch | CLC1GLS2 | 3C5Ch | CLC4GLS0 | 3C3Ch | — | 3C1Ch | — |

| 3CFBh | MD1CON1 | 3CDBh | — | 3CBBh | — | 3C9Bh | — | 3C7Bh | CLC1GLS1 | 3C5Bh | CLC4SEL3 | 3C3Bh | — | 3C1Bh | _ |

| 3CFAh | MD1CON0 | 3CDAh | — | 3CBAh | — | 3C9Ah | — | 3C7Ah | CLC1GLS0 | 3C5Ah | CLC4SEL2 | 3C3Ah | — | 3C1Ah | — |

| 3CF9h | —       | 3CD9h | — | 3CB9h | — | 3C99h | — | 3C79h | CLC1SEL3 | 3C59h | CLC4SEL1 | 3C39h | — | 3C19h | _ |

| 3CF8h | —       | 3CD8h | — | 3CB8h | — | 3C98h | — | 3C78h | CLC1SEL2 | 3C58h | CLC4SEL0 | 3C38h | — | 3C18h | _ |

| 3CF7h | —       | 3CD7h | — | 3CB7h | — | 3C97h | — | 3C77h | CLC1SEL1 | 3C57h | CLC4POL  | 3C37h | — | 3C17h | _ |

| 3CF6h | —       | 3CD6h | — | 3CB6h | — | 3C96h | — | 3C76h | CLC1SEL0 | 3C56h | CLC4CON  | 3C36h | — | 3C16h | _ |

| 3CF5h | —       | 3CD5h | — | 3CB5h | — | 3C95h | — | 3C75h | CLC1POL  | 3C55h |          | 3C35h | — | 3C15h | _ |

| 3CF4h | —       | 3CD4h | — | 3CB4h | — | 3C94h | — | 3C74h | CLC1CON  | 3C54h |          | 3C34h | — | 3C14h | — |

| 3CF3h | _       | 3CD3h | _ | 3CB3h | _ | 3C93h | _ | 3C73h | CLC2GLS3 | 3C53h | _        | 3C33h | _ | 3C13h | _ |

| 3CF2h | _       | 3CD2h | _ | 3CB2h | _ | 3C92h | _ | 3C72h | CLC2GLS2 | 3C52h | _        | 3C32h | _ | 3C12h | _ |

| 3CF1h | _       | 3CD1h | _ | 3CB1h | _ | 3C91h | _ | 3C71h | CLC2GLS1 | 3C51h | _        | 3C31h | _ | 3C11h | _ |

| 3CF0h | _       | 3CD0h | _ | 3CB0h | _ | 3C90h | _ | 3C70h | CLC2GLS0 | 3C50h | _        | 3C30h | _ | 3C10h | _ |

| 3CEFh | _       | 3CCFh | _ | 3CAFh | _ | 3C8Fh | _ | 3C6Fh | CLC2SEL3 | 3C4Fh | _        | 3C2Fh | _ | 3C0Fh | _ |

| 3CEEh | _       | 3CCEh | _ | 3CAEh | _ | 3C8Eh | _ | 3C6Eh | CLC2SEL2 | 3C4Eh | _        | 3C2Eh | _ | 3C0Eh | _ |

| 3CEDh | _       | 3CCDh | _ | 3CADh | _ | 3C8Dh | _ | 3C6Dh | CLC2SEL1 | 3C4Dh | _        | 3C2Dh | _ | 3C0Dh | _ |

| 3CECh | _       | 3CCCh | _ | 3CACh | _ | 3C8Ch | _ | 3C6Ch | CLC2SEL0 | 3C4Ch | _        | 3C2Ch | _ | 3C0Ch | _ |

| 3CEBh | _       | 3CCBh | _ | 3CABh | _ | 3C8Bh | _ | 3C6Bh | CLC2POL  | 3C4Bh | _        | 3C2Bh | _ | 3C0Bh | _ |

| 3CEAh | _       | 3CCAh | _ | 3CAAh | _ | 3C8Ah | _ | 3C6Ah | CLC2CON  | 3C4Ah | _        | 3C2Ah | _ | 3C0Ah | _ |

| 3CE9h | _       | 3CC9h | _ | 3CA9h | _ | 3C89h | _ | 3C69h | CLC3GLS3 | 3C49h | _        | 3C29h | _ | 3C09h | _ |

| 3CE8h | _       | 3CC8h | _ | 3CA8h | _ | 3C88h | _ | 3C68h | CLC3GLS2 | 3C48h | _        | 3C28h | _ | 3C08h | _ |

| 3CE7h | _       | 3CC7h | _ | 3CA7h | _ | 3C87h | _ | 3C67h | CLC3GLS1 | 3C47h | _        | 3C27h | _ | 3C07h | _ |

| 3CE6h | CLKRCLK | 3CC6h | _ | 3CA6h | _ | 3C86h | _ | 3C66h | CLC3GLS0 | 3C46h | _        | 3C26h | _ | 3C06h | _ |

| 3CE5h | CLKRCON | 3CC5h | _ | 3CA5h | _ | 3C85h | _ | 3C65h | CLC3SEL3 | 3C45h | _        | 3C25h | _ | 3C05h | _ |

| 3CE4h | —       | 3CC4h | — | 3CA4h | — | 3C84h | — | 3C64h | CLC3SEL2 | 3C44h | —        | 3C24h | — | 3C04h | — |

| 3CE3h | —       | 3CC3h | — | 3CA3h | — | 3C83h | — | 3C63h | CLC3SEL1 | 3C43h | —        | 3C23h | _ | 3C03h | — |

| 3CE2h | —       | 3CC2h | — | 3CA2h | — | 3C82h | — | 3C62h | CLC3SEL0 | 3C42h | _        | 3C22h | — | 3C02h | _ |

| 3CE1h | —       | 3CC1h | — | 3CA1h | — | 3C81h | — | 3C61h | CLC3POL  | 3C41h | —        | 3C21h | — | 3C01h | — |

| 3CE0h | —       | 3CC0h |   | 3CA0h | — | 3C80h | — | 3C60h | CLC3CON  | 3C40h | —        | 3C20h | — | 3C00h | — |

Legend: Unimplemented data memory locations and registers, read as '0'.

Note 1: Unimplemented in LF devices.

2: Unimplemented in PIC18(L)F26/27K42.

**3:** Unimplemented in PIC18(L)F26/27/45/46/47K42.

| REGISTER      | S-4: CONFI                                                                                                                                                                                       | GURATION                                                                                                                                                          | WORD 2H (3                                                                                                                        | 30 0003h)                                                                                           |                  |                 |                      |  |

|---------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------|------------------|-----------------|----------------------|--|

| R/W-1         | U-1                                                                                                                                                                                              | R/W-1                                                                                                                                                             | R/W-1                                                                                                                             | R/W-1                                                                                               | R/W-1            | R/W-1           | R/W-1                |  |

| XINST         | —                                                                                                                                                                                                | DEBUG                                                                                                                                                             | STVREN                                                                                                                            | PPS1WAY                                                                                             | ZCD              | BORV            | <1:0> <sup>(1)</sup> |  |

| bit 7         |                                                                                                                                                                                                  |                                                                                                                                                                   |                                                                                                                                   |                                                                                                     |                  |                 | bit C                |  |

|               |                                                                                                                                                                                                  |                                                                                                                                                                   |                                                                                                                                   |                                                                                                     |                  |                 |                      |  |

| Legend:       |                                                                                                                                                                                                  |                                                                                                                                                                   |                                                                                                                                   |                                                                                                     |                  |                 |                      |  |

| R = Readab    | ole bit                                                                                                                                                                                          | W = Writable                                                                                                                                                      | bit                                                                                                                               | U = Unimplem                                                                                        | nented bit, read | d as '1'        |                      |  |

| -n = Value fo | or blank device                                                                                                                                                                                  | '1' = Bit is se                                                                                                                                                   | t                                                                                                                                 | '0' = Bit is clea                                                                                   | ared             | x = Bit is unkr | nown                 |  |

| bit 7         |                                                                                                                                                                                                  | instruction set                                                                                                                                                   | and Indexed                                                                                                                       | t<br>Addressing mod<br>Addressing mod                                                               |                  |                 | e)                   |  |

| bit 6         | Unimplemente                                                                                                                                                                                     | ed: Read as '1                                                                                                                                                    | ,                                                                                                                                 |                                                                                                     |                  |                 |                      |  |

| bit 5         | it 5 <b>DEBUG</b> : Debugger Enable bit<br>1 = Background debugger is disabled<br>0 = Background debugger is enabled                                                                             |                                                                                                                                                                   |                                                                                                                                   |                                                                                                     |                  |                 |                      |  |

| bit 4         | STVREN: Stac<br>1 = Stack Ove<br>0 = Stack Ove                                                                                                                                                   | rflow or Under                                                                                                                                                    | flow will cause                                                                                                                   | e a Reset                                                                                           |                  |                 |                      |  |

| bit 3         | cycle                                                                                                                                                                                            | ED bit can be                                                                                                                                                     | cleared and se                                                                                                                    | nable bit<br>et only once; PP<br>ed multiple time                                                   | C                |                 |                      |  |

| bit 2         | <b>ZCD</b> : Zero-Cro<br>1 = ZCD is dis<br>0 = ZCD is alv                                                                                                                                        | abled; ZCD ca                                                                                                                                                     |                                                                                                                                   | by setting the b                                                                                    | oit SEN of the 2 | ZCDCON regis    | ter                  |  |

| bit 1-0       | BORV<1:0>: E<br><u>PIC18FXXK42</u><br>11 = Brown-ou<br>10 = Brown-ou<br>01 = Brown-ou<br>00 = Brown-ou<br><u>PIC18LFXXK4</u><br>11 = Brown-ou<br>10 = Brown-ou<br>01 = Brown-ou<br>00 = Brown-ou | Devices:<br>It Reset Voltag<br>It Reset Voltag<br>It Reset Voltag<br>It Reset Voltag<br><u>2 Device:</u><br>It Reset Voltag<br>It Reset Voltag<br>It Reset Voltag | le (VBOR) is se<br>le (VBOR) is se | et to 2.45V<br>et to 2.45V<br>et to 2.7V<br>et to 2.85V<br>et to 1.90V<br>et to 2.45V<br>et to 2.7V |                  |                 |                      |  |

### **Note 1:** The higher voltage setting is recommended for operation at or above 16 MHz.

| REGISTER 5                                                                                             | -7: CONF                                                                                              | <b>GURATION V</b>                                       | VORD 4L (3       | 0 0006h)            |                      |           |       |  |

|--------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------|---------------------------------------------------------|------------------|---------------------|----------------------|-----------|-------|--|

| R/W-1                                                                                                  | U-1                                                                                                   | U-1                                                     | R/W-1            | R/W-1               | R/W-1                | R/W-1     | R/W-1 |  |

| WRTAPP (1)                                                                                             | — — <del>SAFEN <sup>(1)</sup></del>                                                                   |                                                         |                  | BBEN <sup>(1)</sup> | (1) BBSIZE<2:0> (2)  |           |       |  |

| bit 7                                                                                                  |                                                                                                       | ·                                                       |                  |                     |                      |           | bit C |  |

| [                                                                                                      |                                                                                                       |                                                         |                  |                     |                      |           |       |  |

| Legend:                                                                                                |                                                                                                       |                                                         |                  |                     |                      |           |       |  |

| R = Readable                                                                                           | bit                                                                                                   | W = Writable                                            | bit              | U = Unimple         | mented bit, rea      | ad as '1' |       |  |

| -n = Value for blank device                                                                            |                                                                                                       | '1' = Bit is set                                        | '1' = Bit is set |                     | '0' = Bit is cleared |           | nown  |  |

| bit 7                                                                                                  | 1 = Applicat                                                                                          | plication Block<br>ion Block is NO<br>ion Block is writ | T write-protec   |                     |                      |           |       |  |

| bit 6-5                                                                                                | Unimplemen                                                                                            | ted: Read as '1                                         | ,<br>-           |                     |                      |           |       |  |

| bit 4 SAFEN: Storage Area Flash Enable bit <sup>(1)</sup><br>1 = SAF is disabled<br>0 = SAF is enabled |                                                                                                       |                                                         |                  |                     |                      |           |       |  |

| bit 3                                                                                                  | bit 3 BBEN: Boot Block Enable bit <sup>(1)</sup><br>1 = Boot Block disabled<br>0 = Boot Block enabled |                                                         |                  |                     |                      |           |       |  |

|                                                                                                        |                                                                                                       |                                                         |                  |                     |                      |           |       |  |

bit 2-0 BBSIZE<2:0>: Boot Block Size Selection bits<sup>(2)</sup> Refer to Table 5-1.

- Note 1: Bits are implemented as sticky bits. Once protection is enabled through ICSP<sup>™</sup> or a self-write, it can only be reset through a Bulk Erase.

- 2: BBSIZE<2:0> bits can only be changed when BBEN = 1. Once BBEN = 0, BBSIZE<2:0> can only be changed through a Bulk Erase.

| BBEN | BBSIZE<2:0> | Boot Block Size | END_ADDRESS_BOOT | Device Size <sup>(1)</sup> |        |     |  |

|------|-------------|-----------------|------------------|----------------------------|--------|-----|--|

| DDEN | BB3IZE Z.02 | (words)         | END_ADDRESS_BOOT | 16k                        | 32k    | 64k |  |

| 1    | XXX         | 0               | _                | Х                          | Х      | Х   |  |

| 0    | 111         | 512             | 00 03FFh         | Х                          | Х      | Х   |  |

| 0    | 110         | 1024            | 00 07FFh         | Х                          | Х      | Х   |  |

| 0    | 101         | 2048            | 00 0FFFh         | Х                          | Х      | Х   |  |

| 0    | 100         | 4096            | 00 1FFFh         | Х                          | Х      | Х   |  |

| 0    | 011         | 8192            | 00 3FFFh         | Х                          | Х      | Х   |  |

| 0    | 010         | 16384           | 00 7FFFh         | _                          | Х      | Х   |  |

| 0    | 001         | 32768           | 00 FFFFh         |                            | Note 2 | Х   |  |

| 0    | 000         | 32768           | 00 FFFFh         | _                          | _      | _   |  |

#### TABLE 5-1: BOOT BLOCK SIZE BITS

Note 1: For each device, the quoted device size specification is listed in Table 4-1.

2: The maximum boot block size is half the user program memory size. All selections higher than the maximum size default to maximum boot block size of half PFM. For example, all settings of BBSIZE = 000 through BBSIZE = 010, default to a boot block size of 16 kW on a 32 kW device.

### 5.7 Device Information Area

The Device Information Area (DIA) is a dedicated region in the Program memory space. The DIA contains the calibration data for the internal temperature indicator module, stores the Microchip Unique Identifier words and the Fixed Voltage Reference voltage readings measured in mV.

The complete DIA table is shown in Table 5-3: Device Information Area, followed by a description of each region and its functionality. The data is mapped from 3F0000h to 3F003Fh in the PIC18(L)F26/27/45/46/47/55/56/57K42 family. These locations are read-only and cannot be erased or modified by the user. The data is programmed into the device during manufacturing.

| Address Range     | Name of Region        | Standard Device Information                                      |  |  |  |  |  |

|-------------------|-----------------------|------------------------------------------------------------------|--|--|--|--|--|

|                   | MUI0                  |                                                                  |  |  |  |  |  |

|                   | MUI1                  |                                                                  |  |  |  |  |  |

| 3F0000h-3F000Bh   | MUI2                  | Microchip Unique Identifier (6 Words)                            |  |  |  |  |  |

| 3F000011-3F000B11 | MUI3                  | Microchip Onique Identiner (8 Words)                             |  |  |  |  |  |

|                   | MUI4                  |                                                                  |  |  |  |  |  |

|                   | MUI5                  |                                                                  |  |  |  |  |  |

| 3F000Ch-3F000Fh   | MUI6                  | Jnassigned (2 Words)                                             |  |  |  |  |  |

| 3F000CII-3F000FII | MUI7                  | Chassigned (2 Words)                                             |  |  |  |  |  |

|                   | EUI0                  |                                                                  |  |  |  |  |  |

|                   | EUI1                  |                                                                  |  |  |  |  |  |

|                   | EUI2                  |                                                                  |  |  |  |  |  |

|                   | EUI3                  |                                                                  |  |  |  |  |  |

| 3F0010h-3F0023h   | EUI4                  | Optional External Unique Identifier (10 Marda)                   |  |  |  |  |  |

| 3F001011-3F002311 | EUI5                  | Optional External Unique Identifier (10 Words)                   |  |  |  |  |  |

|                   | EUI6                  |                                                                  |  |  |  |  |  |

|                   | EUI7                  |                                                                  |  |  |  |  |  |

|                   | EUI8                  |                                                                  |  |  |  |  |  |

|                   | EUI9                  |                                                                  |  |  |  |  |  |

| 3F0024h-3F0025h   |                       | Reserved (1 Word)                                                |  |  |  |  |  |

| 3F0026h-3F0027h   | TSLR2                 | Temperature Indicator ADC reading at @ 90°C (low range setting)  |  |  |  |  |  |

| 3F0028h-3F0029h   |                       | Reserved (1 Word)                                                |  |  |  |  |  |

| 3F002Ah-3F002Bh   |                       | Reserved (1 Word)                                                |  |  |  |  |  |

| 3F002Ch-3F002Dh   | TSHR2                 | Temperature Indicator ADC reading at @ 90°C (high range setting) |  |  |  |  |  |

| 3F002Eh-3F002Fh   |                       | Reserved (1 Word)                                                |  |  |  |  |  |

| 3F0030h-3F0031h   | FVRA1X                | ADC FVR1 Output voltage for 1x setting (in mV)                   |  |  |  |  |  |

| 3F0032h-3F0033h   | FVRA2X                | ADC FVR1 Output Voltage for 2x setting (in mV)                   |  |  |  |  |  |

| 3F0034h-3F0035h   | FVRA4X                | ADC FVR1 Output Voltage for 4x setting (in mV)                   |  |  |  |  |  |

| 3F0036h-3F0037h   | FVRC1X                | Comparator FVR2 output voltage for 1x setting (in mV)            |  |  |  |  |  |

| 3F0038h-3F0039h   | FVRC2X                | Comparator FVR2 output voltage for 2x setting (in mV)            |  |  |  |  |  |

| 3F003Ah-3F003Bh   | FVRC4X <sup>(1)</sup> | Comparator FVR2 output voltage for 4x setting (in mV)            |  |  |  |  |  |

| 3F003Ch-3F003Fh   |                       | Unassigned (2 Words)                                             |  |  |  |  |  |

TABLE 5-3: DEVICE INFORMATION AREA

**Note 1:** Value not present on LF devices.

### 5.7.1 MICROCHIP UNIQUE IDENTIFIER (MUI)

The PIC18(L)F26/27/45/46/47/55/56/57K42 devices are individually encoded during final manufacturing with a Microchip Unique Identifier, or MUI. The MUI cannot be user-erased. This feature allows for manufacturing traceability of Microchip Technology devices in applications where this is a required. It may also be used by the application manufacturer for a number of functions that require unverified unique identification, such as:

- · Tracking the device

- Unique serial number

The MUI consists of six program words. When read together, these fields form a unique identifier. The MUI is stored in nine read-only locations, located between 3F0000h to 3F000Fh in the DIA space. Table 5-3 lists the addresses of the identifier words.

| Note: | For applications that require verified |

|-------|----------------------------------------|

|       | unique identification, contact your    |

|       | Microchip Technology sales office to   |

|       | create a Serialized Quick Turn         |

|       | Programming <sup>sм</sup> option.      |

### 5.7.2 EXTERNAL UNIQUE IDENTIFIER (EUI)

The EUI data is stored at locations 3F0010h to 3F0023h in the Program Memory region. This region is an optional space for placing application specific information. The data is coded per customer requirements during manufacturing.

Note: Data is stored in this address range on receiving a request from the customer. The customer may contact the local sales representative, or Field Applications Engineer, and provide them the unique identifier information that is supposed to be stored in this region.

### 5.7.3 ANALOG-TO-DIGITAL CONVERSION DATA OF THE TEMPERATURE SENSOR

The purpose of the Temperature Sensor module is to provide a temperature-dependent voltage that can be measured by an analog module, see Section 35.0 "Temperature Indicator Module".

The DIA table contains the internal ADC measurement values of the Temperature sensor for Low and High range at fixed points of reference. The values are measured during test and are unique to each device. The measurement data is stored in the DIA memory region as hexadecimal numbers corresponding to the ADC conversion result. The calibration data can be used to plot the approximate sensor output voltage, VTSENSE vs. Temperature curve without having to make calibration measurements in the application. For more information on the operation of the Temperature Sensor, refer to Section 35.0 "Temperature Indicator Module".

- **TSLR2**: Address 3F0026h to 3F0027h store the measurements for the low-range setting of the Temperature Sensor at VDD = 3V.

- **TSHR2**: Address 3F002Ch to 3F002Dh store the measurements for the High Range setting of the Temperature Sensor at VDD = 3V.

- The stored measurements are made by the device ADC using the internal VREF = 2.048V.

### 7.2.2 INTERNAL CLOCK SOURCES

The device may be configured to use the internal oscillator block as the system clock by performing one of the following actions:

- Program the RSTOSC<2:0> bits in Configuration Words to select the INTOSC clock source, which will be used as the default system clock upon a device Reset.

- Write the NOSC<2:0> bits in the OSCCON1 register to switch the system clock source to the internal oscillator during run-time. See Section 7.3 "Clock Switching" for more information.

In INTOSC mode, OSC1/CLKIN is available for general purpose I/O, provided that FEXTOSC is configured to 'oscillator is not enabled'. OSC2/CLKOUT is available for general purpose I/O or CLKOUT.

The function of the OSC2/CLKOUT pin is determined by the CLKOUTEN bit in Configuration Words.

The internal oscillator block has two independent oscillators that can produce two internal system clock sources.

- 1. The **HFINTOSC** (High-Frequency Internal Oscillator) is factory-calibrated and operates from 1 to 64 MHz. The frequency of HFINTOSC can be selected through the OSCFRQ Frequency Selection register, and fine-tuning can be done via the OSCTUNE register.

- 2. The **LFINTOSC** (Low-Frequency Internal Oscillator) is factory-calibrated and operates at 31 kHz.

### 7.2.2.1 HFINTOSC

The High-Frequency Internal Oscillator (HFINTOSC) is a precision digitally-controlled internal clock source that produces a stable clock up to 64 MHz. The HFINTOSC can be enabled through one of the following methods:

- Programming the RSTOSC<2:0> bits in Configuration Word 1 to '110' (Fosc = 1 MHz) or '000' (Fosc = 64 MHz) to set the oscillator upon device Power-up or Reset.

- Write to the NOSC<2:0> bits of the OSCCON1 register during run-time. See Section 7.3 "Clock Switching" for more information.

The HFINTOSC frequency can be selected by setting the FRQ<3:0> bits of the OSCFRQ register.

The NDIV<3:0> bits of the OSCCON1 register allow for division of the HFINTOSC output from a range between 1:1 and 1:512.

### 7.2.2.2 MFINTOSC

The module provides two (500 kHz and 31.25 kHz) constant clock outputs. These clocks are digital divisors of the HFINTOSC clock. Dynamic divider logic is used to provide constant MFINTOSC clock rates for all settings of HFINTOSC.

The MFINTOSC cannot be used to drive the system but it is used to clock certain modules such as the Timers and WWDT.

| U-0                                                     | U-0            | R/W-0/0                      | R/W-0/0 | U-0            | R/W-0/0          | R/W-0/0          | R/W-0/0      |

|---------------------------------------------------------|----------------|------------------------------|---------|----------------|------------------|------------------|--------------|

| —                                                       | —              | U2MD                         | U1MD    | —              | SPI1MD           | I2C2MD           | I2C1MD       |

| bit 7                                                   |                |                              |         |                |                  |                  | bit 0        |

|                                                         |                |                              |         |                |                  |                  |              |

| Legend:                                                 |                |                              |         |                |                  |                  |              |

| R = Reada                                               | ble bit        | W = Writable                 | bit     | U = Unimplen   | nented bit, read | as '0'           |              |

| u = Bit is u                                            | nchanged       | x = Bit is unkn              | iown    | -n/n = Value a | t POR and BOF    | R/Value at all o | other Resets |

| '1' = Bit is :                                          | set            | '0' = Bit is clea            | ared    | q = Value dep  | ends on conditi  | on               |              |

|                                                         |                |                              |         |                |                  |                  |              |

| bit 7-6                                                 | Unimpleme      | nted: Read as '0             | )'      |                |                  |                  |              |

| bit 5                                                   | U2MD: Disa     | ble UART2 bit                |         |                |                  |                  |              |

| 1 = UART2 module disabled                               |                |                              |         |                |                  |                  |              |

|                                                         | 0 = UART2      | module enabled               |         |                |                  |                  |              |

| bit 4                                                   |                | ble UART1 bit                |         |                |                  |                  |              |

|                                                         | -              | module disabled              |         |                |                  |                  |              |

| L:1 0                                                   |                | module enabled               |         |                |                  |                  |              |

| bit 3                                                   | -              | nted: Read as '0             |         |                |                  |                  |              |

| bit 2                                                   |                | sable SPI1 Modu              | ile bit |                |                  |                  |              |

|                                                         | -              | odule disabled               |         |                |                  |                  |              |

|                                                         |                | odule enabled                |         |                |                  |                  |              |

| bit 1                                                   |                | sable I <sup>2</sup> C2 Modu | le bit  |                |                  |                  |              |

| $1 = I^2C2$ module disabled<br>0 = I^2C2 module enabled |                |                              |         |                |                  |                  |              |

|                                                         |                |                              |         |                |                  |                  |              |

| bit 0                                                   | -              | sable I <sup>2</sup> C1 Modu | le bit  |                |                  |                  |              |

|                                                         |                | odule disabled               |         |                |                  |                  |              |

|                                                         | 0 = 1 - 0.1  m | odule enabled                |         |                |                  |                  |              |

### REGISTER 19-6: PMD5: PMD CONTROL REGISTER 5

### REGISTER 20-3: TMR0L: TIMER0 COUNT REGISTER

| R/W-0/0          | R/W-0/0 | R/W-0/0           | R/W-0/0 | R/W-0/0        | R/W-0/0          | R/W-0/0          | R/W-0/0     |

|------------------|---------|-------------------|---------|----------------|------------------|------------------|-------------|

|                  |         |                   | TMRC    | )L<7:0>        |                  |                  |             |

| bit 7            |         |                   |         |                |                  |                  | bit 0       |

|                  |         |                   |         |                |                  |                  |             |

| Legend:          |         |                   |         |                |                  |                  |             |

| R = Readable     | bit     | W = Writable      | bit     | U = Unimpler   | nented bit, read | l as '0'         |             |

| u = Bit is unch  | anged   | x = Bit is unkr   | nown    | -n/n = Value a | at POR and BO    | R/Value at all c | ther Resets |

| '1' = Bit is set |         | '0' = Bit is clea | ared    |                |                  |                  |             |

bit 7-0 TMR0L<7:0>: TMR0 Counter bits <7:0>

### REGISTER 20-4: TMR0H: TIMER0 PERIOD REGISTER

| R/W-1/1 |

|---------|---------|---------|---------|---------|---------|---------|---------|

|         |         |         | TMR0H   | 1<15:8> |         |         |         |

| bit 7   |         |         |         |         |         |         | bit 0   |

| Legend:              |                      |                                                       |

|----------------------|----------------------|-------------------------------------------------------|

| R = Readable bit     | W = Writable bit     | U = Unimplemented bit, read as '0'                    |

| u = Bit is unchanged | x = Bit is unknown   | -n/n = Value at POR and BOR/Value at all other Resets |

| '1' = Bit is set     | '0' = Bit is cleared |                                                       |

bit 7-0 When MD16 = 0 **PR0<7:0>:**TMR0 Period Register Bits <7:0> When MD16 = 1 **TMR0H<15:8>:** TMR0 Counter bits <15:8>

#### TABLE 20-1: SUMMARY OF REGISTERS ASSOCIATED WITH TIMER0

| Name   | Bit 7 | Bit 6      | Bit 5 | Bit 4       | Bit 3      | Bit 2 | Bit 1 | Bit 0 | Register<br>on Page |

|--------|-------|------------|-------|-------------|------------|-------|-------|-------|---------------------|

| T0CON0 | EN    | —          | OUT   | MD16        | OUTPS<3:0> |       |       |       | 301                 |

| T0CON1 |       | CS<2:0>    |       | ASYNC       | CKPS<3:0>  |       |       |       | 302                 |

| TMR0L  |       | TMR0L<7:0> |       |             |            |       |       |       | 303                 |

| TMR0H  |       |            |       | TMR0H<15:8> |            |       |       |       |                     |

**Legend:** — = unimplemented location, read as '0'. Shaded cells are not used by Timer0.

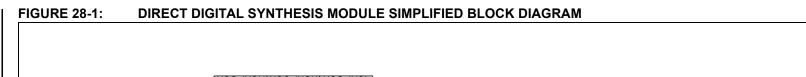

Note 1: The increment registers are double-buffered to allow for value changes to be made without first disabling the NCO module. The full increment value is loaded into the buffer registers on the second rising edge of the NCOx\_clk signal that occurs immediately after a write to NCOxINCL register. The buffers are not user-accessible and are shown here for reference.

### 31.12.3 XON/XOFF FLOW CONTROL

XON/XOFF flow control is selected by setting the FLO<1:0> bits to '01'.

XON/XOFF is a data based flow control method. The signals to suspend and resume transmission are special characters sent by the receiver to the transmitter The advantage is that additional hardware lines are not needed.

XON/XOFF flow control requires full duplex operation because the transmitter must be able to receive the signal to suspend transmitting while the transmission is in progress. Although XON and XOFF are not defined in the ASCII code, the generally accepted values are 13h for XOFF and 11h for XON. The UART uses those codes.

The transmitter defaults to XON, or transmitter enabled. This state is also indicated by the read-only XON bit in the UxFIFO register.

When an XOFF character is received, the transmitter stops transmitting after completing the character actively being transmitted. The transmitter remains disabled until an XON character is received.

XON will be forced on when software toggles the TXEN bit.

When the RUNOVF bit in the UxCON2 register is set then XON and XOFF characters continue to be received and processed without the need to clear the input FIFO by reading the UxRXB. However, if the RUNOVF bit is clear then the UxRXB must be read to avoid a receive overflow which will suspend flow control when the receive buffer overflows.

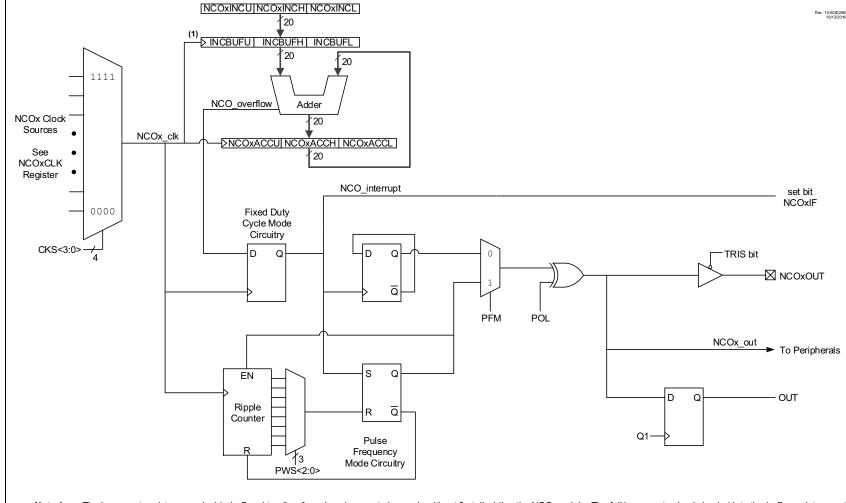

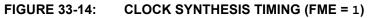

### 33.5.4.2 Clock Timing with FME = 1

One TSCL, consists of four clocks of the I<sup>2</sup>C clock input. The first clock is used to drive SCL low, the third releases SCL high, and the fourth is used to detect if the clock is, in fact, high or being stretched by a slave.

If a slave is clock stretching, the hardware waits; checking SCL on each successive  $l^2C$  clock, proceeding only after detecting SCL high. Figure 33-14 shows the clock synthesis timing when FME = 1.

### 36.5.2 PRECHARGE CONTROL

The precharge stage is an optional period of time that brings the external channel and internal sample and hold capacitor to known voltage levels. Precharge is enabled by writing a non-zero value to the ADPRE register. This stage is initiated when an ADC conversion begins, either from setting the GO bit, a special event trigger, or a conversion restart from the computation functionality. If the ADPRE register is cleared when an ADC conversion begins, this stage is skipped.

During the precharge time, CHOLD is disconnected from the outer portion of the sample path that leads to the external capacitive sensor and is connected to either VDD or VSS, depending on the value of the PPOL bit of ADCON1. At the same time, the port pin logic of the selected analog channel is overridden to drive a digital high or low out, in order to precharge the outer portion of the ADC's sample path, which includes the external sensor. The output polarity of this override is also determined by the PPOL bit of ADCON1. The amount of time that this charging receives is controlled by the ADPRE register.

- **Note 1:** The external charging overrides the TRIS setting of the respective I/O pin.

- **2:** If there is a device attached to this pin, Precharge should not be used.

### 36.5.3 ACQUISITION CONTROL

The Acquisition stage is an optional time for the voltage on the internal sample and hold capacitor to charge or discharge from the selected analog channel. This acquisition time is controlled by the ADACQ register. If PRE = 0, acquisition starts at the beginning of conversion. When PRE = 1, the acquisition stage begins when precharge ends.

At the start of the acquisition stage, the port pin logic of the selected analog channel is overridden to turn off the digital high/low output drivers so they do not affect the final result of the charge averaging. Also, the selected ADC channel is connected to CHOLD. This allows charge averaging to proceed between the precharged channel and the CHOLD capacitor.

Note: When PRE! = 0, acquisition time cannot be '0'. In this case, setting ADACQ to '0' will set a maximum acquisition time (8191 ADC clock cycles). When precharge is disabled, setting ADACQ to '0' will disable hardware acquisition time control.

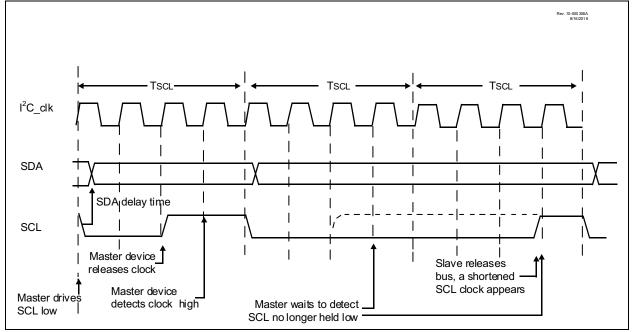

### 36.5.4 GUARD RING OUTPUTS

Figure 36-8 shows a typical guard ring circuit. CGUARD represents the capacitance of the guard ring trace placed on the PCB board. The user selects values for RA and RB that will create a voltage profile on CGUARD, which will match the selected acquisition channel.

The purpose of the guard ring is to generate a signal in phase with the CVD sensing signal to minimize the effects of the parasitic capacitance on sensing electrodes. It also can be used as a mutual drive for mutual capacitive sensing. For more information about active guard and mutual drive, see Application Note AN1478, "*mTouch*<sup>TM</sup> Sensing Solution Acquisition Methods Capacitive Voltage Divider" (DS01478).

The ADC has two guard ring drive outputs, ADGRDA and ADGRDB. These outputs can be routed through PPS controls to I/O pins (see Section **17.0 "Peripheral Pin Select (PPS) Module**" for details) and the polarity of these outputs are controlled by the ADGPOL and ADIPEN bits of ADCON1.

At the start of the first precharge stage, both outputs are set to match the ADGPOL bit of ADCON1. Once the acquisition stage begins, ADGRDA changes polarity, while ADGRDB remains unchanged. When performing a double sample conversion, setting the ADIPEN bit of ADCON1 causes both guard ring outputs to transition to the opposite polarity of ADGPOL at the start of the second precharge stage, and ADGRDA toggles again for the second acquisition. For more information on the timing of the guard ring output, refer to Figure 36-8 and Figure 36-9.

| BCF                                  | Bit Clear f                                                                                                                                                                                                                                                                                                                                                                                      | BN                                                                                       | Branch if Negative                                                                                                                                                                                                                                                                                    |

|--------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Syntax:                              | BCF f, b {,a}                                                                                                                                                                                                                                                                                                                                                                                    | Syntax:                                                                                  | BN n                                                                                                                                                                                                                                                                                                  |

| Operands:                            | $0 \leq f \leq 255$                                                                                                                                                                                                                                                                                                                                                                              | Operands:                                                                                | $-128 \le n \le 127$                                                                                                                                                                                                                                                                                  |

|                                      | $\begin{array}{l} 0 \leq b \leq 7 \\ a \in [0,1] \end{array}$                                                                                                                                                                                                                                                                                                                                    | Operation:                                                                               | if NEGATIVE bit is '1' (PC) + 2 + 2n $\rightarrow$ PC                                                                                                                                                                                                                                                 |

| Operation:                           | $0 \rightarrow f \le b >$                                                                                                                                                                                                                                                                                                                                                                        | Status Affected:                                                                         | None                                                                                                                                                                                                                                                                                                  |

| Status Affected:                     | None                                                                                                                                                                                                                                                                                                                                                                                             | Encoding:                                                                                | 1110 0110 nnnn nnnn                                                                                                                                                                                                                                                                                   |

| Encoding:<br>Description:            | 1001bbbaffffffffBit 'b' in register 'f' is cleared.If 'a' is '0', the Access Bank is selected.If 'a' is '1', the BSR is used to select theGPR bank.If 'a' is '0' and the extended instructionset is enabled, this instruction operatesin Indexed Literal Offset Addressingmode whenever $f \le 95$ (5Fh). See Section 41.2.3 "Byte-Oriented and Bit-Oriented Instructions in Indexed Literations | Description:<br>Words:<br>Cycles:                                                        | If the NEGATIVE bit is '1', then the<br>program will branch.<br>The 2's complement number '2n' is<br>added to the PC. Since the PC will have<br>incremented to fetch the next<br>instruction, the new address will be<br>PC + 2 + 2n. This instruction is then a<br>2-cycle instruction.<br>1<br>1(2) |

| Words:                               | eral Offset Mode" for details.                                                                                                                                                                                                                                                                                                                                                                   | Q Cycle Activity:<br>If Jump:                                                            |                                                                                                                                                                                                                                                                                                       |

| Cycles:                              | 1                                                                                                                                                                                                                                                                                                                                                                                                | Q1                                                                                       | Q2 Q3 Q4                                                                                                                                                                                                                                                                                              |

| Q Cycle Activity:                    |                                                                                                                                                                                                                                                                                                                                                                                                  | Decode                                                                                   | Read literalProcessWrite to PC'n'Data                                                                                                                                                                                                                                                                 |

| Q1<br>Decode                         | Q2 Q3 Q4<br>Read Process Write                                                                                                                                                                                                                                                                                                                                                                   | No<br>operation                                                                          | No No No<br>operation operation                                                                                                                                                                                                                                                                       |

|                                      | register 'f' Data register 'f'                                                                                                                                                                                                                                                                                                                                                                   | If No Jump:                                                                              |                                                                                                                                                                                                                                                                                                       |

| Fuemples                             |                                                                                                                                                                                                                                                                                                                                                                                                  | Q1                                                                                       | Q2 Q3 Q4                                                                                                                                                                                                                                                                                              |

| Example:<br>Before Instruc<br>FLAG_R |                                                                                                                                                                                                                                                                                                                                                                                                  | Decode                                                                                   | Read literalProcessNo'n'Dataoperation                                                                                                                                                                                                                                                                 |

| After Instruction<br>FLAG_R          | on                                                                                                                                                                                                                                                                                                                                                                                               | Example:<br>Before Instruc<br>PC<br>After Instructio<br>If NEGAT<br>PC<br>If NEGAT<br>PC | = address (HERE)<br>on<br>TIVE = 1;<br>= address (Jump)                                                                                                                                                                                                                                               |

|                                   |                                                                           |                                                                                         | w                                                    | BNZ                          | Branch if                                                               |                                                                                      |                                        |

|-----------------------------------|---------------------------------------------------------------------------|-----------------------------------------------------------------------------------------|------------------------------------------------------|------------------------------|-------------------------------------------------------------------------|--------------------------------------------------------------------------------------|----------------------------------------|

| Syntax:                           | BNOV n                                                                    |                                                                                         |                                                      | Syntax:                      | BNZ n                                                                   | BNZ n                                                                                |                                        |

| Operands:                         | -128 ≤ n ≤ 1                                                              | 27                                                                                      |                                                      | Operands:                    | -128 ≤ n ≤                                                              | 127                                                                                  |                                        |

| Operation:                        |                                                                           | if OVERFLOW bit is '0'<br>(PC) + 2 + 2n $\rightarrow$ PC                                |                                                      | Operation:                   |                                                                         | if ZERO bit is '0'<br>(PC) + 2 + 2n $\rightarrow$ PC                                 |                                        |

| Status Affected:                  | None                                                                      |                                                                                         |                                                      | Status Affected:             | None                                                                    |                                                                                      |                                        |

| Encoding:                         | 1110                                                                      | 0101 nni                                                                                | nn nnnn                                              | Encoding:                    | 1110                                                                    | 0001 nn                                                                              | nn nnnn                                |

| Description:                      | program wil<br>The 2's com<br>added to the<br>incremented<br>instruction, | nplement num<br>e PC. Since th<br>d to fetch the r<br>the new addre<br>n. This instruct | ber '2n' is<br>e PC will have<br>next<br>ess will be | Description:                 | will branch<br>The 2's cor<br>added to th<br>incremente<br>instruction, | nplement num<br>e PC. Since the<br>d to fetch the<br>the new addr<br>n. This instruc | ne PC will have<br>next<br>ess will be |

| Words:                            | 1                                                                         |                                                                                         |                                                      | Words:                       | 1                                                                       |                                                                                      |                                        |

| Cycles:                           | 1(2)                                                                      |                                                                                         |                                                      | Cycles:                      | 1(2)                                                                    |                                                                                      |                                        |

| Q Cycle Activity:<br>If Jump:     |                                                                           |                                                                                         |                                                      | Q Cycle Activity<br>If Jump: | :                                                                       |                                                                                      |                                        |

| Q1                                | Q2                                                                        | Q3                                                                                      | Q4                                                   | Q1                           | Q2                                                                      | Q3                                                                                   | Q4                                     |

| Decode                            | Read literal<br>'n'                                                       | Process<br>Data                                                                         | Write to PC                                          | Decode                       | Read literal<br>'n'                                                     | Process<br>Data                                                                      | Write to PC                            |

| No                                | No                                                                        | No                                                                                      | No                                                   | No                           | No                                                                      | No                                                                                   | No                                     |

| operation                         | operation                                                                 | operation                                                                               | operation                                            | operation                    | operation                                                               | operation                                                                            | operation                              |

| If No Jump:                       | 00                                                                        | 00                                                                                      | 04                                                   | If No Jump:                  | 00                                                                      | 00                                                                                   | 04                                     |

| Q1<br>Decode                      | Q2<br>Read literal                                                        | Q3<br>Process                                                                           | Q4<br>No                                             | Q1<br>Decode                 | Q2<br>Read literal                                                      | Q3<br>Process                                                                        | Q4<br>No                               |

| Decode                            | 'n'                                                                       | Data                                                                                    | operation                                            | Decode                       | 'n'                                                                     | Data                                                                                 | operation                              |

| <u>Example</u> :<br>Before Instru |                                                                           | BNOV Jump                                                                               | <u> </u>                                             | Example:<br>Before Instr     |                                                                         | BNZ Jump                                                                             |                                        |

| PC<br>After Instruct              |                                                                           | dress (HERE)                                                                            | )                                                    | PC<br>After Instruc          |                                                                         | Idress (HERE)                                                                        |                                        |

|                                   | RFLOW = 0;                                                                | dress (Jump)                                                                            |                                                      | If ZER<br>P                  | O = 0;                                                                  | ldress (Jump)                                                                        |                                        |

W

| INFS                                   | NZ                | Incremen                     | t f, skip if no                           | ot 0            |  |  |  |  |

|----------------------------------------|-------------------|------------------------------|-------------------------------------------|-----------------|--|--|--|--|

| Synta                                  | x:                | INFSNZ f                     | {,d {,a}}                                 |                 |  |  |  |  |

| Opera                                  | ands:             | $0 \leq f \leq 255$          |                                           |                 |  |  |  |  |

|                                        |                   | d ∈ [0,1]<br>a ∈ [0,1]       | d ∈ [0,1]<br>a ∈ [0,1]                    |                 |  |  |  |  |

| Opera                                  | ation.            | $(f) + 1 \rightarrow de$     | et                                        |                 |  |  |  |  |

| Opere                                  |                   | skip if result               |                                           |                 |  |  |  |  |

| Status                                 | Affected:         | None                         | None                                      |                 |  |  |  |  |

| Encod                                  | ding:             | 0100                         | 0100 10da ffff ffff                       |                 |  |  |  |  |

| Descr                                  | iption:           | The content                  | ts of register 'f                         | ' are           |  |  |  |  |

|                                        |                   |                              | <b>d. If 'd' is '</b> 0', th              |                 |  |  |  |  |