#### Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

### Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Product Status             | Active                                                                    |

|----------------------------|---------------------------------------------------------------------------|

| Core Processor             | PIC                                                                       |

| Core Size                  | 8-Bit                                                                     |

| Speed                      | 64MHz                                                                     |

| Connectivity               | I <sup>2</sup> C, LINbus, SPI, UART/USART                                 |

| Peripherals                | Brown-out Detect/Reset, DMA, HLVD, POR, PWM, WDT                          |

| Number of I/O              | 36                                                                        |

| Program Memory Size        | 32KB (16K x 16)                                                           |

| Program Memory Type        | FLASH                                                                     |

| EEPROM Size                | 256 x 8                                                                   |

| RAM Size                   | 2K x 8                                                                    |

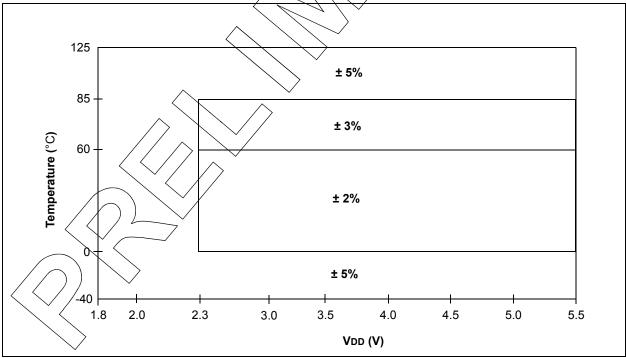

| Voltage - Supply (Vcc/Vdd) | 2.3V ~ 5.5V                                                               |

| Data Converters            | A/D 35x12b; D/A 1x5b                                                      |

| Oscillator Type            | Internal                                                                  |

| Operating Temperature      | -40°C ~ 125°C (TA)                                                        |

| Mounting Type              | Through Hole                                                              |

| Package / Case             | 40-DIP (0.600", 15.24mm)                                                  |

| Supplier Device Package    | 40-PDIP                                                                   |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/pic18f45k42-e-p |

|                            |                                                                           |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

# TO OUR VALUED CUSTOMERS

It is our intention to provide our valued customers with the best documentation possible to ensure successful use of your Microchip products. To this end, we will continue to improve our publications to better suit your needs. Our publications will be refined and enhanced as new volumes and updates are introduced.

If you have any questions or comments regarding this publication, please contact the Marketing Communications Department via E-mail at docerrors@microchip.com. We welcome your feedback.

# Most Current Data Sheet

To obtain the most up-to-date version of this data sheet, please register at our Worldwide Website at:

#### http://www.microchip.com

You can determine the version of a data sheet by examining its literature number found on the bottom outside corner of any page. The last character of the literature number is the version number, (e.g., DS3000000A is version A of document DS30000000).

### Errata

An errata sheet, describing minor operational differences from the data sheet and recommended workarounds, may exist for current devices. As device/documentation issues become known to us, we will publish an errata sheet. The errata will specify the revision of silicon and revision of document to which it applies.

To determine if an errata sheet exists for a particular device, please check with one of the following:

- Microchip's Worldwide Website; http://www.microchip.com

- Your local Microchip sales office (see last page)

When contacting a sales office, please specify which device, revision of silicon and data sheet (include literature number) you are using.

# **Customer Notification System**

Register on our website at www.microchip.com to receive the most current information on all of our products.

# 4.4.2 INSTRUCTIONS IN PROGRAM MEMORY

The program memory is addressed in bytes. Instructions are stored as either two bytes or four bytes in program memory. The Least Significant Byte of an instruction word is always stored in a program memory location with an even address (LSb = 0). To maintain alignment with instruction boundaries, the PC increments in steps of two and the LSb will always read '0' (see Section 4.2.4 "Program Counter").

Figure 4-2 shows an example of how instruction words are stored in the program memory.

The CALL and GOTO instructions have the absolute program memory address embedded into the instruction. Since instructions are always stored on word boundaries, the data contained in the instruction is a word address. The word address is written to PC<20:1>, which accesses the desired byte address in program memory. Instruction #2 in Figure 4-2 shows how the instruction GOTO 0006h is encoded in the program memory. Program branch instructions, which encode a relative address offset, operate in the same manner. The offset value stored in a branch instruction represents the number of single-word instructions that the PC will be offset by. Section 41.0 "Instruction Set Summary" provides further details of the instruction set.

# 4.4.3 MULTI-WORD INSTRUCTIONS

The standard PIC18 instruction set has four two-word instructions: CALL, MOVFF, GOTO and LFSR and two three-word instructions: MOVFFL and MOVSFL. In all cases, the second and the third word of the instruction always has '1111' as its four Most Significant bits; the other 12 bits are literal data, usually a data memory address.

The use of '1111' in the four MSbs of an instruction specifies a special form of NOP. If the instruction is executed in proper sequence – immediately after the first word – the data in the second word is accessed and used by the instruction sequence. If the first word is skipped for some reason and the second or third word is executed by itself, a NOP is executed instead. This is necessary for cases when the multi-word instruction is preceded by a conditional instruction that changes the PC. Example 4-4 shows how this works.

# FIGURE 4-2: INSTRUCTIONS IN PROGRAM MEMORY

|                |             |                   | <b>LSB =</b> 1 | LSB = 0 | Word Address $\downarrow$ |

|----------------|-------------|-------------------|----------------|---------|---------------------------|

|                | Program M   | emory             |                |         | 000000h                   |

|                | Byte Locati | ons $\rightarrow$ |                |         | 000002h                   |

|                |             |                   |                |         | 000004h                   |

|                |             |                   |                |         | 000006h                   |

| Instruction 1: | MOVLW       | 055h              | 0Fh            | 55h     | 000008h                   |

| Instruction 2: | GOTO        | 0006h             | EFh            | 03h     | 00000Ah                   |

|                |             |                   | F0h            | 00h     | 00000Ch                   |

| Instruction 3: | MOVFF       | 123h, 456h        | C1h            | 23h     | 00000Eh                   |

|                |             |                   | F4h            | 56h     | 000010h                   |

| Instruction 4: | MOVFFL      | 123h, 456h        | 00h            | 60h     | 000012h                   |

|                |             |                   | F4h            | 8Ch     | 000014h                   |

|                |             |                   | F4h            | 56h     | 000016h                   |

|                |             |                   |                |         | 000018h                   |

|                |             |                   |                |         | 00001Ah                   |

# 6.11.1 MEMORY EXECUTION VIOLATION

If the CPU executes outside the valid execution area, a memory execution violation reset occurs.

The invalid execution areas are:

- 1. Addresses outside implemented program memory (see Table 5-1).

- 2. Storage Area Flash (SAF) inside program memory, if it is enabled.

When a memory execution violation is generated, flag MEMV is cleared in PCON1 (Register 6-3) to signal the cause of Reset. It needs to be set in the user code after a memory execution violation Reset has occurred to detect further violation Resets.

# 6.12 Determining the Cause of a Reset

Upon any Reset, multiple bits in the STATUS and PCON0 registers are updated to indicate the cause of the Reset. Table 6-3 shows the Reset conditions of these registers.

| Condition                          | Program<br>Counter | STATUS<br>Register <sup>(1,2)</sup> | PCON0<br>Register | PCON1<br>Register |

|------------------------------------|--------------------|-------------------------------------|-------------------|-------------------|

| Power-on Reset                     | 0                  | -110 0000                           | 0011 110x         | 1-                |

| Brown-out Reset                    | 0                  | -110 0000                           | 0011 11u0         | 1-                |

| MCLR Reset during normal operation | 0                  | -uuu uuuu                           | uuuu Ouuu         | u-                |

| MCLR Reset during Sleep            | 0                  | -10u uuuu                           | uuuu Ouuu         | u-                |

| WWDT Time-out Reset                | 0                  | -0uu uuuu                           | uuu0 uuuu         | u-                |

| WWDT Window Violation Reset        | 0                  | -uuu uuuu                           | uu0u uuuu         | u-                |

| RESET Instruction Executed         | 0                  | -uuu uuuu                           | uuuu u0uu         | u-                |

| Stack Overflow Reset (STVREN = 1)  | 0                  | -uuu uuuu                           | luuu uuuu         | u-                |

| Stack Underflow Reset (STVREN = 1) | 0                  | -uuu uuuu                           | uluu uuuu         | u-                |

| Memory Violation Reset             | 0                  | -uuu uuuu                           | uuuu uuuu         | 0-                |

TABLE 6-3: RESET CONDITION FOR SPECIAL REGISTERS

**Legend:** u = unchanged, x = unknown, - = unimplemented bit, reads as '0'.

**Note 1:** If a Status bit is not implemented, that bit will be read as '0'.

2: Status bits Z, C, DC are reset by POR/BOR, but not defined by the Resets module (Register 4-2).

| R/W-1/1         | R/W-1/1                      | R/W-1/1             | R/W-1/1          | R/W-1/1        | R/W-1/1          | R/W-1/1          | R/W-1/1     |

|-----------------|------------------------------|---------------------|------------------|----------------|------------------|------------------|-------------|

| IOCIP           | CRCIP                        | SCANIP              | NVMIP            | CSWIP          | OSFIP            | HLVDIP           | SWIP        |

| bit 7           |                              |                     |                  |                |                  |                  | bit         |

|                 |                              |                     |                  |                |                  |                  |             |

| Legend:         |                              |                     |                  |                |                  | (0)              |             |

| R = Readable    |                              | W = Writable        |                  | •              | mented bit, read |                  |             |

| u = Bit is unc  | •                            | x = Bit is unk      |                  | -n/n = value a | at POR and BO    | R/value at all c | iner Resets |

| '1' = Bit is se | t                            | '0' = Bit is cle    | ared             |                |                  |                  |             |

| bit 7           | IOCIP: Inter                 | rupt-on-Change      | Priority bit     |                |                  |                  |             |

|                 | 1 = High pri                 |                     | 2                |                |                  |                  |             |

|                 | 0 = Low price                | ority               |                  |                |                  |                  |             |

| bit 6           | CRCIP: CR                    | C Interrupt Prior   | ity bit          |                |                  |                  |             |

|                 | 1 = High pri                 |                     |                  |                |                  |                  |             |

|                 | 0 = Low price                | •                   |                  |                |                  |                  |             |

| bit 5           |                              | emory Scanner       | Interrupt Prior  | ity bit        |                  |                  |             |

|                 | 1 = High pri<br>0 = Low prie |                     |                  |                |                  |                  |             |

| bit 4           | -                            | M Interrupt Prior   | ity hit          |                |                  |                  |             |

|                 | 1 = High pri                 | -                   |                  |                |                  |                  |             |

|                 | 0 = Low price                | •                   |                  |                |                  |                  |             |

| bit 3           | CSWIP: Clo                   | ck Switch Interr    | upt Priority bit |                |                  |                  |             |

|                 | 1 = High pri                 | ,                   |                  |                |                  |                  |             |

|                 | 0 = Low price                | ority               |                  |                |                  |                  |             |

| bit 2           |                              | illator Fail Interr | upt Priority bit | :              |                  |                  |             |

|                 | 1 = High pri                 |                     |                  |                |                  |                  |             |

| L:1 4           | 0 = Low price                | •                   | a with a latit   |                |                  |                  |             |

| bit 1           | 1 = High pri                 | VD Interrupt Pri    | ority dit        |                |                  |                  |             |

|                 | 1 = High phi0 = Low price    |                     |                  |                |                  |                  |             |

| bit 0           | -                            | vare Interrupt Pr   | iority bit       |                |                  |                  |             |

|                 | 1 = High pri                 |                     | <b>,</b> -       |                |                  |                  |             |

|                 | 0 = Low price                | -                   |                  |                |                  |                  |             |

# REGISTER 9-25: IPR0: PERIPHERAL INTERRUPT PRIORITY REGISTER 0

# 15.10 Reset

The DMA registers are set to the default state on any Reset. The registers are also reset to the default state when the enable bit is cleared (DMA1CON1bits.EN=0).

# 15.11 Power Saving Mode Operation

The DMA utilizes system clocks and it is treated as a peripheral when it comes to power saving operations. Like other peripherals, the DMA also uses Peripheral Module Disable bits to further tailor its operation in low-power states.

# 15.11.1 SLEEP MODE

When the device enters Sleep mode, the system clock to the module is shut down, therefore no DMA operation is supported in Sleep. Once the system clock is disabled, the requisite read and write clocks are also disabled, without which the DMA cannot perform any of its tasks.

Any transfers that may be in progress are resumed on exiting from Sleep mode. Register contents are not affected by the device entering or leaving Sleep mode. It is recommended that DMA transactions be allowed to finish before entering Sleep mode.

# 15.11.2 IDLE MODE

In IDLE mode, all of the system clocks (including the read and write clocks) are still operating but the CPU is not using them to save power.

Therefore, every instruction cycle is available to the system arbiter and if the bubble is granted to the DMA, it may be utilized to move data.

### 15.11.3 DOZE MODE

Similar to the Idle mode, the CPU does not utilize all of the available instruction cycles slots that are available to it in order to save power. It only executes instructions based on its settings from the Doze settings.

Therefore, every instruction not used by the CPU is available for system arbitration and may be utilized by the DMA if granted by the arbiter.

### 15.11.4 PERIPHERAL MODULE DISABLE

The Peripheral Module Disable (PMD) registers provide a method to disable DMA by gating all clock sources supplied to it. The respective DMAxMD bit needs to be set in order to disable the DMA.

# 15.12 DMA Register Interfaces

The DMA can transfer data to any GPR or SFR location. For better user accessibility, some of the more commonly used SFR spaces have their Mirror registers placed in Bank 64 (0x4000-0x40FF). These Mirror registers can be only accessed through the DMA Source and Destination Address registers. Refer to Table 4-3 for details about Bank 64 Registers.

| U-0            | U-0                                                                           | R/W-0/0                      | R/W-0/0 | U-0            | R/W-0/0          | R/W-0/0          | R/W-0/0      |

|----------------|-------------------------------------------------------------------------------|------------------------------|---------|----------------|------------------|------------------|--------------|

| —              | —                                                                             | U2MD                         | U1MD    | —              | SPI1MD           | I2C2MD           | I2C1MD       |

| bit 7          |                                                                               |                              |         |                |                  |                  | bit 0        |

|                |                                                                               |                              |         |                |                  |                  |              |

| Legend:        |                                                                               |                              |         |                |                  |                  |              |

| R = Reada      | ble bit                                                                       | W = Writable                 | bit     | U = Unimplen   | nented bit, read | as '0'           |              |

| u = Bit is u   | nchanged                                                                      | x = Bit is unkn              | iown    | -n/n = Value a | t POR and BOF    | R/Value at all o | other Resets |

| '1' = Bit is : | set                                                                           | '0' = Bit is clea            | ared    | q = Value dep  | ends on conditi  | on               |              |

|                |                                                                               |                              |         |                |                  |                  |              |

| bit 7-6        | Unimpleme                                                                     | nted: Read as '0             | )'      |                |                  |                  |              |

| bit 5          | U2MD: Disa                                                                    | ble UART2 bit                |         |                |                  |                  |              |

|                |                                                                               | module disabled              |         |                |                  |                  |              |

|                | 0 = UART2                                                                     | module enabled               |         |                |                  |                  |              |

| bit 4          |                                                                               | ble UART1 bit                |         |                |                  |                  |              |

|                | -                                                                             | module disabled              |         |                |                  |                  |              |

| L:1 0          |                                                                               | module enabled               |         |                |                  |                  |              |

| bit 3          | -                                                                             | nted: Read as '0             |         |                |                  |                  |              |

| bit 2          |                                                                               | sable SPI1 Modu              | ile bit |                |                  |                  |              |

|                | -                                                                             | odule disabled               |         |                |                  |                  |              |

|                | 0 = SPI1 module enabled<br>I2C2MD: Disable I <sup>2</sup> C2 Module bit       |                              |         |                |                  |                  |              |

| bit 1          |                                                                               |                              |         |                |                  |                  |              |

|                | $1 = I^{2}C2 \text{ module disabled}$<br>$0 = I^{2}C2 \text{ module enabled}$ |                              |         |                |                  |                  |              |

|                |                                                                               |                              |         |                |                  |                  |              |

| bit 0          | -                                                                             | sable I <sup>2</sup> C1 Modu | le bit  |                |                  |                  |              |

|                |                                                                               | odule disabled               |         |                |                  |                  |              |

|                | 0 = 1 - 0.1  m                                                                | odule enabled                |         |                |                  |                  |              |

# REGISTER 19-6: PMD5: PMD CONTROL REGISTER 5

# 22.5.10 LEVEL-TRIGGERED HARDWARE LIMIT ONE-SHOT MODES

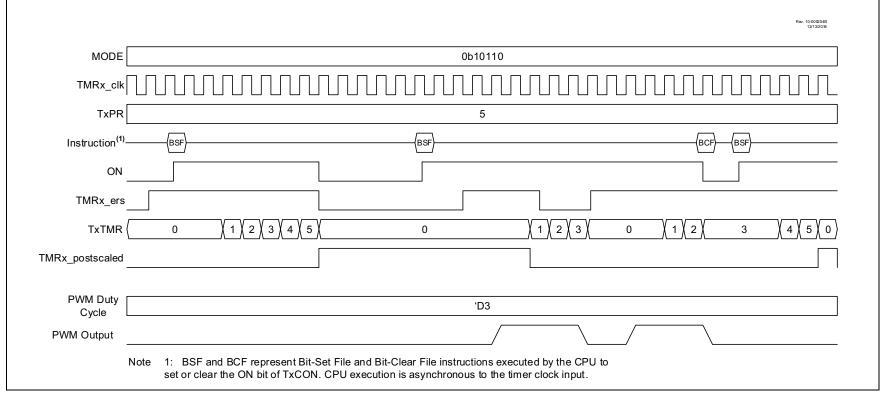

The Level Triggered Hardware Limit One-Shot modes hold the timer in Reset on an external Reset level and start counting when both the ON bit is set and the external signal is not at the Reset level. If one of either the external signal is not in reset or the ON bit is set then the other signal being set/made active will start the timer. Reset levels are selected as follows:

- Low reset level (MODE<4:0> = 10110)

- High reset level (MODE<4:0> = 10111)

When the timer count matches the T2PR period count, the timer is reset and the ON bit is cleared. When the ON bit is cleared by either a T2PR match or by software control, the timer will stay in Reset until both the ON bit is set and the external signal is not at the Reset level.

When Level Triggered Hardware Limit One-Shot modes are used in conjunction with the CCP PWM operation, the PWM drive goes active with either the external signal edge or the setting of the ON bit, whichever of the two starts the timer.

PIC18(L)F26/27/45/46/47/55/56/57K42

# FIGURE 22-13: LEVEL-TRIGGERED HARDWARE LIMIT ONE-SHOT MODE TIMING DIAGRAM (MODE = 10110)

# 22.7 Register Definitions: Timer2/4/6 Control

Long bit name prefixes for the Timer2/4/6 peripherals are shown in Table 22-2. Refer to **Section 1.3.2.2 "Long Bit Names"** for more information.

# TABLE 22-2: OPERATING MODES

| Peripheral | Bit Name Prefix |

|------------|-----------------|

| Timer2     | T2              |

| Timer4     | T4              |

| Timer6     | Т6              |

# REGISTER 22-1: TxCLK: TIMERx CLOCK SELECTION REGISTER

| U-0   | U-0 | U-0 | U-0 | R/W-0/0 | R/W-0/0 | R/W-0/0 | R/W-0/0 |

|-------|-----|-----|-----|---------|---------|---------|---------|

| —     | —   | —   | —   |         | CS<     | 3:0>    |         |

| bit 7 |     |     |     |         |         |         | bit 0   |

# Legend:

| •                    |                      |                                                       |

|----------------------|----------------------|-------------------------------------------------------|

| R = Readable bit     | W = Writable bit     | U = Unimplemented bit, read as '0'                    |

| u = Bit is unchanged | x = Bit is unknown   | -n/n = Value at POR and BOR/Value at all other Resets |

| '1' = Bit is set     | '0' = Bit is cleared |                                                       |

#### bit 7-4 Unimplemented: Read as '0'

#### bit 3-0 CS<3:0>: Timerx Clock Selection bits

| 00 (0.0) | T2TMR                   | TMR4                    | TMR6                    |

|----------|-------------------------|-------------------------|-------------------------|

| CS<3:0>  | Clock Source            | Clock Source            | Clock Source            |

| 1111     | Reserved                | Reserved                | Reserved                |

| 1110     | CLC4_out                | CLC4_out                | CLC4_out                |

| 1101     | CLC3_out                | CLC3_out                | CLC3_out                |

| 1100     | CLC2_out                | CLC2_out                | CLC2_out                |

| 1011     | CLC1_out                | CLC1_out                | CLC1_out                |

| 1010     | ZCD_OUT                 | ZCD_OUT                 | ZCD_OUT                 |

| 1001     | NCO10UT                 | NCO10UT                 | NCO10UT                 |

| 1000     | CLKREF_OUT              | CLKREF_OUT              | CLKREF_OUT              |

| 0111     | SOSC                    | SOSC                    | SOSC                    |

| 0110     | MFINTOSC (32 kHz)       | MFINTOSC (32 kHz)       | MFINTOSC (32 kHz)       |

| 0101     | MFINTOSC (500 kHz)      | MFINTOSC (500 kHz)      | MFINTOSC (500 kHz)      |

| 0100     | LFINTOSC                | LFINTOSC                | LFINTOSC                |

| 0011     | HFINTOSC                | HFINTOSC                | HFINTOSC                |

| 0010     | Fosc                    | Fosc                    | Fosc                    |

| 0001     | Fosc/4                  | Fosc/4                  | Fosc/4                  |

| 0000     | Pin selected by T2INPPS | Pin selected by T4INPPS | Pin selected by T6INPPS |

# 23.2.3 SOFTWARE INTERRUPT MODE

When the Capture mode is changed, a false capture interrupt may be generated. The user should keep the CCPxIE Interrupt Priority bit of the respective PIE register clear to avoid false interrupts. Additionally, the user should clear the CCPxIF interrupt flag bit of the respective PIR register following any change in Operating mode.

# 23.2.4 CAPTURE DURING SLEEP

Capture mode depends upon the Timer1 module for proper operation. There are two options for driving the Timer1 module in Capture mode. It can be driven by the instruction clock (FOSC/4), or by an external clock source.

When Timer1 is clocked by FOSC/4, Timer1 will not increment during Sleep. When the device wakes from Sleep, Timer1 will continue from its previous state.

Capture mode will operate during Sleep as long as the clock source for Timer1 is active in Sleep.

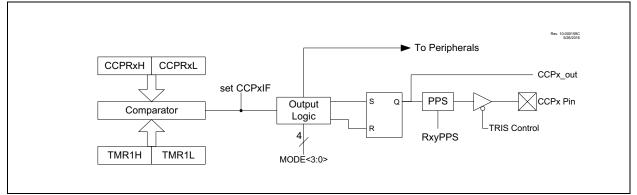

# 23.3 Compare Mode

Compare mode makes use of the 16-bit Timer1 resource. The 16-bit value of the CCPRxH:CCPRxL register pair is constantly compared against the 16-bit value of the TMRxH:TMRxL register pair. When a match occurs, one of the following events can occur:

- Toggle the CCPx output, clear TMRx

- Toggle the CCPx output

- Set the CCPx output

- · Clear the CCPx output

- · Pulse output

- Pulse output, clear TMRx

The action on the pin is based on the value of the MODE<3:0> control bits of the CCPxCON register. At the same time, the interrupt flag CCPxIF bit is set, and an ADC conversion can be triggered, if selected.

All Compare modes can generate an interrupt and trigger an ADC conversion. When MODE = 0b0001 or 0b1011, the CCP resets the TMR register pair.

Figure 23-2 shows a simplified diagram of the compare operation.

# FIGURE 23-2: COMPARE MODE OPERATION BLOCK DIAGRAM

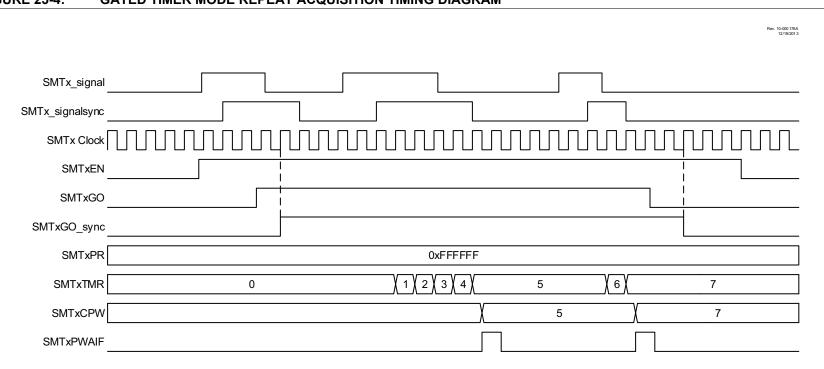

#### 25.6.6 GATED WINDOWED MEASURE MODE

This mode measures the duty cycle of the SMT1\_signal input over a known input window. It does so by incrementing the timer on each pulse of the clock signal while the SMT1\_signal input is high, updating the SMT1CPR register and resetting the timer on every rising edge of the SMTWINx input after the first. See Figure 25-12 and Figure 25-13.

| Name     | Bit 7    | Bit 6 | Bit 5    | Bit 4    | Bit 3 | Bit 2    | Bit 1     | Bit 0 | Register<br>on Page |

|----------|----------|-------|----------|----------|-------|----------|-----------|-------|---------------------|

| CWGxCON0 | EN       | LD    |          |          |       |          | MODE<2:0> | ,     | 424                 |

| CWGxCON1 | _        |       | IN       | _        | POLD  | POLC     | POLB      | POLA  | 425                 |

| CWGxCLK  |          | _     | _        | _        | _     | —        | _         | CS    | 426                 |

| CWGxISM  | —        |       | _        |          |       | ISM<4:0> |           |       | 427                 |

| CWGxSTR  | OVRD     | OVRC  | OVRB     | OVRA     | STRD  | STRC     | STRB      | STRA  | 428                 |

| CWGxAS0  | SHUTDOWN | REN   | LSBD     | <1:0>    | LSAC  | <1:0>    |           | —     | 429                 |

| CWGxAS1  | —        | AS6E  | AS5E     | AS4E     | AS3E  | AS2E     | AS1E      | AS0E  | 430                 |

| CWGxDBR  |          | _     | DBR<5:0> |          |       | 431      |           |       |                     |

| CWGxDBF  |          |       |          | DBF<5:0> |       |          |           |       | 431                 |

# TABLE 26-2: SUMMARY OF REGISTERS ASSOCIATED WITH CWG

**Legend:** – = unimplemented locations read as '0'. Shaded cells are not used by CWG.

### REGISTER 27-3: CLCxSEL0: GENERIC CLCx DATA 0 SELECT REGISTER

| U-0   | U-0 | R/W-x/u | R/W-x/u | R/W-x/u | R/W-x/u | R/W-x/u | R/W-x/u |

|-------|-----|---------|---------|---------|---------|---------|---------|

| —     | —   |         |         | D1S     | 8<5:0>  |         |         |

| bit 7 |     |         |         |         |         |         | bit 0   |

|       |     |         |         |         |         |         |         |

| Legend:              |                      |                                                       |

|----------------------|----------------------|-------------------------------------------------------|

| R = Readable bit     | W = Writable bit     | U = Unimplemented bit, read as '0'                    |

| u = Bit is unchanged | x = Bit is unknown   | -n/n = Value at POR and BOR/Value at all other Resets |

| '1' = Bit is set     | '0' = Bit is cleared |                                                       |

#### bit 7-6 Unimplemented: Read as '0'

bit 5-0 D1S<5:0>: CLCx Data1 Input Selection bits See Table 27-1.

#### REGISTER 27-4: CLCxSEL1: GENERIC CLCx DATA 1 SELECT REGISTER

| U-0   | U-0 | R/W-x/u | R/W-x/u  | R/W-x/u | R/W-x/u | R/W-x/u | R/W-x/u |  |

|-------|-----|---------|----------|---------|---------|---------|---------|--|

| —     | -   |         | D2S<5:0> |         |         |         |         |  |

| bit 7 |     |         |          |         |         |         | bit 0   |  |

|       |     |         |          |         |         |         |         |  |

| Legend:              |                      |                                                       |

|----------------------|----------------------|-------------------------------------------------------|

| R = Readable bit     | W = Writable bit     | U = Unimplemented bit, read as '0'                    |

| u = Bit is unchanged | x = Bit is unknown   | -n/n = Value at POR and BOR/Value at all other Resets |

| '1' = Bit is set     | '0' = Bit is cleared |                                                       |

#### bit 7-6 Unimplemented: Read as '0'

bit 5-0 D2S<5:0>: CLCx Data 2 Input Selection bits See Table 27-1.

#### See Table 27-1.

#### REGISTER 27-5: CLCxSEL2: GENERIC CLCx DATA 2 SELECT REGISTER

| U-0                  | U-0 | R/W-x/u                                                                  | R/W-x/u | R/W-x/u         | R/W-x/u | R/W-x/u | R/W-x/u |

|----------------------|-----|--------------------------------------------------------------------------|---------|-----------------|---------|---------|---------|

| —                    | —   |                                                                          |         | D3S             | 8<5:0>  |         |         |

| bit 7                |     |                                                                          |         |                 |         |         | bit 0   |

|                      |     |                                                                          |         |                 |         |         |         |

| Legend:              |     |                                                                          |         |                 |         |         |         |

| R = Readable bit     |     | W = Writable bit                                                         |         | U = Unimplement |         |         |         |

| u = Bit is unchanged | d   | x = Bit is unknown -n/n = Value at POR and BOR/Value at all other Resets |         |                 |         |         |         |

| '1' = Bit is set     |     | '0' = Bit is cleared                                                     |         |                 |         |         |         |

bit 7-6 Unimplemented: Read as '0'

bit 5-0 D3S<5:0>: CLCx Data 3 Input Selection bits See Table 27-1.

### REGISTER 27-6: CLCxSEL3: GENERIC CLCx DATA 3 SELECT REGISTER

| U-0   | U-0 | R/W-x/u | R/W-x/u  | R/W-x/u | R/W-x/u | R/W-x/u | R/W-x/u |  |

|-------|-----|---------|----------|---------|---------|---------|---------|--|

| —     | —   |         | D4S<5:0> |         |         |         |         |  |

| bit 7 |     |         |          |         |         |         | bit 0   |  |

|       |     |         |          |         |         |         |         |  |

| Legend:              |                      |                                                       |

|----------------------|----------------------|-------------------------------------------------------|

| R = Readable bit     | W = Writable bit     | U = Unimplemented bit, read as '0'                    |

| u = Bit is unchanged | x = Bit is unknown   | -n/n = Value at POR and BOR/Value at all other Resets |

| '1' = Bit is set     | '0' = Bit is cleared |                                                       |

bit 7-6 Unimplemented: Read as '0'

bit 5-0 D4S<5:0>: CLCx Data 4 Input Selection bits See Table 27-1.

| U-0                                   | U-0 | U-0                                                    | R/W-0/0 | R/W-0/0      | R/W-0/0                | R/W-0/0     | R/W-0/0 |

|---------------------------------------|-----|--------------------------------------------------------|---------|--------------|------------------------|-------------|---------|

| —                                     | —   | —                                                      |         |              | CH<4:0> <sup>(1)</sup> |             |         |

| bit 7                                 | •   | ·                                                      |         |              |                        |             | bit 0   |

|                                       |     |                                                        |         |              |                        |             |         |

| Legend:                               |     |                                                        |         |              |                        |             |         |

| R = Readable I                        | oit | W = Writable                                           | bit     | U = Unimpler | nented bit, read       | as '0'      |         |

| u = Bit is unchanged x = Bit is unkno |     | nown -n/n = Value at POR and BOR/Value at all other Re |         |              |                        | ther Resets |         |

| '1' = Bit is set                      |     | '0' = Bit is clea                                      | ared    |              |                        |             |         |

|                                       |     |                                                        |         |              |                        |             |         |

# REGISTER 30-3: MD1CARH: MODULATION HIGH CARRIER CONTROL REGISTER

| bit 7-5 | Unimplemented: Read as '0' |

|---------|----------------------------|

| bit 7-5 | Unimplemented: Read as '0  |

bit 4-0 CH<4:0>: Modulator Carrier High Selection bits<sup>(1)</sup> See Table 30-1 for signal list

Note 1: Unused selections provide an input value.

### REGISTER 30-4: MD1CARL: MODULATION LOW CARRIER CONTROL REGISTER

| U-0   | U-0 | U-0 | R/W-0/0 | R/W-0/0 | R/W-0/0    | R/W-0/0 | R/W-0/0 |

|-------|-----|-----|---------|---------|------------|---------|---------|

| —     | —   | _   |         |         | CL<4:0>(1) |         |         |

| bit 7 |     |     |         |         |            |         | bit 0   |

| Legend:              |                      |                                                       |

|----------------------|----------------------|-------------------------------------------------------|

| R = Readable bit     | W = Writable bit     | U = Unimplemented bit, read as '0'                    |

| u = Bit is unchanged | x = Bit is unknown   | -n/n = Value at POR and BOR/Value at all other Resets |

| '1' = Bit is set     | '0' = Bit is cleared |                                                       |

bit 7-5 Unimplemented: Read as '0'

bit 4-0 CL<4:0>: Modulator Carrier Low Input Selection bits<sup>(1)</sup> See Table 30-1 for signal list

Note 1: Unused selections provide a zero as the input value.

| FIGURE 31-5:                        | ASYNCHRONOUS RECE                                                                       | EPTION                   |                     |                        |           |

|-------------------------------------|-----------------------------------------------------------------------------------------|--------------------------|---------------------|------------------------|-----------|

| RX pin                              | Start<br>                                                                               | p Start<br>bit bit 0 / / | Xlast bit/ Stop bit | Stop                   |           |

| Rcv Shift<br>Reg<br>Rcv Buffer Reg. | ↓ ↓ ↓ ↓ ↓ ↓ ↓ ↓ ↓ ↓ ↓ ↓ ↓ ↓ ↓ ↓ ↓ ↓ ↓                                                   | <u> </u>                 | Word 2<br>UxRXB     | <u></u>                |           |

| RXIDL -                             |                                                                                         | <u> </u>                 | i~i                 | <u>}</u>               |           |

| Read Rcv<br>Buffer Reg.<br>UxRXB —  | <u>}                                </u>                                                | <u>} </u>                |                     | <u>}</u>               | ų         |

| UxRXIF<br>(Interrupt Flag)  -       | j                                                                                       | <u> </u>                 |                     |                        |           |

| RXFOIF bit                          |                                                                                         | <u> </u>                 |                     | <u></u> ز              |           |

|                                     |                                                                                         |                          |                     | Cleared by so          | oftware ) |

|                                     | iming diagram shows three words appearing<br>eived, causing the RXFOIF (FIFO overrun) b |                          |                     | ead before the third w | /ord      |

| R/W-0/0      | R/W-0/0                                                                                              | R/W-0/0                           | R/W-0/0         | U-0             | R/W-1/1          | R/W-0/0  | R/W-0/0 |  |  |  |  |

|--------------|------------------------------------------------------------------------------------------------------|-----------------------------------|-----------------|-----------------|------------------|----------|---------|--|--|--|--|

| SMP          | CKE                                                                                                  | CKP                               | FST             |                 | SSP              | SDIP     | SDOP    |  |  |  |  |

| bit 7        |                                                                                                      |                                   |                 |                 |                  |          | bit 0   |  |  |  |  |

| Legend:      |                                                                                                      |                                   |                 |                 |                  |          |         |  |  |  |  |

| R = Readable | e bit                                                                                                | W = Writable                      | bit             | U = Unimple     | mented bit, read | 1 as '0' |         |  |  |  |  |

|              |                                                                                                      |                                   | <b>0</b>        |                 |                  |          |         |  |  |  |  |

| bit 7        |                                                                                                      | out Sample Pha                    | ase Control bit |                 |                  |          |         |  |  |  |  |

|              | <u>Slave mode:</u><br>1 = Reserved                                                                   | 4                                 |                 |                 |                  |          |         |  |  |  |  |

|              |                                                                                                      |                                   | the middle of a | lata output tim |                  |          |         |  |  |  |  |

|              | <ul> <li>0 = SDI input is sampled in the middle of data output time</li> <li>Master mode:</li> </ul> |                                   |                 |                 |                  |          |         |  |  |  |  |

|              | <u>Master mode:</u><br>1 = SDI input is sampled at the end of data output time                       |                                   |                 |                 |                  |          |         |  |  |  |  |

|              | <ul> <li>0 = SDI input is sampled at the middle of data output time</li> </ul>                       |                                   |                 |                 |                  |          |         |  |  |  |  |

| bit 6        | CKE: Clock Edge Select bit                                                                           |                                   |                 |                 |                  |          |         |  |  |  |  |

|              | 1 = Output data changes on transition from active to idle clock state                                |                                   |                 |                 |                  |          |         |  |  |  |  |

|              | 0 = Output data changes on transition from idle to active clock state                                |                                   |                 |                 |                  |          |         |  |  |  |  |

| bit 5        | CKP: Clock Polarity Select bit                                                                       |                                   |                 |                 |                  |          |         |  |  |  |  |

|              | 1 = Idle state for SCK is high level                                                                 |                                   |                 |                 |                  |          |         |  |  |  |  |

|              | 0 = Idle state for SCK is low level                                                                  |                                   |                 |                 |                  |          |         |  |  |  |  |

| bit 4        | FST: Fast Start Enable bit                                                                           |                                   |                 |                 |                  |          |         |  |  |  |  |

|              | Slave mode:                                                                                          |                                   |                 |                 |                  |          |         |  |  |  |  |

|              | This bit is ignored                                                                                  |                                   |                 |                 |                  |          |         |  |  |  |  |

|              | Master mode:                                                                                         |                                   |                 |                 |                  |          |         |  |  |  |  |

|              | 1 = Delay to first SCK may be less than $\frac{1}{2}$ baud period                                    |                                   |                 |                 |                  |          |         |  |  |  |  |

|              | 0 = Delay to first SCK will be at least ½ baud period                                                |                                   |                 |                 |                  |          |         |  |  |  |  |

| bit 3        | Unimplemented: Read as '0'                                                                           |                                   |                 |                 |                  |          |         |  |  |  |  |

| bit 2        | SSP: SS Input/Output Polarity Control bit                                                            |                                   |                 |                 |                  |          |         |  |  |  |  |

|              | 1 = SS is active-low                                                                                 |                                   |                 |                 |                  |          |         |  |  |  |  |

| hit 1        | 0 = SS is active-high                                                                                |                                   |                 |                 |                  |          |         |  |  |  |  |

| bit 1        | SDIP: SDI Input Polarity Control bit                                                                 |                                   |                 |                 |                  |          |         |  |  |  |  |

|              | 1 = SDI input is active-low                                                                          |                                   |                 |                 |                  |          |         |  |  |  |  |

|              | <ul> <li>0 = SDI input is active-high</li> <li>SDOP: SDI Output Polarity Control bit</li> </ul>      |                                   |                 |                 |                  |          |         |  |  |  |  |

| hit 0        |                                                                                                      | Jutnut Polarity                   | Control hit     |                 |                  |          |         |  |  |  |  |

| bit 0        |                                                                                                      | Dutput Polarity out is active-lov |                 |                 |                  |          |         |  |  |  |  |

| BZ Branch if Zero |                                                                                     |                                                                                                                                                                                                                                                                       |                        |                              |                 |  |  |  |  |  |

|-------------------|-------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------|------------------------------|-----------------|--|--|--|--|--|

| Synta             | ax:                                                                                 | BZ n                                                                                                                                                                                                                                                                  | BZ n                   |                              |                 |  |  |  |  |  |

| Oper              | ands:                                                                               | -128 ≤ n ≤ <sup>-</sup>                                                                                                                                                                                                                                               | 127                    |                              |                 |  |  |  |  |  |

| Oper              | ation:                                                                              | if ZERO bit<br>(PC) + 2 + 2                                                                                                                                                                                                                                           |                        |                              |                 |  |  |  |  |  |

| Statu             | is Affected:                                                                        | None                                                                                                                                                                                                                                                                  |                        |                              |                 |  |  |  |  |  |

| Enco              | ding:                                                                               | 1110                                                                                                                                                                                                                                                                  | 0000                   | nnnı                         | n nnnn          |  |  |  |  |  |

| Desc              | ription:                                                                            | If the ZERO bit is '1', then the program will branch.<br>The 2's complement number '2n' is added to the PC. Since the PC will have incremented to fetch the next instruction, the new address will be PC + $2 + 2n$ . This instruction is then a 2-cycle instruction. |                        |                              |                 |  |  |  |  |  |

| Word              | ls:                                                                                 | 1                                                                                                                                                                                                                                                                     | 1                      |                              |                 |  |  |  |  |  |

| Cycle             | es:                                                                                 | 1(2)                                                                                                                                                                                                                                                                  | 1(2)                   |                              |                 |  |  |  |  |  |

| Q C<br>If Ju      | ycle Activity:<br>Imp:                                                              |                                                                                                                                                                                                                                                                       |                        |                              |                 |  |  |  |  |  |

|                   | Q1                                                                                  | Q2                                                                                                                                                                                                                                                                    | Q3                     |                              | Q4              |  |  |  |  |  |

|                   | Decode                                                                              | Read literal<br>'n'                                                                                                                                                                                                                                                   | Proces<br>Data         | s                            | Write to PC     |  |  |  |  |  |

|                   | No<br>operation                                                                     | No<br>operation                                                                                                                                                                                                                                                       | No<br>operatio         | on                           | No<br>operation |  |  |  |  |  |

| lf No             | o Jump:                                                                             |                                                                                                                                                                                                                                                                       |                        |                              |                 |  |  |  |  |  |

|                   | Q1                                                                                  | Q2                                                                                                                                                                                                                                                                    | Q3                     |                              | Q4              |  |  |  |  |  |

|                   | Decode                                                                              | Read literal<br>'n'                                                                                                                                                                                                                                                   | Proces<br>Data         | s                            | No<br>operation |  |  |  |  |  |

| <u>Exan</u>       | nple:<br>Before Instruc<br>PC<br>After Instructio<br>If ZERO<br>If ZERO<br>PC<br>PC | = ad<br>= 1;<br>= ad<br>= 0;                                                                                                                                                                                                                                          | dress (HI<br>dress (J1 | ump<br>ERE)<br>ump)<br>ERE - | + 2)            |  |  |  |  |  |

| CAL                                                                                                                                                                                                                                                                                                                                                                                           | L                                       | Subrouti                                                                                    | ne Call                                                                                                                                                                                                         |                           |                                           |  |  |  |  |

|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------|---------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------|-------------------------------------------|--|--|--|--|

| Synta                                                                                                                                                                                                                                                                                                                                                                                         | ax:                                     | CALL k {,s}                                                                                 |                                                                                                                                                                                                                 |                           |                                           |  |  |  |  |

| Oper                                                                                                                                                                                                                                                                                                                                                                                          | ands:                                   | $0 \le k \le 104$<br>s $\in$ [0,1]                                                          | 0 ≤ k ≤ 1048575<br>s ∈ [0,1]                                                                                                                                                                                    |                           |                                           |  |  |  |  |

| Oper                                                                                                                                                                                                                                                                                                                                                                                          | ation:                                  | $\hat{k} \rightarrow PC < 20$<br>if s = 1<br>(W) $\rightarrow$ WS<br>(Status) $\rightarrow$ | $\begin{array}{l} (PC) + 4 \rightarrow TOS, \\ k \rightarrow PC < 20:1>, \\ \text{if s = 1} \\ (W) \rightarrow WS, \\ (\text{Status}) \rightarrow \text{STATUSS}, \\ (BSR) \rightarrow \text{BSRS} \end{array}$ |                           |                                           |  |  |  |  |

| Statu                                                                                                                                                                                                                                                                                                                                                                                         | s Affected:                             | None                                                                                        |                                                                                                                                                                                                                 |                           |                                           |  |  |  |  |

|                                                                                                                                                                                                                                                                                                                                                                                               | ding:<br>/ord (k<7:0>)<br>word(k<19:8>) | 1110<br>1111                                                                                | 110s<br>k <sub>19</sub> kkk                                                                                                                                                                                     | k <sub>7</sub> kk<br>kkk} | 0                                         |  |  |  |  |

| Description:<br>Subroutine call of entire 2-Mbyte<br>memory range. First, return addr<br>(PC + 4) is pushed onto the return<br>stack. If 's' = 1, the W, Status and<br>registers are also pushed into the<br>respective shadow registers, WS<br>STATUSS and BSRS. If 's' = 0, r<br>update occurs (default). Then, th<br>20-bit value 'k' is loaded into PC<<br>CALL is a 2-cycle instruction. |                                         |                                                                                             |                                                                                                                                                                                                                 |                           |                                           |  |  |  |  |

| Word                                                                                                                                                                                                                                                                                                                                                                                          | ls:                                     | 2                                                                                           |                                                                                                                                                                                                                 |                           |                                           |  |  |  |  |

| Cycle                                                                                                                                                                                                                                                                                                                                                                                         | es:                                     | 2                                                                                           | 2                                                                                                                                                                                                               |                           |                                           |  |  |  |  |

| QC                                                                                                                                                                                                                                                                                                                                                                                            | ycle Activity:                          |                                                                                             |                                                                                                                                                                                                                 |                           |                                           |  |  |  |  |

|                                                                                                                                                                                                                                                                                                                                                                                               | Q1                                      | Q2                                                                                          | Q3                                                                                                                                                                                                              |                           | Q4                                        |  |  |  |  |

|                                                                                                                                                                                                                                                                                                                                                                                               | Decode                                  | Read literal<br>'k'<7:0>,                                                                   | PUSH F<br>stac                                                                                                                                                                                                  | :k                        | Read literal<br>'k'<19:8>,<br>Write to PC |  |  |  |  |

|                                                                                                                                                                                                                                                                                                                                                                                               | No<br>operation                         | No<br>operation                                                                             | No<br>operation                                                                                                                                                                                                 |                           | No<br>operation                           |  |  |  |  |

| Exan                                                                                                                                                                                                                                                                                                                                                                                          |                                         | HERE                                                                                        | CALL                                                                                                                                                                                                            | THER                      | •                                         |  |  |  |  |

Before Instruction PC

After Instruction

PC TOS WS BSRS

=

=

=

= = STATUSS = address (HERE)

address (THERE)

Status

address (HERE + 4) W BSR

# TABLE 44-6: I/O PORTS

| Standard     | d Operati | ing Conditions (unless otherwi       | se stated)          |                      | -                   |       |                                                       |  |  |  |

|--------------|-----------|--------------------------------------|---------------------|----------------------|---------------------|-------|-------------------------------------------------------|--|--|--|

| Param<br>No. | Sym.      | Characteristic                       | Min.                | Тур†                 | Max.                | Units | Conditions                                            |  |  |  |

|              | VIL       | Input Low Voltage                    |                     |                      |                     |       |                                                       |  |  |  |

|              |           | I/O PORT:                            | I/O PORT:           |                      |                     |       |                                                       |  |  |  |

| D300         |           | with TTL buffer                      |                     | _                    | 0.8                 | V     | $4.5V \le VDD \le 5.5V$                               |  |  |  |

| D301         |           |                                      | _                   | _                    | 0.15 Vdd            | V     | 1.8V ≤ VDD < 4.5V                                     |  |  |  |

| D302         |           | with Schmitt Trigger buffer          | _                   | _                    | 0.2 VDD             | V     | 2.0V ≤ VDD ≤ 5.5                                      |  |  |  |

| D303         |           | with I <sup>2</sup> C levels         | _                   | _                    | 0.3 VDD             | V     |                                                       |  |  |  |

| D304         |           | with SMBus 2.0                       | _                   | _                    | 0.8                 | V     | 2.7V ≤ VDØ ≤ 5.5V                                     |  |  |  |

| D305         |           | with SMBus 3.0                       | _                   | —                    | 0.8                 | V     | 1.8V ≤ VDØ ≤ 5.5V                                     |  |  |  |

| D306         |           | MCLR                                 | _                   | _                    | 0.2 VDD             | V     |                                                       |  |  |  |

|              | Vih       | Input High Voltage                   |                     |                      |                     |       |                                                       |  |  |  |

|              |           | I/O PORT:                            |                     |                      |                     |       |                                                       |  |  |  |

| D320         |           | with TTL buffer                      | 2.0                 | _                    | _                   | v     | 4.5V ≩ Vpp ≤ 5,5V                                     |  |  |  |

| D321         |           |                                      | 0.25 VDD +<br>0.8   | _                    |                     | V     | 1.8V 2 VDD < 4.5V                                     |  |  |  |

| D322         |           | with Schmitt Trigger buffer          | 0.8 Vdd             | _                    | `                   | X     | $2.0 \times \neq V$ DD $\leq 5.5 V$                   |  |  |  |

| D323         |           | with I <sup>2</sup> C levels         | 0.7 Vdd             | _                    |                     | A     |                                                       |  |  |  |

| D324         |           | with SMBus 2.0                       | 2.1                 | -^                   | $\mathcal{F}$       | V     | $2.7V \le VDD \le 5.5V$                               |  |  |  |

| D325         |           | with SMBus 3.0                       | 1.35                |                      | /-/                 | У     | $1.8V \leq V\text{DD} \leq 5.5V$                      |  |  |  |

| D326         |           | MCLR                                 | 0.7 VDD             | $\overline{\langle}$ | $\langle - \rangle$ | ٧     |                                                       |  |  |  |

|              | lı∟       | Input Leakage Current <sup>(1)</sup> |                     |                      |                     |       |                                                       |  |  |  |

| D340         |           | I/O Ports                            |                     | ± 5                  | € 125               | nA    | $Vss \le VPIN \le VDD$ , Pin at high-impedance, 85°C  |  |  |  |

| D341         |           | <                                    | $\langle - \rangle$ | ±5                   | ± 1000              | nA    | $Vss \le VPIN \le VDD$ , Pin at high-impedance, 125°C |  |  |  |

| D342         |           | MCLR <sup>(2)</sup>                  | 7                   | ± 50                 | ± 200               | nA    | $Vss \le VPIN \le VDD$ , Pin at high-impedance, 85°C  |  |  |  |

|              | IPUR      | Weak Pull-up Current                 | · · ·               |                      |                     |       |                                                       |  |  |  |

| D350         |           |                                      | 25                  | 120                  | 200                 | μA    | VDD = 3.0V, VPIN = VSS                                |  |  |  |

|              | Vol       | Output Low Voltage                   |                     |                      |                     |       |                                                       |  |  |  |