Welcome to E-XFL.COM

### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

### Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

### Details

| Details                    |                                                                            |

|----------------------------|----------------------------------------------------------------------------|

| Product Status             | Active                                                                     |

| Core Processor             | PIC                                                                        |

| Core Size                  | 8-Bit                                                                      |

| Speed                      | 64MHz                                                                      |

| Connectivity               | I <sup>2</sup> C, LINbus, SPI, UART/USART                                  |

| Peripherals                | Brown-out Detect/Reset, DMA, HLVD, POR, PWM, WDT                           |

| Number of I/O              | 36                                                                         |

| Program Memory Size        | 32KB (16K x 16)                                                            |

| Program Memory Type        | FLASH                                                                      |

| EEPROM Size                | 256 x 8                                                                    |

| RAM Size                   | 2K x 8                                                                     |

| Voltage - Supply (Vcc/Vdd) | 2.3V ~ 5.5V                                                                |

| Data Converters            | A/D 35x12b; D/A 1x5b                                                       |

| Oscillator Type            | Internal                                                                   |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                          |

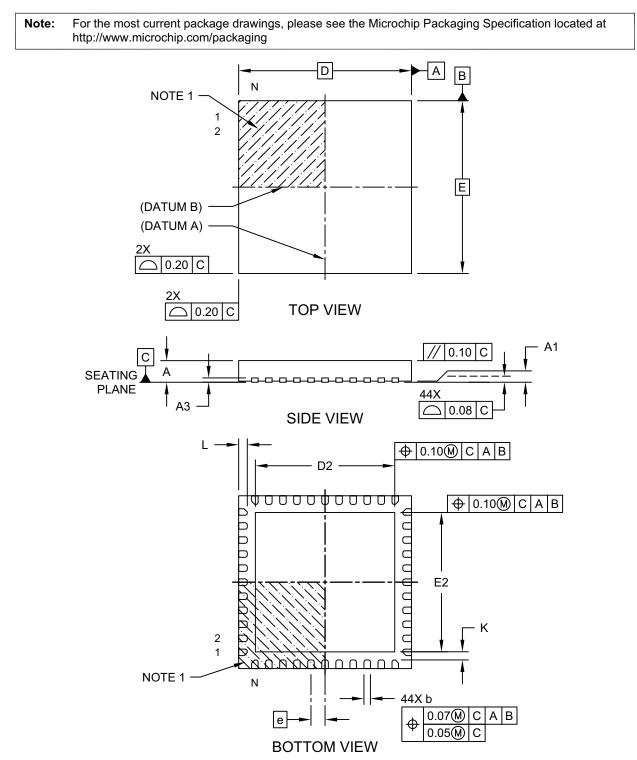

| Mounting Type              | Surface Mount                                                              |

| Package / Case             | 44-VQFN Exposed Pad                                                        |

| Supplier Device Package    | 44-QFN (8x8)                                                               |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/pic18f45k42-i-ml |

|                            |                                                                            |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

| Pin Allocation Tables |

|-----------------------|

|-----------------------|

| bit         bit <th>TABLE 1</th> <th>:</th> <th></th> <th>28-PIN ALI</th> <th>LOCATION</th> <th>TABLE (PIC18(</th> <th>L)F2XK42)</th> <th></th>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | TABLE 1 | :                      |               | 28-PIN ALI                    | LOCATION          | TABLE (PIC18( | L)F2XK42)        |                   |                       |                    |                     |                       |                      |                     |                       |                       |     |                        |                     |         |

|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------|------------------------|---------------|-------------------------------|-------------------|---------------|------------------|-------------------|-----------------------|--------------------|---------------------|-----------------------|----------------------|---------------------|-----------------------|-----------------------|-----|------------------------|---------------------|---------|

| Image: Problem in the system in theresystem in the system in there and the system in the s | 0/1     | 28-Pin SPDIP/SOIC/SSOP | 28-Pin (U)QFN | ADC                           | Voltage Reference | DAC           | Comparators      | Zero Cross Detect | I²C                   | SPI                | UART                | WSD                   | Timers/SMT           | CCP and PWM         | CWG                   | CLC                   | NCO | Clock Reference (CLKR) | Interrupt-on-Change | Basic   |

| Image: Probability of the p | RA0     | 2                      | 27            | ANA0                          | —                 | —             | C1IN0-<br>C2IN0- | -                 | —                     | _                  |                     | _                     | _                    | -                   | -                     | CLCIN0 <sup>(1)</sup> | _   | -                      | IOCA0               | —       |

| Image         Image <t< td=""><td>RA1</td><td>3</td><td>28</td><td>ANA1</td><td>-</td><td>—</td><td></td><td>-</td><td>-</td><td>-</td><td>-</td><td>—</td><td>_</td><td>—</td><td>—</td><td>CLCIN1<sup>(1)</sup></td><td>-</td><td>-</td><td>IOCA1</td><td>-</td></t<>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | RA1     | 3                      | 28            | ANA1                          | -                 | —             |                  | -                 | -                     | -                  | -                   | —                     | _                    | —                   | —                     | CLCIN1 <sup>(1)</sup> | -   | -                      | IOCA1               | -       |

| R4         6         3         ANA4             MDCARH <sup>0</sup> TOCKI <sup>0</sup> MDCARH <sup>0</sup> TOCKI <sup>0</sup> MDCARH <sup>0</sup> TOCKI <sup>0</sup> </td <td>RA2</td> <td>4</td> <td>1</td> <td>ANA2</td> <td>VREF-</td> <td>DAC1OUT1</td> <td></td> <td>I</td> <td>-</td> <td>—</td> <td>-</td> <td>-</td> <td>—</td> <td>—</td> <td>—</td> <td>-</td> <td>—</td> <td>-</td> <td>IOCA2</td> <td>—</td>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | RA2     | 4                      | 1             | ANA2                          | VREF-             | DAC1OUT1      |                  | I                 | -                     | —                  | -                   | -                     | —                    | —                   | —                     | -                     | —   | -                      | IOCA2               | —       |

| RAS       7       4       ANAS           NDSRC <sup>10</sup> ICCAS          RA6       10       7       ANAG        ICCAS       ICCAS <td>RA3</td> <td>5</td> <td>2</td> <td>ANA3</td> <td>VREF+</td> <td>_</td> <td>C1IN1+</td> <td> </td> <td>_</td> <td>_</td> <td> </td> <td>MDCARL<sup>(1)</sup></td> <td>_</td> <td>_</td> <td>_</td> <td>_</td> <td>_</td> <td>_</td> <td>IOCA3</td> <td>_</td>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | RA3     | 5                      | 2             | ANA3                          | VREF+             | _             | C1IN1+           |                   | _                     | _                  |                     | MDCARL <sup>(1)</sup> | _                    | _                   | _                     | _                     | _   | _                      | IOCA3               | _       |

| RA6       10       7       ANA6                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | RA4     | 6                      | 3             | ANA4                          | _                 | _             |                  | _                 | _                     | _                  | -                   | MDCARH <sup>(1)</sup> | T0CKI <sup>(1)</sup> | _                   | _                     | _                     | _   | _                      | IOCA4               | _       |

| Image: Normal Section  | RA5     | 7                      | 4             | ANA5                          | _                 | _             | _                | -                 | _                     | SS1 <sup>(1)</sup> | _                   | MDSRC <sup>(1)</sup>  | _                    | _                   | _                     | _                     | _   | -                      | IOCA5               | —       |

| Image: Constraint of the state of | RA6     | 10                     | 7             | ANA6                          | -                 | -             | -                | -                 | -                     | -                  | -                   | -                     | -                    | -                   | -                     | —                     |     |                        | IOCA6               |         |

| Image: Constraint of the state of | RA7     | 9                      | 6             | ANA7                          | _                 | —             | _                | -                 | —                     | _                  | _                   | —                     | _                    | —                   | —                     | —                     | _   | -                      | IOCA7               |         |

| Image: Normal Section Sectin Section Section Section Section Section Section S | RB0     | 21                     | 18            | ANB0                          | —                 | -             | C2IN1+           | ZCD               | -                     | —                  | -                   | -                     | —                    | CCP4 <sup>(1)</sup> | CWG1IN <sup>(1)</sup> | -                     | —   | -                      |                     | —       |

| Image: Normal system         Image: N                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | RB1     | 22                     | 19            | ANB1                          | —                 | —             |                  |                   | SCL2 <sup>(3,4)</sup> | _                  | -                   | —                     | —                    | —                   | CWG2IN <sup>(1)</sup> | —                     | _   | _                      |                     | —       |

| RB4         25         24         ANB4<br>ADCACT <sup>(1)</sup> TGG <sup>(1)</sup> TGG <sup>(1)</sup>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | RB2     | 23                     | 20            | ANB2                          | —                 | -             | -                | I                 | SDA2 <sup>(3,4)</sup> | —                  | -                   | -                     | —                    | —                   | CWG3IN <sup>(1)</sup> | -                     | —   | -                      |                     | —       |

| ADCACT <sup>(1)</sup>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | RB3     | 24                     | 21            | ANB3                          | —                 | -             |                  | —                 | —                     | _                  | —                   | —                     | _                    | -                   | -                     | -                     | —   | —                      | IOCB3               | —       |

| RB6 27 24 ANB6 CLCIN2 <sup>(1)</sup> IOCB6 ICSPCLK                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | RB4     | 25                     | 22            | ANB4<br>ADCACT <sup>(1)</sup> | —                 | —             | —                | —                 | —                     | —                  | —                   | —                     | T5G <sup>(1)</sup>   | —                   | —                     | —                     | —   | —                      | IOCB4               | —       |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | RB5     | 26                     | 23            | ANB5                          | _                 | —             | _                | -                 | _                     | _                  | _                   | _                     | T1G <sup>(1)</sup>   | CCP3 <sup>(1)</sup> | —                     | —                     | _   | _                      | IOCB5               | —       |

| RB7 28 25 ANB7 - DAC10UT2 RX2 <sup>(1)</sup> - T6IN(1) CLCIN3 <sup>(1)</sup> IOCB7 ICSPDAT                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | RB6     | 27                     | 24            | ANB6                          | —                 |               | _                | —                 | _                     | _                  | CTS2 <sup>(1)</sup> | _                     | _                    | _                   | _                     |                       | _   | _                      | IOCB6               | ICSPCLK |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | RB7     | 28                     | 25            | ANB7                          | —                 | DAC10UT2      | _                | _                 | _                     |                    | RX2 <sup>(1)</sup>  | _                     | T6IN(1)              | —                   | —                     | CLCIN3 <sup>(1)</sup> | -   | -                      | IOCB7               | ICSPDAT |

Note 1: This is a PPS remappable input signal. The input function may be moved from the default location shown to one of several other PORTx pins.

2: All output signals shown in this row are PPS remappable.

3: This is a bidirectional signal. For normal module operation, the firmware should map this signal to the same pin in both the PPS input and PPS output registers.

4: These pins can be configured for I<sup>2</sup>C and SMB<sup>™</sup> 3.0/2.0 logic levels; The SCLx/SDAx signals may be assigned to any of the RB1/RB2/RC3/RC4 pins. PPS assignments to the other pins (e.g., RA5) will operate, but input logic levels will be standard TTL/ST as selected by the INLVL register, instead of the I<sup>2</sup>C specific or SMBUs input buffer thresholds.

| EXAMPLE 9-3                                    | SETTING UP VECTOR                                                                      | ED INTERRUPTS USING MPASM                                                                                                |

|------------------------------------------------|----------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------|

| ISR_TMR0: CC<br>BANKSI<br>BCF<br>BTG<br>RETFIN | L PIRO<br>PIR3, TMROIF<br>LATC, 0, ACCESS                                              | ; ISR code at 0x08C0 in PFM<br>; Select bank for PIR0<br>; Clear TMR0IF<br>; Code to execute in ISR<br>; Return from ISR |

| InterruptInit                                  | :                                                                                      |                                                                                                                          |

| BANKSI                                         | L INTCONO                                                                              | ; Select bank for INTCON0                                                                                                |

| BSF                                            | INTCONO, GIEH                                                                          | ; Enable high priority interrupts                                                                                        |

| BSF                                            | INTCONO, GIEL                                                                          | ; Enable low priority interrupts                                                                                         |

| BSF                                            | INTCONU, IPEN_INTC                                                                     | CON0 ; Enable interrupt priority                                                                                         |

| BANKSI                                         | CL PIEO                                                                                | ; Select bank for PIE0                                                                                                   |

| BSF                                            | PIE3, TMROIE                                                                           | ; Enable TMR0 interrupt                                                                                                  |

| BSF                                            | PIE4, TMR1IE                                                                           | ; Enable TMR1 interrupt                                                                                                  |

| BCF<br>RETURI                                  | IPR3, TMROIP<br>1 1                                                                    | ; Make TMR0 interrupt low priority                                                                                       |

| VectorTableIn                                  | it:                                                                                    |                                                                                                                          |

| ; Set                                          | IVTBASE (optional - defaul                                                             | t is 0x000008)                                                                                                           |

| MOVLW                                          | 0x00                                                                                   | ; This is optional                                                                                                       |

| MOVWF                                          |                                                                                        | ; If not included, then the                                                                                              |

| MOVLW                                          | 0x40                                                                                   | ; hardware default value of                                                                                              |

| MOVWF                                          | IVTBASEH, ACCESS                                                                       | ; 0x0008 will be taken.                                                                                                  |

| MOVLW<br>MOVWF                                 | 0x08<br>IVTBASEL, ACCESS                                                               |                                                                                                                          |

| 110 VW1                                        |                                                                                        |                                                                                                                          |

| ; TMR(                                         | vector at IVTBASE + 2*(TM                                                              | R0 vector number i.e. 31) = 0x4046                                                                                       |

| MOVLW                                          | 0x00                                                                                   | ; Load TBLPTR with the                                                                                                   |

| MOVWF                                          | TBLPTRU, ACCESS                                                                        | ; PFM memory location to be                                                                                              |

| MOVLW<br>MOVWF                                 | 0x40<br>TBLPTRH, ACCESS                                                                | ; written to.                                                                                                            |

| MOVIW                                          | 0x46                                                                                   |                                                                                                                          |

| MOVWF                                          | TBLPTRL, ACCESS                                                                        |                                                                                                                          |

|                                                | te the contents of TMR0 vector<br>TMR0_ADDRESS >> 2 = 0x08C0<br>0x30<br>TABLAT, ACCESS |                                                                                                                          |

| TBLWT                                          |                                                                                        | ; Write to temp table latch                                                                                              |

|                                                |                                                                                        | ,                                                                                                                        |

| MOVLW                                          | 0x02                                                                                   | ; High byte next                                                                                                         |

| MOVWF<br>TBLWT:                                | TABLAT, ACCESS                                                                         | ; Write to temp table latch                                                                                              |

|                                                |                                                                                        | ,                                                                                                                        |

|                                                | e to PFM now using NVMCON                                                              |                                                                                                                          |

| BANKSI                                         |                                                                                        | ; Select bank for NVMCON1                                                                                                |

| MOVLW                                          | 0x84                                                                                   | ; Setting to write to PFM                                                                                                |

| MOVWF                                          | NVMCON1                                                                                |                                                                                                                          |

| MOVLW                                          | 0x55                                                                                   | ; Required unlock sequence                                                                                               |

| MOVWF                                          | NVMCON2                                                                                |                                                                                                                          |

| MOVLW                                          | 0 x A A                                                                                |                                                                                                                          |

| MOVWF                                          | NVMCON2                                                                                |                                                                                                                          |

| BSF                                            | NVMCON1, WR                                                                            | ; Start writing to PFM                                                                                                   |

| BTFSC                                          | NVMCON1, WR                                                                            | ; Wait for write to complete                                                                                             |

| GOTO                                           | \$-2                                                                                   |                                                                                                                          |

| RETURI                                         | 1                                                                                      |                                                                                                                          |

|                                                | -                                                                                      |                                                                                                                          |

| L                                              |                                                                                        |                                                                                                                          |

### EXAMPLE 9-3: SETTING UP VECTORED INTERRUPTS USING MPASM

| R/W-1/1                 | R/W-1/1                        | R/W-1/1           | R/W-1/1          | R/W-1/1         | R/W-1/1          | R/W-1/1        | R/W-1/1      |

|-------------------------|--------------------------------|-------------------|------------------|-----------------|------------------|----------------|--------------|

| TMR0IP                  | U1IP                           | U1EIP             | U1TXIP           | U1RXIP          | I2C1EIP          | I2C1IP         | I2C1TXIP     |

| bit 7                   |                                |                   |                  |                 |                  |                | bit C        |

|                         |                                |                   |                  |                 |                  |                |              |

| Legend:<br>R = Readable | hit                            | W = Writable      | hit              | II – I Inimplor | nented bit, read | as 'O'         |              |

| u = Bit is unch         |                                | x = Bit is unkr   |                  |                 | at POR and BOI   |                | othor Pocote |

| '1' = Bit is set        | -                              | 0' = Bit is clear |                  |                 |                  | value at all t |              |

|                         |                                |                   | areu             |                 |                  |                |              |

| bit 7                   | TMR0IP: TM                     | R0 Interrupt Pri  | ority bit        |                 |                  |                |              |

|                         | 1 = High prio<br>0 = Low prior |                   |                  |                 |                  |                |              |

| bit 6                   | U1IP: UART1                    | Interrupt Prior   | ity bit          |                 |                  |                |              |

|                         | 1 = High prio                  | •                 |                  |                 |                  |                |              |

|                         | 0 = Low prior                  | •                 |                  |                 |                  |                |              |

| bit 5                   |                                | 1 Framing Err     | or Interrupt Pr  | iority bit      |                  |                |              |

|                         | 1 = High prio<br>0 = Low prio  |                   |                  |                 |                  |                |              |

| bit 4                   | •                              | RT1 Transmit Ir   | terrupt Priorit  | v bit           |                  |                |              |

|                         | 1 = High prio                  |                   |                  | ,               |                  |                |              |

|                         | 0 = Low prior                  |                   |                  |                 |                  |                |              |

| bit 3                   |                                | RT1 Receive In    | terrupt Priority | y bit           |                  |                |              |

|                         | 1 = High prio                  |                   |                  |                 |                  |                |              |

| <b>h</b> # 0            | 0 = Low prior                  | •                 |                  |                 |                  |                |              |

| bit 2                   | 1 = High prio                  | 1 Error Interrup  | ot Priority bit  |                 |                  |                |              |

|                         | 0 = Low prior                  |                   |                  |                 |                  |                |              |

| bit 1                   |                                | Interrupt Priorit | ty bit           |                 |                  |                |              |

|                         | 1 = High prio                  | rity              |                  |                 |                  |                |              |

|                         | 0 = Low prior                  |                   |                  |                 |                  |                |              |

| bit 0                   |                                | C1 Transmit Int   | errupt Priority  | bit             |                  |                |              |

|                         | 1 = High prio                  |                   |                  |                 |                  |                |              |

|                         | 0 = Low prior                  | TITV              |                  |                 |                  |                |              |

### REGISTER 9-28: IPR3: PERIPHERAL INTERRUPT PRIORITY REGISTER 3

### 11.0 WINDOWED WATCHDOG TIMER (WWDT)

The Watchdog Timer (WDT) is a system timer that generates a Reset if the firmware does not issue a CLRWDT instruction within the time-out period. The Watchdog Timer is typically used to recover the system from unexpected events. The Windowed Watchdog Timer (WWDT) differs in that CLRWDT instructions are only accepted when they are performed within a specific window during the time-out period.

The WWDT has the following features:

- Selectable clock source

- Multiple operating modes

- WWDT is always On

- WWDT is off when in Sleep

- WWDT is controlled by software

- WWDT is always Off

- Configurable time-out period is from 1 ms to 256s (nominal)

- Configurable window size from 12.5% to 100% of the time-out period

- Multiple Reset conditions

| U-0     | R/W <sup>(3)</sup> -q/q <sup>(1)</sup> R/W <sup>(3)</sup> -q/q <sup>(1)</sup> R/W <sup>(3)</sup> -q/q <sup>(1)</sup> | U-0 | R/W <sup>(4)</sup> -q/q <sup>(2)</sup> | R/W <sup>(4)</sup> _q/q <sup>(2)</sup> | R/W <sup>(4)</sup> -q/q <sup>(2)</sup> |

|---------|----------------------------------------------------------------------------------------------------------------------|-----|----------------------------------------|----------------------------------------|----------------------------------------|

| -       | CS<2:0>                                                                                                              | _   |                                        | WINDOW<2:0>                            |                                        |

| bit 7   |                                                                                                                      |     |                                        |                                        | bit 0                                  |

|         |                                                                                                                      |     |                                        |                                        |                                        |

| Legend: |                                                                                                                      |     |                                        |                                        |                                        |

### REGISTER 11-2: WDTCON1: WATCHDOG TIMER CONTROL REGISTER 1

| Legena.              |                      |                                                       |

|----------------------|----------------------|-------------------------------------------------------|

| R = Readable bit     | W = Writable bit     | U = Unimplemented bit, read as '0'                    |

| u = Bit is unchanged | x = Bit is unknown   | -n/n = Value at POR and BOR/Value at all other Resets |

| '1' = Bit is set     | '0' = Bit is cleared | q = Value depends on condition                        |

### bit 7 Unimplemented: Read as '0'

bit 6-4 **CS<2:0>:** Watchdog Timer Clock Select bits

- 111 = Reserved •

- •

- •

- 011 = Reserved

- 010 = SOSC

- 001 = MFINTOSC 31.25 kHz

- 000 = LFINTOSC 31 kHz

- bit 3 Unimplemented: Read as '0'

### bit 2-0 WINDOW<2:0>: Watchdog Timer Window Select bits

| WINDOW<2:0> | Window delay<br>Percent of time | Window opening<br>Percent of time |

|-------------|---------------------------------|-----------------------------------|

| 111         | N/A                             | 100                               |

| 110         | 12.5                            | 87.5                              |

| 101         | 25                              | 75                                |

| 100         | 37.5                            | 62.5                              |

| 011         | 50                              | 50                                |

| 010         | 62.5                            | 37.5                              |

| 001         | 75                              | 25                                |

| 000         | 87.5                            | 12.5                              |

Note 1: If WDTCCS <2:0> in CONFIG3H = 111, the Reset value of CS<2:0> is 000.

2: The Reset value of WINDOW<2:0> is determined by the value of WDTCWS<2:0> in the CONFIG3H register.

**3:** If WDTCCS<2:0> in CONFIG3H  $\neq$  111, these bits are read-only.

4: If WDTCWS<2:0> in CONFIG3H  $\neq$  111, these bits are read-only.

### **REGISTER 14-6: CRCACCL: CRC ACCUMULATOR LOW BYTE REGISTER**

| R/W-0/0          | R/W-0/0 | R/W-0/0           | R/W-0/0 | R/W-0/0        | R/W-0/0          | R/W-0/0          | R/W-0/0     |

|------------------|---------|-------------------|---------|----------------|------------------|------------------|-------------|

|                  |         |                   | ACC     | <7:0>          |                  |                  |             |

| bit 7            |         |                   |         | -              |                  |                  | bit 0       |

|                  |         |                   |         |                |                  |                  |             |

| Legend:          |         |                   |         |                |                  |                  |             |

| R = Readable     | bit     | W = Writable      | bit     | U = Unimpler   | nented bit, read | l as '0'         |             |

| u = Bit is unch  | anged   | x = Bit is unkr   | nown    | -n/n = Value a | at POR and BO    | R/Value at all c | ther Resets |

| '1' = Bit is set |         | '0' = Bit is clea | ared    |                |                  |                  |             |

bit 7-0 ACC<7:0>: CRC Accumulator Register bits

### REGISTER 14-7: CRCSHIFTH: CRC SHIFT HIGH BYTE REGISTER

| R-0   | R-0 | R-0 | R-0   | R-0    | R-0 | R-0 | R-0   |

|-------|-----|-----|-------|--------|-----|-----|-------|

|       |     |     | SHIFT | <15:8> |     |     |       |

| bit 7 |     |     |       |        |     |     | bit 0 |

|       |     |     |       |        |     |     |       |

| Legend:              |                      |                                                       |

|----------------------|----------------------|-------------------------------------------------------|

| R = Readable bit     | W = Writable bit     | U = Unimplemented bit, read as '0'                    |

| u = Bit is unchanged | x = Bit is unknown   | -n/n = Value at POR and BOR/Value at all other Resets |

| '1' = Bit is set     | '0' = Bit is cleared |                                                       |

bit 7-0 SHIFT<15:8>: CRC Shifter Register bits

Reading from this register reads the CRC Shifter.

### REGISTER 14-8: CRCSHIFTL: CRC SHIFT LOW BYTE REGISTER

| R-0   | R-0 | R-0 | R-0  | R-0    | R-0 | R-0 | R-0   |

|-------|-----|-----|------|--------|-----|-----|-------|

|       |     |     | SHIF | Γ<7:0> |     |     |       |

| bit 7 |     |     |      |        |     |     | bit 0 |

| Legend:              |                      |                                                       |

|----------------------|----------------------|-------------------------------------------------------|

| R = Readable bit     | W = Writable bit     | U = Unimplemented bit, read as '0'                    |

| u = Bit is unchanged | x = Bit is unknown   | -n/n = Value at POR and BOR/Value at all other Resets |

| '1' = Bit is set     | '0' = Bit is cleared |                                                       |

bit 7-0 SHIFT<7:0>: CRC Shifter Register bits Reading from this register reads the CRC Shifter.

### 15.5 DMA Message Transfers

Once the Enable bit is set to start DMA message transfers, the Source/Destination pointer and counter registers are initialized to the conditions shown in Table 15-3.

### TABLE 15-3: DMA INITIAL CONDITIONS

| Register       | Value loaded  |

|----------------|---------------|

| DMAxSPTR<21:0> | DMAxSSA<21:0> |

| DMAxSCNT<11:0> | DMAxSSZ<11:0> |

| DMAxDPTR<15:0> | DMAxDSA<15:0> |

| DMAxDCNT<11:0> | DMAxDSZ<11:0> |

During the DMA Operation after each transaction, Table 15-4 and Table 15-5 indicate how the Source/ Destination pointer and counter registers are modified.

### TABLE 15-4: DMA SOURCE POINTER/COUNTER DURING OPERATION

| Register            | Modified Source Counter/Pointer Value |

|---------------------|---------------------------------------|

| DMAxSCNT<11:0> != 1 | DMAxSCNT = DMAxSCNT -1                |

|                     | SMODE = 00: DMAxSPTR = DMAxSPTR       |

|                     | SMODE = 01: DMAxSPTR = DMAxSPTR + 1   |

|                     | SMODE = 10: DMAxSPTR = DMAxSPTR - 1   |

| DMAxSCNT<11:0> == 1 | DMAxSCNT = DMAxSSZ                    |

|                     | DMAxSPTR = DMAxSSA                    |

### TABLE 15-5: DMA DESTINATION POINTER/COUNTER DURING OPERATION

| Register            | Modified Destination Counter/Pointer Value |

|---------------------|--------------------------------------------|

| DMAxDCNT<11:0>!= 1  | DMAxDCNT = DMAxDCNT -1                     |

|                     | DMODE = 00: DMAxDPTR = DMAxDPTR            |

|                     | DMODE = 01: DMAxDPTR = DMAxDPTR + 1        |

|                     | DMODE = 10: DMAxDPTR = DMAxDPTR - 1        |

| DMAxDCNT<11:0> == 1 | DMAxDCNT = DMAxDSZ                         |

|                     | DMAxDPTR = DMAxDSA                         |

The following sections discuss how to initiate and terminate DMA transfers.

### 15.5.1 STARTING DMA MESSAGE TRANSFERS

The DMA can initiate data transactions by either of the following two conditions:

- 1. User software control

- 2. Hardware trigger, SIRQ

15.5.1.1 User Software Control

Software starts or stops DMA transaction by setting/ clearing the DGO bit. The DGO bit is also used to indicate whether a DMA hardware trigger has been received and a message is in progress.

- Note 1: Software start can only occur if the EN bit (DMAxCON1) is set.

- 2: If the CPU writes to the DGO bit while it is already set, there is no effect on the system, the DMA will continue to operate normally.

### 15.5.3.1 Clearing the SIRQEN bit

Clearing the SIRQEN bit (DMAxCON1 register) stops the sampling of external start interrupt triggers, hence preventing further DMA Message transfers.

An example would be a communications peripheral with a level-triggered interrupt. The peripheral will continue to request data (because its buffer is empty) even though there is no more data to be moved. Disabling the SIRQEN bit prevents the DMA from processing these requests.

### 15.5.3.2 Source/Destination Stop

The SSTP and DSTP bits (DMAxCON0 register) determine whether or not to disable the hardware triggers (SIRQEN = 0) once a DMA message has completed.

When the SSTP bit is set and the DMAxSCNT = 0, then the SIRQEN bit will be cleared. Similarly, when the DSTP bit is set and the DMAxDCNT = 0, the SIRQEN bit will be cleared.

Note: The SSTP and DSTP bits are independent functions and do not depend on each other. It is possible for a message to be stopped by either counter at message end or both counters at message end.

### **15.6 Types of Hardware Triggers**

The DMA has two different trigger inputs namely the Source trigger and the abort trigger. Each of these trigger sources is user configurable using the DMAxSIRQ and DMAxAIRQ registers.

Based on the source selected for each trigger, there are two types of requests that can be sent to the DMA.

- Edge triggers

- · Level triggers

### 15.6.1 EDGE TRIGGER REQUESTS

An Edge request occurs only once when a given module interrupt requirements are true.

### 15.6.2 LEVEL TRIGGER REQUESTS

A level request is asserted as long as the condition that causes the interrupt is true.

### 15.7 Types of Data Transfers

Based on the memory access capabilities of the DMA (See Table 15-1), the following sections discuss the different types of data movement between the Source and Destination Memory regions.

• N: 1

This type of transfer is common when sending predefined data packets (such as strings) through a single interface point (such as communications modules transmit registers).

• N: N

This type of transfer is useful for moving information out of the Program Flash or Data EEPROM to SRAM for manipulation by the CPU or other peripherals.

• 1: N

This type of transfer is common when bridging two different modules data streams together (communications bridge).

• 1: N

This type of transfer is useful for moving information from a single data source into a memory buffer (communications receive registers).

### 15.8 DMA Interrupts

Each DMA has its own set of four interrupt flags, used to indicate a range of conditions during data transfers. The interrupt flag bits can be accessed using the corresponding PIR registers (Refer to the Interrupt Section).

### 15.8.1 DMA SOURCE COUNT INTERRUPT

The DMAxSCNTIF source count interrupt flag is set every time the DMAxSCNT<11:0> reaches zero and is reloaded to its starting value.

### 15.8.2 DMA DESTINATION COUNT INTERRUPT

The DMAxDCNTIF destination count interrupt flag is set every time the DMAxDCNT<11:0> reaches zero and is reloaded to its starting value.

The DMA Source Count zero and Destination Count zero interrupts are used in conjunction to determine when to signal the CPU when the DMA Messages are completed.

### 15.8.3 ABORT INTERRUPT

The DMAxAIF abort interrupt flag is used to signal that the DMA has halted activity due to an abort signal from one of the abort sources. This is used to indicate that the transaction has been halted for some reason.

### 15.8.4 OVERRUN INTERRUPT

When the DMA receives a trigger to start a new message before the current message is completed, then the DMAxORIF Overrun interrupt flag is set.

This condition indicates that the DMA is being requested before its current transaction is finished. This implies that the active DMA may not be able to keep up with the demands from the peripheral module being serviced, which may result in data loss.

The DMAxORIF flag being set does not cause the current DMA transfer to terminate.

The Overrun interrupt is only available for trigger sources that are edge based and not available for sources that are level-based. Therefore a level-based interrupt source does not trigger a DMA overrun error due to the potential latency issues in the system.

An example of an interrupt that could use the overrun interrupt would be a timer overflow (or period match) interrupt. This event only happens every time the timer rolls over and is not dependent on any other system conditions.

An example of an interrupt that does not allow the overrun interrupt would be the UARTTX buffer. The UART will continue to assert the interrupt until the DMA is able to process the MSG. Due to latency issues, the DMA may not be able to service an empty buffer immediately, but the UART continues to assert its transmit interrupt until it is serviced. If overrun was allowed in this case, the overrun would occur almost immediately as the module samples the interrupt sources every instruction cycle.

### 15.9 DMA Setup and Operation

The following steps illustrate how to configure the DMA for data transfer:

- 1. Program the appropriate Source and Destination addresses for the transaction into the DMAxSSA and DMAxDSA registers

- Select the source memory region that is being addressed by DMAxSSA register, using the SMR<1:0> bits.

- 3. Program the SMODE and DMODE bits to select the addressing mode.

- 4. Program the Source size DMAxSSZ and Destination size DMAxDSZ registers with the number of bytes to be transferred. It is recommended for proper operation that the size registers be a multiple of each other.

- If the user desires to disable data transfers once the message has completed, then the SSTP and DSTP bits in DMAxCON0 register need to be set. (see Section 15.5.3.2 "Source/Destination Stop").

- If using hardware triggers for data transfer, setup the hardware trigger interrupt sources for the starting and aborting DMA transfers (DMAxSIRQ and DMAxAIRQ), and set the corresponding interrupt request enable bits (SIRQEN and AIRQEN).

- Select the priority level for the DMA (see Section 3.1 "System Arbitration") and lock the priorities (see Section 3.1.1 "Priority Lock")

- 8. Enable the DMA (DMAxCON1bits. EN = 1)

- 9. If using software control for data transfer, set the DGO bit, else this bit will be set by the hardware trigger.

Once the DMA is set up, the following flow chart describes the sequence of operation when the DMA uses hardware triggers and utilizes the unused CPU cycles (bubble) for DMA transfers.

## 15.9.7 ABORT TRIGGER, MESSAGE IN PROGRESS

When an abort interrupt request is received in a DMA transaction, the DMA will perform a soft-stop by clearing the DGO (i.e., if the DMA was reading the source register, it will complete the read operation and then clear the DGO bit).

The SIREQEN bit is cleared to prevent any overrun and the AIRQEN bit is cleared to prevent any false aborts.

When the DGO bit is set again the DMA will resume operation from where it left off after the soft-stop.

|                               | 0 0 0 0 0 0 0 0 0 0 0                                                              | Rav. 10-001275G<br>8/12/2016 |

|-------------------------------|------------------------------------------------------------------------------------|------------------------------|

| Instruction<br>Clock          |                                                                                    |                              |

| EN                            |                                                                                    |                              |

| SIRQEN                        |                                                                                    |                              |

| AIRQEN                        |                                                                                    |                              |

| Source Hardware<br>Trigger —— |                                                                                    |                              |

| Abort Hardware<br>Trigger     |                                                                                    |                              |

| DGO                           |                                                                                    |                              |

| DMAxSPTR <                    | 0x3EEF 0x3EF0 0x3EF0 0x3EEF                                                        |                              |

| DMAxDPTR                      | 0x100 0x101 0x102                                                                  |                              |

|                               | 2 1 2                                                                              |                              |

|                               | 10 9 8                                                                             |                              |

| DMA STATE                     | $IDLE$ $SR^{(1)}$ $IDLE$ $DW^{(2)}$ $SR^{(1)}$ $DW^{(2)}$ $IDLE$ $DW^{(2)}$ $IDLE$ |                              |

| DMAxCONbits.XIP               |                                                                                    |                              |

| DMAxAIF ——                    |                                                                                    |                              |

| DMAxSSA                       | 0x3EEF DMAxDSA 0x100                                                               |                              |

|                               |                                                                                    |                              |

| DMAxSSZ                       | 0x2 DMAxDSZ 0xA                                                                    |                              |

| Note 1: SR - So               |                                                                                    |                              |

| <b>2:</b> DW - De             | estination Write                                                                   |                              |

The following table contains some of the cases in which the DMA module can be configured to.

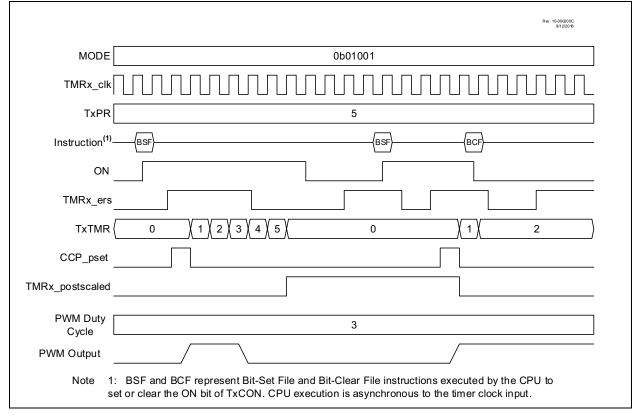

### 22.5.6 EDGE-TRIGGERED ONE-SHOT MODE

The Edge-Triggered One-Shot modes start the timer on an edge from the external signal input, after the ON bit is set, and clear the ON bit when the timer matches the T2PR period value. The following edges will start the timer:

- Rising edge (MODE<4:0> = 01001)

- Falling edge (MODE<4:0> = 01010)

- Rising or Falling edge (MODE<4:0>='01011')

If the timer is halted by clearing the ON bit then another TMRx\_ers edge is required after the ON bit is set to resume counting. Figure 22-9 illustrates operation in the rising edge One-Shot mode.

When Edge-Triggered One-Shot mode is used in conjunction with the CCP then the edge-trigger will activate the PWM drive and the PWM drive will deactivate when the timer matches the CCPRx pulse width value and stay deactivated when the timer halts at the T2PR period count match.

### FIGURE 22-9: EDGE TRIGGERED ONE-SHOT MODE TIMING DIAGRAM (MODE = 01001)

| R/W-x/u          | R/W-x/u                                                                                                                  | R/W-x/u                                                                                           | R/W-x/u             | R/W-x/u        | R/W-x/u          | R/W-x/u          | R/W-x/u     |  |

|------------------|--------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------|---------------------|----------------|------------------|------------------|-------------|--|

| G2D4T            | G2D4N                                                                                                                    | G2D3T                                                                                             | G2D3N               | G2D2T          | G2D2N            | G2D1T            | G2D1N       |  |

| bit 7            | 1                                                                                                                        |                                                                                                   | ·                   | •              |                  |                  | bit         |  |

| Legend:          |                                                                                                                          |                                                                                                   |                     |                |                  |                  |             |  |

| R = Readable     | bit                                                                                                                      | W = Writable                                                                                      | bit                 | U = Unimpler   | mented bit, read | l as '0'         |             |  |

| u = Bit is unch  | nanged                                                                                                                   | x = Bit is unkr                                                                                   | nown                | -n/n = Value a | at POR and BO    | R/Value at all c | ther Resets |  |

| '1' = Bit is set |                                                                                                                          | '0' = Bit is cle                                                                                  | ared                |                |                  |                  |             |  |

|                  |                                                                                                                          |                                                                                                   |                     |                |                  |                  |             |  |

| bit 7            |                                                                                                                          | e 1 Data 4 True                                                                                   | . ,                 |                |                  |                  |             |  |

|                  |                                                                                                                          | (true) is gated i                                                                                 |                     |                |                  |                  |             |  |

|                  |                                                                                                                          | (true) is not gat                                                                                 |                     |                |                  |                  |             |  |

| bit 6            |                                                                                                                          | e 1 Data 4 Nega                                                                                   | •                   |                |                  |                  |             |  |

|                  |                                                                                                                          | (inverted) is ga<br>(inverted) is no                                                              |                     |                |                  |                  |             |  |

| bit 5            |                                                                                                                          |                                                                                                   | •                   |                |                  |                  |             |  |

|                  |                                                                                                                          | <b>G2D3T:</b> Gate 1 Data 3 True (noninverted) bit<br>1 = CLCIN2 (true) is gated into CLCx Gate 1 |                     |                |                  |                  |             |  |

|                  |                                                                                                                          | (true) is not gat                                                                                 |                     |                |                  |                  |             |  |

| bit 4            | G2D3N: Gat                                                                                                               | e 1 Data 3 Neg                                                                                    | ated (inverted)     | ) bit          |                  |                  |             |  |

|                  | 1 = CLCIN2                                                                                                               | (inverted) is ga                                                                                  | ted into CLCx       | Gate 1         |                  |                  |             |  |

|                  | 0 = CLCIN2                                                                                                               | (inverted) is no                                                                                  | t gated into C      | LCx Gate 1     |                  |                  |             |  |

| bit 3            | G2D2T: Gate                                                                                                              | e 1 Data 2 True                                                                                   | (noninverted)       | bit            |                  |                  |             |  |

|                  | <ul> <li>1 = CLCIN1 (true) is gated into CLCx Gate 1</li> <li>0 = CLCIN1 (true) is not gated into CLCx Gate 1</li> </ul> |                                                                                                   |                     |                |                  |                  |             |  |