#### Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

#### Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Product Status             | Active                                                                    |

|----------------------------|---------------------------------------------------------------------------|

| Core Processor             | PIC                                                                       |

| Core Size                  | 8-Bit                                                                     |

| Speed                      | 64MHz                                                                     |

| Connectivity               | I <sup>2</sup> C, LINbus, SPI, UART/USART                                 |

| Peripherals                | Brown-out Detect/Reset, DMA, HLVD, POR, PWM, WDT                          |

| Number of I/O              | 36                                                                        |

| Program Memory Size        | 32KB (16K x 16)                                                           |

| Program Memory Type        | FLASH                                                                     |

| EEPROM Size                | 256 x 8                                                                   |

| RAM Size                   | 2K x 8                                                                    |

| Voltage - Supply (Vcc/Vdd) | 2.3V ~ 5.5V                                                               |

| Data Converters            | A/D 35x12b; D/A 1x5b                                                      |

| Oscillator Type            | Internal                                                                  |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                         |

| Mounting Type              | Through Hole                                                              |

| Package / Case             | 40-DIP (0.600", 15.24mm)                                                  |

| Supplier Device Package    | 40-PDIP                                                                   |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/pic18f45k42-i-p |

|                            |                                                                           |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

#### 4.5.2 GENERAL PURPOSE REGISTER FILE

General Purpose RAM is available starting Bank 0 of data memory. GPRs are not initialized by a Power-on Reset and are unchanged on all other Resets.

#### 4.5.3 SPECIAL FUNCTION REGISTERS

The Special Function Registers (SFRs) are registers used by the CPU and peripheral modules for controlling the desired operation of the device. These registers are implemented as static RAM. SFRs start at the top of data memory (3FFFh) and extend downward to occupy Bank 56 through 63 (3800h to 3FFFh). A list of these registers is given in Table 4-3 to Table 4-11. A bitwise summary of these registers can be found in **Section 42.0 "Register Summary"**.

### 4.5.4 ACCESS BANK

To streamline access for the most commonly used data memory locations, the data memory is configured with an Access Bank, which allows users to access a mapped block of memory without specifying a BSR. The Access Bank consists of the first 96 bytes of memory (00h-5Fh) in Bank 0 and the last 160 bytes of memory (60h-FFh) in Bank 63. The lower half is known as the "Access RAM" and is composed of GPRs. This upper half is also where some of the SFRs of the device are mapped. These two areas are mapped contiguously in the Access Bank and can be addressed linearly by an 8-bit address (Figure 4-4).

The Access Bank is used by core PIC18 instructions that include the Access RAM bit (the 'a' parameter in the instruction). When 'a' is equal to '1', the instruction uses the BSR and the 8-bit address included in the opcode for the data memory address. When 'a' is '0', however, the instruction uses the Access Bank address map; the current value of the BSR is ignored.

Using this "forced" addressing allows the instruction to operate on a data address in a single cycle, without updating the BSR first. For 8-bit addresses of 60h and above, this means that users can evaluate and operate on SFRs more efficiently. The Access RAM below 60h is a good place for data values that the user might need to access rapidly, such as immediate computational results or common program variables. Access RAM also allows for faster and more code efficient and switching of variables.

The mapping of the Access Bank is slightly different when the extended instruction set is enabled (XINST Configuration bit = 1). This is discussed in more detail in Section 4.8.3 "Mapping the Access Bank in Indexed Literal Offset Mode".

### 6.14 Register Definitions: Power Control

#### REGISTER 6-2: PCON0: POWER CONTROL REGISTER 0

| R/W/HS-0/q | R/W/HS-0/q | R/W/HC-1/q | R/W/HC-1/q | R/W/HC-1/q | R/W/HC-1/q | R/W/HC-0/u | R/W/HC-q/u |

|------------|------------|------------|------------|------------|------------|------------|------------|

| STKOVF     | STKUNF     | WDTWV      | RWDT       | RMCLR      | RI         | POR        | BOR        |

| bit 7      |            |            |            |            |            |            | bit 0      |

| Legend:          |                                                                                                                                                                                                                                                                                             |                          |                                                                                                     |  |  |  |  |

|------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------|-----------------------------------------------------------------------------------------------------|--|--|--|--|

| HC = Bit is cle  | ared by hardware                                                                                                                                                                                                                                                                            |                          | HS = Bit is set by hardware                                                                         |  |  |  |  |

| R = Readable     | bit W =                                                                                                                                                                                                                                                                                     | Writable bit             | U = Unimplemented bit, read as '0'                                                                  |  |  |  |  |

| u = Bit is unch  | anged x = E                                                                                                                                                                                                                                                                                 | Bit is unknown           | -m/n = Value at POR and BOR/Value at all other Resets                                               |  |  |  |  |

| '1' = Bit is set | "O' =                                                                                                                                                                                                                                                                                       | Bit is cleared           | q = Value depends on condition                                                                      |  |  |  |  |

|                  |                                                                                                                                                                                                                                                                                             |                          |                                                                                                     |  |  |  |  |

| bit 7            |                                                                                                                                                                                                                                                                                             | •                        | LLs than fit on the stack)<br>r set to '0' by firmware                                              |  |  |  |  |

| bit 6            |                                                                                                                                                                                                                                                                                             | erflow occurred (more I  | RETURN <b>s than</b> CALL <b>S)</b><br>or set to '0' by firmware                                    |  |  |  |  |

| bit 5            | <ul> <li>WDTWV: Watchdog Window Violation bit</li> <li>1 = A WDT window violation has not occurred or set to '1' by firmware</li> <li>0 = A CLRWDT instruction was issued when the WDT Reset window was closed (set to '0' in hardware when a WDT window violation Reset occurs)</li> </ul> |                          |                                                                                                     |  |  |  |  |

| bit 4            |                                                                                                                                                                                                                                                                                             | ow/time-out Reset has    | not occurred or set to '1' by firmware<br>occurred (set to '0' in hardware when a WDT Reset occurs) |  |  |  |  |

| bit 3            |                                                                                                                                                                                                                                                                                             | et has not occurred or s | set to '1' by firmware<br>'0' in hardware when a MCLR Reset occurs)                                 |  |  |  |  |

| bit 2            |                                                                                                                                                                                                                                                                                             | ruction has not been ex  | ecuted or set to '1' by firmware<br>ecuted (set to '0' in hardware upon executing a RESET           |  |  |  |  |

| bit 1            | <b>POR</b> : Power-on Re<br>1 = No Power-on                                                                                                                                                                                                                                                 | Reset occurred or set t  | to '1' by firmware<br>)' in hardware when a Power-on Reset occurs)                                  |  |  |  |  |

| bit 0            |                                                                                                                                                                                                                                                                                             | t Reset occurred or set  | to ʻ1' by firmware<br>0' in hardware when a Brown-out Reset occurs)                                 |  |  |  |  |

#### 7.4.4 RESET OR WAKE-UP FROM SLEEP

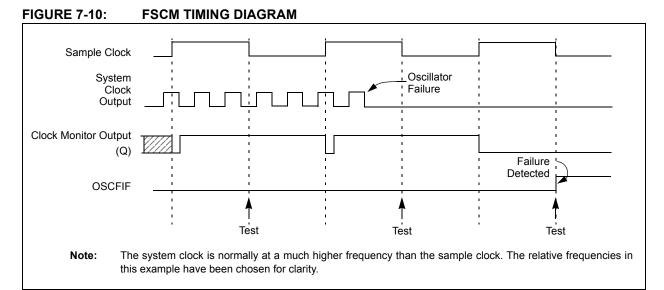

The FSCM is designed to detect an oscillator failure after the Oscillator Start-up Timer (OST) has expired. The OST is used after waking up from Sleep and after any type of Reset. The OST is not used with the EC Clock modes so that the FSCM will be active as soon as the Reset or wake-up has completed.

#### TABLE 7-1: NOSC/COSC AND NDIV/CDIV BIT SETTINGS

| NOSC<2:0><br>COSC<2:0> | Clock Source                   | NDIV<<br>CDIV< |      | Clock Divider |

|------------------------|--------------------------------|----------------|------|---------------|

| 111                    | EXTOSC <sup>(1)</sup>          | 1111-          | 1010 | Reserved      |

| 110                    | HFINTOSC <sup>(2)</sup>        | 100            | 01   | 512           |

| 101                    | LFINTOSC                       | 100            | 00   | 256           |

| 100                    | SOSC                           | 011            | 11   | 128           |

| 011                    | Reserved                       | 011            | 10   | 64            |

| 010                    | EXTOSC + 4x PLL <sup>(3)</sup> | 010            | 01   | 32            |

| 001                    | Reserved                       | 010            | 00   | 16            |

| 000                    | Reserved                       | 001            | 11   | 8             |

|                        |                                | 001            | 10   | 4             |

|                        |                                | 000            | 01   | 2             |

0000

Note 1: EXTOSC configured by the FEXTOSC bits of Configuration Word 1 (Register 5-1).

- 2: HFINTOSC frequency is set with the FRQ bits of the OSCFRQ register (Register 7-5).

- **3:** EXTOSC must meet the PLL specifications (Table 44-11).

1

| R-0/0               | R/W/HS-0/0                                   | R/W/HS-0/0                        | R/W/HS-0/0      | R/W/HS-0/0           | R/W/HS-0/0       | R/W/HS-0/0        | R/W/HS-0/0   |

|---------------------|----------------------------------------------|-----------------------------------|-----------------|----------------------|------------------|-------------------|--------------|

| IOCIF <sup>(2</sup> | ) CRCIF                                      | SCANIF                            | NVMIF           | CSWIF <sup>(3)</sup> | OSFIF            | HLVDIF            | SWIF         |

| bit 7               |                                              |                                   |                 |                      |                  |                   | bit 0        |

|                     |                                              |                                   |                 |                      |                  |                   |              |

| Legend:             |                                              |                                   |                 |                      |                  |                   |              |

| R = Reada           |                                              | W = Writable                      |                 | •                    | nented bit, read |                   |              |

| u = Bit is u        | •                                            | x = Bit is unkr                   |                 |                      | at POR and BO    | R/Value at all c  | other Resets |

| '1' = Bit is s      | set                                          | '0' = Bit is clea                 | ared            | HS = BIt IS SE       | et in hardware   |                   |              |

| bit 7               | IOCIF: Interru                               | pt-on-Change                      | Interrupt Flag  | bit( <b>2</b> )      |                  |                   |              |

| Sit 1               | 1 = Interrupt                                |                                   | interrupt r lag | bit                  |                  |                   |              |

|                     | 0 = Interrupt                                | event has not o                   | occurred        |                      |                  |                   |              |

| bit 6               | CRCIF: CRC                                   | Interrupt Flag                    | oit             |                      |                  |                   |              |

|                     |                                              | has occurred (                    |                 | ed by software       | )                |                   |              |

| bit E               | •                                            | event has not o                   |                 | -:+                  |                  |                   |              |

| bit 5               |                                              | nory Scanner I<br>has occurred (  |                 |                      | )                |                   |              |

|                     |                                              | event has not o                   |                 | cu by soltware       | )                |                   |              |

| bit 4               | NVMIF: NVM                                   | Interrupt Flag                    | bit             |                      |                  |                   |              |

|                     |                                              | has occurred (                    |                 | ed by software       | )                |                   |              |

|                     | -                                            | event has not o                   |                 |                      |                  |                   |              |

| bit 3               |                                              | c Switch Interru                  |                 |                      | ,                |                   |              |

|                     | •                                            | has occurred (<br>event has not o |                 | ed by software       | )                |                   |              |

| bit 2               | •                                            | ator Fail Interru                 |                 |                      |                  |                   |              |

|                     |                                              | has occurred (                    |                 | ed by software       | )                |                   |              |

|                     | 0 = Interrupt                                | event has not o                   | occurred        |                      |                  |                   |              |

| bit 1               |                                              | D Interrupt Fla                   | -               |                      |                  |                   |              |

|                     |                                              | has occurred (<br>event has not o |                 | ed by software       | )                |                   |              |

| bit 0               | •                                            | re Interrupt Fla                  |                 |                      |                  |                   |              |

| bit 0               |                                              | Interrupt Flag                    | -               |                      |                  |                   |              |

|                     |                                              | Interrupt Flag                    |                 |                      |                  |                   |              |

|                     | Interrupt flag bits g                        |                                   |                 |                      |                  |                   |              |

|                     | enable bit, or the g<br>clear prior to enabl |                                   |                 | re should ensu       | ire the appropri | ate interrupt fla | ig bits are  |

|                     | IOCIF is a read-on                           | •                                 |                 | ondition, all bit    | s in the IOCxF   | registers must    | be cleared.  |

|                     | The CSWIF interru                            | 5                                 | •               | •                    |                  | 0                 |              |

|                     | causes the wake-u                            | •                                 | -               | ·                    | -                | -                 |              |

### REGISTER 9-3: PIR0: PERIPHERAL INTERRUPT REQUEST REGISTER 0

| R/W-0/0          | R/W-0/0                                           | R/W-0/0           | U-0            | R/W-0/0        | R/W-0/0          | R/W-0/0          | R/W-0/0     |

|------------------|---------------------------------------------------|-------------------|----------------|----------------|------------------|------------------|-------------|

| CLC1IE           | CWG1IE                                            | NCO1IE            | _              | CCP1IE         | TMR2IE           | TMR1GIE          | TMR1IE      |

| bit 7            |                                                   |                   |                |                |                  |                  | bit         |

|                  |                                                   |                   |                |                |                  |                  |             |

| Legend:          |                                                   |                   |                |                |                  |                  |             |

| R = Readable     |                                                   | W = Writable      |                | •              | nented bit, read |                  |             |

| u = Bit is unch  | •                                                 | x = Bit is unkr   |                | -n/n = Value a | at POR and BC    | R/Value at all o | ther Resets |

| '1' = Bit is set |                                                   | '0' = Bit is clea | ared           |                |                  |                  |             |

| bit 7            | CLC1IE: CI (                                      | C1 Interrupt Ena  | able bit       |                |                  |                  |             |

|                  | 1 = Enabled<br>0 = Disabled                       |                   |                |                |                  |                  |             |

| bit 6            | <b>CWG1IE:</b> CV<br>1 = Enabled<br>0 = Disabled  | VG1 Interrupt E   | nable bit      |                |                  |                  |             |

| bit 5            | NCO1IE: NC<br>1 = Enabled<br>0 = Disabled         | O1 Interrupt En   | able bit       |                |                  |                  |             |

| bit 4            | Unimplemen                                        | ted: Read as '    | )'             |                |                  |                  |             |

| bit 3            | <b>CCP1IE:</b> CCI<br>1 = Enabled<br>0 = Disabled | P1 Interrupt En   | able bit       |                |                  |                  |             |

| bit 2            | <b>TMR2IE:</b> TM<br>1 = Enabled<br>0 = Disabled  | R2 Interrupt En   | able bit       |                |                  |                  |             |

| bit 1            | <b>TMR1GIE:</b> TI<br>1 = Enabled<br>0 = Disabled | MR1 Gate Inter    | rupt Enable bi | t              |                  |                  |             |

| bit 0            | TMR1IE: TM<br>1 = Enabled<br>0 = Disabled         | R1 Interrupt En   | able bit       |                |                  |                  |             |

#### REGISTER 9-18: PIE4: PERIPHERAL INTERRUPT ENABLE REGISTER 4

| R/W-1/1         | R/W-1/1                                                         | R/W-1/1             | R/W-1/1          | R/W-1/1        | R/W-1/1          | R/W-1/1          | R/W-1/1     |  |  |

|-----------------|-----------------------------------------------------------------|---------------------|------------------|----------------|------------------|------------------|-------------|--|--|

| IOCIP           | CRCIP                                                           | SCANIP              | NVMIP            | CSWIP          | OSFIP            | HLVDIP           | SWIP        |  |  |

| bit 7           |                                                                 |                     |                  |                |                  |                  | bit         |  |  |

|                 |                                                                 |                     |                  |                |                  |                  |             |  |  |

| Legend:         |                                                                 |                     |                  |                |                  | (0)              |             |  |  |

| R = Readable    |                                                                 | W = Writable        |                  | •              | mented bit, read |                  |             |  |  |

| u = Bit is unc  | •                                                               | x = Bit is unk      |                  | -n/n = value a | at POR and BO    | R/value at all c | iner Resets |  |  |

| '1' = Bit is se | t                                                               | '0' = Bit is cle    | ared             |                |                  |                  |             |  |  |

| bit 7           | IOCIP: Inter                                                    | rupt-on-Change      | Priority bit     |                |                  |                  |             |  |  |

|                 | 1 = High priority                                               |                     |                  |                |                  |                  |             |  |  |

|                 | 0 = Low price                                                   | ority               |                  |                |                  |                  |             |  |  |

| bit 6           | CRCIP: CR                                                       | C Interrupt Prior   | ity bit          |                |                  |                  |             |  |  |

|                 | 1 = High priority                                               |                     |                  |                |                  |                  |             |  |  |

|                 | 0 = Low priority                                                |                     |                  |                |                  |                  |             |  |  |

| oit 5           | SCANIP: Memory Scanner Interrupt Priority bit                   |                     |                  |                |                  |                  |             |  |  |

|                 | <ul> <li>1 = High priority</li> <li>0 = Low priority</li> </ul> |                     |                  |                |                  |                  |             |  |  |

| bit 4           | NVMIP: NVM Interrupt Priority bit                               |                     |                  |                |                  |                  |             |  |  |

|                 |                                                                 | 1 = High priority   |                  |                |                  |                  |             |  |  |

|                 | 0 = Low priority                                                |                     |                  |                |                  |                  |             |  |  |

| bit 3           | CSWIP: Clo                                                      | ck Switch Interr    | upt Priority bit |                |                  |                  |             |  |  |

|                 | 1 = High pri                                                    | ,                   |                  |                |                  |                  |             |  |  |

|                 | 0 = Low price                                                   | ority               |                  |                |                  |                  |             |  |  |

| bit 2           |                                                                 | illator Fail Interr | upt Priority bit | :              |                  |                  |             |  |  |

|                 | 1 = High pri                                                    |                     |                  |                |                  |                  |             |  |  |

| L:1 4           | 0 = Low priority                                                |                     |                  |                |                  |                  |             |  |  |

| bit 1           | HLVDIP: HLVD Interrupt Priority bit                             |                     |                  |                |                  |                  |             |  |  |

|                 | 1 = High priority<br>0 = Low priority                           |                     |                  |                |                  |                  |             |  |  |

| bit 0           | SWIP: Software Interrupt Priority bit                           |                     |                  |                |                  |                  |             |  |  |

|                 | 1 = High pri                                                    |                     | <b>,</b> -       |                |                  |                  |             |  |  |

|                 | 0 = Low price                                                   | -                   |                  |                |                  |                  |             |  |  |

#### REGISTER 9-25: IPR0: PERIPHERAL INTERRUPT PRIORITY REGISTER 0

#### FIGURE 10-2: WAKE-UP FROM SLEEP THROUGH INTERRUPT

| Q1 Q2 Q3 Q4 Q1 Q2 Q3 Q4 Q1                         | 01/02/03/04         |                    | Q3 Q4 Q1 Q2 Q3 Q4   |

|----------------------------------------------------|---------------------|--------------------|---------------------|

|                                                    |                     |                    |                     |

|                                                    | Tost <sup>(3)</sup> | ·/                 |                     |

| Interrupt flag                                     | / Interrupt Late    | ncy <sup>(4)</sup> |                     |

| GIE bit<br>(INTCON reg.)<br>Sleet                  |                     | <u>.</u>           |                     |

| Instruction Flow<br>PC X PC X PC + 1 X             | PC + 2 X PC + 2     | PC+2 00            | 004h X 0005h        |

| Instruction { Inst(PC) = Sleep Inst(PC + 1)        | Inst(PC + 2)        | Inst               | (0004h) Inst(0005h) |

| Instruction { Inst(PC - 1) Sleep                   | Inst(PC + 1)        | Forced NOP Force   | ed NOP Inst(0004h)  |

| Note 1: External clock. High, Medium, Low mode ass | umed.               |                    |                     |

2: CLKOUT is shown here for timing reference.

3: TOST = 1024 TOSC. This delay does not apply to EC and INTOSC Oscillator modes.

4: GIE = 1 assumed. In this case after wake-up, the processor calls the ISR at 0004h. If GIE = 0, execution will continue in-line.

#### 10.2.3 LOW-POWER SLEEP MODE

The PIC18F26/27/45/46/47/55/56/57K42 device family contains an internal Low Dropout (LDO) voltage regulator, which allows the device I/O pins to operate at voltages up to 5.5V while the internal device logic operates at a lower voltage. The LDO and its associated reference circuitry must remain active when the device is in Sleep mode.

The PIC18F26/27/45/46/47/55/56/57K42 devices allow the user to optimize the operating current in Sleep, depending on the application requirements.

Low-Power Sleep mode can be selected by setting the VREGPM bit of the VREGCON register.

#### 10.2.3.1 Sleep Current vs. Wake-up Time

In the default operating mode, the LDO and reference circuitry remain in the normal configuration while in Sleep. The device is able to exit Sleep mode quickly since all circuits remain active. In Low-Power Sleep mode, when waking-up from Sleep, an extra delay time is required for these circuits to return to the normal configuration and stabilize.

The Low-Power Sleep mode is beneficial for applications that stay in Sleep mode for long periods of time. The Normal mode is beneficial for applications that need to wake from Sleep quickly and frequently.

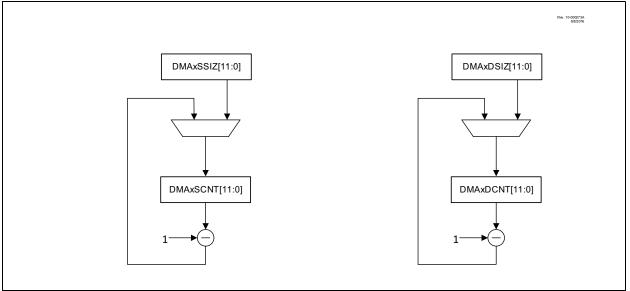

#### FIGURE 15-3: DMA COUNTERS BLOCK DIAGRAM

Table 15-2 has a few examples of configuring DMAMessage sizes.

| TABLE 15-2: EXAMPLE MESSAGE SIZE TABLE |        |     |         |      |      |  |  |

|----------------------------------------|--------|-----|---------|------|------|--|--|

|                                        | Operat | ion | Example | SCNT | DONT |  |  |

| Operation                                | Example           | SCNT | DCNT | Comments                                                                                  |

|------------------------------------------|-------------------|------|------|-------------------------------------------------------------------------------------------|

| Read from single SFR<br>location to RAM  | U1RXB             | 1    | Ν    | N equals the number of bytes desired in the destination buffer. N >= 1.                   |

| Write to single SFR location<br>from RAM | U1TXB             | N    | 1    | N equals the number of bytes desired in the source buffer. N >= 1.                        |

|                                          | ADRES[H:L]        | 2    | 2*N  | N equals the number of ADC results to be stored in memory. N>= 1                          |

| Read from multiple SFR location          | TMR1[H:L]         | 2    | 2*N  | N equals the number of TMR1 Acquisition results to be stored in memory. N>= 1             |

|                                          | SMT1CPR[U:H:L]    | 3    | 3*N  | N equals the number of Capture Pulse Width measurements to be stored in memory. N>= 1     |

| Write to Multiple SFR regis-             | PWMDC[H:L]        | 2*N  | 2    | N equals the number of PWM duty cycle val-<br>ues to be loaded from a memory table. N>= 1 |

| ters                                     | All ADC registers | N*31 | 31   | Using the DMA to transfer a complete ADC context from RAM to the ADC registers.N>= 1      |

x = bit is unknown u = bit is unchanged

| REGISTER 15-1: DMAXCON0: DMAX CONTROL REGISTER 0 |            |               |             |                  |            |     |             |  |  |

|--------------------------------------------------|------------|---------------|-------------|------------------|------------|-----|-------------|--|--|

| R/W-0/0                                          | R/W/HC-0/0 | R/W/HS/HC-0/0 | U-0         | U-0              | R/W/HC-0/0 | U-0 | R/HS/HC-0/0 |  |  |

| EN                                               | SIRQEN     | DGO           | _           | _                | AIRQEN     | _   | XIP         |  |  |

| bit 7                                            |            |               |             |                  |            |     | bit 0       |  |  |

|                                                  |            |               |             |                  |            |     |             |  |  |

| Legend:                                          |            |               |             |                  |            |     |             |  |  |

| R = Readable bit W = Writable bit                |            |               | U = Unimple | mented bit, read | d as '0'   |     |             |  |  |

| -n/n = Value at POR  | 0 = bit is cleared |   |

|----------------------|--------------------|---|

| and BOR/Value at all |                    | I |

| other Resets         |                    |   |

|                      |                    |   |

| bit 7 EN: DMA Module Enable b | oit |

|-------------------------------|-----|

|-------------------------------|-----|

- 1 = Enables module

- 0 = Disables module

- SIRQEN: Start of Transfer Interrupt Request Enable bits

- 1 = Hardware triggers are allowed to start DMA transfers

- 0 = Hardware triggers are not allowed to start DMA transfers

#### bit 5 DGO: DMA transaction bit

bit 6

- 1 = DMA transaction is in progress

- 0 = DMA transaction is not in progress

- bit 4-3 Unimplemented: Read as '0'

#### bit 2 AIRQEN: Abort of Transfer Interrupt Request Enable bits

- 1 = Hardware triggers are allowed to abort DMA transfers

- 0 = Hardware triggers are not allowed to abort DMA transfers

#### bit 1 Unimplemented: Read as '0'

- bit 0 XIP: Transfer in Progress Status bit

- 1 = The DMAxBUF register currently holds contents from a read operation and has not transferred data to the destination.

- 0 = The DMAxBUF register is empty or has successfully transferred data to the destination address

| Name   | Bit 7                                              | Bit 6         | Bit 5        | Bit 4         | Bit 3           | Bit 2      | Bit 1      | Bit 0 | Reset<br>Values<br>on<br>Page |

|--------|----------------------------------------------------|---------------|--------------|---------------|-----------------|------------|------------|-------|-------------------------------|

| TxCON  |                                                    |               | CKPS         | <1:0>         |                 | SYNC       | RD16       | ON    | 313                           |

| TxGCON | GE                                                 | GPOL          | GTM          | GSPM          | GO/DONE         | GVAL       | _          | _     | 314                           |

| TxCLK  | —                                                  | —             | _            |               | (               | CS<4:0>    |            |       | 315                           |

| TxGATE | —                                                  | _             | _            | GSS<4:0>      |                 |            |            |       |                               |

| TMRxL  | Least Significant Byte of the 16-bit TMR3 Register |               |              |               |                 |            |            | 317   |                               |

| TMRxH  | Ho                                                 | Iding Registe | r for the Mo | ost Significa | ant Byte of the | 16-bit TMR | 3 Register |       | 317                           |

#### TABLE 21-3: SUMMARY OF REGISTERS ASSOCIATED WITH TIMER1/3/5 AS A TIMER/COUNTER

Legend: — = Unimplemented location, read as '0'. Shaded cells are not used by TIMER1/3/5.

### 23.2 Capture Mode

Capture mode makes use of the 16-bit Timer1 resource. When an event occurs on the capture source, the 16-bit CCPRxH:CCPRxL register pair captures and stores the 16-bit value of the TMRxH:TMRxL register pair, respectively. An event is defined as one of the following and is configured by the MODE<3:0> bits of the CCPxCON register:

- · Every falling edge of CCPx input

- Every rising edge of CCPx input

- Every 4th rising edge of CCPx input

- · Every 16th rising edge of CCPx input

- Every edge of CCPx input (rising or falling)

When a capture is made, the Interrupt Request Flag bit CCPxIF of the respective PIR register is set. The interrupt flag must be cleared in software. If another capture occurs before the value in the CCPRxH:CCPRxL register pair is read, the old captured value is overwritten by the new captured value.

Note: If an event occurs during a 2-byte read, the high and low-byte data will be from different events. It is recommended while reading the CCPRxH:CCPRxL register pair to either disable the module or read the register pair twice for data integrity.

Figure 23-1 shows a simplified diagram of the capture operation.

#### 23.2.1 CAPTURE SOURCES

In Capture mode, the CCPx pin should be configured as an input by setting the associated TRIS control bit.

| Note: | If the CCPx pin is configured as an output, |

|-------|---------------------------------------------|

|       | a write to the port can cause a capture     |

|       | condition.                                  |

The capture source is selected by configuring the CTS<2:0> bits of the CCPxCAP register. Refer to CCPxCAP register (Register 23-3) for a list of sources that can be selected.

#### 23.2.2 TIMER1 MODE RESOURCE

Timer1 must be running in Timer mode or Synchronized Counter mode for the CCP module to use the capture feature. In Asynchronous Counter mode, the capture operation may not work.

• See Section 21.0 "Timer1/3/5 Module with Gate Control" for more information on configuring Timer1.

Note: Clocking Timer1 from the system clock (Fosc) should not be used in Capture mode. In order for Capture mode to recognize the trigger event on the CCPx pin, Timer1 must be clocked from the instruction clock (Fosc/4) or from an external clock source.

| Name     | Bit 7 | Bit 6           | Bit 5 | Bit 4 | Bit 3                      | Bit 2     | Bit 1     | Bit 0 | Register on Page |  |

|----------|-------|-----------------|-------|-------|----------------------------|-----------|-----------|-------|------------------|--|

| SMT1CON0 | EN    | —               | STP   | WPOL  | WPOL SPOL CPOL SMT1PS<1:0> |           |           |       |                  |  |

| SMT1CON1 | GO    | REPEAT          | _     | _     | — MODE<3:0>                |           |           |       |                  |  |

| SMT1STAT | CPRUP | CPWUP           | RST   | _     | _                          | TS        | WS        | AS    | 396              |  |

| SMT1CLK  | _     |                 | _     | _     | _                          | (         | CSEL<2:0> |       | 397              |  |

| SMT1SIG  | _     |                 |       |       |                            | SSEL<4:0> |           |       | 399              |  |

| SMT1WIN  | _     | — — — WSEL<4:0> |       |       |                            |           |           |       | 398              |  |

| SMT1TMRL |       | TMR<7:0>        |       |       |                            |           |           |       |                  |  |

| SMT1TMRH |       | TMR<15:8>       |       |       |                            |           |           |       |                  |  |

| SMT1TMRU |       |                 |       | TMR<2 | 23:16>                     |           |           |       | 400              |  |

| SMT1CPRL |       |                 |       | CPR<  | :7:0>                      |           |           |       | 401              |  |

| SMT1CPRH |       |                 |       | CPR<  | 15:8>                      |           |           |       | 401              |  |

| SMT1CPRU |       |                 |       | CPR<2 | 3:16>                      |           |           |       | 401              |  |

| SMT1CPWL |       |                 |       | CPW<  | <7:0>                      |           |           |       | 402              |  |

| SMT1CPWH |       |                 |       | CPW<  | 15:8>                      |           |           |       | 402              |  |

| SMT1CPWU |       | CPW<23:16>      |       |       |                            |           |           |       |                  |  |

| SMT1PRL  |       | PR<7:0>         |       |       |                            |           |           |       |                  |  |

| SMT1PRH  |       | PR<15:8>        |       |       |                            |           |           |       |                  |  |

| SMT1PRU  |       |                 |       | PR<2  | 3:16>                      |           |           |       | 403              |  |

#### TABLE 25-3: SUMMARY OF REGISTERS ASSOCIATED WITH SMT1

**Legend:** -= unimplemented read as '0'. Shaded cells are not used for SMT1 module.

#### 33.4.3 SLAVE OPERATION IN 7-BIT ADDRESSING MODE

The 8th bit in an address byte transmitted by the master is used to determine if the Master wants to read from or write to the Slave device. If set, it denotes that the Master wants to read from the slave and if cleared it means the master wants to write to the slave device. If there is an address match, the R/W bit is copied to the R/W bit of the I2CxSTAT0 register.

### 33.4.3.1 Slave Reception (7-bit Addressing Mode)

This section describes the sequence of events for the  $I^2C$  module configured as an  $I^2C$  slave in 7-bit Addressing mode and is receiving data. Figure 33-6, Figure 33-7, and Figure 33-8 are used as a visual reference for this description.

- Master asserts Start condition (can also be a restart) on the bus. Start condition Interrupt Flag (SCIF) in I2CxPIR register is set.

- 2. If Start condition interrupt is enabled (SCIE bit is set), generic interrupt I2CxIF is set.

- 3. Master transmits eight bits 7-bit address and R/W = 0.

- Received address is compared with the values in I2CxADR0/I2CxADR1/I2CxADR2/I2CxADR3 registers. Refer to section Section 33.4.1 "Slave Addressing Modes" for slave addressing modes.

- 5. If address matches; SMA in I2CxSTAT0 register is set, R/W is copied to R/W bit, D/A bit is cleared. If the address does not match; module becomes idle.

- 6. The matched address data is loaded into I2CxADB0 and ADRIF in I2CxPIR register is set.

- If Address hold interrupt is enabled (ADRIE = 1), CSTR is set. I2CxIF is set. Slave software can read address from I2CxADB0 and set/clear ACKDT before releasing SCL.

- If there are any previous error conditions, e.g., Receive buffer overflow or transmit buffer underflow errors, Slave will force a NACK and the module becomes idle.

- 9. ACKDT value is copied out to SDA for ACK pulse to be read by the Master on the 9th SCL pulse.

- If the Acknowledge interrupt and hold is enabled (ACKTIE = 1), CSTR is set, I2CxIF is set, then Slave software can read address from I2CxADB0 register and change the value of ACKDT before releasing SCL by clearing CSTR.

- 11. Master sends first seven SCL pulses of the data byte or a Stop condition (in the case of NACK).

- 12. If Stop condition; PCIF in I2CxPIR register is set, module becomes idle.

- If the receive buffer is full from the previous transaction i.e. RXBF = 1 (I2CxRXIF = 1), CSTR is set. Slave software must read data out of I2CxRXB to resume communication.

- 14. Master sends 8th SCL pulse of the data byte. D/ A bit is set, WRIF is set.

- 15. I2CxRXB is loaded with new data, RXBF bit is set, I2CxRXIF is set.

- 16. If Data write interrupt and hold is enabled (WRIE = 1), CSTR is set, I2CxIF is set. Slave software can read data from I2CxRXB and set/ clear ACKDT before releasing SCL by clearing CSTR.

- 17. If I2CxCNT = 0, the ACKCNT value is output to the SDA; else, if I2CxCNT!= 0, the ACKDT value is used and the value of I2CxCNT is decremented.

- 18. The ACK value is copied out to SDA to be read by the Master on the 9th SCL pulse.

- 19. If I2CxCNT = 0, CNTIF is set.

- 20. If a NACK was sent, NACKIF is set, module becomes idle.

- 21. If ACKTIE = 1, CSTR is set, I2CxIF is set. Slave software can read data from I2CxRXB clearing RXBF, before releasing SCL by clearing CSTR.

- 22. Go to step 11.

#### 33.5.12 MASTER RECEPTION IN 10-BIT ADDRESSING MODE

This section describes the sequence of events for the  $I^2C$  module configured as an  $I^2C$  master in 10-bit Addressing mode and is receiving data. Figure 33-22 is used as a visual reference for this description.

- Master software loads high address byte in I2CxADB1 and low address byte in I2CxADB0 for write and sets restart enable (RSTEN) bit.

- 2. Master software sets START bit.

- Master hardware waits for BFRE bit to be set; then shifts out start, high address and waits for acknowledge.

- 4. If slave responds with a NACK, master hardware sends Stop and ends communication.

- 5. If slave responds with ACK, master hardware shifts out the low address.

- If the transmit buffer empty flag (TXBE) is set and I2CxCNT! = 0, the clock is stretched on 8th falling SCL edge. Allowing master software writes next data to I2CxTXB.

- Master hardware sends 9th SCL pulse for ACK from slave and loads the shift register from I2CxTXB.

- 8. If slave responds with a NACK, master hardware sends Stop and ends communication.

- If slave responds with an ACK and I2CxCNT = 0, master hardware sets MDR bit, go to Step 11.

- If slave responds with an ACK and I2CxCNT! = 0, master hardware outputs data in shift register on SDA and waits for ACK from slave. Go to step 4.

- 11. Master software loads I2CxADB0 for read, and I2CCNT with the number of bytes to be received in the current transaction.

- 12. Master software sets Start bit.

- 13. Master hardware shifts out Restart and high address with R/W = 1.

- 14. Master sends out 9th SCL pulse for ACK from Slave.

- 15. If slave responds with a NACK, master hardware sends Stop or sets MDR (RSEN bit).

- 16. If slave responds with an ACK, master hardware shifts 7 bits of data into the shift register from the slave.

- 17. If the receive buffer full flag (RXBF) is set, clock is stretched on seventh falling SCL edge.

- 18. Master software can clear clock stretching by reading the previous data in the receive buffer.

- 19. Master hardware shifts 8th bit of data into the shift register from slave and loads it into I2CxRXB.

- 20. Master software reads data from I2CxRXB register.

- 21. If I2CxCNT! = 0, master hardware clocks out ACKDT as ACK value to slave.

- 22. If I2CxCNT = 0, master hardware clocks out ACKCNT as ACK value to slave

- 23. Go to step 4.

| R/W-1  | R/W-1 | R/W-1 | R/W-1 | R/W-1 | R/W-1 | R/W-1 | U-0   |

|--------|-------|-------|-------|-------|-------|-------|-------|

| 40044  | 40040 |       | 40044 | 40040 | 4000  | 4000  |       |

| ADR14  | ADR13 | ADR12 | ADR11 | ADR10 | ADR9  | ADR8  | —     |

| bit 15 |       |       |       |       |       |       | bit 8 |

| R/W-1  | R/W-1 | R/W-1 | R/W-1 | R/W-1 | R/W-1 | R/W-1 | U-0   |

| ADR7   | ADR6  | ADR5  | ADR4  | ADR3  | ADR2  | ADR1  | _     |

| bit 7  |       |       |       |       |       |       | bit 0 |

### REGISTER 33-15: I2CXADR3: I<sup>2</sup>C ADDRESS 3 REGISTER

| Legend:              |                      |                                                       |

|----------------------|----------------------|-------------------------------------------------------|

| R = Readable bit     | W = Writable bit     | U = Unimplemented bit, read as '0'                    |

| u = Bit is unchanged | x = Bit is unknown   | -n/n = Value at POR and BOR/Value at all other Resets |

| '1' = Bit is set     | '0' = Bit is cleared | HS = Hardware set HC = Hardware clear                 |

bit 7-0 ADR<7-0>: Address 3 bits

MODE<2:0> = 000 | 110 - 7-bit Slave/Multi-Master Modes

ADR<7:1>:7-bit Slave Address

ADR<0>: Unused in this mode; bit state is a don't care

MODE<2:0> = 001 | 111 - 7-bit Slave/Multi-Master Mode with Masking

MSK1<7:1>:7-bit Slave Address

MSK1<0>: Unused in this mode; bit state is a don't care

#### MODE<2:0> = 010 - 10-Bit Slave Mode

ADR<14-10>:Bit pattern sent by master is fixed by I<sup>2</sup>C specification and must be equal to '11110'. However, these bit values are compared by hardware to the received data to determine a match. It is up to the user to set these bits as '11110'

ADR<9-8>:Two Most Significant bits of 10-bit address

MODE<2:0> = 011 - 10-Bit Slave Mode with Masking

**MSK0<14-8>:**The received address byte, bit *n*, is compared to I2CxADR0 to detect I<sup>2</sup>C address match

| U-0             | U-0                                                                | U-0                                                                        | R/W-0/0        | R/W-0/0          | R/W-0/0            | R/W-0/0            | R/W-0/0 |  |  |  |  |  |  |

|-----------------|--------------------------------------------------------------------|----------------------------------------------------------------------------|----------------|------------------|--------------------|--------------------|---------|--|--|--|--|--|--|

| —               | _                                                                  | _                                                                          |                |                  | ACT<4:0>           |                    |         |  |  |  |  |  |  |

| oit 7           |                                                                    |                                                                            |                |                  |                    |                    | bit     |  |  |  |  |  |  |

|                 |                                                                    |                                                                            |                |                  |                    |                    |         |  |  |  |  |  |  |

| Legend:         |                                                                    |                                                                            |                |                  |                    |                    |         |  |  |  |  |  |  |

| R = Readabl     | e bit                                                              | W = Writable b                                                             | it             | U = Unimplem     | ented bit, read as | s 'O'              |         |  |  |  |  |  |  |

| u = Bit is und  | changed                                                            | x = Bit is unkno                                                           | own            | -n/n = Value at  | POR and BOR/       | /alue at all other | Resets  |  |  |  |  |  |  |

| '1' = Bit is se | 0                                                                  | '0' = Bit is clea                                                          | red            |                  |                    |                    |         |  |  |  |  |  |  |

|                 | -                                                                  |                                                                            |                |                  |                    |                    |         |  |  |  |  |  |  |

| bit 7-5         | Unimpleme                                                          | nted: Read as '0'                                                          |                |                  |                    |                    |         |  |  |  |  |  |  |

| bit 4-0         | •                                                                  | Unimplemented: Read as '0' ADACT<4:0>: Auto-Conversion Trigger Select Bits |                |                  |                    |                    |         |  |  |  |  |  |  |

|                 |                                                                    | served, do not use                                                         |                | 2.10             |                    |                    |         |  |  |  |  |  |  |

|                 | •                                                                  |                                                                            |                |                  |                    |                    |         |  |  |  |  |  |  |

|                 | •                                                                  |                                                                            |                |                  |                    |                    |         |  |  |  |  |  |  |

|                 | •                                                                  |                                                                            |                |                  |                    |                    |         |  |  |  |  |  |  |

|                 |                                                                    | served, do not use                                                         |                |                  |                    |                    |         |  |  |  |  |  |  |

|                 |                                                                    | ftware write to ADF                                                        |                |                  |                    |                    |         |  |  |  |  |  |  |

|                 |                                                                    | served, do not use                                                         |                |                  |                    |                    |         |  |  |  |  |  |  |

|                 | 11011 = Software read of ADRESH<br>11010 = Software read of ADERRH |                                                                            |                |                  |                    |                    |         |  |  |  |  |  |  |

|                 | 11010 = Software read of ADERRH<br>11001 = CLC4_out                |                                                                            |                |                  |                    |                    |         |  |  |  |  |  |  |

|                 | 11000 <b>= CL</b>                                                  | —                                                                          |                |                  |                    |                    |         |  |  |  |  |  |  |

|                 |                                                                    | —                                                                          |                |                  |                    |                    |         |  |  |  |  |  |  |

|                 |                                                                    | 10111 = CLC2_out<br>10110 = CLC1_out                                       |                |                  |                    |                    |         |  |  |  |  |  |  |

|                 |                                                                    | gical OR of all Inter                                                      | runt-on-change | Interrupt Flags  |                    |                    |         |  |  |  |  |  |  |

|                 | 10100 = CN                                                         | -                                                                          | apt on onango  | interrupt i lage |                    |                    |         |  |  |  |  |  |  |

|                 | 10011 <b>= CN</b>                                                  |                                                                            |                |                  |                    |                    |         |  |  |  |  |  |  |

|                 | 10010 <b>= NC</b>                                                  | O1_out                                                                     |                |                  |                    |                    |         |  |  |  |  |  |  |

|                 | 10001 <b>= PW</b>                                                  |                                                                            |                |                  |                    |                    |         |  |  |  |  |  |  |

|                 | 10000 <b>= PW</b>                                                  | —                                                                          |                |                  |                    |                    |         |  |  |  |  |  |  |

|                 | 01111 = PW<br>01110 = PW                                           | _                                                                          |                |                  |                    |                    |         |  |  |  |  |  |  |

|                 | 01101 <b>= CC</b>                                                  |                                                                            |                |                  |                    |                    |         |  |  |  |  |  |  |

|                 | 01100 <b>= CC</b>                                                  |                                                                            |                |                  |                    |                    |         |  |  |  |  |  |  |

|                 | 01011 <b>= CC</b>                                                  |                                                                            |                |                  |                    |                    |         |  |  |  |  |  |  |

|                 | 01010 <b>= CC</b>                                                  |                                                                            |                |                  |                    |                    |         |  |  |  |  |  |  |

|                 | 01001 = SM                                                         | IR6_postscaled                                                             |                |                  |                    |                    |         |  |  |  |  |  |  |

|                 |                                                                    | IR5 overflow                                                               |                |                  |                    |                    |         |  |  |  |  |  |  |

|                 |                                                                    | IR4_postscaled                                                             |                |                  |                    |                    |         |  |  |  |  |  |  |

|                 | 00101 <b>= TM</b>                                                  | IR3_overflow                                                               |                |                  |                    |                    |         |  |  |  |  |  |  |

|                 |                                                                    | IR2_postscaled                                                             |                |                  |                    |                    |         |  |  |  |  |  |  |

|                 |                                                                    | IR1_overflow                                                               |                |                  |                    |                    |         |  |  |  |  |  |  |

|                 |                                                                    | IR0_overflow<br>i selected by ADAC                                         | TPPS           |                  |                    |                    |         |  |  |  |  |  |  |

|                 |                                                                    | ternal Trigger Disal                                                       |                |                  |                    |                    |         |  |  |  |  |  |  |

### REGISTER 36-35: ADACT: ADC AUTO CONVERSION TRIGGER CONTROL REGISTER

#### TABLE 44-6: I/O PORTS

| Standard     | d Operati | ing Conditions (unless otherwi       | se stated)        |                      | -                   |       |                                                                                                                                    |

|--------------|-----------|--------------------------------------|-------------------|----------------------|---------------------|-------|------------------------------------------------------------------------------------------------------------------------------------|

| Param<br>No. | Sym.      | Characteristic                       | Min.              | Тур†                 | Max.                | Units | Conditions                                                                                                                         |

|              | VIL       | Input Low Voltage                    |                   |                      |                     |       |                                                                                                                                    |

|              |           | I/O PORT:                            |                   |                      |                     |       |                                                                                                                                    |

| D300         |           | with TTL buffer                      |                   | —                    | 0.8                 | V     | $4.5V \le VDD \le 5.5V$                                                                                                            |

| D301         |           |                                      | _                 | _                    | 0.15 Vdd            | V     | 1.8V ≤ VDD < 4.5V                                                                                                                  |

| D302         |           | with Schmitt Trigger buffer          | _                 | _                    | 0.2 VDD             | V     | 2.0V ≤ VDD ≤ 5.5                                                                                                                   |

| D303         |           | with I <sup>2</sup> C levels         | _                 | _                    | 0.3 VDD             | V     |                                                                                                                                    |

| D304         |           | with SMBus 2.0                       | _                 | _                    | 0.8                 | V     | 2.7V ≤ VDØ ≤ 5.5V                                                                                                                  |

| D305         |           | with SMBus 3.0                       | _                 | —                    | 0.8                 | V     | 1.8V ≤ VDØ ≤ 5.5V                                                                                                                  |

| D306         |           | MCLR                                 | _                 | _                    | 0.2 VDD             | V     |                                                                                                                                    |

|              | Vih       | Input High Voltage                   |                   |                      |                     |       |                                                                                                                                    |

|              |           | I/O PORT:                            |                   |                      |                     |       |                                                                                                                                    |

| D320         |           | with TTL buffer                      | 2.0               | _                    | _                   | v     | 4.5V ≩ Vpp ≤ 5,5V                                                                                                                  |

| D321         |           |                                      | 0.25 VDD +<br>0.8 | _                    |                     | V     | 1.8V 2 VDD < 4.5V                                                                                                                  |

| D322         |           | with Schmitt Trigger buffer          | 0.8 Vdd           | _                    | `                   | X     | $2.0 \times \neq V$ DD $\leq 5.5 V$                                                                                                |

| D323         |           | with I <sup>2</sup> C levels         | 0.7 Vdd           | _                    |                     | A     |                                                                                                                                    |

| D324         |           | with SMBus 2.0                       | 2.1               | -^                   | $\mathcal{F}$       | V     | $2.7V \le VDD \le 5.5V$                                                                                                            |

| D325         |           | with SMBus 3.0                       | 1.35              |                      | /_/                 | У     | $1.8V \leq V\text{DD} \leq 5.5V$                                                                                                   |

| D326         |           | MCLR                                 | 0.7 VDD           | $\overline{\langle}$ | $\langle - \rangle$ | ٧     |                                                                                                                                    |

|              | lı∟       | Input Leakage Current <sup>(1)</sup> |                   | V                    | $\overline{\nabla}$ |       |                                                                                                                                    |

| D340         |           | I/O Ports                            |                   | ± 5                  | € 125               | nA    | $\label{eq:VSS} \begin{split} Vss \leq V \mbox{PIN} \leq V \mbox{DD}, \\ Pin \mbox{ at high-impedance, } 85 \mbox{°C} \end{split}$ |

| D341         |           | <                                    |                   | ±5                   | ± 1000              | nA    | $Vss \le VPIN \le VDD$ , Pin at high-impedance, 125°C                                                                              |

| D342         |           | MCLR <sup>(2)</sup>                  | ~                 | ± 50                 | ± 200               | nA    | $Vss \le VPIN \le VDD$ , Pin at high-impedance, 85°C                                                                               |

|              | IPUR      | Weak Pull-up Current                 | · · ·             |                      |                     |       |                                                                                                                                    |

| D350         |           |                                      | 25                | 120                  | 200                 | μA    | VDD = 3.0V, VPIN = VSS                                                                                                             |

|              | Vol       | Output Low Voltage                   |                   |                      |                     |       |                                                                                                                                    |

| D360         |           | I/O ports                            | - V               | _                    | 0.6                 | V     | IOL = 10.0mA, VDD = 3.0V                                                                                                           |

|              | Vон       | Output High Voltage                  | •                 | •                    | •                   |       |                                                                                                                                    |

| D370         |           | I/Ø ports                            | Vdd - 0.7         | _                    | _                   | V     | Юн = 6.0 mA, VDD = 3.0V                                                                                                            |

| D380         | Cio /     | All I/O pins                         | _                 | 5                    | 50                  | pF    |                                                                                                                                    |

† Data in "Typ" column is at 3.0V, 25°C unless otherwise stated. These parameters are for design guidance only and are not tested.

Note 1: Negative current is defined as current sourced by the pin.

2. The leakage current on the MCLR pin is strongly dependent on the applied voltage level. The specified levels represent normal operating conditions. Higher leakage current may be measured at different input voltages.

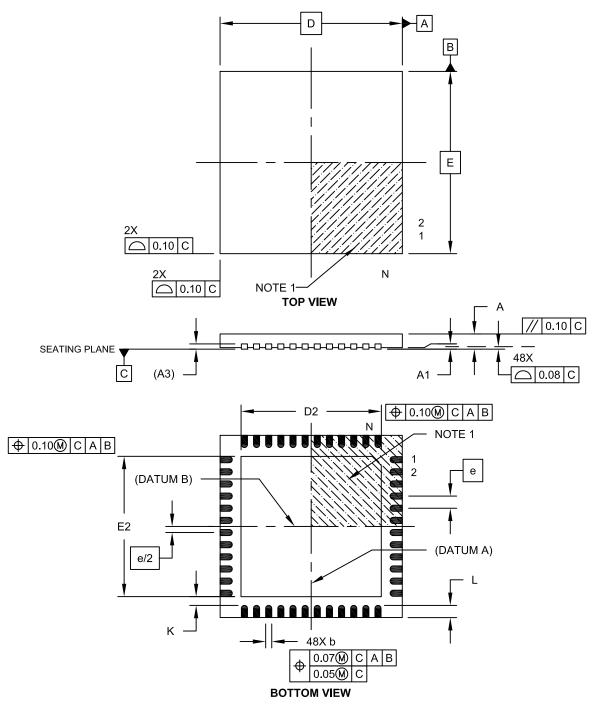

#### 28-Lead Plastic Quad Flat, No Lead Package (ML) - 6x6 mm Body [QFN] With 0.55 mm Terminal Length

**Note:** For the most current package drawings, please see the Microchip Packaging Specification located at http://www.microchip.com/packaging

|                         | Units  | М        | ILLIMETERS | ;    |

|-------------------------|--------|----------|------------|------|

| Dimension               | Limits | MIN      | NOM        | MAX  |

| Number of Pins          | Ν      |          | 28         |      |

| Pitch                   | е      |          | 0.65 BSC   |      |

| Overall Height          | А      | 0.80     | 0.90       | 1.00 |

| Standoff                | A1     | 0.00     | 0.02       | 0.05 |

| Terminal Thickness      | A3     | 0.20 REF |            |      |

| Overall Width           | E      | 6.00 BSC |            |      |

| Exposed Pad Width       | E2     | 3.65     | 3.70       | 4.20 |

| Overall Length          | D      |          | 6.00 BSC   |      |

| Exposed Pad Length      | D2     | 3.65     | 3.70       | 4.20 |

| Terminal Width          | b      | 0.23     | 0.30       | 0.35 |

| Terminal Length         | L      | 0.50     | 0.55       | 0.70 |

| Terminal-to-Exposed Pad | К      | 0.20     | -          | -    |

Notes:

1. Pin 1 visual index feature may vary, but must be located within the hatched area.

2. Package is saw singulated

3. Dimensioning and tolerancing per ASME Y14.5M.

BSC: Basic Dimension. Theoretically exact value shown without tolerances.

REF: Reference Dimension, usually without tolerance, for information purposes only.

Microchip Technology Drawing C04-105C Sheet 2 of 2

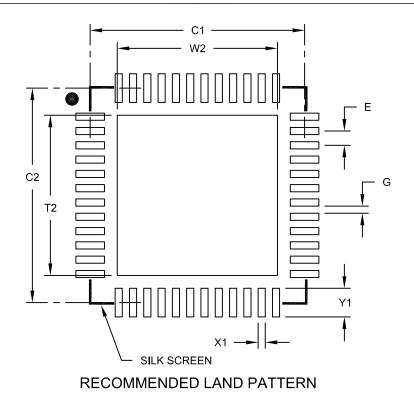

#### 48-Lead Plastic Ultra Thin Quad Flat, No Lead Package (MV) – 6x6x0.5 mm Body [UQFN]

Microchip Technology Drawing C04-153A Sheet 1 of 2

48-Lead Ultra Thin Plastic Quad Flat, No Lead Package (MV) - 6x6 mm Body [UQFN] With 0.40 mm Contact Length

**Note:** For the most current package drawings, please see the Microchip Packaging Specification located at http://www.microchip.com/packaging

|                            | Units            | ſ    | MILLIMETER | S    |

|----------------------------|------------------|------|------------|------|

| Dimension                  | Dimension Limits |      |            |      |

| Contact Pitch              | E                |      | 0.40 BSC   | •    |

| Optional Center Pad Width  | W2               |      |            | 4.45 |

| Optional Center Pad Length | T2               |      |            | 4.45 |

| Contact Pad Spacing        | C1               |      | 6.00       |      |

| Contact Pad Spacing        | C2               |      | 6.00       |      |

| Contact Pad Width (X28)    | X1               |      |            | 0.20 |

| Contact Pad Length (X28)   | Y1               |      |            | 0.80 |

| Distance Between Pads      | G                | 0.20 |            |      |

Notes:

1. Dimensioning and tolerancing per ASME Y14.5M

BSC: Basic Dimension. Theoretically exact value shown without tolerances.

Microchip Technology Drawing No. C04-2153A