Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

#### Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Product Status             | Active                                                                     |

|----------------------------|----------------------------------------------------------------------------|

| Core Processor             | PIC                                                                        |

| Core Size                  | 8-Bit                                                                      |

| Speed                      | 64MHz                                                                      |

| Connectivity               | I <sup>2</sup> C, LINbus, SPI, UART/USART                                  |

| Peripherals                | Brown-out Detect/Reset, DMA, HLVD, POR, PWM, WDT                           |

| Number of I/O              | 36                                                                         |

| Program Memory Size        | 64KB (32K x 16)                                                            |

| Program Memory Type        | FLASH                                                                      |

| EEPROM Size                | 1K x 8                                                                     |

| RAM Size                   | 4K x 8                                                                     |

| Voltage - Supply (Vcc/Vdd) | 2.3V ~ 5.5V                                                                |

| Data Converters            | A/D 35x12b; D/A 1x5b                                                       |

| Oscillator Type            | Internal                                                                   |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                          |

| Mounting Type              | Surface Mount                                                              |

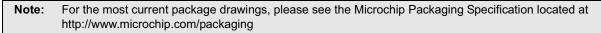

| Package / Case             | 44-TQFP                                                                    |

| Supplier Device Package    | 44-TQFP (10x10)                                                            |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/pic18f46k42-i-pt |

|                            |                                                                            |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

### 3.1 System Arbitration

The System Arbiter resolves memory access between the System Level Selections (i.e., Main, Interrupt Service Routine) and Peripheral Selection (i.e., DMA and Scanner) based on user-assigned priorities. Each of the system level and peripheral selections has its own priority selection registers. Memory access priority is resolved using the number written to the corresponding Priority registers, 0 being the highest priority and 4 the lowest. The default priorities are listed in Table 3-1.

In case the user wants to change priorities, ensure each Priority register is written with a unique value from 0 to 4.

| Sele         | Priority register<br>Reset value |   |

|--------------|----------------------------------|---|

| System Level | ISR                              | 0 |

|              | MAIN                             | 1 |

| Peripheral   | DMA1                             | 2 |

|              | DMA2                             | 3 |

|              | SCANNER                          | 4 |

TABLE 3-1: DEFAULT PRIORITIES

| Bank              | BSR<5:0>                | Address<br>addr<7:0> | PIC18(L)F45K42<br>PIC18(L)F55K42 | PIC18(L)F26K42<br>PIC18(L)F46K42<br>PIC18(L)F56K42 | PIC18(L)F27K42<br>PIC18(L)F47K42<br>PIC18(L)F57K42 | Address<br>addr<13:0>   |                |

|-------------------|-------------------------|----------------------|----------------------------------|----------------------------------------------------|----------------------------------------------------|-------------------------|----------------|

|                   |                         | 00h                  | Access RAM                       | Access RAM                                         | Access RAM                                         | 0000h<br>005Fh          |                |

| Bank 0            | 00 0000                 | FFh                  | GPR                              | GPR                                                | GPR                                                | 0060h<br>00FFh          |                |

| Bank 1            | 00 0001                 | 00h<br>FFh           |                                  |                                                    |                                                    | 0100h                   |                |

| Bank 2            | 00 0010                 | 00h<br>FFh           | GPR                              | GPR                                                | GPR                                                | •                       |                |

|                   |                         | 00h                  | GPR                              | GPR                                                | GPR                                                |                         |                |

| Bank 3            | 00 0011                 | ·<br>FFh             |                                  |                                                    |                                                    | 03FFh                   | Virtual Bank   |

|                   | 00 0100                 | 00h                  |                                  |                                                    |                                                    | 0400h<br>•              | Access RAM 00h |

| Banks<br>4 to 7   | 00 0111                 | :<br>FFh             | GPR                              | GPR                                                | GPR                                                | :<br>07FFh              | SFR 60h        |

|                   |                         | 00h                  |                                  |                                                    |                                                    | 0800h                   | / FFh          |

| Banks<br>8 to 15  | 00 1000<br>-<br>00 1111 | :                    |                                  | GPR                                                |                                                    | •                       |                |

|                   | 00 1111                 | FFh<br>00h           |                                  |                                                    | GPR                                                | 0FFFh<br>1000h          | _ //           |

| Banks<br>16 to 31 | 01 0000                 | :                    | Unimplemented                    |                                                    |                                                    |                         |                |

|                   | 01 1111                 | FFh<br>00h           |                                  | Unimplemented                                      |                                                    | 1FFFh<br>2000h          |                |

| Banks             | 10 0000                 |                      |                                  |                                                    | Unimplemented                                      |                         |                |

| 32 to 55          | -<br>11 0111            | FFh                  |                                  |                                                    |                                                    | 37FFh                   |                |

| Banks             | 11 1000                 | 00h                  |                                  |                                                    |                                                    | 3800h<br>•              |                |

| Banks<br>56 to 62 | 11 1110                 | :<br>FFh             | SFR                              | SFR                                                | SFR                                                | ·<br>3EFFh              |                |

| Bank 63           | 11 1111                 | 00h                  | SFR                              | SFR                                                | SFR                                                | 3800h<br>3EFFh<br>3F60h |                |

FIGURE 4-4:

#### DATA MEMORY MAP FOR PIC18/I )E26/27/45/46/47/55/56/57K42 DEVICES

© 2016-2017 Microchip Technology Inc.

| R/W-0/0          | R/W-0/0                                                              | R/W-0/0           | R/W-0/0        | R/W-0/0        | R/W-0/0          | R/W-0/0          | R/W-0/0      |  |  |

|------------------|----------------------------------------------------------------------|-------------------|----------------|----------------|------------------|------------------|--------------|--|--|

| TMR0IE           | U1IE                                                                 | U1EIE             | U1TXIE         | U1RXIE         | I2C1EIE          | I2C1IE           | I2C1TXIE     |  |  |

| bit 7            |                                                                      |                   |                |                |                  |                  | bit (        |  |  |

|                  |                                                                      |                   |                |                |                  |                  |              |  |  |

| Legend:          |                                                                      |                   |                |                |                  |                  |              |  |  |

| R = Readable     |                                                                      | W = Writable      |                | •              | mented bit, read |                  |              |  |  |

| u = Bit is unch  | anged                                                                | x = Bit is unkr   |                | -n/n = Value a | at POR and BO    | R/Value at all c | other Resets |  |  |

| '1' = Bit is set |                                                                      | '0' = Bit is clea | ared           |                |                  |                  |              |  |  |

| bit 7            | TMROIF                                                               | R0 Interrupt En   | able bit       |                |                  |                  |              |  |  |

|                  | 1 = Enabled<br>0 = Disabled                                          |                   |                |                |                  |                  |              |  |  |

| bit 6            | U1IE: UART1                                                          | Interrupt Enab    | ole bit        |                |                  |                  |              |  |  |

|                  | 1 = Enabled                                                          |                   |                |                |                  |                  |              |  |  |

|                  | 0 = Disabled                                                         |                   |                |                |                  |                  |              |  |  |

| bit 5            | U1EIE: UART1 Framing Error Interrupt Enable bit                      |                   |                |                |                  |                  |              |  |  |

|                  | 1 = Enabled<br>0 = Disabled                                          |                   |                |                |                  |                  |              |  |  |

| bit 4            | U1TXIE: UART1 Transmit Interrupt Enable bit                          |                   |                |                |                  |                  |              |  |  |

|                  | 1 = Enabled                                                          |                   |                |                |                  |                  |              |  |  |

|                  | 0 = Disabled                                                         |                   |                |                |                  |                  |              |  |  |

| bit 3            |                                                                      | RT1 Receive In    | terrupt Enable | e bit          |                  |                  |              |  |  |

|                  | 1 = Enabled<br>0 = Disabled                                          |                   |                |                |                  |                  |              |  |  |

| bit 2            |                                                                      |                   | t Enable bit   |                |                  |                  |              |  |  |

|                  | I2C1EIE: I <sup>2</sup> C1 Error Interrupt Enable bit<br>1 = Enabled |                   |                |                |                  |                  |              |  |  |

|                  | 0 = Disabled                                                         |                   |                |                |                  |                  |              |  |  |

| bit 1            | I2C1IE: I <sup>2</sup> C1 Interrupt Enable bit                       |                   |                |                |                  |                  |              |  |  |

|                  | 1 = Enabled                                                          |                   |                |                |                  |                  |              |  |  |

|                  | 0 = Disabled                                                         |                   |                |                |                  |                  |              |  |  |

| bit 0            |                                                                      | C1 Transmit Int   | errupt Enable  | bit            |                  |                  |              |  |  |

|                  | 1 = Enabled                                                          |                   |                |                |                  |                  |              |  |  |

### REGISTER 9-17: PIE3: PERIPHERAL INTERRUPT ENABLE REGISTER 3

#### 10.2.3.2 Peripheral Usage in Sleep

Some peripherals that can operate in Sleep mode will not operate properly with the Low-Power Sleep mode selected. The Low-Power Sleep mode is intended for use with these peripherals:

- Brown-out Reset (BOR)

- Windowed Watchdog Timer (WWDT)

- External interrupt pin/Interrupt-On-Change pins

- Peripherals that run off external secondary clock source

It is the responsibility of the end user to determine what is acceptable for their application when setting the VREGPM settings in order to ensure operation in Sleep.

| Note: | The PIC18F26/27/45/46/47/55/56/57K42     |

|-------|------------------------------------------|

|       | devices do not have a configurable Low-  |

|       | Power Sleep mode. PIC18F26/27/45/46/     |

|       | 47/55/56/57K42 devices are unregulated   |

|       | and are always in the lowest power state |

|       | when in Sleep, with no wake-up time      |

|       | penalty. These devices have a lower      |

|       | maximum VDD and I/O voltage than the     |

|       | PIC18(L)F26/27/45/46/47/55/56/57K42.     |

|       |                                          |

|       | See Section 44.0 "Electrical             |

|       | Specifications" for more information.    |

#### 10.2.4 IDLE MODE

When IDLEN is set (IDLEN = 1), the SLEEP instruction will put the device into Idle mode. In Idle mode, the CPU and memory operations are halted, but the peripheral clocks continue to run. This mode is similar to Doze mode, except that in IDLE both the CPU and PFM are shut off.

Note: If CLKOUTEN is enabled (CLKOUTEN = 0, Configuration Word 1H), the output will continue operating while in idle.

#### 10.2.4.1 Idle and Interrupts

IDLE mode ends when an interrupt occurs (even if GIE = 0), but IDLEN is not changed. The device can reenter IDLE by executing the SLEEP instruction.

If Recover-On-Interrupt is enabled (ROI = 1), the interrupt that brings the device out of idle also restores full-speed CPU execution when doze is also enabled.

#### 10.2.4.2 Idle and WWDT

When in idle, the WWDT Reset is blocked and will instead wake the device. The WWDT wake-up is not an interrupt, therefore ROI does not apply.

Note: The WDT can bring the device out of idle, in the same way it brings the device out of Sleep. The DOZEN bit is not affected.

### 10.3 Peripheral Operation in Power Saving Modes

All selected clock sources and the peripherals running off them are active in both IDLE and DOZE mode. Only in Sleep mode, both the Fosc and Fosc/4 clocks are unavailable. All the other clock sources are active, if enabled manually or through peripheral clock selection before the part enters Sleep.

| WRITE_BYTE  | TO_HREGS |                     |                                         |

|-------------|----------|---------------------|-----------------------------------------|

|             | MOVF     | POSTINCO, W         | ; get low byte of buffer data           |

|             | MOVWF    | TABLAT              | ; present data to table latch           |

|             | TBLWT+*  |                     | ; write data, perform a short write     |

|             |          |                     | ; to internal TBLWT holding register.   |

|             | DECFSZ   | COUNTER             | ; loop until holding registers are full |

|             | BRA      | WRITE WORD TO HREGS |                                         |

| PROGRAM MEM | ORY      |                     |                                         |

|             | BCF      | NVMCON1, REG0       | ; point to Program Flash Memory         |

|             | BSF      | NVMCON1, REG1       | ; point to Program Flash Memory         |

|             | BSF      | NVMCON1, WREN       | ; enable write to memory                |

|             | BCF      | NVMCON1, FREE       | ; enable write to memory                |

|             | BCF      | INTCON0, GIE        | ; disable interrupts                    |

|             | MOVLW    | 55h                 |                                         |

| Required    | MOVWF    | NVMCON2             | ; write 55h                             |

| Sequence    | MOVLW    | 0AAh                |                                         |

|             | MOVWF    | NVMCON2             | ; write OAAh                            |

|             | BSF      | NVMCON1, WR         | ; start program (CPU stall)             |

|             | DCFSZ    | COUNTER2            | ; repeat for remaining write blocks     |

|             | BRA      | WRITE_BYTE_TO_HREGS |                                         |

|             | BSF      | INTCONO, GIE        | ; re-enable interrupts                  |

|             | BCF      | NVMCON1, WREN       | ; disable write to memory               |

|             |          |                     |                                         |

# EXAMPLE 13-4: WRITING TO PROGRAM FLASH MEMORY (CONTINUED)

| Name       | Bit 7 | Bit 6 | Bit 5 | Bit 4 | Bit 3         | Bit 2      | Bit 1  | Bit 0     | Register<br>on page |

|------------|-------|-------|-------|-------|---------------|------------|--------|-----------|---------------------|

| PPSLOCK    | —     |       | —     | —     | —             | —          | —      | PPSLOCKED | 283                 |

| INT0PPS    | _     | _     | _     |       | INTOPPS<4:0>  |            |        |           |                     |

| INT1PPS    | _     | _     | _     |       |               | INT1PPS<   | 4:0>   |           | 277                 |

| INT2PPS    | _     | _     | _     |       |               | INT2PPS<4  | 4:0>   |           | 277                 |

| TOCKIPPS   |       | _     | _     |       |               | T0CKIPPS<  | :4:0>  |           | 277                 |

| T1CKIPPS   |       | _     | _     |       |               | T1CKIPPS<  | :4:0>  |           | 277                 |

| T1GPPS     | _     | _     | _     |       |               | T1GPPS<4   | 4:0>   |           | 277                 |

| T3CKIPPS   | _     | _     | _     |       |               | T3CKIPPS<  | :4:0>  |           | 277                 |

| T3GPPS     | _     | _     | _     |       |               | T3GPPS<4   | 4:0>   |           | 277                 |

| T5CKIPPS   | -     | _     | —     |       |               | T5CKIPPS<  | :4:0>  |           | 277                 |

| T5GPPS     | -     | _     | —     |       |               | T5GPPS<4   | 4:0>   |           | 277                 |

| T2INPPS    | _     | _     | _     |       |               | T2INPPS<   | 4:0>   |           | 277                 |

| T4INPPS    | -     | _     | —     |       |               | T4INPPS<   | 4:0>   |           | 277                 |

| T6INPPS    | _     | _     | _     |       |               | T6INPPS<4  | 4:0>   |           | 277                 |

| CCP1PPS    | _     | _     | _     |       |               | CCP1PPS<   | 4:0>   |           | 277                 |

| CCP2PPS    | _     | _     | _     |       |               | CCP2PPS<   | 4:0>   |           | 277                 |

| CCP3PPS    | _     | _     | _     |       |               | CCP3PPS<   | 4:0>   |           | 277                 |

| CCP4PPS    | _     | _     | _     |       |               | CCP4PPS<   | 4:0>   |           | 277                 |

| SMT1WINPPS | _     | _     | _     |       |               | SMT1WINPP  | S<4:0> |           | 277                 |

| SMT1SIGPPS | _     | _     | _     |       |               | SMT1SIGPPS | S<4:0> |           | 277                 |

| CWG1PPS    |       | _     | _     |       |               | CWG1PPS<   | :4:0>  |           | 277                 |

| CWG2PPS    |       | _     | _     |       |               | CWG2PPS<   | :4:0>  |           | 277                 |

| CWG3PPS    |       | _     | _     |       |               | CWG3PPS<   | :4:0>  |           | 277                 |

| MD1CARLPPS | _     | _     | _     |       |               | MDCARLPPS  | 6<4:0> |           | 277                 |

| MD1CARHPPS | _     | _     | _     |       |               | MDCARHPP   | S<4:0> |           | 277                 |

| MD1SRCPPS  | _     | _     | _     |       |               | MDSRCPPS   | <4:0>  |           | 277                 |

| CLCIN0PPS  |       | _     | _     |       |               | CLCIN0PPS  | <4:0>  |           | 277                 |

| CLCIN1PPS  | _     | _     | _     |       |               | CLCIN1PPS  | <4:0>  |           | 277                 |

| CLCIN2PPS  | _     | _     | _     |       |               | CLCIN2PPS  | <4:0>  |           | 277                 |

| CLCIN3PPS  |       | _     | _     |       |               | CLCIN3PPS  | <4:0>  |           | 277                 |

| ADACTPPS   | _     | _     | _     |       |               | ADACTPPS   | <4:0>  |           | 277                 |

| SPI1SCKPPS | _     | _     | _     |       |               | SPI1SCKPPS | S<4:0> |           | 277                 |

| SPI1SDIPPS | _     | _     | _     |       |               | SPI1SDIPPS | <4:0>  |           | 277                 |

| SPI1SSPPS  | _     | _     | _     |       |               | SPI1SSPPS  | <4:0>  |           | 277                 |

| I2C1SCLPPS |       | _     | _     |       |               | I2C1SCLPPS | 6<4:0> |           | 277                 |

| I2C1SDAPPS | _     | _     | _     |       |               | I2C1SDAPPS | 6<4:0> |           | 277                 |

| I2C2SCLPPS | _     | _     | _     |       |               | I2C2SCLPPS | 6<4:0> |           | 277                 |

| I2C2SDAPPS | _     | _     | _     |       |               | I2C2SDAPPS | 6<4:0> |           | 277                 |

| U1RXPPS    | _     | _     | _     |       |               | U1RXPPS<   | 4:0>   |           | 277                 |

| U1CTSPPS   | _     | _     | _     |       | U1CTSPPS<4:0> |            |        |           |                     |

| U2RXPPS    | _     | _     | _     |       | U2RXPPS<4:0>  |            |        |           |                     |

| U2CTSPPS   | _     | _     | —     |       |               | U2CTPPS<   | 4:0>   |           | 277<br>277          |

| RxyPPS     | _     | _     | _     |       |               | RxyPPS<4   |        |           | 280                 |

### TABLE 17-3: SUMMARY OF REGISTERS ASSOCIATED WITH THE PPS MODULE

**Legend:** — = unimplemented, read as '0'. Shaded cells are unused by the PPS module.

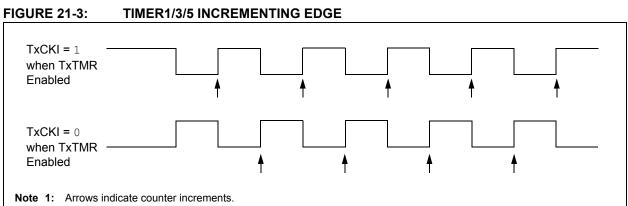

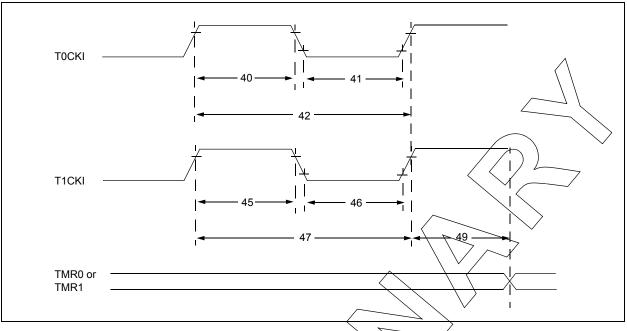

2: In Counter mode, a falling edge must be registered by the counter prior to the first incrementing rising edge of the clock.

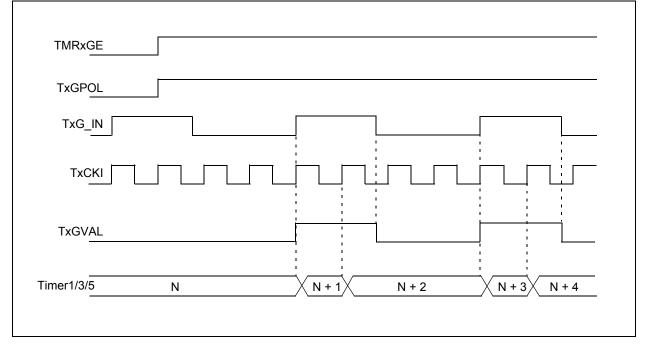

# FIGURE 21-4: TIMER1/3/5 GATE ENABLE MODE

| U-0                   | U-0                                                                                                                                                                                                                                                                                                         | R/W-0/0                                                                                                                                         | R/W-0/0          | U-0            | U-0              | R/W-0/0  | R/W-0/0      |  |  |  |  |

|-----------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------|------------------|----------------|------------------|----------|--------------|--|--|--|--|

| _                     | —                                                                                                                                                                                                                                                                                                           | CHPOL                                                                                                                                           | CHSYNC           | —              | —                | CLPOL    | CLSYNC       |  |  |  |  |

| bit 7                 |                                                                                                                                                                                                                                                                                                             |                                                                                                                                                 |                  |                |                  |          | bit C        |  |  |  |  |

| Lagandi               |                                                                                                                                                                                                                                                                                                             |                                                                                                                                                 |                  |                |                  |          |              |  |  |  |  |

| Legend:<br>R = Readab | le bit                                                                                                                                                                                                                                                                                                      | W = Writable I                                                                                                                                  | oit              | U = Unimple    | mented bit, read | d as '0' |              |  |  |  |  |

| u = Bit is un         | changed                                                                                                                                                                                                                                                                                                     | x = Bit is unkn                                                                                                                                 | own              | -              | at POR and BC    |          | other Resets |  |  |  |  |

| '1' = Bit is se       | •                                                                                                                                                                                                                                                                                                           | '0' = Bit is clea                                                                                                                               | ared             |                |                  |          |              |  |  |  |  |

|                       |                                                                                                                                                                                                                                                                                                             |                                                                                                                                                 |                  |                |                  |          |              |  |  |  |  |

| bit 7-6               | Unimplemer                                                                                                                                                                                                                                                                                                  | nted: Read as '                                                                                                                                 | 0'               |                |                  |          |              |  |  |  |  |

| bit 5                 | CHPOL: Mod                                                                                                                                                                                                                                                                                                  | dulator High Ca                                                                                                                                 | rrier Polarity S | elect bit      |                  |          |              |  |  |  |  |

|                       | 1 = Selected                                                                                                                                                                                                                                                                                                | 1 = Selected high carrier signal is inverted                                                                                                    |                  |                |                  |          |              |  |  |  |  |

|                       | 0 = Selected                                                                                                                                                                                                                                                                                                | 0 = Selected high carrier signal is not inverted                                                                                                |                  |                |                  |          |              |  |  |  |  |

| bit 4                 | CHSYNC: M                                                                                                                                                                                                                                                                                                   | odulator High C                                                                                                                                 | arrier Synchro   | nization Enabl | le bit           |          |              |  |  |  |  |

|                       |                                                                                                                                                                                                                                                                                                             | <ul> <li>1 = Modulator waits for a falling edge on the high time carrier signal before allowing a switch to the<br/>low time carrier</li> </ul> |                  |                |                  |          |              |  |  |  |  |

|                       | 0 = Modulate                                                                                                                                                                                                                                                                                                | ator output is not synchronized to the high time carrier signal <sup>(1)</sup>                                                                  |                  |                |                  |          |              |  |  |  |  |

| bit 3-2               | Unimplemer                                                                                                                                                                                                                                                                                                  | nted: Read as '                                                                                                                                 | 0'               |                |                  |          |              |  |  |  |  |

| bit 1                 | CLPOL: Mod                                                                                                                                                                                                                                                                                                  | dulator Low Car                                                                                                                                 | rier Polarity Se | elect bit      |                  |          |              |  |  |  |  |

|                       |                                                                                                                                                                                                                                                                                                             | l low carrier sig<br>l low carrier sig                                                                                                          |                  | ted            |                  |          |              |  |  |  |  |

| bit 0                 | <ul> <li>CLSYNC: Modulator Low Carrier Synchronization Enable bit</li> <li>1 = Modulator waits for a falling edge on the low time carrier signal before allowing a switch to the hig time carrier</li> <li>0 = Modulator output is not synchronized to the low time carrier signal<sup>(1)</sup></li> </ul> |                                                                                                                                                 |                  |                |                  |          |              |  |  |  |  |

|                       |                                                                                                                                                                                                                                                                                                             |                                                                                                                                                 |                  |                |                  |          |              |  |  |  |  |

#### REGISTER 30-2: MD1CON1: MODULATION CONTROL REGISTER 1

Note 1: Narrowed carrier pulse widths or spurs may occur in the signal stream if the carrier is not synchronized.

| Name    | Bit 7  | Bit 6      | Bit 5  | Bit 4 | Bit 3  | Bit 2  | Bit 1  | Bit 0 | Register<br>on page |

|---------|--------|------------|--------|-------|--------|--------|--------|-------|---------------------|

| UxCON0  | BRGS   | ABDEN      | TXEN   | RXEN  |        | MODE   | <3:0>  |       | 498                 |

| UxCON1  | ON     | _          | —      | WUE   | RXBIMD | —      | BRKOVR | SENDB | 499                 |

| UxCON2  | RUNOVF | RXPOL      | STP    | <1:0> | C0EN   | TXPOL  | FLO<   | <1:0> | 500                 |

| UxERRIR | TXMTIF | PERIF      | ABDOVF | CERIF | FERIF  | RXBKIF | RXFOIF | TXCIF | 501                 |

| UxERRIE | TXMTIE | PERIE      | ABDOVE | CERIE | FERIE; | RXBKIE | RXFOIE | TXCIE | 502                 |

| UxUIR   | WUIF   | ABDIF      | _      | _     | _      | ABDIE  | _      | _     | 503                 |

| UxFIFO  | TXWRE  | STPMD      | TXBE   | TXBF  | RXIDL  | XON    | RXBE   | RXBF  | 504                 |

| UxBRGL  |        | BRG<7:0>   |        |       |        |        |        |       | 505                 |

| UxBRGH  |        |            |        | BRG<  | <15:8> |        |        |       | 505                 |

| UxRXB   |        |            |        | RXB   | <7:0>  |        |        |       | 506                 |

| UxTXB   |        |            |        | TXB   | <7:0>  |        |        |       | 506                 |

| UxP1H   | _      | _          | _      | _     | —      | _      | _      | P1<8> | 507                 |

| UxP1L   |        |            | •      | P1<   | 7:0>   |        |        |       | 507                 |

| UxP2H   | _      | _          | _      | _     | —      | _      | _      | P2<8> | 508                 |

| UxP2L   |        |            | •      | P2<   | 7:0>   |        |        |       | 508                 |

| UxP3H   | —      | —          | —      | —     | —      | —      | —      | P3<8> | 509                 |

| UxP3L   |        |            | •      | P3<   | 7:0>   | •      | •      |       | 509                 |

| UxTXCHK |        |            |        | TXCH  | K<7:0> |        |        |       | 510                 |

| UxRXCHK |        | RXCHK<7:0> |        |       |        |        |        |       | 510                 |

### TABLE 31-3: SUMMARY OF REGISTERS ASSOCIATED WITH THE UART

Legend: — = unimplemented, read as '0'. Shaded cells are unused by the UART module.

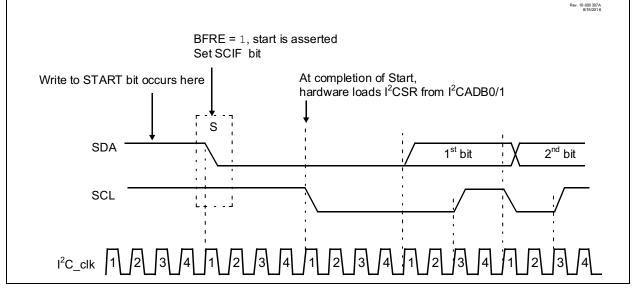

asserting the Start condition. The action of the SDA being driven low while SCL is high is the Start condition,

causing the SCIF bit to be set. One TSCL later the SCL

is asserted low, ending the start sequence. Figure 33-

15 shows the Start condition timing.

### 33.5.5 I<sup>2</sup>C MASTER MODE START CONDITION TIMING

The user can initiate a Start condition by either writing to the Start bit (S) of the I2CxCON0 register or by writing to the I2CxTXB register based on the ABD bit setting. Master hardware waits for BFRE = 1, before

### FIGURE 33-15: START CONDITION TIMING

#### 33.5.6 I<sup>2</sup>C MASTER MODE REPEATED START CONDITION TIMING

A Repeated Start condition occurs when the Start bit of the I2CxCON0 register is set and the master module is waiting from a Restart clock stretch event (RSEN = 1 and I2CxCNT = 0).

When the Start bit is set, the SDA pin is released high for TscL/2. Then the SCL pin is released floated high) for TscL/2. If the SDA pin is detected low, bus collision flag (BCLIF) is set and the master goes idle. If SDA is detected high, the SDA pin will be pulled low (Start condition) for TscL. Last, SCL is asserted low and I2CxADB0/1 is loaded into the shift register. As soon as a Restart condition is detected on the SDA and SCL pins, the RSCIF bit is set. Figure 33-16 shows the timings for repeated Start Condition.

# **REGISTER 33-9:** I2CxCNT: I<sup>2</sup>C BYTE COUNT REGISTER

| R/W-x/u      | R/W-x/u | R/W-x/u | R/W-x/u | R/W-x/u | R/W-x/u | R/W-x/u | R/W-x/u |

|--------------|---------|---------|---------|---------|---------|---------|---------|

|              |         |         | CNT     | <7:0>   |         |         |         |

| bit 7        |         |         |         |         |         |         | bit 0   |

|              |         |         |         |         |         |         |         |

| Legend:      |         |         |         |         |         |         |         |

| D Deedeklerk |         |         | L       |         |         | (0)     |         |

| R = Readable bit     | VV = VVritable bit   | U = Unimplemented bit, read as '0'                    |

|----------------------|----------------------|-------------------------------------------------------|

| u = Bit is unchanged | x = Bit is unknown   | -n/n = Value at POR and BOR/Value at all other Resets |

| ʻı' = Bit is set     | '0' = Bit is cleared | HS = Hardware set HC = Hardware clear                 |

bit 7-0 CNT<7:0>: I<sup>2</sup>C Byte Count Register bits

If receiving data,

decremented 8th SCL edge, when a new data byte is loaded into I2CxRXB

If transmitting data,

decremented 9th SCL edge, when a new data byte is moved from I2CxTXB CNTIF flag is set on 9th falling SCL edge, when I2CxCNT = 0. (Byte count cannot decrement past '0')

**Note 1:** It is recommended to write this register only when the module is IDLE (MMA = 0, SMA = 0) or when clock

stretching (CSTR =  $1 \parallel MDR = 1$ ).

| ADDWFC                                                                        | ADD W and CARRY bit to f                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |  |  |  |  |  |

|-------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|--|

| Syntax:                                                                       | ADDWFC f {,d {,a}}                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |  |  |  |  |  |

| Operands:                                                                     | 0 ≤ f ≤ 255<br>d ∈ [0,1]<br>a ∈ [0,1]                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |  |  |  |  |  |

| Operation:                                                                    | $(W) + (f) + (C) \rightarrow dest$                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |  |  |  |  |  |

| Status Affected:                                                              | N,OV, C, DC, Z                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |  |  |  |  |  |

| Encoding:                                                                     | 0010 00da ffff ffff                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |  |  |  |  |  |

|                                                                               | ory location 'f'. If 'd' is '0', the result is<br>placed in W. If 'd' is '1', the result is<br>placed in data memory location 'f'.<br>If 'a' is '0', the Access Bank is selected.<br>If 'a' is '1', the BSR is used to select the<br>GPR bank.<br>If 'a' is '0' and the extended instruction<br>set is enabled, this instruction operates<br>in Indexed Literal Offset Addressing<br>mode whenever $f \le 95$ (5Fh). See Sec-<br>tion 41.2.3 "Byte-Oriented and Bit-<br>Oriented Instructions in Indexed Lit-<br>eral Offset Mode" for details. |  |  |  |  |  |

| Words:                                                                        | 1                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |  |  |  |  |  |

| Cycles:                                                                       | 1                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |  |  |  |  |  |

| Q Cycle Activity:                                                             |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |  |  |  |  |  |

| Q1                                                                            | Q2 Q3 Q4                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |  |  |  |  |  |

| Decode                                                                        | ReadProcessWrite toregister 'f'Datadestination                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |  |  |  |  |  |

| Example:                                                                      | ADDWFC REG, 0, 1                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |  |  |  |  |  |

| Before Instruct<br>CARRY<br>REG<br>W<br>After Instructio<br>CARRY<br>REG<br>W | bit = 1<br>= 02h<br>= 4Dh<br>on                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |  |  |  |  |  |

|                    | DLW               | A    | AND literal with W                                                                  |         |                 |    |           |  |  |

|--------------------|-------------------|------|-------------------------------------------------------------------------------------|---------|-----------------|----|-----------|--|--|

| Syntax:            |                   |      | ANDLW k                                                                             |         |                 |    |           |  |  |

| Oper               | ands:             | 0    | $0 \leq k \leq 255$                                                                 |         |                 |    |           |  |  |

| Operation:         |                   |      | V) .AND.                                                                            | $k\toW$ |                 |    |           |  |  |

| Status Affected:   |                   |      | N, Z                                                                                |         |                 |    |           |  |  |

| Encoding:          |                   |      | 0000                                                                                | 1011    | kk}             | ck | kkkk      |  |  |

| Description:       |                   |      | The contents of W are AND'ed with the 8-bit literal 'k'. The result is placed in W. |         |                 |    |           |  |  |

| Words:             |                   |      |                                                                                     |         |                 |    |           |  |  |

| Cycle              | es:               | 1    |                                                                                     |         |                 |    |           |  |  |

| QC                 | ycle Activity:    |      |                                                                                     |         |                 |    |           |  |  |

|                    | Q1                |      | Q2                                                                                  | Q3      | Q3              |    | Q4        |  |  |

|                    | Decode I          |      | ad literal<br>'k'                                                                   |         | Process<br>Data |    | rite to W |  |  |

| Example:           |                   | A    | NDLW                                                                                | 05Fh    |                 |    |           |  |  |

| Before Instruction |                   | tion |                                                                                     |         |                 |    |           |  |  |

|                    | W                 | =    | A3h                                                                                 |         |                 |    |           |  |  |

|                    | After Instruction | on   |                                                                                     |         |                 |    |           |  |  |

|                    | W                 | =    | 03h                                                                                 |         |                 |    |           |  |  |

| BNC                           | Branch if Not Carry                                                                                                                                                                                                                                                                   |                             | BNN                                                                                                                                                                                                              |                | Branch if                | Not Negati                                            | ve                                                                                                                                                                                                                         |                 |                                                         |  |  |

|-------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------|--------------------------|-------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------|---------------------------------------------------------|--|--|

| Syntax:                       | BNC n                                                                                                                                                                                                                                                                                 |                             |                                                                                                                                                                                                                  | Synta          | x:                       | BNN n                                                 | BNN n                                                                                                                                                                                                                      |                 |                                                         |  |  |

| Operands:                     | -128 ≤ n ≤ 1                                                                                                                                                                                                                                                                          | 127                         |                                                                                                                                                                                                                  | Opera          | ands:                    | $-128 \le n \le 127$                                  |                                                                                                                                                                                                                            |                 |                                                         |  |  |

| Operation:                    | if CARRY b<br>(PC) + 2 + 2                                                                                                                                                                                                                                                            |                             |                                                                                                                                                                                                                  | Opera          | ation:                   | if NEGATIVE bit is '0' (PC) + 2 + 2n $\rightarrow$ PC |                                                                                                                                                                                                                            |                 |                                                         |  |  |

| Status Affected:              | None                                                                                                                                                                                                                                                                                  |                             |                                                                                                                                                                                                                  | Status         | Affected:                | None                                                  | None                                                                                                                                                                                                                       |                 |                                                         |  |  |

| Encoding:                     | 1110                                                                                                                                                                                                                                                                                  | 0011 nn:                    | nn nnnn                                                                                                                                                                                                          | Encod          | ding:                    | 1110                                                  | 0111 nr                                                                                                                                                                                                                    | inn nnnn        |                                                         |  |  |

| Description:                  | If the CARRY bit is '0', then the program<br>will branch.<br>The 2's complement number '2n' is<br>added to the PC. Since the PC will have<br>incremented to fetch the next<br>instruction, the new address will be<br>PC + 2 + 2n. This instruction is then a<br>2-cycle instruction. |                             | will branch.<br>The 2's complement number '2n' is<br>added to the PC. Since the PC will have<br>incremented to fetch the next<br>instruction, the new address will be<br>PC + 2 + 2n. This instruction is then a |                | Descr                    | iption:                                               | If the NEGATIVE bit is '0', the program will branch.<br>The 2's complement number added to the PC. Since the lincremented to fetch the new instruction, the new address PC + 2 + 2n. This instruction 2-cycle instruction. |                 | nber '2n' is<br>ne PC will have<br>next<br>ress will be |  |  |

| Words:                        | 1                                                                                                                                                                                                                                                                                     |                             |                                                                                                                                                                                                                  | Words          | 3:                       | 1                                                     |                                                                                                                                                                                                                            |                 |                                                         |  |  |

| Cycles:                       | 1(2)                                                                                                                                                                                                                                                                                  |                             |                                                                                                                                                                                                                  | Cycle          | s:                       | 1(2)                                                  |                                                                                                                                                                                                                            |                 |                                                         |  |  |

| Q Cycle Activity:<br>If Jump: |                                                                                                                                                                                                                                                                                       |                             |                                                                                                                                                                                                                  | Q Cy<br>If Jur | rcle Activity:<br>np:    |                                                       |                                                                                                                                                                                                                            |                 |                                                         |  |  |

| Q1                            | Q2                                                                                                                                                                                                                                                                                    | Q3                          | Q4                                                                                                                                                                                                               | _              | Q1                       | Q2                                                    | Q3                                                                                                                                                                                                                         | Q4              |                                                         |  |  |

| Decode                        | Read literal<br>'n'                                                                                                                                                                                                                                                                   | Process<br>Data             | Write to PC                                                                                                                                                                                                      |                | Decode                   | Read literal<br>'n'                                   | Process<br>Data                                                                                                                                                                                                            | Write to PC     |                                                         |  |  |

| No                            | No                                                                                                                                                                                                                                                                                    | No                          | No                                                                                                                                                                                                               |                | No                       | No                                                    | No                                                                                                                                                                                                                         | No              |                                                         |  |  |

| operation                     | operation                                                                                                                                                                                                                                                                             | operation                   | operation                                                                                                                                                                                                        |                | operation                | operation                                             | operation                                                                                                                                                                                                                  | operation       |                                                         |  |  |

| If No Jump:                   |                                                                                                                                                                                                                                                                                       |                             |                                                                                                                                                                                                                  | If No          | Jump:                    |                                                       |                                                                                                                                                                                                                            | •               |                                                         |  |  |

| Q1                            | Q2                                                                                                                                                                                                                                                                                    | Q3                          | Q4                                                                                                                                                                                                               | Г              | Q1                       | Q2                                                    | Q3                                                                                                                                                                                                                         | Q4              |                                                         |  |  |

| Decode                        | Read literal<br>'n'                                                                                                                                                                                                                                                                   | Process<br>Data             | No<br>operation                                                                                                                                                                                                  |                | Decode                   | Read literal<br>'n'                                   | Process<br>Data                                                                                                                                                                                                            | No<br>operation |                                                         |  |  |

| Example:                      | HERE                                                                                                                                                                                                                                                                                  | BNC Jump                    |                                                                                                                                                                                                                  | Exam           | <u>ple</u> :             | HERE                                                  | BNN Jumj                                                                                                                                                                                                                   | þ               |                                                         |  |  |

| Before Instru                 | ction                                                                                                                                                                                                                                                                                 |                             |                                                                                                                                                                                                                  | E              | Before Instruc           | ction                                                 |                                                                                                                                                                                                                            |                 |                                                         |  |  |

| PC<br>After Instruct          | ion                                                                                                                                                                                                                                                                                   | dress (HERE                 | )                                                                                                                                                                                                                | 4              | PC<br>After Instruction  | on                                                    | dress (HERE                                                                                                                                                                                                                | 2)              |                                                         |  |  |

| If CARF<br>PC<br>If CARF      | C = ad<br>RY = 1;                                                                                                                                                                                                                                                                     | dress (Jump)<br>dress (HERE |                                                                                                                                                                                                                  |                | If NEGA<br>PC<br>If NEGA | = ad                                                  | dress (Jum <u>r</u>                                                                                                                                                                                                        | ))              |                                                         |  |  |

| BRA               | ۱.          | Unconditional Branch                                                                                                                                                                                             |              |             |             |  |  |  |

|-------------------|-------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------|-------------|-------------|--|--|--|