Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

#### Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

E·XFI

| Details                    |                                                                             |

|----------------------------|-----------------------------------------------------------------------------|

| Product Status             | Active                                                                      |

| Core Processor             | PIC                                                                         |

| Core Size                  | 8-Bit                                                                       |

| Speed                      | 64MHz                                                                       |

| Connectivity               | I <sup>2</sup> C, LINbus, SPI, UART/USART                                   |

| Peripherals                | Brown-out Detect/Reset, DMA, HLVD, POR, PWM, WDT                            |

| Number of I/O              | 36                                                                          |

| Program Memory Size        | 64KB (32K x 16)                                                             |

| Program Memory Type        | FLASH                                                                       |

| EEPROM Size                | 1K x 8                                                                      |

| RAM Size                   | 4K x 8                                                                      |

| Voltage - Supply (Vcc/Vdd) | 2.3V ~ 5.5V                                                                 |

| Data Converters            | A/D 35x12b; D/A 1x5b                                                        |

| Oscillator Type            | Internal                                                                    |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                           |

| Mounting Type              | Surface Mount                                                               |

| Package / Case             | 44-VQFN Exposed Pad                                                         |

| Supplier Device Package    | 44-QFN (8x8)                                                                |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/pic18f46k42t-i-ml |

|                            |                                                                             |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

## **Table of Contents**

| 1.0 Device Overview                                                                          |     |

|----------------------------------------------------------------------------------------------|-----|

| 2.0 Guidelines for Getting Started with PIC18(L)F26/27/45/46/47/55/56/57K42 Microcontrollers | 22  |

| 3.0 PIC18 CPU                                                                                |     |

| 4.0 Memory Organization                                                                      | 32  |

| 5.0 Device Configuration                                                                     | 63  |

| 6.0 Resets                                                                                   |     |

| 7.0 Oscillator Module (with Fail-Safe Clock Monitor)                                         |     |

| 8.0 Reference Clock Output Module                                                            |     |

| 9.0 Interrupt Controller                                                                     |     |

| 10.0 Power-Saving Operation Modes                                                            | 168 |

| 11.0 Windowed Watchdog Timer (WWDT)                                                          |     |

| 12.0 8x8 Hardware Multiplier                                                                 |     |

| 13.0 Nonvolatile Memory (NVM) Control                                                        |     |

| 14.0 Cyclic Redundancy Check (CRC) Module with Memory Scanner                                |     |

| 15.0 Direct Memory Access (DMA)                                                              |     |

| 16.0 /O Ports                                                                                |     |

| 17.0 Peripheral Pin Select (PPS) Module                                                      |     |

| 18.0 Interrupt-on-Change                                                                     | 283 |

| 19.0 Peripheral Module Disable (PMD)                                                         |     |

| 20.0 Timer0 Module                                                                           | 296 |

| 21.0 Timer1/3/5 Module with Gate Control                                                     | 302 |

| 22.0 Timer2/4/6 Module                                                                       |     |

| 23.0Capture/Compare/PWM Module                                                               |     |

| 24.0 Pulse-Width Modulation (PWM)                                                            |     |

| 25.0Signal Measurement Timer (SMT)                                                           |     |

| 26.0 Complementary Waveform Generator (CWG) Module                                           | 403 |

| 27.0 Configurable Logic Cell (CLC)                                                           |     |

| 28.0 Numerically Controlled Oscillator (NCO) Module                                          |     |

| 29.0 Zero-Cross Detection (ZCD) Module                                                       |     |

| 30.0 Data Signal Modulator (DSM) Module                                                      |     |

| 31.0 Universal Asynchronous Receiver Transmitter (UART) With Protocol Support                | 472 |

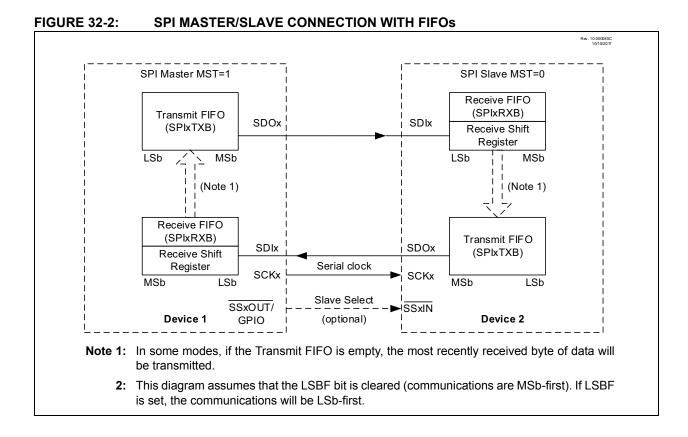

| 32.0 Serial Peripheral Interface (SPI) Module                                                |     |

| 33.0 I2C Module                                                                              |     |

| 34.0 Fixed Voltage Reference (FVR)                                                           | 594 |

| 35.0 Temperature Indicator Module                                                            |     |

| 36.0 Analog-to-Digital Converter with Computation (ADC2) Module                              |     |

| 37.0 5-Bit Digital-to-Analog Converter (DAC) Module                                          |     |

| 38.0 Comparator Module                                                                       |     |

| 39.0 High/Low-Voltage Detect (HLVD)                                                          |     |

| 40.0 In-Circuit Serial Programming™ (ICSP™)                                                  |     |

| 41.0 Instruction Set Summary                                                                 |     |

| 42.0 Register Summary                                                                        |     |

| 43.0 Development Support                                                                     |     |

| 44.0 Electrical Specifications                                                               |     |

| 45.0 DC and AC Characteristics Graphs and Tables                                             |     |

| 46.0 Packaging Information                                                                   |     |

### 9.7.1 ABORTING INTERRUPTS

If the last instruction before the interrupt controller vectors to the ISR from main routine clears the GIE, PIE or PIR bit associated with the interrupt, the controller executes one force NOP cycle before it returns to the main routine.

Figure 9-10 illustrates the sequence of events when a peripheral interrupt is asserted and then cleared on the last executed instruction cycle.

If the GIE, PIE or PIR bit associated with the interrupt is cleared prior to vectoring to the ISR, then the controller continues executing the main routine.

### FIGURE 9-10: INTERRUPT TIMING DIAGRAM - ABORTING INTERRUPTS

|                         |      |                         |      |            |            | Rev. 10-002269D<br>7/6/2018 |

|-------------------------|------|-------------------------|------|------------|------------|-----------------------------|

|                         |      | 2                       | 3    | 4          | 5          |                             |

| Instruction<br>Clock    |      |                         |      |            |            |                             |

| Program<br>Counter      | X    | X+2                     | X+2  | X+4        | X+6        |                             |

| Instruction<br>Register |      | Inst @ X <sup>(1)</sup> | FNOP | Inst @ X+2 | Inst @ X+4 |                             |

| Interrupt               |      |                         |      |            |            |                             |

| Routine                 | MAII | N                       | FNOP | X MA       | N          | $\rangle$                   |

|                         |      |                         |      |            |            |                             |

Note 1: Inst @ X clears the interrupt flag, Example BCF INTCON0, GIE.

Example 12-3 shows the sequence to do a 16 x 16 unsigned multiplication. Equation 12-1 shows the algorithm that is used. The 32-bit result is stored in four registers (RES<3:0>).

#### EQUATION 12-1: 16 x 16 UNSIGNED MULTIPLICATION ALGORITHM

| RES3:RES0 | = |                                          |

|-----------|---|------------------------------------------|

|           | = | $(ARG1H \bullet ARG2H \bullet 2^{16}) +$ |

|           |   | $(ARG1H \bullet ARG2L \bullet 2^8) +$    |

|           |   | $(ARG1L \bullet ARG2H \bullet 2^8) +$    |

|           |   | $(ARG1L \bullet ARG2L)$                  |

|           |   |                                          |

## EXAMPLE 12-3: 16 x 16 UNSIGNED MULTIPLY ROUTINE

|   | MOVF<br>MULWF |                                            | ; ARG1L * ARG2L-><br>; PRODH:PRODL<br>; |

|---|---------------|--------------------------------------------|-----------------------------------------|

| ; |               | PRODL, RESO                                | ;                                       |

|   | MOVF<br>MULWF | ARG1H, W<br>ARG2H                          | ; ARG1H * ARG2H-><br>; PRODH:PRODL      |

|   |               | PRODH, RES3<br>PRODL, RES2                 | ;                                       |

| ; | MOVF<br>MULWF | ARG1L, W<br>ARG2H                          | ; ARG1L * ARG2H-><br>; PRODH:PRODL      |

|   | MOVF          | PRODL, W<br>RES1, F<br>PRODH, W<br>RES2, F | ; Add cross<br>; products<br>;          |

| ; | CLRF          |                                            | ;;                                      |

|   | MULWF         |                                            | ;<br>; ARG1H * ARG2L-><br>; PRODH:PRODL |

|   | ADDWF<br>MOVF | - /                                        | ;<br>; Add cross<br>; products          |

|   | CLRF          | RES2, F<br>WREG<br>RES3, F                 | ;<br>;<br>;                             |

Example 12-4 shows the sequence to do a 16 x 16 signed multiply. Equation 12-2 shows the algorithm used. The 32-bit result is stored in four registers (RES<3:0>). To account for the sign bits of the arguments, the MSb for each argument pair is tested and the appropriate subtractions are done.

## EQUATION 12-2: 16 x 16 SIGNED MULTIPLICATION ALGORITHM

| RES3:RES0 = ARG1H:ARG1L • ARG2H:ARG2L                           |

|-----------------------------------------------------------------|

| $= (ARG1H \bullet ARG2H \bullet 2^{16}) +$                      |

| $(ARG1H \bullet ARG2L \bullet 2^8) +$                           |

| $(ARG1L \bullet ARG2H \bullet 2^8) +$                           |

| $(ARG1L \bullet ARG2L) +$                                       |

| $(-1 \bullet ARG2H < 7 > \bullet ARG1H:ARG1L \bullet 2^{16}) +$ |

| $(-1 \bullet ARG1H < 7 > \bullet ARG2H: ARG2L \bullet 2^{16})$  |

|                                                                 |

## EXAMPLE 12-4: 16 x 16 SIGNED MULTIPLY ROUTINE

|                | liitee        |                                        |

|----------------|---------------|----------------------------------------|

| MOVF           | ARG1L, W      |                                        |

| MULWF          | ARG2L         | ; ARG1L * ARG2L ->                     |

|                |               | ; PRODH:PRODL                          |

| MOVFF          | PRODH, RES1   | ;                                      |

| MOVFF          | PRODL, RESO   | ;                                      |

| ;              | ,             | ,                                      |

| MOVF           | ARG1H, W      |                                        |

| MULWF          |               | ; ARG1H * ARG2H ->                     |

| TIODWI         | 1110211       | ; PRODH:PRODL                          |

| MOVEE          | PRODH, RES3   | ;                                      |

| MOVFF          | PRODL, RES2   | ;                                      |

| ;              | 110000, 11002 | ,                                      |

| MOVF           | ARG1L, W      |                                        |

|                | ARG2H         | ; ARG1L * ARG2H ->                     |

| PIOLIWE        | ANGZII        | ; PRODH:PRODL                          |

| MOVF           | PRODL, W      | ;                                      |

| ADDWF          | RES1, F       | ,<br>; Add cross                       |

| MOVF           | PRODH, W      | ; products                             |

| ADDWFC         | RES2, F       | ; produces                             |

| CLRF           | WREG          |                                        |

|                | RES3, F       | ;                                      |

| ;              | KESS, F       | ,                                      |

|                | ARG1H, W      |                                        |

| MULWF          | ARG2L         | ;<br>; ARG1H * ARG2L ->                |

| PIOTIME        | ANGZU         | ; PRODH:PRODL                          |

| MOVF           | PRODL, W      | ;                                      |

| ADDWF          | RES1, F       | ,<br>; Add cross                       |

| MOVF           | PRODH, W      | ; products                             |

|                | RES2, F       | ;                                      |

| CLRF           | WREG          | ;                                      |

| -              | RES3, F       | ;                                      |

| ;              | 1000, 1       | ,                                      |

|                | ARG2H, 7      | ; ARG2H:ARG2L neg?                     |

| BRA            | SIGN ARG1     | ; ARG2H:ARG2L neg?<br>; no, check ARG1 |

| MOVF           | ARG1L, W      | ;                                      |

| SUBWF          | RES2          | ;                                      |

| MOVE           | ARG1H, W      | ;                                      |

| SUBWFB         |               | ,                                      |

| ;              | 1(100         |                                        |

| ,<br>SIGN ARG1 |               |                                        |

| BTFSS          | ARG1H, 7      | ; ARG1H:ARG1L neg?                     |

| BRA            | CONT CODE     | ; no, done                             |

| MOVE           | ARG2L, W      | ;                                      |

| SUBWF          | RES2          | ;                                      |

| MOVE           | ARG2H, W      | ;                                      |

| SUBWFB         |               | ,                                      |

|                | 1             |                                        |

| ,<br>CONT CODE |               |                                        |

| :              |               |                                        |

| •              |               |                                        |

| bit 7 Legend: R = Readable bit W = Writable bit U = Unimplemented bit, read as '0' u = Bit is unchanged x = Bit is unknown -n/n = Value at POR and BOR/Value at all other R '1' = Bit is set '0' = Bit is cleared HC = Bit is cleared by hardware bit 7 EN: Scanner Enable bit <sup>(1)</sup> 1 = Scanner is enabled 0 = Scanner trigger is disabled bit 6 TRIGEN: Scanner Trigger Isable bit <sup>(2)</sup> 1 = Scanner trigger is disabled Bit 5 SGG: Scanner GO bit <sup>(3, 4)</sup> 1 = When the CRC is ready, the Memory region set by the MREG bit will be accessed and data is to the CRC peripheral. 0 = Scanner operations will not occur bit 4-3 Unimplemented: Read as '0' bit 2 MREG: Scanner Burst Mode bit 1 BURSTMD: Scanner Burst Mode bit 1 BURSTMD: Scanner Burst Mode bit 1 BURSTMD: Scanner Burst Mode bit 1 = Memory access request to the CPU Arbiter is always true 0 = Memory access request to the CPU Arbiter is dependent on the CRC request and Trigger Refer Table 14-1. bit 0 BUSY: Scanner Busy Indicator bit 1 = Scanner cycle is in process 0 = Scanner cycle is oneyte (or never started) Note 1: Setting EN = 1 (SCANCON0 register) does not affect any other register content. 2: Scanner trigger selection can be set using the SCANTRIG register. 3: This bit can be cleared in software. It is cleared in hardware when LADR>HADR (and a data cycle is                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | R/W-0/0        | ) R/W-0/0                                                                                                                                                                                         | R/W/HC-0/0                                                                                                | U-0 | U-0              | R/W-0/0          | R/W-0/0           | R-0/0         |  |  |

|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------|-----|------------------|------------------|-------------------|---------------|--|--|

| Legend:         R = Readable bit       W = Writable bit       U = Unimplemented bit, read as '0'         u = Bit is unchanged       x = Bit is unknown       -n/n = Value at POR and BOR/Value at all other R         '1' = Bit is set       '0' = Bit is cleared       HC = Bit is cleared by hardware         bit 7       EN: Scanner Enable bit <sup>(1)</sup> 1 = Scanner is enabled         0 = Scanner is enabled       0 = Scanner trigger Enable bit <sup>(2)</sup> 1 = Scanner trigger is disabled       Refer Table 14-1.         bit 5       SGO: Scanner GO bit <sup>(3, 4)</sup> 1 = When the CRC is ready, the Memory region set by the MREG bit will be accessed and data is to the CRC peripheral.         0 = Scanner operations will not occur         bit 4-3       Unimplemented: Read as '0'         bit 2       MREG: Scanner Memory Region Select bit <sup>(2)</sup> 1 = Scanner address points to Drata EEPROM       0 = Scanner address points to Program Flash Memory         bit 1       BURSTMD: Scanner Burst Mode bit         1 = Memory access request to the CPU Arbiter is always true       0 = Memory access request to the CPU Arbiter is dependent on the CRC request and Trigger Refer Table 14-1.         bit 0       BUSY: Scanner Busy Indicator bit       1 = Scanner cycle is in process         0 = Scanner cycle is in process       0 = Scanner cycle is in process         0 = Scanner cycle is in process                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | EN             | TRIGEN                                                                                                                                                                                            | SGO                                                                                                       |     | _                | MREG             | BURSTMD           | BUSY          |  |  |

| R = Readable bit       W = Writable bit       U = Unimplemented bit, read as '0'         u = Bit is unchanged       x = Bit is unknown       -n/n = Value at POR and BOR/Value at all other R         '1' = Bit is set       '0' = Bit is cleared       HC = Bit is cleared by hardware         bit 7       EN: Scanner Enable bit <sup>(1)</sup> 1         1 = Scanner is enabled       0 = Scanner trigger Enable bit <sup>(2)</sup> 1 = Scanner trigger is enabled       0 = Scanner trigger is disabled         bit 5       SGO: Scanner Go bit <sup>(3, 4)</sup> 1 = When the CRC is ready, the Memory region set by the MREG bit will be accessed and data is to the CRC peripheral.         0 = Scanner operations will not occur         bit 4-3       Unimplemented: Read as '0'         bit 1       BURSTIND: Scanner Burst Mode bit         1 = Memory access request to the CPU Arbiter is always true         0 = Scanner ddress points to Data EEPROM         0 = Scanner address points to Program Flash Memory         bit 1       BURSTIND: Scanner Burst Mode bit         1 = Memory access request to the CPU Arbiter is always true         0 = Scanner cycle is in process         0 = Scanner cycle is in process         0 = Scanner cycle is in process         0 = Scanner trigger selection can be set using the SCANTRIG register.         3:       This bit can be cleared in software. It i                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | bit 7          | ·                                                                                                                                                                                                 |                                                                                                           |     | ·                | -                | •                 | bit           |  |  |

| <ul> <li>u = Bit is unchanged x = Bit is unknown -n/n = Value at POR and BOR/Value at all other R<br/>(1' = Bit is set '0' = Bit is cleared HC = Bit is cleared by hardware</li> <li>bit 7 EN: Scanner Enable bit<sup>(1)</sup><br/>1 = Scanner is enabled<br/>0 = Scanner is disabled<br/>bit 6 TRIGEN: Scanner Trigger Enable bit<sup>(2)</sup><br/>1 = Scanner trigger is disabled<br/>0 = Scanner trigger is disabled<br/>Refer Table 14-1.</li> <li>bit 5 SGO: Scanner GO bit<sup>(3, 4)</sup><br/>1 = When the CRC is ready, the Memory region set by the MREG bit will be accessed and data is<br/>to the CRC peripheral.<br/>0 = Scanner operations will not occur</li> <li>bit 4.3 Unimplemented: Read as '0'<br/>bit 2 MREG: Scanner Memory Region Select bit<sup>(2)</sup><br/>1 = Scanner address points to Data EEPROM<br/>0 = Scanner address points to Drogram Flash Memory</li> <li>bit 1 BURSTMD: Scanner Burst Mode bit<br/>1 = Memory access request to the CPU Arbiter is always true<br/>0 = Memory access request to the CPU Arbiter is dependent on the CRC request and Trigger<br/>Refer Table 14-1.</li> <li>bit 0 BUSY: Scanner Busy Indicator bit<br/>1 = Scanner cycle is in process<br/>0 = Scanner cycle is in process<br/>0 = Scanner cycle is compete (or never started)</li> <li>Note 1: Setting EN = 1 (SCANCON0 register) does not affect any other register content.</li> <li>2: Scanner trigger selection can be set using the SCANTRIG register.</li> <li>3: This bit can be cleared in software. It is cleared in hardware when LADR&gt;HADR (and a data cycle is</li> </ul>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | Legend:        |                                                                                                                                                                                                   |                                                                                                           |     |                  |                  |                   |               |  |  |

| '1' = Bit is set       '0' = Bit is cleared       HC = Bit is cleared by hardware         bit 7       EN: Scanner Enable bit <sup>(1)</sup> 1 = Scanner is disabled         0 = Scanner is disabled       0 = Scanner Trigger Enable bit <sup>(2)</sup> 1 = Scanner trigger is disabled       0 = Scanner trigger is disabled         0 = Scanner trigger is disabled       Refer Table 14-1.         bit 5       SGO: Scanner GO bit <sup>(3, 4)</sup> 1 = When the CRC is ready, the Memory region set by the MREG bit will be accessed and data is to the CRC peripheral.         0 = Scanner operations will not occur         bit 4-3       Unimplemented: Read as '0'         bit 2       MREG: Scanner Memory Region Select bit <sup>(2)</sup> 1 = Scanner address points to Data EEPROM         0 = Scanner address points to Program Flash Memory         bit 1       BURSTMD: Scanner Burst Mode bit         1 = Memory access request to the CPU Arbiter is always true         0 = Memory access request to the CPU Arbiter is dependent on the CRC request and Trigger         Refer Table 14-1.         bit 0       BUSY: Scanner Busy Indicator bit         1 = Scanner cycle is in process       0 = Scanner cycle is compet (or never started)         Note 1:       Setting EN = 1 (SCANCON0 register) does not affect any other register content.         2:       Scanner trigger selection can be set using the SCANTRIG regist                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | R = Reada      | ble bit                                                                                                                                                                                           | W = Writable bi                                                                                           | t   | U = Unimple      | mented bit, rea  | d as '0'          |               |  |  |

| <ul> <li>bit 7 EN: Scanner Enable bit<sup>(1)</sup> <ol> <li>= Scanner is enabled</li> <li>= Scanner is disabled</li> </ol> </li> <li>bit 6 TRIGEN: Scanner Trigger Enable bit<sup>(2)</sup> <ol> <li>= Scanner trigger is enabled</li> <li>= Scanner trigger is disabled</li> <li>Refer Table 14-1.</li> </ol> </li> <li>bit 5 SGO: Scanner GO bit<sup>(3, 4)</sup> <ol> <li>= When the CRC is ready, the Memory region set by the MREG bit will be accessed and data is to the CRC peripheral.</li> <li>= Scanner operations will not occur</li> </ol> </li> <li>bit 4-3 Unimplemented: Read as '0'</li> <li>bit 2 MREG: Scanner Memory Region Select bit<sup>(2)</sup> <ol> <li>= Scanner address points to Data EEPROM</li> <li>= Scanner address points to Program Flash Memory</li> <li>bit 1 BURSTMD: Scanner Burst Mode bit</li> <li>= Memory access request to the CPU Arbiter is always true</li> <li>= Memory access request to the CPU Arbiter is dependent on the CRC request and Trigger Refer Table 14-1.</li> </ol> </li> <li>bit 0 BUSY: Scanner Busy Indicator bit</li> <li>= Scanner cycle is in process <ol> <li>= Scanner cycle is compete (or never started)</li> </ol> </li> <li>Note 1: Setting EN = 1 (SCANCON0 register) does not affect any other register content.</li> <li>2: Scanner trigger selection can be set using the SCANTRIG register.</li> <li>3: This bit can be cleared in software. It is cleared in hardware when LADR&gt;HADR (and a data cycle is compete for the set of the compete of the compete of the compete of the compete of the competer of the</li></ul> | u = Bit is u   | nchanged                                                                                                                                                                                          | x = Bit is unkno                                                                                          | wn  | -n/n = Value     | at POR and BC    | R/Value at all ot | her Resets    |  |  |

| <ul> <li>1 = Scanner is enabled</li> <li>0 = Scanner is disabled</li> <li>bit 6</li> <li>TRIGEN: Scanner Trigger Enable bit<sup>(2)</sup></li> <li>1 = Scanner trigger is enabled</li> <li>0 = Scanner trigger is disabled</li> <li>Refer Table 14-1.</li> <li>bit 5</li> <li>SGO: Scanner GO bit<sup>(3, 4)</sup></li> <li>1 = When the CRC is ready, the Memory region set by the MREG bit will be accessed and data is to the CRC peripheral.</li> <li>0 = Scanner operations will not occur</li> <li>bit 4-3</li> <li>Unimplemented: Read as '0'</li> <li>bit 2</li> <li>MREG: Scanner Memory Region Select bit<sup>(2)</sup></li> <li>1 = Scanner address points to Data EEPROM</li> <li>0 = Scanner address points to Program Flash Memory</li> <li>bit 1</li> <li>BURSTMD: Scanner Burst Mode bit</li> <li>1 = Memory access request to the CPU Arbiter is always true</li> <li>0 = Memory access request to the CPU Arbiter is dependent on the CRC request and Trigger Refer Table 14-1.</li> <li>bit 0</li> <li>BUSY: Scanner Busy Indicator bit</li> <li>1 = Scanner cycle is in process</li> <li>0 = Scanner cycle is compete (or never started)</li> <li>Note 1: Setting EN = 1 (SCANCON0 register) does not affect any other register content.</li> <li>2: Scanner trigger selection can be set using the SCANTRIG register.</li> <li>3: This bit can be cleared in software. It is cleared in hardware when LADR&gt;HADR (and a data cycle is</li> </ul>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | '1' = Bit is s | set                                                                                                                                                                                               | '0' = Bit is clear                                                                                        | ed  | HC = Bit is c    | leared by hardv  | vare              |               |  |  |

| <ul> <li>1 = Scanner trigger is enabled</li> <li>0 = Scanner trigger is disabled</li> <li>Refer Table 14-1.</li> <li>bit 5</li> <li>SGO: Scanner GO bit<sup>(3, 4)</sup></li> <li>1 = When the CRC is ready, the Memory region set by the MREG bit will be accessed and data is to the CRC peripheral.</li> <li>0 = Scanner operations will not occur</li> <li>bit 4-3</li> <li>Unimplemented: Read as '0'</li> <li>bit 2</li> <li>MREG: Scanner Memory Region Select bit<sup>(2)</sup></li> <li>1 = Scanner address points to Data EEPROM</li> <li>0 = Scanner address points to Program Flash Memory</li> <li>bit 1</li> <li>BURSTMD: Scanner Burst Mode bit</li> <li>1 = Memory access request to the CPU Arbiter is always true</li> <li>0 = Memory access request to the CPU Arbiter is dependent on the CRC request and Trigger Refer Table 14-1.</li> <li>bit 0</li> <li>BUSY: Scanner Busy Indicator bit</li> <li>1 = Scanner cycle is in process</li> <li>0 = Scanner cycle is compete (or never started)</li> </ul> Note 1: Setting EN = 1 (SCANCON0 register) does not affect any other register content. 2: Scanner trigger selection can be set using the SCANTRIG register. 3: This bit can be cleared in software. It is cleared in hardware when LADR>HADR (and a data cycle is                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | bit 7          | 1 = Scanner                                                                                                                                                                                       | is enabled                                                                                                |     |                  |                  |                   |               |  |  |

| <ul> <li>1 = When the CRC is ready, the Memory region set by the MREG bit will be accessed and data is to the CRC peripheral.</li> <li>0 = Scanner operations will not occur</li> <li>bit 4-3 Unimplemented: Read as '0'</li> <li>bit 2 MREG: Scanner Memory Region Select bit<sup>(2)</sup></li> <li>1 = Scanner address points to Data EEPROM</li> <li>0 = Scanner address points to Program Flash Memory</li> <li>bit 1 BURSTMD: Scanner Burst Mode bit</li> <li>1 = Memory access request to the CPU Arbiter is always true</li> <li>0 = Memory access request to the CPU Arbiter is dependent on the CRC request and Trigger Refer Table 14-1.</li> <li>bit 0 BUSY: Scanner Busy Indicator bit</li> <li>1 = Scanner cycle is in process</li> <li>0 = Scanner cycle is compete (or never started)</li> <li>Note 1: Setting EN = 1 (SCANCON0 register) does not affect any other register content.</li> <li>2: Scanner trigger selection can be set using the SCANTRIG register.</li> <li>3: This bit can be cleared in software. It is cleared in hardware when LADR&gt;HADR (and a data cycle is is</li> </ul>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | bit 6          | 1 = Scanner<br>0 = Scanner                                                                                                                                                                        | trigger is enabled<br>trigger is disabled                                                                 |     |                  |                  |                   |               |  |  |

| <ul> <li>bit 2 MREG: Scanner Memory Region Select bit<sup>(2)</sup> <ol> <li>= Scanner address points to Data EEPROM</li> <li>= Scanner address points to Program Flash Memory</li> </ol> </li> <li>bit 1 BURSTMD: Scanner Burst Mode bit <ol> <li>= Memory access request to the CPU Arbiter is always true</li> <li>= Memory access request to the CPU Arbiter is dependent on the CRC request and Trigger Refer Table 14-1.</li> </ol> </li> <li>bit 0 BUSY: Scanner Busy Indicator bit <ol> <li>= Scanner cycle is in process</li> <li>= Scanner cycle is compete (or never started)</li> </ol> </li> <li>Note 1: Setting EN = 1 (SCANCON0 register) does not affect any other register content.</li> <li>Scanner trigger selection can be set using the SCANTRIG register.</li> <li>This bit can be cleared in software. It is cleared in hardware when LADR&gt;HADR (and a data cycle is in process)</li> </ul>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | bit 5          | 1 = When the to the C                                                                                                                                                                             | e CRC is ready, the<br>RC peripheral.                                                                     |     | egion set by the | MREG bit will be | e accessed and o  | lata is passe |  |  |

| <ul> <li>1 = Scanner address points to Data EEPROM         <ul> <li>9 = Scanner address points to Program Flash Memory</li> </ul> </li> <li>bit 1 BURSTMD: Scanner Burst Mode bit         <ul> <li>1 = Memory access request to the CPU Arbiter is always true</li> <li>0 = Memory access request to the CPU Arbiter is dependent on the CRC request and Trigger Refer Table 14-1.</li> </ul> </li> <li>bit 0 BUSY: Scanner Busy Indicator bit         <ul> <li>1 = Scanner cycle is in process</li> <li>0 = Scanner cycle is compete (or never started)</li> </ul> </li> <li>Note 1: Setting EN = 1 (SCANCON0 register) does not affect any other register content.</li> <li>2: Scanner trigger selection can be set using the SCANTRIG register.</li> <li>3: This bit can be cleared in software. It is cleared in hardware when LADR&gt;HADR (and a data cycle is in process)</li> </ul>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | bit 4-3        | Unimpleme                                                                                                                                                                                         | nted: Read as '0'                                                                                         |     |                  |                  |                   |               |  |  |

| <ul> <li>1 = Memory access request to the CPU Arbiter is always true         <ul> <li>a Memory access request to the CPU Arbiter is dependent on the CRC request and Trigger Refer Table 14-1.</li> </ul> </li> <li>bit 0 BUSY: Scanner Busy Indicator bit         <ul> <li>1 = Scanner cycle is in process</li> <li>0 = Scanner cycle is compete (or never started)</li> </ul> </li> <li>Note 1: Setting EN = 1 (SCANCON0 register) does not affect any other register content.</li> <li>2: Scanner trigger selection can be set using the SCANTRIG register.</li> <li>3: This bit can be cleared in software. It is cleared in hardware when LADR&gt;HADR (and a data cycle is in process)</li> </ul>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | bit 2          | 1 = Scanner                                                                                                                                                                                       | <b>MREG:</b> Scanner Memory Region Select bit <sup>(2)</sup><br>1 = Scanner address points to Data EEPROM |     |                  |                  |                   |               |  |  |

| <ol> <li>1 = Scanner cycle is in process         <ul> <li>0 = Scanner cycle is compete (or never started)</li> </ul> </li> <li>Note 1: Setting EN = 1 (SCANCON0 register) does not affect any other register content.         <ul> <li>2: Scanner trigger selection can be set using the SCANTRIG register.</li> <li>3: This bit can be cleared in software. It is cleared in hardware when LADR&gt;HADR (and a data cycle is</li> </ul> </li> </ol>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | bit 1          | <b>BURSTMD:</b> Scanner Burst Mode bit<br>1 = Memory access request to the CPU Arbiter is always true<br>0 = Memory access request to the CPU Arbiter is dependent on the CRC request and Trigger |                                                                                                           |     |                  |                  |                   |               |  |  |

| <ol> <li>Scanner trigger selection can be set using the SCANTRIG register.</li> <li>This bit can be cleared in software. It is cleared in hardware when LADR&gt;HADR (and a data cycle is</li> </ol>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | bit 0          | 1 = Scanner                                                                                                                                                                                       | cycle is in proces                                                                                        | S   | tarted)          |                  |                   |               |  |  |

| occurring) or when CRCGO = 0 (CRCCON0 register).                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 2:<br>3:       | Setting EN = 1 (SCANCON0 register) does not affect any other register content.                                                                                                                    |                                                                                                           |     |                  |                  |                   |               |  |  |

## REGISTER 14-11: SCANCONO: SCANNER ACCESS CONTROL REGISTER 0

- - 4: CRCEN and CRCGO bits (CRCCON0 register) must be set before setting the SGO bit.

## 17.0 PERIPHERAL PIN SELECT (PPS) MODULE

The Peripheral Pin Select (PPS) module connects peripheral inputs and outputs to the device I/O pins. Only digital signals are included in the selections. All analog inputs and outputs remain fixed to their assigned pins. Input and output selections are independent as shown in the simplified block diagram Figure 17-1.

The peripheral input is selected with the peripheral xxxPPS register (Register 17-1), and the peripheral output is selected with the PORT RxyPPS register (Register 17-2). For example, to select PORTC<7> as the UART1 RX input, set U1RXPPS to 0b1 0111, and to select PORTC<6> as the UART1 TX output set RC6PPS to 0b01 0011.

## 17.1 PPS Inputs

Each peripheral has a PPS register with which the inputs to the peripheral are selected. Inputs include the device pins.

Multiple peripherals can operate from the same source simultaneously. Port reads always return the pin level regardless of peripheral PPS selection. If a pin also has analog functions associated, the ANSEL bit for that pin must be cleared to enable the digital input buffer.

Although every peripheral has its own PPS input selection register, the selections are identical for every peripheral as shown in Register 17-1.

| Note: | The notation "xxx" in the register name is    |

|-------|-----------------------------------------------|

|       | a place holder for the peripheral identifier. |

|       | For example, INT0PPS.                         |

## 17.2 PPS Outputs

Each I/O pin has a PPS register with which the pin output source is selected. With few exceptions, the port TRIS control associated with that pin retains control over the pin output driver. Peripherals that control the pin output driver as part of the peripheral operation will override the TRIS control as needed. These peripherals include:

• UART

Although every pin has its own PPS peripheral selection register, the selections are identical for every pin as shown in Register 17-2.

**Note:** The notation "Rxy" is a place holder for the pin identifier. For example, RA0PPS.

## 20.3 Programmable Prescaler

A software programmable prescaler is available for exclusive use with Timer0. There are 16 prescaler options for Timer0 ranging in powers of two from 1:1 to 1:32768. The prescaler values are selected using the CKPS<3:0> bits of the T0CON1 register.

The prescaler is not directly readable or writable. Clearing the prescaler register can be done by writing to the TMR0L register or to the T0CON0/T0CON1 register or by any Reset.

## 20.4 Programmable Postscaler

A software programmable postscaler (output divider) is available for exclusive use with Timer0. There are 16 postscaler options for Timer0 ranging from 1:1 to 1:16. The postscaler values are selected using the OUTPS bits of the T0CON0 register.

The postscaler is not directly readable or writable. Clearing the postscaler register can be done by writing to the TMR0L register or to the T0CON0/T0CON1 register or by any Reset.

## 20.5 Operation During Sleep

When operating synchronously, Timer0 will halt. When operating asynchronously, Timer0 will continue to increment and wake the device from Sleep (if Timer0 interrupts are enabled) provided that the input clock source is active.

## 20.6 Timer0 Interrupts

The Timer0 interrupt flag bit (TMR0IF) is set when either of the following conditions occur:

- 8-bit TMR0L matches the TMR0H value

- 16-bit TMR0 rolls over from 'FFFFh'

When the postscaler bits (OUTPS) are set to 1:1 operation (no division), the T0IF flag bit will be set with every TMR0 match or rollover. In general, the TMR0IF flag bit will be set every OUTPS +1 matches or rollovers.

If Timer0 interrupts are enabled (TMR0IE bit of the PIE3 register = '1'), the CPU will be interrupted and the device may wake from Sleep (see Section 20.2 "Clock Source Selection" for more details).

## 20.7 Timer0 Output

The Timer0 output can be routed to any I/O pin via the RxyPPS output selection register (see Section **17.0 "Peripheral Pin Select (PPS) Module**" for additional information). The Timer0 output can also be used by other peripherals, such as the auto-conversion trigger of the Analog-to-Digital Converter. Finally, the Timer0 output can be monitored through software via the Timer0 output bit (OUT) of the T0CON0 register (Register 20-1).

TMR0\_out will be a pulse of one postscaled clock period when a match occurs between TMR0L and PR0 (Period register for TMR0) in 8-bit mode, or when TMR0 rolls over in 16-bit mode. The Timer0 output is a 50% duty cycle that toggles on each TMR0\_out rising clock edge.

| REGISTER      | 21-2: IXGC                                                                                                                                                                                                         | UN: HMER                                                                                                                                                                                                                                     | X GATE CO                        | NIROL REGIS                                                                       | IER                                |                  |       |  |  |

|---------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------|-----------------------------------------------------------------------------------|------------------------------------|------------------|-------|--|--|

| R/W-0/u       | R/W-0/u                                                                                                                                                                                                            | R/W-0/u                                                                                                                                                                                                                                      | R/W-0/u                          | R/W-0/u                                                                           | R-x                                | U-0              | U-0   |  |  |

| GE            | GPOL                                                                                                                                                                                                               | GTM                                                                                                                                                                                                                                          | GSPM                             | GGO/DONE                                                                          | GVAL                               | _                | _     |  |  |

| bit 7         |                                                                                                                                                                                                                    |                                                                                                                                                                                                                                              |                                  |                                                                                   |                                    |                  | bit 0 |  |  |

|               |                                                                                                                                                                                                                    |                                                                                                                                                                                                                                              |                                  |                                                                                   |                                    |                  |       |  |  |

| Legend:       |                                                                                                                                                                                                                    |                                                                                                                                                                                                                                              |                                  |                                                                                   |                                    |                  |       |  |  |

| R = Readable  | e bit                                                                                                                                                                                                              | W = Writable                                                                                                                                                                                                                                 | bit                              | U = Unimpleme                                                                     | nted bit, read as                  | s 'O'            |       |  |  |

| -n = Value at | POR                                                                                                                                                                                                                | '1' = Bit is se                                                                                                                                                                                                                              | t                                | '0' = Bit is cleare                                                               | ed                                 | x = Bit is unkno | own   |  |  |

| bit 7         | If TMRxON =           1 =         Timerx           0 =         Timerx           If TMRxON =                                                                                                                        | counting is co<br>is always cour                                                                                                                                                                                                             | ntrolled by th                   | e Timerx gate fur                                                                 | nction                             |                  |       |  |  |

| bit 6         | 1 = Timerx                                                                                                                                                                                                         | <b>GPOL:</b> Timerx Gate Polarity bit<br>1 = Timerx gate is active-high (Timerx counts when gate is high)                                                                                                                                    |                                  |                                                                                   |                                    |                  |       |  |  |

| bit 5         | <b>GTM:</b> Timerx Gate Toggle Mode bit<br>1 = Timerx Gate Toggle mode is enabled<br>0 = Timerx Gate Toggle mode is disabled and Toggle flip-flop is cleared<br>Timerx Gate Flip Flop Toggles on every rising edge |                                                                                                                                                                                                                                              |                                  |                                                                                   |                                    |                  |       |  |  |

| bit 4         | 1 = Timerx                                                                                                                                                                                                         | rx Gate Single<br>Gate Single P<br>Gate Single P                                                                                                                                                                                             | ulse mode is                     | enabled and is co                                                                 | ontrolling Timer                   | gate)            |       |  |  |

| bit 3         | 1 = Timerx<br>0 = Timerx                                                                                                                                                                                           | Gate Single P<br>Gate Single P                                                                                                                                                                                                               | ulse Acquisiti<br>ulse Acquisiti | Acquisition Status<br>on is ready, waitii<br>on has completed<br>(GSPM is cleared | ng for an edge<br>d or has not bee | n started.       |       |  |  |

| bit 2         | Indicates the                                                                                                                                                                                                      | This bit is automatically cleared when TxGSPM is cleared.<br><b>GVAL:</b> Timerx Gate Current State bit<br>Indicates the current state of the Timerx gate that could be provided to TMRxH:TMRxL<br>Unaffected by Timerx Gate Enable (TMRxGE) |                                  |                                                                                   |                                    |                  |       |  |  |

| bit 1-0       | Unimpleme                                                                                                                                                                                                          | nted: Read as                                                                                                                                                                                                                                | ʻ0 <b>'</b>                      |                                                                                   |                                    |                  |       |  |  |

|               |                                                                                                                                                                                                                    |                                                                                                                                                                                                                                              |                                  |                                                                                   |                                    |                  |       |  |  |

## REGISTER 21-2: TxGCON: TIMERx GATE CONTROL REGISTER

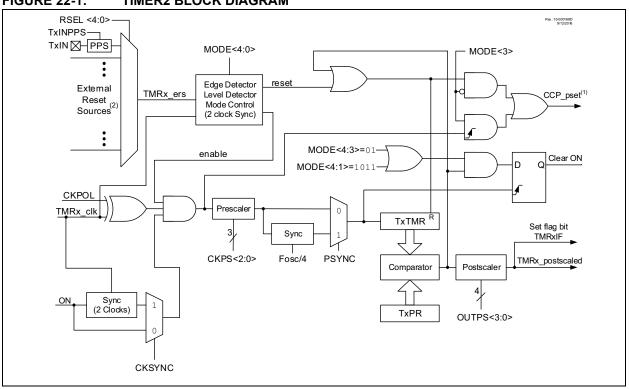

## 22.0 TIMER2/4/6 MODULE

The Timer2/4/6 modules are 8-bit timers that can operate as free-running period counters or in conjunction with external signals that control start, run, freeze, and reset operation in One-Shot and Monostable modes of operation. Sophisticated waveform control such as pulse density modulation are possible by combining the operation of these timers with other internal peripherals such as the comparators and CCP modules. Features of the timer include:

- 8-bit timer register

- 8-bit period register

- Selectable external hardware timer resets

- Programmable prescaler (1:1 to 1:128)

- Programmable postscaler (1:1 to 1:16)

- Selectable synchronous/asynchronous operation

- Alternate clock sources

- Interrupt on period

- Three modes of operation:

- Free Running Period

- One-Shot

- Monostable

See Figure 22-1 for a block diagram of Timer2. See Figure 22-2 for the clock source block diagram.

**Note:** Three identical Timer2 modules are implemented on this device. The timers are named Timer2, Timer4, and Timer6. All references to Timer2 apply as well to Timer4 and Timer6. All references to T2PR apply as well to T4PR and T6PR.

### FIGURE 22-1: TIMER2 BLOCK DIAGRAM

## 25.6.4 HIGH AND LOW MEASURE MODE

This mode measures the high and low pulse time of the SMTSIGx relative to the SMT clock. It begins incrementing the SMT1TMR on a rising edge on the SMTSIGx input, then updates the SMT1CPW register with the value and resets the SMT1TMR on a falling edge, starting to increment again. Upon observing another rising edge, it updates the SMT1CPR register with its current value and once again resets the SMT1TMR value and begins incrementing again. See Figure 25-8 and Figure 25-9.

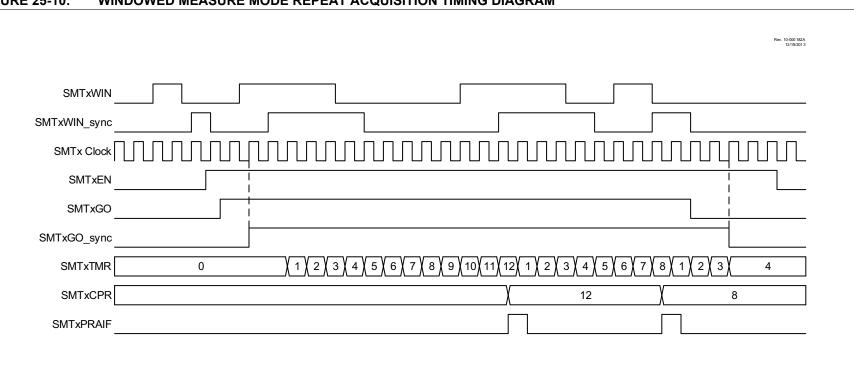

### 25.6.5 WINDOWED MEASURE MODE

This mode measures the window duration of the SMTWINx input of the SMT. It begins incrementing the timer on a rising edge of the SMTWINx input and updates the SMT1CPR register with the value of the timer and resets the timer on a second rising edge. See Figure 25-10 and Figure 25-11.

FIGURE 2

PIC18(L)F26/27/45/46/47/55/56/57K42

## 25.7 Interrupts

The SMT can trigger an interrupt under three different conditions:

- PW Acquisition Complete

- PR Acquisition Complete

- Counter Period Match

The interrupts are controlled by the PIR and PIE registers of the device.

#### 25.7.1 PW AND PR ACQUISITION INTERRUPTS

The SMT can trigger interrupts whenever it updates the SMT1CPW and SMT1CPR registers, the circumstances for which are dependent on the SMT mode, and are discussed in each mode's specific section. The SMT1CPW interrupt is controlled by SMT1PWAIF and SMT1PWAIE bits in the respective PIR and PIE registers. The SMT1CPR interrupt is controlled by the SMT1PRAIF and SMT1PRAIE bits, also located in the respective PIR and PIE registers.

In synchronous SMT modes, the interrupt trigger is synchronized to the SMT1CLK. In Asynchronous modes, the interrupt trigger is asynchronous. In either mode, once triggered, the interrupt will be synchronized to the CPU clock.

### 25.7.2 COUNTER PERIOD MATCH INTERRUPT

As described in Section 25.1.2 "Period Match interrupt", the SMT will also interrupt upon SMT1TMR, matching SMT1PR with its period match limit functionality described in Section 25.3 "Halt Operation". The period match interrupt is controlled by SMT1IF and SMT1IE, located in the respective PIR and PIE registers.

## 28.8 NCO Control Registers

|                                                                                                                            | 0-1. NCOT                                                                                                                                   |                  |                 |                |                  |                  |              |

|----------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------|------------------|-----------------|----------------|------------------|------------------|--------------|

| R/W-0/0                                                                                                                    | U-0                                                                                                                                         | R-0/0            | R/W-0/0         | U-0            | U-0              | U-0              | R/W-0/0      |

| EN                                                                                                                         | _                                                                                                                                           | OUT              | POL             | —              | _                |                  | PFM          |

| bit 7                                                                                                                      |                                                                                                                                             | •                |                 |                |                  |                  | bit 0        |

|                                                                                                                            |                                                                                                                                             |                  |                 |                |                  |                  |              |