#### Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

## Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

### Details

| Product Status             | Active                                                                    |

|----------------------------|---------------------------------------------------------------------------|

| Core Processor             | PIC                                                                       |

| Core Size                  | 8-Bit                                                                     |

| Speed                      | 64MHz                                                                     |

| Connectivity               | I <sup>2</sup> C, LINbus, SPI, UART/USART                                 |

| Peripherals                | Brown-out Detect/Reset, DMA, HLVD, POR, PWM, WDT                          |

| Number of I/O              | 36                                                                        |

| Program Memory Size        | 128KB (64K x 16)                                                          |

| Program Memory Type        | FLASH                                                                     |

| EEPROM Size                | 1K x 8                                                                    |

| RAM Size                   | 8K x 8                                                                    |

| Voltage - Supply (Vcc/Vdd) | 2.3V ~ 5.5V                                                               |

| Data Converters            | A/D 35x12b; D/A 1x5b                                                      |

| Oscillator Type            | Internal                                                                  |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                         |

| Mounting Type              | Through Hole                                                              |

| Package / Case             | 40-DIP (0.600", 15.24mm)                                                  |

| Supplier Device Package    | 40-PDIP                                                                   |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/pic18f47k42-i-p |

|                            |                                                                           |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

# 4.5 Data Memory Organization

Data memory in PIC18F26/27/45/46/47/55/56/57K42 devices is implemented as static RAM. Each register in the data memory has a 14-bit address, allowing up to 16384 bytes of data memory. The memory space is divided into 64 banks that contain 256 bytes each. Figure 4-3 shows the data memory organization for the PIC18F26/27/45/46/47/55/56/57K42 devices in this data sheet.

The data memory contains Special Function Registers (SFRs) and General Purpose Registers (GPRs). The SFRs are used for control and status of the controller and peripheral functions, while GPRs are used for data storage and scratchpad operations in the user's application. Any read of an unimplemented location will read as '0's.

The instruction set and architecture allow operations across all banks. The entire data memory may be accessed by Direct, Indirect or Indexed Addressing modes. Addressing modes are discussed later in this subsection.

To ensure that commonly used registers (select SFRs and GPRs) can be accessed in a single cycle, PIC18 devices implement an Access Bank. This is a 256-byte memory space that provides fast access to some SFRs and the lower portion of GPR Bank 0 without using the Bank Select Register (BSR). Section 4.5.4 "Access Bank" provides a detailed description of the Access RAM.

## 4.5.1 BANK SELECT REGISTER (BSR)

Large areas of data memory require an efficient addressing scheme to make rapid access to any address possible. Ideally, this means that an entire address does not need to be provided for each read or write operation. For PIC18 devices, this is accomplished with a RAM banking scheme. This divides the memory space into 64 contiguous banks of 256 bytes. Depending on the instruction, each location can be addressed directly by its full 14-bit address, or an 8-bit low-order address and a 6-bit Bank Select Register.

This SFR holds the six Most Significant bits of a location address; the instruction itself includes the eight Least Significant bits. Only the six lower bits of the BSR are implemented (BSR<5:0>). The upper two bits are unused; they will always read '0' and cannot be written to. The BSR can be loaded directly by using the MOVLB instruction.

The value of the BSR indicates the bank in data memory; the eight bits in the instruction show the location in the bank and can be thought of as an offset from the bank's lower boundary. The relationship between the BSR's value and the bank division in data memory is shown in Figure 4-3.

Since up to 64 registers may share the same low-order address, the user must always be careful to ensure that the proper bank is selected before performing a data read or write. For example, writing what should be program data to an 8-bit address of F9h while the BSR is 3Fh will end up corrupting the program counter.

While any bank can be selected, only those banks that are actually implemented can be read or written to. Writes to unimplemented banks are ignored, while reads from unimplemented banks will return '0's. Even so, the STATUS register will still be affected as if the operation was successful. The data memory maps in Figure 4-3 indicate which banks are implemented.

| Bank              | BSR<5:0>                | Address<br>addr<7:0> | PIC18(L)F45K42<br>PIC18(L)F55K42 | PIC18(L)F26K42<br>PIC18(L)F46K42<br>PIC18(L)F56K42 | PIC18(L)F27K42<br>PIC18(L)F47K42<br>PIC18(L)F57K42 | Address<br>addr<13:0>   |                |

|-------------------|-------------------------|----------------------|----------------------------------|----------------------------------------------------|----------------------------------------------------|-------------------------|----------------|

|                   |                         | 00h                  | Access RAM                       | Access RAM                                         | Access RAM                                         | 0000h<br>005Fh          |                |

| Bank 0            | 00 0000                 | FFh                  | GPR                              | GPR                                                | GPR                                                | 0060h<br>00FFh          |                |

| Bank 1            | 00 0001                 | 00h<br>FFh           |                                  |                                                    |                                                    | 0100h                   |                |

| Bank 2            | 00 0010                 | 00h<br>FFh           | GPR                              | GPR                                                | GPR                                                | •                       |                |

|                   |                         | 00h                  | GPR                              | GPR                                                | GPR                                                |                         |                |

| Bank 3            | 00 0011                 | ·<br>FFh             |                                  |                                                    |                                                    | 03FFh                   | Virtual Bank   |

|                   | 00 0100                 | 00h                  |                                  |                                                    |                                                    | 0400h<br>•              | Access RAM 00h |

| Banks<br>4 to 7   | 00 0111                 | :<br>FFh             | GPR                              | GPR                                                | GPR                                                | :<br>07FFh              | SFR 60h        |

|                   |                         | 00h                  |                                  |                                                    |                                                    | 0800h                   | / FFh          |

| Banks<br>8 to 15  | 00 1000<br>-<br>00 1111 | :                    |                                  | GPR                                                |                                                    | •                       |                |

|                   | 00 1111                 | FFh<br>00h           |                                  |                                                    | GPR                                                | 0FFFh<br>1000h          | _ //           |

| Banks<br>16 to 31 | 01 0000                 | :                    | Unimplemented                    |                                                    |                                                    |                         |                |

|                   | 01 1111                 | FFh<br>00h           |                                  | Unimplemented                                      |                                                    | 1FFFh<br>2000h          |                |

| Banks             | 10 0000                 |                      |                                  |                                                    | Unimplemented                                      |                         |                |

| 32 to 55          | -<br>11 0111            | FFh                  |                                  |                                                    |                                                    | 37FFh                   |                |

| Banks             | 11 1000                 | 00h                  |                                  |                                                    |                                                    | 3800h<br>•              |                |

| Banks<br>56 to 62 | 11 1110                 | :<br>FFh             | SFR                              | SFR                                                | SFR                                                | ·<br>3EFFh              |                |

| Bank 63           | 11 1111                 | 00h                  | SFR                              | SFR                                                | SFR                                                | 3800h<br>3EFFh<br>3F60h |                |

FIGURE 4-4:

## DATA MEMORY MAP FOR PIC18/I )E26/27/45/46/47/55/56/57K42 DEVICES

© 2016-2017 Microchip Technology Inc.

PIC18(L)F26/27/45/46/47/55/56/57K42

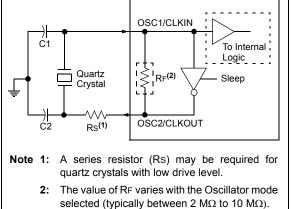

# FIGURE 7-3: QUARTZ CRYSTAL OPERATION (LP, XT OR HS MODE) PIC® MCU

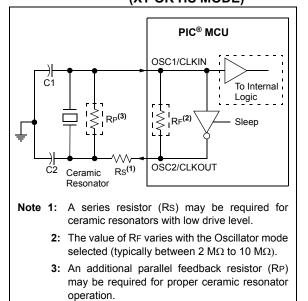

## FIGURE 7-4: CERAMIC RESONATOR OPERATION (XT OR HS MODE)

# 7.2.1.3 Oscillator Start-up Timer (OST)

If the oscillator module is configured for LP, XT or HS modes, the Oscillator Start-up Timer (OST) counts 1024 oscillations from OSC1. This occurs following a Power-on Reset (POR), or a wake-up from Sleep. The OST ensures that the oscillator circuit, using a quartz crystal resonator or ceramic resonator, has started and is providing a stable system clock to the oscillator module.

# 7.2.1.4 4x PLL

The oscillator module contains a 4x PLL that can be used with the external clock sources to provide a system clock source. The input frequency for the PLL must fall within specifications. See the PLL Clock Timing Specifications in Table 44-11.

The PLL can be enabled for use by one of two methods:

- 1. Program the RSTOSC bits in the Configuration Word 1 to 010 (enable EXTOSC with 4x PLL).

- 2. Write the NOSC bits in the OSCCON1 register to 010 (enable EXTOSC with 4x PLL).

## 9.8 Interrupt Setup Procedure

1. When using interrupt priority levels, set the IPEN bit in INTCON0 register and then select the user-assigned priority level for the interrupt source by writing the control bits in the appropriate IPRx Control register.

| Note: | At a device Reset, the IPRx registers are |

|-------|-------------------------------------------|

|       | initialized, such that all user interrupt |

|       | sources are assigned to high priority.    |

- 2. Clear the Interrupt Flag Status bit associated with the peripheral in the associated PIRx Status register.

- 3. Enable the interrupt source by setting the interrupt enable control bit associated with the source in the appropriate PIEx Control register.

- If the vector table is used (MVECEN = 1), then setup the start address for the Interrupt Vector Table using the IVTBASE register. See Section 9.2.2 "Interrupt Vector Table Contents".

- 5. Once the IVTBASE is written to, set the Interrupt enable bits in INTCON0 register.

- 6. An example of setting up interrupts and ISRs using assembly and C can be found in Examples 9-3 and 9-4.

# 9.9 External Interrupt Pins

The PIC18(L)F26/27/45/46/47/55/56/57K42 devices have three external interrupt sources which can be assigned to any pin on different ports based on the PPS settings. Refer Section 17.0 "Peripheral Pin Select (PPS) Module" for possible rerouting options. The external interrupt sources are edge-triggered. If the corresponding INTxEDG bit in the INTCON0 register is set (= 1), the interrupt is triggered by a rising edge. If the bit is clear, the trigger is on the falling edge.

When a valid edge appears on the INTx pin, the corresponding flag bit, INTxF in the PIRx registers, is set. This interrupt can be disabled by clearing the corresponding enable bit, INTxE. Flag bit, INTxF, must be cleared by software in the Interrupt Service Routine before re-enabling the interrupt.

All external interrupts (INT0, INT1 and INT2) can wakeup the processor from Idle or Sleep modes if bit INTxE was set prior to going into those modes. If the Global Interrupt Enable bit, GIE/GIEH, is set, the processor will branch to the interrupt vector following wake-up. Interrupt priority is determined by the value contained in the interrupt priority bits, INT0IP, INT1IP and INT2IP of the IPRx registers.

# 9.10 Wake-up from Sleep

The interrupt controller provides a wake-up request to the CPU whenever an interrupt event occurs, if the interrupt event is enabled. This occurs regardless of whether the part is in Run, Idle/Doze or Sleep modes. The status of the GIEH/GIEL bits has no effect on the wake-up request. The wake-up request will be asynchronous to all clocks.

# 9.11 Interrupt Compatibility

When the MVECEN bit in Configuration Word 2L is cleared (Register 5-3), the Interrupt Vector Table feature is disabled and interrupts are compatible with previous high performance 8-bit PIC18 microcontroller devices. In this mode, the Interrupt Vector Table priority has no effect.

When the IPEN bit is also cleared, the interrupt priority feature is disabled and interrupts are compatible with PIC<sup>®</sup>16 microcontroller mid-range devices. All interrupts branch to address 0008h since the interrupt priority is disabled.

| _              |                                                                                                                                                                                                                                                                   |                                    | _     |                |                  |                  |              |

|----------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------|-------|----------------|------------------|------------------|--------------|

| R/W/HS-0/      | 0 R/W/HS-0/0                                                                                                                                                                                                                                                      | R/W/HS-0/0                         | U-0   | R/W/HS-0/0     | R/W/HS-0/0       | R/W/HS-0/0       | R/W/HS-0/0   |

| CLC1IF         | CWG1IF                                                                                                                                                                                                                                                            | NCO1IF                             |       | CCP1IF         | TMR2IF           | TMR1GIF          | TMR1IF       |

| bit 7          |                                                                                                                                                                                                                                                                   |                                    |       |                |                  |                  | bit 0        |

|                |                                                                                                                                                                                                                                                                   |                                    |       |                |                  |                  |              |

| Legend:        |                                                                                                                                                                                                                                                                   |                                    |       |                |                  |                  |              |

| R = Readab     | ole bit                                                                                                                                                                                                                                                           | W = Writable                       | oit   | U = Unimpler   | nented bit, read | l as '0'         |              |

| u = Bit is un  | changed                                                                                                                                                                                                                                                           | x = Bit is unkn                    | own   | -n/n = Value a | at POR and BO    | R/Value at all c | other Resets |

| '1' = Bit is s | et                                                                                                                                                                                                                                                                | '0' = Bit is clea                  | ared  | HS = Bit is se | et in hardware   |                  |              |

|                |                                                                                                                                                                                                                                                                   |                                    |       |                |                  |                  |              |

| bit 7          | CLC1IF: CLC                                                                                                                                                                                                                                                       | 1 Interrupt Flag                   | g bit |                |                  |                  |              |

|                |                                                                                                                                                                                                                                                                   | has occurred (r                    |       | ed by software | )                |                  |              |

|                | •                                                                                                                                                                                                                                                                 | event has not o                    |       |                |                  |                  |              |

| bit 6          |                                                                                                                                                                                                                                                                   | /G1 Interrupt FI                   | •     |                |                  |                  |              |

|                |                                                                                                                                                                                                                                                                   | has occurred (r<br>event has not o |       | ed by software | )                |                  |              |

| bit 5          |                                                                                                                                                                                                                                                                   | D1 Interrupt Fla                   |       |                |                  |                  |              |

| bit 0          |                                                                                                                                                                                                                                                                   | has occurred (r                    | •     | ed by software | )                |                  |              |

|                |                                                                                                                                                                                                                                                                   | event has not o                    |       |                | /                |                  |              |

| bit 4          | Unimplemen                                                                                                                                                                                                                                                        | ted: Read as '                     | )'    |                |                  |                  |              |

| bit 3          | CCP1IF: CCF                                                                                                                                                                                                                                                       | P1 Interrupt Flag                  | g bit |                |                  |                  |              |

|                |                                                                                                                                                                                                                                                                   | has occurred (r                    |       | ed by software | )                |                  |              |

|                |                                                                                                                                                                                                                                                                   | event has not o                    |       |                |                  |                  |              |

| bit 2          |                                                                                                                                                                                                                                                                   | R2 Interrupt Fla                   | •     |                | ,                |                  |              |

|                |                                                                                                                                                                                                                                                                   | has occurred (r<br>event has not o |       | ed by software | )                |                  |              |

| bit 1          | •                                                                                                                                                                                                                                                                 | /R1 Gate Inter                     |       |                |                  |                  |              |

|                |                                                                                                                                                                                                                                                                   |                                    |       | ed bv software | )                |                  |              |

|                | <ul> <li>1 = Interrupt has occurred (must be cleared by software)</li> <li>0 = Interrupt event has not occurred</li> </ul>                                                                                                                                        |                                    |       |                |                  |                  |              |

| bit 0          | TMR1IF: TMF                                                                                                                                                                                                                                                       | R1 Interrupt Fla                   | g bit |                |                  |                  |              |

|                | •                                                                                                                                                                                                                                                                 | has occurred (r                    |       | ed by software | )                |                  |              |

|                |                                                                                                                                                                                                                                                                   | event has not o                    |       |                |                  |                  |              |

| e              | nterrupt flag bits get set when an interrupt condition occurs, regardless of the state of its corresponding<br>enable bit, or the global enable bit. User software should ensure the appropriate interrupt flag bits are<br>clear prior to enabling an interrupt. |                                    |       |                |                  |                  |              |

|                |                                                                                                                                                                                                                                                                   |                                    |       |                |                  |                  |              |

# REGISTER 9-7: PIR4: PERIPHERAL INTERRUPT REGISTER 4<sup>(1)</sup>

# PIC18(L)F26/27/45/46/47/55/56/57K42

|                                      |               |                   |                |                                                       |                  | •       |         |  |  |

|--------------------------------------|---------------|-------------------|----------------|-------------------------------------------------------|------------------|---------|---------|--|--|

| U-0                                  | U-0           | U-0               | U-0            | U-0                                                   | U-0              | R/W-0/0 | R/W-0/0 |  |  |

| —                                    | -             | —                 | —              | -                                                     | —                | CLC4IE  | CCP4IE  |  |  |

| bit 7                                |               |                   |                |                                                       |                  |         | bit 0   |  |  |

|                                      |               |                   |                |                                                       |                  |         |         |  |  |

| Legend:                              |               |                   |                |                                                       |                  |         |         |  |  |

| R = Readable                         | bit           | W = Writable      | bit            | U = Unimplei                                          | mented bit, read | as '0'  |         |  |  |

| u = Bit is unch                      | anged         | x = Bit is unkr   | nown           | -n/n = Value at POR and BOR/Value at all other Resets |                  |         |         |  |  |

| '1' = Bit is set                     |               | '0' = Bit is clea | ared           |                                                       |                  |         |         |  |  |

|                                      |               |                   |                |                                                       |                  |         |         |  |  |

| bit 7-2                              | Unimplemen    | ted: Read as '    | 0'             |                                                       |                  |         |         |  |  |

| bit 1                                | CLC4IE: CLC   | 4 Interrupt Ena   | able bit       |                                                       |                  |         |         |  |  |

|                                      | 1 = Interrupt | has occurred (    | must be cleare | ed by software                                        | e)               |         |         |  |  |

| 0 = Interrupt event has not occurred |               |                   |                |                                                       |                  |         |         |  |  |

| bit 0                                | CCP4IE: CCF   | P4 Interrupt En   | able bit       |                                                       |                  |         |         |  |  |

|                                      | 1 = Interrupt | has occurred (    | must be cleare | ed by software                                        | )                |         |         |  |  |

|                                      | 0 = Interrupt | event has not o   | occurred       |                                                       |                  |         |         |  |  |

# REGISTER 9-24: PIE10: PERIPHERAL INTERRUPT ENABLE REGISTER 10

## 13.3.8 ERASING THE DATA EEPROM MEMORY

Data EEPROM Memory can be erased by writing 0xFF to all locations in the Data EEPROM Memory that needs to be erased.

|      | CLRF   | NVMADRL     | ; Start at address 0         |

|------|--------|-------------|------------------------------|

|      | BCF    | NVMCON1, CF | GS ; Set for memory          |

|      | BCF    | NVMCON1, EE | -                            |

|      | BCF    | INTCONO, GI | E ; Disable interrupts       |

|      | BSF    | NVMCON1, WR | EN ; Enable writes           |

| Loop |        |             | ; Loop to refresh array      |

|      | BSF    | NVMCON1, RD | ; Read current address       |

|      | MOVLW  | 55h         | ;                            |

|      | MOVWF  | NVMCON2     | ; Write 55h                  |

|      | MOVLW  | 0AAh        | ;                            |

|      | MOVWF  | NVMCOM2     | ; Write OAAh                 |

|      | BSF    | NVMCON1, WR | ; Set WR bit to begin write  |

|      | BTFSC  | NVMCON1, WR | ; Wait for write to complete |

|      | BRA    | \$-2        |                              |

|      | INCFSZ | NVMADRL, F  | ; Increment address          |

|      | BRA    | LOOP        | ; Not zero, do it again      |

|      | BCF    | NVMCON1, WR | EN ; Disable writes          |

|      | BSF    | INTCON0, GI | E ; Enable interrupts        |

# PIC18(L)F26/27/45/46/47/55/56/57K42

## REGISTER 15-21: DMAxDCNTH: DMAx DESTINATION COUNT HIGH REGISTER

| U-0   | U-0 | U-0 | U-0 | R-0 | R-0   | R-0   | R-0   |

|-------|-----|-----|-----|-----|-------|-------|-------|

| —     | —   | —   | —   |     | DCNT< | 11:8> |       |

| bit 7 |     |     |     |     |       |       | bit 0 |

# Legend:

| Legenu.                                           |                  |                        |                                            |

|---------------------------------------------------|------------------|------------------------|--------------------------------------------|

| R = Readable bit                                  | W = Writable bit | U = Unimplemented bit, | read as '0'                                |

| -n/n = Value at POR and<br>BOR/Value at all other | 1 = bit is set   | 0 = bit is cleared     | x = bit is unknown<br>u = bit is unchanged |

| Resets                                            |                  |                        | C C                                        |

### bit 7-4 Unimplemented: Read as '0'

bit 3-0 DCNT<11:8>: Current Destination Byte Count

### REGISTER 15-22: DMAxSIRQ: DMAx START INTERRUPT REQUEST SOURCE SELECTION REGISTER

| U-0   | R/W-0/0 | R/W-0/0 | R/W-0/0 | R/W-0/0   | R/W-0/0 | R/W-0/0 | R/W-0/0 |

|-------|---------|---------|---------|-----------|---------|---------|---------|

| _     |         |         |         | SIRQ<6:0> |         |         |         |

| bit 7 |         |         |         |           |         |         | bit 0   |

| Legend:                                                     |                  |                        |                                            |

|-------------------------------------------------------------|------------------|------------------------|--------------------------------------------|

| R = Readable bit                                            | W = Writable bit | U = Unimplemented bit, | read as '0'                                |

| -n/n = Value at POR<br>and BOR/Value at all<br>other Resets | 1 = bit is set   | 0 = bit is cleared     | x = bit is unknown<br>u = bit is unchanged |

## bit 7 Unimplemented: Read as '0'

bit 6-0 **SIRQ<6:0>:** DMAx Start Interrupt Request Source Selection bits Please refer to Table 15-2 for more information.

## REGISTER 15-23: DMAxAIRQ: DMAx ABORT INTERRUPT REQUEST SOURCE SELECTION REGISTER

| U-0   | R/W-0/0   | R/W-0/0 | R/W-0/0 | R/W-0/0 | R/W-0/0 | R/W-0/0 | R/W-0/0 |  |

|-------|-----------|---------|---------|---------|---------|---------|---------|--|

| _     | AIRQ<6:0> |         |         |         |         |         |         |  |

| bit 7 |           |         |         |         |         |         | bit 0   |  |

| Legend:                                                     |                  |                        |                                            |

|-------------------------------------------------------------|------------------|------------------------|--------------------------------------------|

| R = Readable bit                                            | W = Writable bit | U = Unimplemented bit, | read as '0'                                |

| -n/n = Value at POR<br>and BOR/Value at all<br>other Resets | 1 = bit is set   | 0 = bit is cleared     | x = bit is unknown<br>u = bit is unchanged |

bit 7 Unimplemented: Read as '0'

bit 6-0 **AIRQ<6:0>:** DMAx Interrupt Request Source Selection bits Please refer to Table 15-2 for more information.

# 21.3 Timer1/3/5 Prescaler

Timer1/3/5 has four prescaler options allowing 1, 2, 4 or 8 divisions of the clock input. The CKPS bits of the TxCON register control the prescale counter. The prescale counter is not directly readable or writable; however, the prescaler counter is cleared upon a write to TMRxH or TMRxL.

# 21.4 Timer1/3/5 Operation in Asynchronous Counter Mode

If control bit SYNC of the TxCON register is set, the external clock input is not synchronized. The timer increments asynchronously to the internal phase clocks. If external clock source is selected then the timer will continue to run during Sleep and can generate an interrupt on overflow, which will wake up the processor. However, special precautions in software are needed to read/write the timer (see Section 21.4.1 "Reading and Writing Timer1/3/5 in Asynchronous Counter Mode").

Note: When switching from synchronous to asynchronous operation, it is possible to skip an increment. When switching from asynchronous to synchronous operation, it is possible to produce an additional increment.

## 21.4.1 READING AND WRITING TIMER1/3/ 5 IN ASYNCHRONOUS COUNTER MODE

Reading TMRxH or TMRxL while the timer is running from an external asynchronous clock will ensure a valid read (taken care of in hardware). However, the user should keep in mind that reading the 16-bit timer in two 8-bit values itself, poses certain problems, since the timer may overflow between the reads. For writes, it is recommended that the user simply stop the timer and write the desired values. A write contention may occur by writing to the timer registers, while the register is incrementing. This may produce an unpredictable value in the TMRxH:TMRxL register pair.

# 21.5 Timer1/3/5 16-Bit Read/Write Mode

Timer1/3/5 can be configured to read and write all 16 bits of data, to and from, the 8-bit TMRxL and TMRxH registers, simultaneously. The 16-bit read and write operations are enabled by setting the RD16 bit of the TxCON register.

To accomplish this function, the TMRxH register value is mapped to a buffer register called the TMRxH buffer register. While in 16-Bit mode, the TMRxH register is not directly readable or writable and all read and write operations take place through the use of this TMRxH buffer register.

When a read from the TMRxL register is requested, the value of the TMRxH register is simultaneously loaded into the TMRxH buffer register. When a read from the TMRxH register is requested, the value is provided from the TMRxH buffer register instead. This provides the user with the ability to accurately read all 16 bits of the Timer1/3/5 value from a single instance in time. Reference the block diagram in Figure 21-2 for more details.

In contrast, when not in 16-Bit mode, the user must read each register separately and determine if the values have become invalid due to a rollover that may have occurred between the read operations.

When a write request of the TMRxL register is requested, the TMRxH buffer register is simultaneously updated with the contents of the TMRxH register. The value of TMRxH must be preloaded into the TMRxH buffer register prior to the write request for the TMRxL register. This provides the user with the ability to write all 16 bits to the TMRxL:TMRxH register pair at the same time.

Any requests to write to the TMRxH directly does not clear the Timer1/3/5 prescaler value. The prescaler value is only cleared through write requests to the TMRxL register.

|       |     |     |   | •   |          |         |         |  |

|-------|-----|-----|---|-----|----------|---------|---------|--|

| U-0   | U-0 | U-0 |   | U-0 | R/W-0/x  | R/W-0/x | R/W-0/x |  |

| —     | —   | —   | _ | —   | CTS<2:0> |         |         |  |

| bit 7 |     |     |   |     |          |         | bit 0   |  |

# REGISTER 23-3: CCPxCAP: CAPTURE INPUT SELECTION MULTIPLEXER REGISTER

| Legend:           |                  |                             |                    |  |

|-------------------|------------------|-----------------------------|--------------------|--|

| R = Readable bit  | W = Writable bit | U = Unimplemented bit, read | l as '0'           |  |

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared        | x = Bit is unknown |  |

### bit 7-3 Unimplemented: Read as '0'

bit 2-0 CTS<2:0>: Capture Trigger Input Selection bits

| CTS<1:0> |                            | Conn                       | ection                     |                            |  |  |  |  |

|----------|----------------------------|----------------------------|----------------------------|----------------------------|--|--|--|--|

| 013<1.0> | CCP1                       | CCP4                       |                            |                            |  |  |  |  |

| 111      |                            | CLC                        | 4_out                      |                            |  |  |  |  |

| 110      |                            | CLC                        | 3_out                      |                            |  |  |  |  |

| 101      |                            | CLC2_out                   |                            |                            |  |  |  |  |

| 100      |                            | CLC                        | 1_out                      |                            |  |  |  |  |

| 011      |                            | IOC_Ir                     | nterrupt                   |                            |  |  |  |  |

| 010      |                            | CMP2                       | _output                    |                            |  |  |  |  |

| 001      |                            | CMP1                       | _output                    |                            |  |  |  |  |

| 000      | Pin selected by<br>CCP1PPS | Pin selected by<br>CCP2PPS | Pin selected by<br>CCP3PPS | Pin selected by<br>CCP4PPS |  |  |  |  |

## REGISTER 23-4: CCPRxL: CCPx REGISTER LOW BYTE

| R/W-x/x   | R/W-x/x R/W-x/x R/W-x/x R/W-x/x R/W-x/x F |  |  |  |  |  |  |  |  |  |

|-----------|-------------------------------------------|--|--|--|--|--|--|--|--|--|

|           | RL<7:0>                                   |  |  |  |  |  |  |  |  |  |

| bit 7 bit |                                           |  |  |  |  |  |  |  |  |  |

| Legend:           |                  |                                                     |                    |  |  |  |

|-------------------|------------------|-----------------------------------------------------|--------------------|--|--|--|

| R = Readable bit  | W = Writable bit | W = Writable bit U = Unimplemented bit, read as '0' |                    |  |  |  |

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared                                | x = Bit is unknown |  |  |  |

bit 7-0

MODE = Capture Mode: RL<7:0>: LSB of captured TMR1 value MODE = Compare Mode: RL<7:0>: LSB compared to TMR1 value MODE = PWM Mode && FMT = 0: RL<7:0>: CCPW<7:0> - Pulse-Width LS 8 bits MODE = PWM Mode && FMT = 1: RL<7:6>: CCPW<1:0> - Pulse-Width LS 2 bits RL<5:0>: Not used

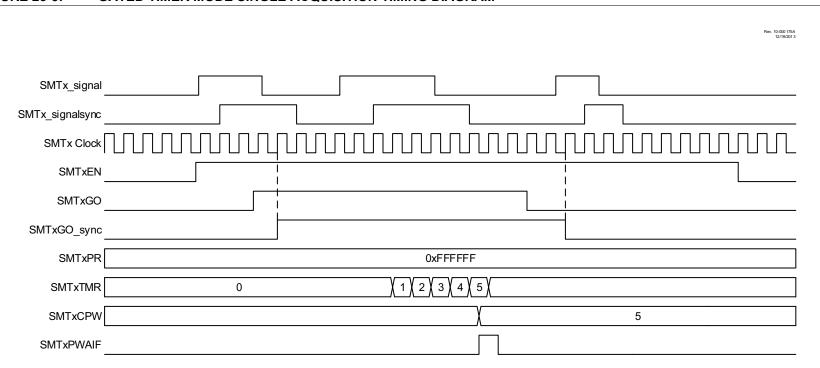

## FIGURE 25-5: GATED TIMER MODE SINGLE ACQUISITION TIMING DIAGRAM

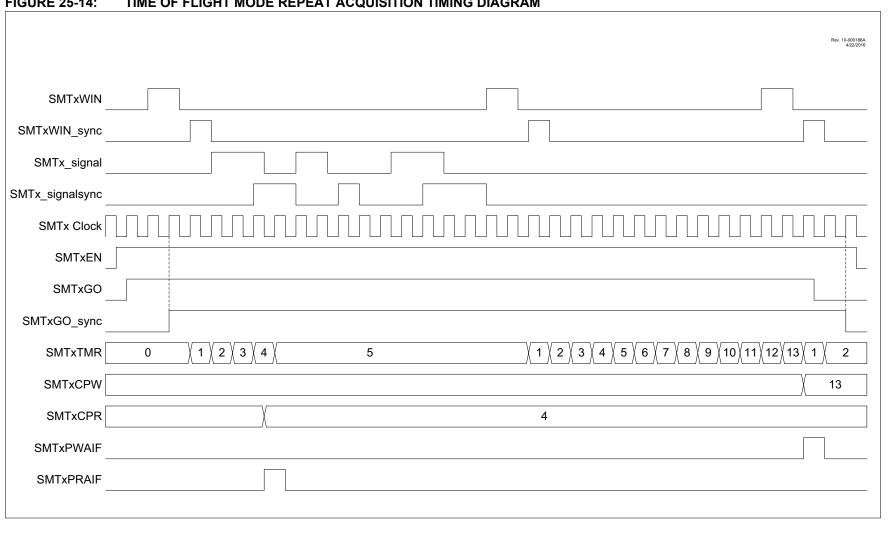

#### FIGURE 25-14: TIME OF FLIGHT MODE REPEAT ACQUISITION TIMING DIAGRAM

# 26.0 COMPLEMENTARY WAVEFORM GENERATOR (CWG) MODULE

The Complementary Waveform Generator (CWG) produces half-bridge, full-bridge, and steering of PWM waveforms. It is backwards compatible with previous CCP functions. The PIC18(L)F2X/4X/5XK42 family has three instances of the CWG module.

Each of the CWG modules has the following features:

- Six operating modes:

- Synchronous Steering mode

- Asynchronous Steering mode

- Full-Bridge mode, Forward

- Full-Bridge mode, Reverse

- Half-Bridge mode

- Push-Pull mode

- · Output polarity control

- Output steering

- Independent 6-bit rising and falling event deadband timers

- Clocked dead band

- Independent rising and falling dead-band enables

- Auto-shutdown control with:

- Selectable shutdown sources

- Auto-restart option

- Auto-shutdown pin override control

# 26.1 Fundamental Operation

The CWG generates two output waveforms from the selected input source.

The off-to-on transition of each output can be delayed from the on-to-off transition of the other output, thereby creating a time delay immediately where neither output is driven. This is referred to as dead time and is covered in **Section 26.6 "Dead-Band Control"**.

It may be necessary to guard against the possibility of circuit faults or a feedback event arriving too late or not at all. In this case, the active drive must be terminated before the Fault condition causes damage. This is referred to as auto-shutdown and is covered in Section 26.10 "Auto-Shutdown".

# 26.2 Operating Modes

The CWG module can operate in six different modes, as specified by the MODE<2:0> bits of the CWGxCON0 register:

- · Half-Bridge mode

- Push-Pull mode

- Asynchronous Steering mode

- Synchronous Steering mode

- Full-Bridge mode, Forward

- Full-Bridge mode, Reverse

All modes accept a single pulse data input, and provide up to four outputs as described in the following sections.

All modes include auto-shutdown control as described in Section 26.10 "Auto-Shutdown".

| Note: | Except as noted for Full-bridge mode  |

|-------|---------------------------------------|

|       | (Section 26.2.3 "Full-Bridge Modes"), |

|       | mode changes should only be performed |

|       | while EN = 0 (Register 26-1).         |

## 26.2.1 HALF-BRIDGE MODE

In Half-Bridge mode, two output signals are generated as true and inverted versions of the input as illustrated in Figure 26-2. A non-overlap (dead-band) time is inserted between the two outputs as described in **Section 26.6 "Dead-Band Control"**. The output steering feature cannot be used in this mode. A basic block diagram of this mode is shown in Figure 26-1.

The unused outputs CWGxC and CWGxD drive similar signals as CWGxA and CWGxB, with polarity independently controlled by the POLC and POLD bits of the CWGxCON1 register, respectively.

# 29.10 Register Definitions: ZCD Control

| REGISIER      | 29-1. ZCDC                             | UN: ZERU-U                                                | RUSS DE H       |                    |               | -R              |         |  |  |  |  |

|---------------|----------------------------------------|-----------------------------------------------------------|-----------------|--------------------|---------------|-----------------|---------|--|--|--|--|

| R/W-0/0       | U-0                                    | R-x                                                       | R/W-0/0         | U-0                | U-0           | R/W-0/0         | R/W-0/0 |  |  |  |  |

| SEN           | —                                      | OUT                                                       | POL             | —                  | _             | INTP            | INTN    |  |  |  |  |

| bit 7         |                                        |                                                           |                 |                    |               |                 | bit     |  |  |  |  |

|               |                                        |                                                           |                 |                    |               |                 |         |  |  |  |  |

| Legend:       |                                        |                                                           |                 |                    |               |                 |         |  |  |  |  |

| R = Readabl   |                                        | W = Writable                                              |                 | U = Unimplen       |               |                 |         |  |  |  |  |

| -n = Value at | POR                                    | '1' = Bit is se                                           | t               | '0' = Bit is clea  | ared          | x = Bit is unkr | nown    |  |  |  |  |

| bit 7         | SEN: Zero-C                            | Cross Detect Sc                                           | ftware Enable   | bit                |               |                 |         |  |  |  |  |

|               | This bit is igr                        | nored when ZC                                             | DSEN configu    | ration bit is set. |               |                 |         |  |  |  |  |

|               |                                        | oss detect is e                                           |                 |                    |               |                 |         |  |  |  |  |

|               | 0= Zero-cr                             | oss detect is di                                          | sabled. ZCD     | oin operates aco   | cording to PP | S and TRIS cont | rols.   |  |  |  |  |

| bit 6         | Unimpleme                              | nted: Read as                                             | ʻ0 <b>'</b>     |                    |               |                 |         |  |  |  |  |

| bit 5         | OUT: Zero-Cross Detect Data Output bit |                                                           |                 |                    |               |                 |         |  |  |  |  |

|               | ZCDPOL bit = 0:                        |                                                           |                 |                    |               |                 |         |  |  |  |  |

|               |                                        | is sinking curre                                          |                 |                    |               |                 |         |  |  |  |  |

|               | 2CD pin<br>ZCDPOL bit                  | is sourcing cur = $1 \cdot$                               | rent            |                    |               |                 |         |  |  |  |  |

|               |                                        | 1 = ZCD pin is sourcing current                           |                 |                    |               |                 |         |  |  |  |  |

|               |                                        | is sinking curre                                          |                 |                    |               |                 |         |  |  |  |  |

| bit 4         | POL: Zero-C                            | Cross Detect Po                                           | larity bit      |                    |               |                 |         |  |  |  |  |

|               | 1 = ZCD log                            | ic output is inve                                         | rted            |                    |               |                 |         |  |  |  |  |

|               | 0 = ZCD log                            | ic output is not                                          | inverted        |                    |               |                 |         |  |  |  |  |

| bit 3-2       | Unimpleme                              | nted: Read as                                             | 0'              |                    |               |                 |         |  |  |  |  |

| bit 1         | INTP: Zero-(                           | Cross Detect Po                                           | ositive-Going I | Edge Interrupt E   | nable bit     |                 |         |  |  |  |  |

|               |                                        | 1 = ZCDIF bit is set on low-to-high ZCD_output transition |                 |                    |               |                 |         |  |  |  |  |

|               | 0 = ZCDIF b                            | it is unaffected                                          | by low-to-high  | ZCD_output tra     | ansition      |                 |         |  |  |  |  |

| bit 0         | INTN: Zero-                            | Cross Detect N                                            | egative-Going   | Edge Interrupt     | Enable bit    |                 |         |  |  |  |  |

|               |                                        | 1 = ZCDIF bit is set on high-to-low ZCD_output transition |                 |                    |               |                 |         |  |  |  |  |

|               | 0 = ZCDIF b                            |                                                           |                 |                    |               |                 |         |  |  |  |  |

## REGISTER 29-1: ZCDCON: ZERO-CROSS DETECT CONTROL REGISTER

# TABLE 29-1: SUMMARY OF REGISTERS ASSOCIATED WITH THE ZCD MODULE

| Name   | Bit 7 | Bit 6 | Bit 5 | Bit 4 | Bit 3 | Bit 2 | Bit 1 | Bit 0 | Register<br>on page |

|--------|-------|-------|-------|-------|-------|-------|-------|-------|---------------------|

| ZCDCON | SEN   | —     | OUT   | POL   | —     | _     | INTP  | INTN  | 462                 |

**Legend:** — = unimplemented, read as '0'. Shaded cells are unused by the ZCD module.

# 31.13 Checksum (UART1 only)

This section does not apply to the LIN mode, which handles checksums automatically.

The transmit and receive checksum adders are enabled when the C0EN bit in the UxCON2 register is set. When enabled, the adders accumulate every byte that is transmitted or received. The accumulated sum includes the carry of the addition. Software is responsible for clearing the checksum registers before a transaction and performing the check at the end of the transaction.

The following is an example of how the checksum registers could be used in the asynchronous modes.

## 31.13.1 TRANSMIT CHECKSUM METHOD

- 1. Clear the UxTXCHK register.

- 2. Set the COEN bit.

- 3. Send all bytes of the transaction output.

- 4. Invert UxTXCHK and send the result as the last byte of the transaction.

## 31.13.2 RECEIVE CHECKSUM METHOD

- 1. Clear the UxRXCHK register.

- 2. Set the COEN bit.

- 3. Receive all bytes in the transaction including the checksum byte.

- 4. Set MSb of UxRXCHK if 7-bit mode is selected.

- 5. Add 1 to UxRXCHK.

- 6. If the result is '0', the checksum passes, otherwise it fails.

The CERIF checksum interrupt flag is not active in any mode other than LIN.

# 31.14 Collision Detection

External forces that interfere with the transmit line are detected in all modes of operation with collision detection. Collision detection is always active when RXEN and TXEN are both set.

When the receive input is connected to the transmit output through either the same I/O pin or external circuitry, a character will be received for every character transmitted. The collision detection circuit provides a warning when the word received does not match the word transmitted. The TXCIF flag in the UxERRIR register is used to signal collisions. This signal is only useful when the TX output is looped back to the RX input and everything that is transmitted is expected to be received. If more than one transmitter is active at the same time, it can be assumed that the TX word will not match the RX word. The TXCIF detects this mismatch and flags an interrupt. The TXCIF bit will also be set in DALI mode transmissions when the received bit is missing the expected mid-bit transition.

Collision detection is always active, regardless of whether or not the RX input is connected to the TX output. It is up to the user to disable the TXCIE bit when collision interrupts are not required.

The software overhead of unloading the receive buffer of transmitted data is avoided by setting the RUNOVF bit in UxCON2 and ignoring the receive interrupt and letting the receive buffer overflow. When the transmission is complete, prepare for receiving data by flushing the receive buffer (see Section 31.11.2, FIFO Reset) and clearing the RXFOIF overflow flag in the UxERRIR register.

# 31.15 RX/TX Activity Timeout

The UART works in conjunction with the HLT timers to monitor activity on the RX and TX lines. Use this feature to determine when there has been no activity on the receive or transmit lines for a user specified period of time.

To use this feature, set the HLT to the desired timeout period by a combination of the HLT clock source, timer prescale value, and timer period registers. Configure the HLT to reset on the UART TX or RX line and start the HLT at the same time the UART is started. UART activity will keep resetting the HLT to prevent a full HLT period from elapsing. When there has been no activity on the selected TX or RX line for longer than the HLT period then an HLT interrupt will occur signaling the timeout event.

For example, the following register settings will configure HLT2 for a 5 ms timeout of no activity on U1RX:

- T2PR = 0x9C (156 prescale periods)

- T2CLKCON = 0x05 (500 kHz internal oscillator)

- T2HLT = 0x04 (free running, reset on rising edge)

- T2RST = 0x15 (reset on U1RX)

- T2CON = 0xC0 (Timer2 on with 1:16 prescale)

# PIC18(L)F26/27/45/46/47/55/56/57K42

| R/W-0/0          | R/W-0/0                                              | R/W-0/0                                  | R/W-0/0         | R/W-0/0         | R/W-0/0          | R/W-0/0          | R/W-0/0     |  |  |  |  |

|------------------|------------------------------------------------------|------------------------------------------|-----------------|-----------------|------------------|------------------|-------------|--|--|--|--|

| TXMTIE           | PERIE                                                | ABDOVE                                   | CERIE           | FERIE           | RXBKIE           | RXFOIE           | TXCIE       |  |  |  |  |

| bit 7            |                                                      |                                          |                 |                 |                  |                  | bit (       |  |  |  |  |

|                  |                                                      |                                          |                 |                 |                  |                  |             |  |  |  |  |

| Legend:          |                                                      |                                          |                 |                 |                  |                  |             |  |  |  |  |

| R = Readable     |                                                      | W = Writable                             |                 |                 | nented bit, read |                  |             |  |  |  |  |

| u = Bit is unch  | anged                                                | x = Bit is unkr                          |                 | -n/n = Value a  | at POR and BO    | R/Value at all c | ther Resets |  |  |  |  |

| '1' = Bit is set |                                                      | '0' = Bit is cle                         | ared            |                 |                  |                  |             |  |  |  |  |

| bit 7            | TXMTIE: Tra                                          | insmit Shift Reg                         | ister Empty In  | terrupt Enable  | bit              |                  |             |  |  |  |  |

|                  | 1 = Interrupt<br>0 = Interrupt                       | t enabled                                |                 |                 |                  |                  |             |  |  |  |  |

| bit 6            | PERIE: Parit                                         | PERIE: Parity Error Interrupt Enable bit |                 |                 |                  |                  |             |  |  |  |  |

|                  | 1 = Interrupt<br>0 = Interrupt                       |                                          |                 |                 |                  |                  |             |  |  |  |  |

| bit 5            | <b>ABDOVE:</b> A<br>1 = Interrupt<br>0 = Interrupt   |                                          | t Overflow Inte | errupt Enable b | bit              |                  |             |  |  |  |  |

| bit 4            | CERIE: Chec<br>1 = Interrupt<br>0 = Interrupt        |                                          | errupt Enable   | bit             |                  |                  |             |  |  |  |  |

| bit 3            | <b>FERIE:</b> Fram<br>1 = Interrupt<br>0 = Interrupt |                                          | upt Enable bit  |                 |                  |                  |             |  |  |  |  |

| bit 2            | <b>RXBKIE:</b> Bre<br>1 = Interrupt<br>0 = Interrupt |                                          | nterrupt Enabl  | le bit          |                  |                  |             |  |  |  |  |

| bit 1            | -                                                    | ceive FIFO Ove<br>t enabled              | rflow Interrup  | t Enable bit    |                  |                  |             |  |  |  |  |

| bit 0            |                                                      | smit Collision In<br>t enabled           | terrupt Enable  | e bit           |                  |                  |             |  |  |  |  |

# REGISTER 31-5: UXERRIE: UART ERROR INTERRUPT ENABLE REGISTER

## 36.5.2 PRECHARGE CONTROL

The precharge stage is an optional period of time that brings the external channel and internal sample and hold capacitor to known voltage levels. Precharge is enabled by writing a non-zero value to the ADPRE register. This stage is initiated when an ADC conversion begins, either from setting the GO bit, a special event trigger, or a conversion restart from the computation functionality. If the ADPRE register is cleared when an ADC conversion begins, this stage is skipped.

During the precharge time, CHOLD is disconnected from the outer portion of the sample path that leads to the external capacitive sensor and is connected to either VDD or VSS, depending on the value of the PPOL bit of ADCON1. At the same time, the port pin logic of the selected analog channel is overridden to drive a digital high or low out, in order to precharge the outer portion of the ADC's sample path, which includes the external sensor. The output polarity of this override is also determined by the PPOL bit of ADCON1. The amount of time that this charging receives is controlled by the ADPRE register.

- **Note 1:** The external charging overrides the TRIS setting of the respective I/O pin.

- **2:** If there is a device attached to this pin, Precharge should not be used.

## 36.5.3 ACQUISITION CONTROL

The Acquisition stage is an optional time for the voltage on the internal sample and hold capacitor to charge or discharge from the selected analog channel. This acquisition time is controlled by the ADACQ register. If PRE = 0, acquisition starts at the beginning of conversion. When PRE = 1, the acquisition stage begins when precharge ends.

At the start of the acquisition stage, the port pin logic of the selected analog channel is overridden to turn off the digital high/low output drivers so they do not affect the final result of the charge averaging. Also, the selected ADC channel is connected to CHOLD. This allows charge averaging to proceed between the precharged channel and the CHOLD capacitor.

Note: When PRE! = 0, acquisition time cannot be '0'. In this case, setting ADACQ to '0' will set a maximum acquisition time (8191 ADC clock cycles). When precharge is disabled, setting ADACQ to '0' will disable hardware acquisition time control.

# 36.5.4 GUARD RING OUTPUTS

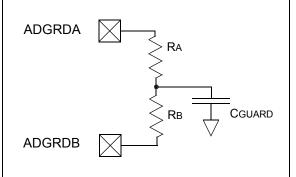

Figure 36-8 shows a typical guard ring circuit. CGUARD represents the capacitance of the guard ring trace placed on the PCB board. The user selects values for RA and RB that will create a voltage profile on CGUARD, which will match the selected acquisition channel.

The purpose of the guard ring is to generate a signal in phase with the CVD sensing signal to minimize the effects of the parasitic capacitance on sensing electrodes. It also can be used as a mutual drive for mutual capacitive sensing. For more information about active guard and mutual drive, see Application Note AN1478, "*mTouch*<sup>TM</sup> Sensing Solution Acquisition Methods Capacitive Voltage Divider" (DS01478).

The ADC has two guard ring drive outputs, ADGRDA and ADGRDB. These outputs can be routed through PPS controls to I/O pins (see Section **17.0 "Peripheral Pin Select (PPS) Module**" for details) and the polarity of these outputs are controlled by the ADGPOL and ADIPEN bits of ADCON1.

At the start of the first precharge stage, both outputs are set to match the ADGPOL bit of ADCON1. Once the acquisition stage begins, ADGRDA changes polarity, while ADGRDB remains unchanged. When performing a double sample conversion, setting the ADIPEN bit of ADCON1 causes both guard ring outputs to transition to the opposite polarity of ADGPOL at the start of the second precharge stage, and ADGRDA toggles again for the second acquisition. For more information on the timing of the guard ring output, refer to Figure 36-8 and Figure 36-9.

# PIC18(L)F26/27/45/46/47/55/56/57K42

| Address          | Name        | Bit 7            | Bit 6         | Bit 5           | Bit 4          | Bit 3     | Bit 2  | Bit 1  | Bit 0  | Register<br>on page |

|------------------|-------------|------------------|---------------|-----------------|----------------|-----------|--------|--------|--------|---------------------|

| 3DF0h            | U1P3L       |                  | •             |                 | P              | 3L        |        | •      |        | 509                 |

| 3DEFh            | U1P2H       | _                | —             | _               | _              | —         | —      | _      | P2H    | 508                 |

| 3DEEh            | U1P2L       |                  |               |                 | P              | 2L        |        |        |        | 508                 |

| 3DEDh            | U1P1H       | —                | —             | _               | —              | —         | _      | —      | P1H    | 507                 |

| 3DECh            | U1P1L       |                  |               |                 | Р              | 1L        |        |        |        | 507                 |

| 3DEBh            | U1TXCHK     |                  |               |                 | TXC            | СНК       |        |        |        | 510                 |

| 3DEAh            | U1TXB       |                  |               |                 | T)             | KB        |        |        |        | 506                 |

| 3DE9h            | U1RXCHK     |                  |               |                 | RX             | СНК       |        |        |        | 510                 |

| 3DE8h            | U1RXB       |                  |               |                 | R              | КB        |        |        |        | 506                 |

| 3DE7h -<br>3DE3h | —           |                  |               |                 | Unimple        | emented   |        |        |        |                     |

| 3DE2h            | U2ERRIE     | TXMTIE           | PERIE         | ABDOVE          | CERIE          | FERIE     | RXBKIE | RXFOIE | TXCIE  | 502                 |

| 3DE1h            | U2ERRIR     | TXMTIF           | PERIF         | ABDOVF          | CERIF          | FERIF     | RXBKIF | RXFOIF | TXCIF  | 501                 |

| 3DE0h            | U2UIR       | WUIF             | ABDIF         | —               | —              | _         | ABDIE  | —      |        | 503                 |

| 3DDFh            | U2FIFO      | TXWRE            | STPMD         | TXBE            | TXBF           | RXIDL     | XON    | RXBE   | RXBF   | 504                 |

| 3DDEh            | U2BRGH      |                  |               |                 | BR             | GH        |        |        |        | 505                 |

| 3DDDh            | U2BRGL      |                  |               |                 | BR             | GL        |        |        |        | 505                 |

| 3DDCh            | U2CON2      | RUNOVF           | RXPOL         | S               | TP             | _         | TXPOL  | I      | FLO    | 500                 |

| 3DDBh            | U2CON1      | ON               | —             |                 | WUE            | RXBIMD    | _      | BRKOVR | SENDB  | 499                 |

| 3DDAh            | U2CON0      | BRGS             | ABDEN         | TXEN            | RXEN           |           | M      | ODE    |        | 498                 |

| 3DD9h            |             |                  |               |                 | Unimple        | emented   |        |        |        |                     |

| 3DD8h            | U2P3L       |                  |               |                 | P              | 3L        |        |        |        | 508                 |

| 3DD7h            | —           |                  |               |                 | Unimple        | emented   |        |        |        |                     |

| 3DD6h            | U2P2L       |                  |               |                 | P              | 2L        |        |        |        | 508                 |

| 3DD5h            | —           |                  |               |                 | Unimple        | emented   |        |        |        |                     |

| 3DD4h            | U2P1L       |                  |               |                 | Р              | 1L        |        |        |        | 507                 |

| 3DD3h            | —           |                  |               |                 | Unimple        | emented   |        |        |        |                     |

| 3DD2h            | U2TXB       |                  |               |                 | T)             | KB        |        |        |        | 506                 |

| 3DD1h            | —           |                  |               |                 | Unimple        | emented   |        |        |        |                     |

| 3DD0h            | U2RXB       |                  |               |                 | R              | КB        |        |        |        | 506                 |

| 3DCFh -<br>3D7Dh | —           |                  |               |                 | Unimple        | emented   |        |        |        |                     |

| 3D7Ch            | I2C1BTO     |                  |               |                 | B              | ГО        |        |        |        | 582                 |

| 3D7Bh            | I2C1CLK     |                  |               |                 | C              | LK        |        |        |        | 581                 |

| 3D7Ah            | I2C1PIE     | CNTIE            | ACKTIE        | —               | WRIE           | ADRIE     | PCIE   | RSCIE  | SCIE   | 588                 |

| 3D79h            | I2C1PIR     | CNTIF            | ACKTIF        | —               | WRIF           | ADRIF     | PCIF   | RSCIF  | SCIF   | 587                 |

| 3D78h            | I2C1STAT1   | TXWE             | _             | TXBE            | —              | RXRE      | CLRBF  | —      | RXBF   | 584                 |

| 3D77h            | I2C1STAT0   | BFRE             | SMA           | MMA             | R              | D         | _      | —      | —      | 583                 |

| 3D76h            | I2C1ERR     | —                | BTOIF         | BCLIF           | NACKIF         | _         | BTOIE  | BCLIE  | NACKIE | 585                 |

| 3D75h            | I2C1CON2    | ACNT             | GCEN          | FME             | ABD            | SD        | AHT    | BI     | FRET   | 580                 |

| 3D74h            | I2C1CON1    | ACKCNT           | ACKDT         | ACKSTAT         | ACKT           | —         | RXO    | TXU    | CSD    | 579                 |

| 3D73h            | I2C1CON0    | EN               | RSEN          | S               | CSTR           | MDR       |        | MODE   |        | 577                 |

| 3D72h            | I2C1ADR3    |                  |               |                 | ADR            |           |        |        | —      | 592                 |

| 3D71h            | I2C1ADR2    |                  |               |                 | A              | DR        |        |        |        | 591                 |

| 3D70h            | I2C1ADR1    |                  |               |                 | ADR            |           |        |        | —      | 590                 |

| 3D6Fh            | I2C1ADR0    |                  |               |                 | A              | DR        |        |        |        | 589                 |

| 3D6Eh            | I2C1ADB1    |                  |               |                 | A              | OB        |        |        |        | 594                 |

| 3D6Dh            | I2C1ADB0    |                  |               |                 | A              | ЭB        |        |        |        | 593                 |

| Legend:          | x = unknown | u = unchanged, · | - = unimpleme | nted, a = value | e depends on o | condition |        |        |        |                     |

## TABLE 42-1: REGISTER FILE SUMMARY FOR PIC18(L)F26/27/45/46/47/55/56/57K42 DEVICES

Note 1: Unimplemented in LF devices.

2: Unimplemented in PIC18(L)F26/27K42.

3: Unimplemented on PIC18(L)F26/27/45/46/47K42 devices.

4: Unimplemented in PIC18(L)F45/55K42.

# 43.11 Demonstration/Development Boards, Evaluation Kits, and Starter Kits

A wide variety of demonstration, development and evaluation boards for various PIC MCUs and dsPIC DSCs allows quick application development on fully functional systems. Most boards include prototyping areas for adding custom circuitry and provide application firmware and source code for examination and modification.

The boards support a variety of features, including LEDs, temperature sensors, switches, speakers, RS-232 interfaces, LCD displays, potentiometers and additional EEPROM memory.

The demonstration and development boards can be used in teaching environments, for prototyping custom circuits and for learning about various microcontroller applications.

In addition to the PICDEM<sup>™</sup> and dsPICDEM<sup>™</sup> demonstration/development board series of circuits, Microchip has a line of evaluation kits and demonstration software for analog filter design, KEELOQ<sup>®</sup> security ICs, CAN, IrDA<sup>®</sup>, PowerSmart battery management, SEEVAL<sup>®</sup> evaluation system, Sigma-Delta ADC, flow rate sensing, plus many more.

Also available are starter kits that contain everything needed to experience the specified device. This usually includes a single application and debug capability, all on one board.

Check the Microchip web page (www.microchip.com) for the complete list of demonstration, development and evaluation kits.

# 43.12 Third-Party Development Tools

Microchip also offers a great collection of tools from third-party vendors. These tools are carefully selected to offer good value and unique functionality.

- Device Programmers and Gang Programmers from companies, such as SoftLog and CCS

- Software Tools from companies, such as Gimpel and Trace Systems

- Protocol Analyzers from companies, such as Saleae and Total Phase

- Demonstration Boards from companies, such as MikroElektronika, Digilent<sup>®</sup> and Olimex

- Embedded Ethernet Solutions from companies, such as EZ Web Lynx, WIZnet and IPLogika<sup>®</sup>

# 44.4 AC Characteristics