Welcome to E-XFL.COM

### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

### Details

E·XFI

| Product Status             | Active                                                                      |

|----------------------------|-----------------------------------------------------------------------------|

| Core Processor             | PIC                                                                         |

| Core Size                  | 8-Bit                                                                       |

| Speed                      | 64MHz                                                                       |

| Connectivity               | I <sup>2</sup> C, LINbus, SPI, UART/USART                                   |

| Peripherals                | Brown-out Detect/Reset, DMA, HLVD, POR, PWM, WDT                            |

| Number of I/O              | 36                                                                          |

| Program Memory Size        | 128KB (64K x 16)                                                            |

| Program Memory Type        | FLASH                                                                       |

| EEPROM Size                | 1K x 8                                                                      |

| RAM Size                   | 8K x 8                                                                      |

| Voltage - Supply (Vcc/Vdd) | 2.3V ~ 5.5V                                                                 |

| Data Converters            | A/D 35x12b; D/A 1x5b                                                        |

| Oscillator Type            | Internal                                                                    |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                           |

| Mounting Type              | Surface Mount                                                               |

| Package / Case             | 44-TQFP                                                                     |

| Supplier Device Package    | 44-TQFP (10x10)                                                             |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/pic18f47k42t-i-pt |

|                            |                                                                             |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

| U                       |

|-------------------------|

|                         |

| IC                      |

| <u>``</u>               |

| $\overline{\mathbf{x}}$ |

| 8                       |

| Ξ                       |

|                         |

| $\mathbf{i}$            |

|                         |

| N                       |

| 6                       |

|                         |

| Ν                       |

| 7                       |

|                         |

| 4                       |

| 5                       |

| 1                       |

| 4                       |

| G                       |

| 1                       |

| /47/                    |

| Z                       |

| /55/                    |

| <b>M</b>                |

| 5                       |

| ;/56                    |

| Q                       |

| δ                       |

| 5                       |

| 5                       |

| Z                       |

| Σ                       |

|                         |

| 42                      |

| N                       |

| IABLE 1            | -                      |               |                  |                   | TABLE (PIC18) | (_)//          | (00.1.1           |                              |                     |                                            |     |                                                                                              |                                                                          |                                                                                                                   |                                          |     |                        |                     |             |

|--------------------|------------------------|---------------|------------------|-------------------|---------------|----------------|-------------------|------------------------------|---------------------|--------------------------------------------|-----|----------------------------------------------------------------------------------------------|--------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------|------------------------------------------|-----|------------------------|---------------------|-------------|

| 0/I                | 28-Pin SPDIP/SOIC/SSOP | 28-Pin (U)QFN | DDA              | Voltage Reference | DAC           | Comparators    | Zero Cross Detect | 1²C                          | IdS                 | UART                                       | WSQ | Timers/SMT                                                                                   | CCP and PWM                                                              | 9M0                                                                                                               | כרכ                                      | NCO | Clock Reference (CLKR) | Interrupt-on-Change | Basic       |

| RC0                | 11                     | 8             | ANC0             | 1                 | _             | -              | -                 | _                            | 1                   | _                                          | _   | T1CKI <sup>(1)</sup><br>T3CKI <sup>(1)</sup><br>T3G <sup>(1)</sup><br>SMTWIN1 <sup>(1)</sup> | _                                                                        | 1                                                                                                                 | 1                                        | 1   | -                      | IOCC0               | SOSCO       |

| RC1                | 12                     | 9             | ANC1             | -                 | _             | _              | -                 | _                            | -                   | _                                          | _   | SMTSIG1 <sup>(1)</sup>                                                                       | CCP2 <sup>(1)</sup>                                                      | -                                                                                                                 | -                                        | -   | _                      | IOCC1               | SOSCI       |

| RC2                | 13                     | 10            | ANC2             | _                 | _             | —              | —                 | _                            | _                   | _                                          | _   | T5CKI <sup>(1)</sup>                                                                         | CCP1 <sup>(1)</sup>                                                      | _                                                                                                                 | _                                        | _   | _                      | IOCC2               | _           |

| RC3                | 14                     | 11            | ANC3             | _                 | —             | —              | _                 | SCL1 <sup>(3,4)</sup>        | SCK1 <sup>(1)</sup> | _                                          | -   | T2IN <sup>(1)</sup>                                                                          | —                                                                        | _                                                                                                                 | _                                        | _   | —                      | IOCC3               | -           |

| RC4                | 15                     | 12            | ANC4             | —                 | —             | —              | —                 | SDA1 <sup>(3,4)</sup>        | SDI1 <sup>(1)</sup> | -                                          | —   | —                                                                                            | —                                                                        | —                                                                                                                 | _                                        | —   | —                      | IOCC4               | —           |

| RC5                | 16                     | 13            | ANC5             | _                 | —             | _              | _                 | —                            | —                   | _                                          |     | T4IN <sup>(1)</sup>                                                                          | —                                                                        | —                                                                                                                 | -                                        | _   | _                      | IOCC5               | _           |

| RC6                | 17                     | 14            | ANC6             | —                 | —             | -              | _                 | —                            | —                   | CTS1 <sup>(1)</sup>                        | -   | —                                                                                            | _                                                                        | —                                                                                                                 | _                                        | —   | —                      | IOCC6               | —           |

| RC7                | 18                     | 15            | ANC7             | _                 | —             | —              | _                 | _                            | _                   | RX1 <sup>(1)</sup>                         |     | —                                                                                            | _                                                                        | _                                                                                                                 | _                                        | _   | _                      | IOCC7               | _           |

| RE3                | 1                      | 26            | -                | _                 | -             | —              | -                 | -                            | —                   | -                                          | _   | -                                                                                            | -                                                                        | _                                                                                                                 | _                                        | _   | —                      | IOCE3               | MCLR<br>VPP |

| VDD                | 20                     | 17            | _                | _                 | —             | —              | —                 | —                            | _                   | —                                          | _   | _                                                                                            | —                                                                        | _                                                                                                                 | _                                        | _   | —                      | -                   | —           |

| Vss                | 8,<br>19               | 5,<br>16      | _                | -                 | —             | -              | -                 | -                            | -                   | -                                          | —   | —                                                                                            | —                                                                        | —                                                                                                                 | —                                        | -   | —                      | _                   | —           |

| OUT <sup>(2)</sup> | _                      | _             | ADGRDA<br>ADGRDB |                   | _             | C1OUT<br>C2OUT | _                 | SDA1<br>SCL1<br>SDA2<br>SCL2 | SS1<br>SCK1<br>SDO1 | DTR1<br>RTS1<br>TX1<br>DTR2<br>RTS2<br>TX2 | DSM | TMR0                                                                                         | CCP1<br>CCP2<br>CCP3<br>CCP4<br>PWM50UT<br>PWM60UT<br>PWM70UT<br>PWM80UT | CWG1A<br>CWG1B<br>CWG1C<br>CWG1D<br>CWG2A<br>CWG2A<br>CWG2A<br>CWG2C<br>CWG3A<br>CWG3A<br>CWG3B<br>CWG3C<br>CWG3D | CLC10UT<br>CLC20UT<br>CLC30UT<br>CLC40UT | NCO | CLKR                   | _                   | _           |

TABLE 1: 28-PIN ALLOCATION TABLE (PIC18(L)F2XK42) (CONTINUED)

2: All output signals shown in this row are PPS remappable.

This is a bidirectional signal. For normal module operation, the firmware should map this signal to the same pin in both the PPS input and PPS output registers. These pins can be configured for I<sup>2</sup>C and SMB™ 3.0/2.0 logic levels; The SCLx/SDAx signals may be assigned to any of the RB1/RB2/RC3/RC4 pins. PPS assignments to the other pins (e.g., RA5) will operate, but input logic levels will be standard TTL/ST as selected by the INLVL register, instead of the I<sup>2</sup>C specific or SMBUs input buffer thresholds. 4:

3:

### **TABLE 1-1**: **DEVICE FEATURES (CONTINUED)**

| © 2016-2017 |  |

|-------------|--|

| Microchip   |  |

| Technology  |  |

| Inc.        |  |

| ADLE I-I. DEVICE FEATURES (CONTINUED)              |                |                                                                                                                       |                |                                  |                                   |                |                |                |  |  |  |  |  |

|----------------------------------------------------|----------------|-----------------------------------------------------------------------------------------------------------------------|----------------|----------------------------------|-----------------------------------|----------------|----------------|----------------|--|--|--|--|--|

| Features                                           | PIC18(L)F26K42 | PIC18(L)F27K42                                                                                                        | PIC18(L)F45K42 | PIC18(L)F46K42                   | PIC18(L)F47K42                    | PIC18(L)F55K42 | PIC18(L)F56K42 | PIC18(L)F57K42 |  |  |  |  |  |

| Comparator Module                                  |                |                                                                                                                       |                |                                  | 2                                 |                |                |                |  |  |  |  |  |

| Direct Memory Access<br>(DMA)                      |                |                                                                                                                       |                | :                                | 2                                 |                |                |                |  |  |  |  |  |

| Configurable Logic Cell (CLC)                      |                |                                                                                                                       |                |                                  | 4                                 |                |                |                |  |  |  |  |  |

| Peripheral Pin Select (PPS)                        |                |                                                                                                                       |                | Ye                               | es                                |                |                |                |  |  |  |  |  |

| Peripheral Module<br>Disable (PMD)                 |                | Yes                                                                                                                   |                |                                  |                                   |                |                |                |  |  |  |  |  |

| 16-bit CRC with Scanner                            |                | Yes                                                                                                                   |                |                                  |                                   |                |                |                |  |  |  |  |  |

| Programmable High/<br>Low-Voltage Detect<br>(HLVD) |                |                                                                                                                       |                | Yı                               | es                                |                |                |                |  |  |  |  |  |

| Resets (and Delays)                                |                | POR, Programmable BOR,<br>RESET Instruction,<br>Stack Overflow,<br>Stack Underflow<br>(PWRT, OST),<br>MCLR, WDT, MEMV |                |                                  |                                   |                |                |                |  |  |  |  |  |

| Instruction Set                                    |                |                                                                                                                       |                | 81 Instr<br>87 with Extended Ins | uctions;<br>struction Set enabled | 1              |                |                |  |  |  |  |  |

| Maximum Operating<br>Frequency                     |                |                                                                                                                       |                | 64 1                             | MHz                               |                |                |                |  |  |  |  |  |

Note 1: PORTE is partially implemented. Pin RE3 is an input-only pin on 28/40/44/48-pin variants. In addition to that, on 40/44/48-pin variants, PORTE also consists of RE0, RE1 and RE2 pins.

# PIC18(L)F26/27/45/46/47/55/56/57K42

### REGISTER 3-4: DMA2PR: DMA2 PRIORITY REGISTER

| U-0   | U-0 | U-0 | U-0 | U-0 | R/W-0/0     | R/W-1/1 R/W-1/1 |       |  |  |  |

|-------|-----|-----|-----|-----|-------------|-----------------|-------|--|--|--|

| —     | —   | —   | —   | _   | DMA2PR<2:0> |                 |       |  |  |  |

| bit 7 |     |     |     |     |             |                 | bit 0 |  |  |  |

### Legend:

| R = Readable bit     | W = Writable bit   | U = Unimplemented bit, read as '0'                    |

|----------------------|--------------------|-------------------------------------------------------|

| u = Bit is unchanged | x = Bit is unknown | -n/n = Value at POR and BOR/Value at all other Resets |

| 1 = bit is set       | 0 = bit is cleared | HS = Hardware set                                     |

### bit 7-3 Unimplemented: Read as '0'

bit 2-0 DMA2PR<2:0>: DMA2 Priority Selection bits

### REGISTER 3-5: SCANPR: SCANNER PRIORITY REGISTER

| U-0   | U-0 | U-0 | U-0 | U-0 | R/W-1/1     | R/W-0/0 |       |  |  |  |

|-------|-----|-----|-----|-----|-------------|---------|-------|--|--|--|

| —     | —   | —   | _   | —   | SCANPR<2:0> |         |       |  |  |  |

| bit 7 |     |     |     |     |             |         | bit 0 |  |  |  |

| Legend:              |                    |                                                       |

|----------------------|--------------------|-------------------------------------------------------|

| R = Readable bit     | W = Writable bit   | U = Unimplemented bit, read as '0'                    |

| u = Bit is unchanged | x = Bit is unknown | -n/n = Value at POR and BOR/Value at all other Resets |

| 1 = bit is set       | 0 = bit is cleared | HS = Hardware set                                     |

### bit 7-3 Unimplemented: Read as '0'

bit 2-0 SCANPR<2:0>: Scanner Priority Selection bits

### REGISTER 3-6: PRLOCK: PRIORITY LOCK REGISTER

| U-0   | U-0 | U-0 | U-0 | U-0 | U-0 | U-0 | R/W-0/0  |

|-------|-----|-----|-----|-----|-----|-----|----------|

| —     | —   | —   | —   | —   | —   | —   | PRLOCKED |

| bit 7 |     |     |     |     |     |     | bit 0    |

| Legend:              |                    |                                                       |

|----------------------|--------------------|-------------------------------------------------------|

| R = Readable bit     | W = Writable bit   | U = Unimplemented bit, read as '0'                    |

| u = Bit is unchanged | x = Bit is unknown | -n/n = Value at POR and BOR/Value at all other Resets |

| 1 = bit is set       | 0 = bit is cleared | HS = Hardware set                                     |

bit 7-1 Unimplemented: Read as '0'

bit 0 PRLOCKED: PR Register Lock bit<sup>(1, 2)</sup>

0 = Priority Registers can be modified by write operations; Peripherals do not have access to the memory

1 = Priority Registers are locked and cannot be written; Peripherals have access to the memory

- Note 1: The PRLOCKED bit can only be set or cleared after the unlock sequence.

- 2: If PR1WAY = 1, the PRLOCKED bit cannot be cleared after it has been set. A device Reset will clear the bit and allow one more set.

### TABLE 4-3: SPECIAL FUNCTION REGISTER MAP FOR PIC18(L)F26/27/45/46/47/55/56/57K42 DEVICES BANK 64

|         |            |       |            | _     |            | _     |            |       |          |       |   |       |   |       |   |

|---------|------------|-------|------------|-------|------------|-------|------------|-------|----------|-------|---|-------|---|-------|---|

| 40FFh   | —          | 40DFh |            | 40BFh | —          | 409Fh | —          | 407Fh | _        | 405Fh | — | 403Fh |   | 401Fh | _ |

| 40FEh   | —          | 40DEh |            | 40BEh | _          | 409Eh | _          | 407Eh | _        | 405Eh | — | 403Eh |   | 401Eh | _ |

| 40FDh   | _          | 40DDh | T6PR_M2    | 40BDh | ADRESH_M2  | 409Dh | _          | 407Dh | _        | 405Dh | — | 403Dh | - | 401Dh | _ |

| 40FCh   | _          | 40DCh | PWM5DCH_M2 | 40BCh | ADRESL_M2  | 409Ch | _          | 407Ch | _        | 405Ch | — | 403Ch | - | 401Ch | _ |

| 40FBh   | TMR5H_M1   | 40DBh | PWM5DCL_M2 | 40BBh | ADPCH_M2   | 409Bh | _          | 407Bh | _        | 405Bh | — | 403Bh | - | 401Bh | _ |

| 40FAh   | TMR5L_M1   | 40DAh | T6PR_M1    | 40BAh | ADCLK_M1   | 409Ah | —          | 407Ah | _        | 405Ah | — | 403Ah |   | 401Ah | _ |

| 40F9h   | TMR3H_M1   | 40D9h | CCPR1H_M2  | 40B9h | ADACT_M1   | 4099h | —          | 4079h | _        | 4059h | — | 4039h |   | 4019h | _ |

| 40F8h   | TMR3L_M1   | 40D8h | CCPR1L_M2  | 40B8h | ADREF_M1   | 4098h | —          | 4078h | _        | 4058h | — | 4038h |   | 4018h | _ |

| 40F7h   | TMR1H_M1   | 40D7h | T4PR_M4    | 40B7h | ADCON3_M1  | 4097h | —          | 4077h | _        | 4057h | — | 4037h |   | 4017h | _ |

| 40F6h   | TMR1L_M1   | 40D6h | PWM8DCH_M1 | 40B6h | ADCON2_M1  | 4096h | ADRESH_M1  | 4076h | _        | 4056h | — | 4036h |   | 4016h | _ |

| 40F5h   | —          | 40D5h | PWM8DCL_M1 | 40B5h | ADCON1_M1  | 4095h | ADRESL_M1  | 4075h | _        | 4055h | — | 4035h |   | 4015h | _ |

| 40F4h   | —          | 40D4h | T4PR_M3    | 40B4h | ADCON0_M1  | 4094h | ADPCH_M1   | 4074h | _        | 4054h | — | 4034h |   | 4014h | _ |

| 40F3h   | —          | 40D3h | PWM7DCH_M1 | 40B3h | ADCAP_M2   | 4093h | ADCAP_M1   | 4073h | _        | 4053h | — | 4033h | _ | 4013h | — |

| 40F2h   | —          | 40D2h | PWM7DCL_M1 | 40B2h | ADACQH_M2  | 4092h | ADACQH_M1  | 4072h | —        | 4052h | — | 4032h | — | 4012h | — |

| 40F1h   | —          | 40D1h | T4PR_M2    | 40B1h | ADACQL_M2  | 4091h | ADACQL_M1  | 4071h | _        | 4051h | — | 4031h | — | 4011h | — |

| 40F0h   | —          | 40D0h | CCPR4H_M1  | 40B0h | ADPREVH_M2 | 4090h | ADPREVH_M1 | 4070h | _        | 4050h | — | 4030h | — | 4010h | — |

| 40EFh P | WM8DCH_M2  | 40CFh | CCPR4L_M1  | 40AFh | ADPREVL_M2 | 408Fh | ADPREVL_M1 | 406Fh | _        | 404Fh | — | 402Fh | — | 400Fh | — |

| 40EEh P | WM8DCL_M2  | 40CEh | T4PR_M1    | 40AEh | ADRPT_M2   | 408Eh | ADRPT_M1   | 406Eh | _        | 404Eh | — | 402Eh | — | 400Eh | — |

| 40EDh P | WM7DCH_M2  | 40CDh | CCPR3H_M1  | 40ADh | ADCNT_M2   | 408Dh | ADCNT_M1   | 406Dh | _        | 404Dh | — | 402Dh | — | 400Dh | — |

| 40ECh P | WM7DCL_M2  | 40CCh | CCPR3L_M1  | 40ACh | ADACCU_M2  | 408Ch | ADACCU_M1  | 406Ch | _        | 404Ch | — | 402Ch | — | 400Ch | — |

| 40EBh P | WM6DCH_M2  | 40CBh | T2PR_M3    | 40ABh | ADACCH_M2  | 408Bh | ADACCH_M1  | 406Bh | _        | 404Bh | — | 402Bh | — | 400Bh | — |

|         | WM6DCL_M2  | 40CAh | PWM6DCH_M1 | 40AAh | ADACCL_M2  | 408Ah | ADACCL_M1  | 406Ah | _        | 404Ah | — | 402Ah |   | 400Ah | _ |

| 40E9h P | WM5DCH_M3  | 40C9h | PWM6DCL_M1 | 40A9h | ADFLTRH_M2 | 4089h | ADFLTRH_M1 | 4069h | _        | 4049h | — | 4029h |   | 4009h | _ |

| 40E8h P | PWM5DCL_M3 | 40C8h | T2PR_M2    | 40A8h | ADFLTRL_M2 | 4088h | ADFLTRL_M1 | 4068h | _        | 4048h | — | 4028h |   | 4008h | _ |

| 40E7h ( | CCPR4H_M2  | 40C7h | PWM5DCH_M1 | 40A7h | ADSTPTH_M2 | 4087h | ADSTPTH_M1 | 4067h | _        | 4047h | — | 4027h | — | 4007h | — |

| 40E6h   | CCPR4L_M2  | 40C6h | PWM5DCL_M1 | 40A6h | ADSTPTL_M2 | 4086h | ADSTPTL_M1 | 4066h | _        | 4046h | — | 4026h | — | 4006h | — |

| 40E5h ( | CCPR3H_M2  | 40C5h | T2PR_M2    | 40A5h | ADERRH_M2  | 4085h | ADERRH_M1  | 4065h | _        | 4045h | — | 4025h | — | 4005h | — |

| 40E4h   | CCPR3L_M2  | 40C4h | CCPR2H_M1  | 40A4h | ADERRL_M2  | 4084h | ADERRL_M1  | 4064h | _        | 4044h | — | 4024h | _ | 4004h |   |

| 40E3h   | CCPR2H_M2  | 40C3h | CCPR2L_M1  | 40A3h | ADUTHH_M2  | 4083h | ADUTHH_M1  | 4063h | IOCEF_M1 | 4043h | _ | 4023h | _ | 4003h | — |

| 40E2h   | CCPR2L_M2  | 40C2h | T2PR_M1    | 40A2h | ADUTHL_M2  | 4082h | ADUTHL_M1  | 4062h | IOCCF_M1 | 4042h | — | 4022h | — | 4002h |   |

| 40E1h   | CCPR1H_M3  | 40C1h | CCPR1H_M1  | 40A1h | ADLTHH_M2  | 4081h | ADLTHH_M1  | 4061h | IOCBF_M1 | 4041h | — | 4021h | — | 4001h |   |

| 40E0h   | CCPR1L_M3  | 40C0h | CCPR1L_M1  | 40A0h | ADLTHL_M2  | 4080h | ADLTHL_M1  | 4060h | IOCAF_M1 | 4040h | _ | 4020h | _ | 4000h | _ |

Note 1: Addresses in Bank 64 are accessible ONLY through DMA Source and Destination Address Registers. CPU does not have access to registers in Bank 64.

### 7.2 Clock Source Types

Clock sources can be classified as external or internal.

External clock sources rely on external circuitry for the clock source to function. Examples are: oscillator modules (ECH, ECM, ECL mode), quartz crystal resonators or ceramic resonators (LP, XT and HS modes).

Internal clock sources are contained within the oscillator module. The internal oscillator block has two internal oscillators that are used to generate internal system clock sources. The High-Frequency Internal Oscillator (HFINTOSC) can produce 1, 2, 4, 8, 12, 16, 32, 48 and 64 MHz clock. The frequency can be controlled through the OSCFRQ register (Register 7-5). The Low-Frequency Internal Oscillator (LFINTOSC) generates a fixed 31 kHz frequency.

A 4x PLL is provided that can be used with an external clock. When used with the HFINTOSC the 4x PLL has input frequency limitations.See **Section 7.2.1.4 "4x PLL"** for more details.

The system clock can be selected between external or internal clock sources via the NOSC bits in the OSCCON1 register. See **Section 7.3 "Clock Switching"** for additional information. The system clock can be made available on the OSC2/CLKOUT pin for any of the modes that do not use the OSC2 pin. The clock out functionality is governed by the CLKOUTEN bit in the CONFIG1H register (Register 5-2). If enabled, the clock out signal is always at a frequency of Fosc/4.

### 7.2.1 EXTERNAL CLOCK SOURCES

An external clock source can be used as the device system clock by performing one of the following actions:

- Program the RSTOSC<2:0> and FEXTOSC<2:0> bits in the Configuration Words to select an external clock source that will be used as the default system clock upon a device Reset.

- Write the NOSC<2:0> and NDIV<3:0> bits in the OSCCON1 register to switch the system clock source.

See **Section 7.3 "Clock Switching"** for more information.

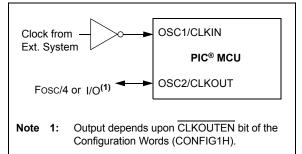

### 7.2.1.1 EC Mode

The External Clock (EC) mode allows an externally generated logic level signal to be the system clock source. When operating in this mode, an external clock source is connected to the OSC1 input. OSC2/ CLKOUT is available for general purpose I/O or CLKOUT. Figure 7-2 shows the pin connections for EC mode. EC mode has three power modes to select from through Configuration Words:

- ECH High power

- ECM Medium power

- · ECL Low power

Refer to Table 44-9 for External Clock/Oscillator Timing Requirements. The Oscillator Start-up Timer (OST) is disabled when EC mode is selected. Therefore, there is no delay in operation after a Power-on Reset (POR) or wake-up from Sleep. Because the PIC<sup>®</sup> MCU design is fully static, stopping the external clock input will have the effect of halting the device while leaving all data intact. Upon restarting the external clock, the device will resume operation as if no time had elapsed.

### FIGURE 7-2: EXTERNAL CLOCK (EC) MODE OPERATION

### 7.2.1.2 LP, XT, HS Modes

The LP, XT and HS modes support the use of quartz crystal resonators or ceramic resonators connected to OSC1 and OSC2 (Figure 7-3). The three modes select a low, medium or high gain setting of the internal inverter-amplifier to support various resonator types and speed.

**LP** Oscillator mode selects the lowest gain setting of the internal inverter-amplifier. LP mode current consumption is the least of the three modes. This mode is designed to drive only 32.768 kHz tuning-fork type crystals (watch crystals).

**XT** Oscillator mode selects the intermediate gain setting of the internal inverter-amplifier. XT mode current consumption is the medium of the three modes. This mode is best suited to drive resonators with a medium drive level specification (above 100 kHz - 8 MHz).

**HS** Oscillator mode selects the highest gain setting of the internal inverter-amplifier. HS mode current consumption is the highest of the three modes. This mode is best suited for resonators that require a high drive setting (above 8 MHz).

Figure 7-3 and Figure 7-4 show typical circuits for quartz crystal and ceramic resonators, respectively.

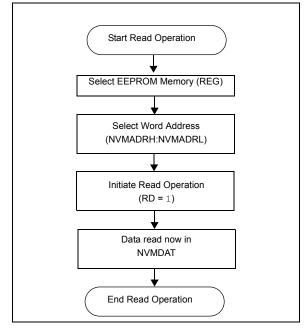

### 13.3.3 READING THE DATA EEPROM MEMORY

To read a data memory location, the user must write the address to the NVMADRL and NVMADRH register pair, clear REG<1:0> control bit in NVMCON1 register to access Data EEPROM locations and then set control bit, RD. The data is available on the very next instruction cycle; therefore, the NVMDAT register can be read by the next instruction. NVMDAT will hold this value until another read operation, or until it is written to by the user (during a write operation).

The basic process is shown in Example 13-5.

### FIGURE 13-11: DATA EEPROM READ FLOWCHART

## 13.3.4 WRITING TO THE DATA EEPROM MEMORY

To write an EEPROM data location, the address must first be written to the NVMADRL and NVMADRH register pair and the data written to the NVMDAT register. The sequence in Example 13-6 must be followed to initiate the write cycle.

The write will not begin if NVM Unlock sequence, described in **Section 13.1.4 "NVM Unlock Sequence"**, is not exactly followed for each byte. It is strongly recommended that interrupts be disabled during this code segment.

Additionally, the WREN bit in NVMCON1 must be set to enable writes. This mechanism prevents accidental writes to data EEPROM due to unexpected code execution (i.e., runaway programs). The WREN bit should be kept clear at all times, except when updating the EEPROM. The WREN bit is not cleared by hardware.

After a write sequence has been initiated, NVMCON1, NVMADRL, NVMADRH and NVMDAT cannot be modified. The WR bit will be inhibited from being set unless the WREN bit is set. Both WR and WREN cannot be set with the same instruction.

After a write sequence has been initiated, clearing the WREN bit will not affect this write cycle. A single Data EEPROM word is written and the operation includes an implicit erase cycle for that word (it is not necessary to set FREE). CPU execution continues in parallel and at the completion of the write cycle, the WR bit is cleared in hardware and the NVM Interrupt Flag bit (NVMIF) is set. The user can either enable this interrupt or poll this bit. NVMIF must be cleared by software.

# PIC18(L)F26/27/45/46/47/55/56/57K42

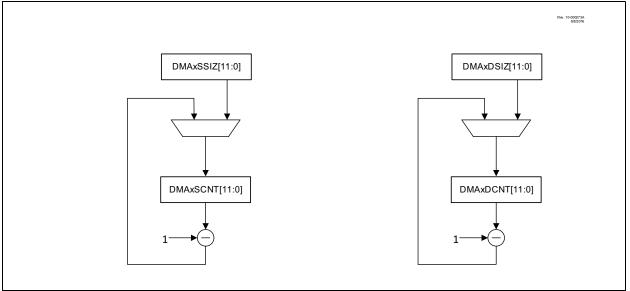

### FIGURE 15-3: DMA COUNTERS BLOCK DIAGRAM

Table 15-2 has a few examples of configuring DMAMessage sizes.

| TABLE 15-2: | EXAMPLE | E MESSAGE SIZE | TABLE |      |

|-------------|---------|----------------|-------|------|

| Operat      | ion     | Example        | SCNT  | DONT |

| Operation                                | Example           | SCNT | DCNT | Comments                                                                                  |

|------------------------------------------|-------------------|------|------|-------------------------------------------------------------------------------------------|

| Read from single SFR<br>location to RAM  | U1RXB             | 1    | Ν    | N equals the number of bytes desired in the destination buffer. N >= 1.                   |

| Write to single SFR location<br>from RAM | U1TXB             | N    | 1    | N equals the number of bytes desired in the source buffer. N >= 1.                        |

|                                          | ADRES[H:L]        | 2    | 2*N  | N equals the number of ADC results to be stored in memory. N>= 1                          |

| Read from multiple SFR location          | TMR1[H:L]         | 2    | 2*N  | N equals the number of TMR1 Acquisition results to be stored in memory. N>= 1             |

|                                          | SMT1CPR[U:H:L]    | 3    | 3*N  | N equals the number of Capture Pulse Width measurements to be stored in memory. N>= 1     |

| Write to Multiple SFR regis-             | PWMDC[H:L]        | 2*N  | 2    | N equals the number of PWM duty cycle val-<br>ues to be loaded from a memory table. N>= 1 |

| ters                                     | All ADC registers | N*31 | 31   | Using the DMA to transfer a complete ADC context from RAM to the ADC registers.N>= 1      |

### 16.2.6 INPUT THRESHOLD CONTROL

The INLVLx register (Register 16-8) controls the input voltage threshold for each of the available PORTx input pins. A selection between the Schmitt Trigger CMOS or the TTL compatible thresholds is available. The input threshold is important in determining the value of a read of the PORTx register and also the level at which an interrupt-on-change occurs, if that feature is enabled. See Table 44-6 for more information on threshold levels.

**Note:** Changing the input threshold selection should be performed while all peripheral modules are disabled. Changing the threshold level during the time a module is active may inadvertently generate a transition associated with an input pin, regardless of the actual voltage level on that pin.

### 16.2.7 WEAK PULL-UP CONTROL

The WPUx register (Register 16-5) controls the individual weak pull-ups for each port pin.

### 16.2.8 EDGE SELECTABLE INTERRUPT-ON-CHANGE

An interrupt can be generated by detecting a signal at the port pin that has either a rising edge or a falling edge. Any individual pin can be configured to generate an interrupt. The interrupt-on-change module is present on all the pins. For further details about the IOC module refer to Section 18.0 "Interrupt-on-Change".

### 16.2.9 I<sup>2</sup>C PAD CONTROL

For the PIC18(L)F26/27/45/46/47/55/56/57K42 devices, the  $I^2C$  specific pads are available on RB1, RB2, RC3, RC4, RD0<sup>(1)</sup> and RD1<sup>(1)</sup> pins. The  $I^2C$  characteristics of each of these pins is controlled by the RxyI2C registers (see Register 16-9). These characteristics include enabling  $I^2C$  specific slew rate (over standard GPIO slew rate), selecting internal pullups for  $I^2C$  pins, and selecting appropriate input threshold as per SMBus specifications.

### **Note 1:** RD0 and RD1 I<sup>2</sup>C pads are not available in PIC18(L)F26K42 parts.

Any peripheral using the I<sup>2</sup>C pins read the I<sup>2</sup>C ST inputs when enabled via RxyI2C.

### 16.3 PORTE Registers

Depending on the device, PORTE is implemented in two different ways.

### 16.3.1 PORTE ON 40/44/48-PIN DEVICES

For PIC18(L)F45/46/47/55/56/57K42 devices, PORTE is a 4-bit wide port. Three pins (RE0, RE1 and RE2) are individually configurable as inputs or outputs. These pins have Schmitt Trigger input buffers. When selected as an analog input, these pins will read as '0's. The corresponding data direction register is TRISE. Setting a TRISE bit (= 1) will make the corresponding PORTE pin an input (i.e., disable the output driver).

Clearing a TRISE bit (= 0) will make the corresponding PORTE pin an output (i.e., enable the output driver and put the contents of the output latch on the selected pin). TRISE controls the direction of the REx pins, even when they are being used as analog pins. The user must make sure to keep the pins configured as inputs when using them as analog inputs. RE<2:0> bits have other registers associated with them (i.e., ANSELE, WPUE, INLVLE, SLRCONE and ODCONE). The functionality is similar to the other ports. The Data Latch register (LATE) is also memory-mapped. Readmodify-write operations on the LATE register read and write the latched output value for PORTE.

Note: On a Power-on Reset, RE<2:0> are configured as analog inputs.

The fourth pin of PORTE (MCLR/VPP/RE3) is an input-only pin. Its operation is controlled by the MCLRE Configuration bit. When selected as a port pin, (MCLRE = 0), it functions as a digital input-only pin; as such, it does not have TRIS or LAT bits associated with its operation. Otherwise, it functions as the device's Master Clear input. In either configuration, RE3 also functions as the programming voltage input during programming. RE3 in PORTE register is a read-only bit and will read '1' when MCLRE = 1 (i.e., Master Clear enabled).

Note: On a Power-on Reset, RE3 is enabled as a digital input only if Master Clear functionality is disabled.

x = Bit is unknown

| R/W-1/1          | R/W-1/1 | R/W-1/1          | R/W-1/1 | R/W-1/1                            | R/W-1/1 | R/W-1/1 | R/W-1/1 |

|------------------|---------|------------------|---------|------------------------------------|---------|---------|---------|

| INLVLx7          | INLVLx6 | INLVLx5          | INLVLx4 | INLVLx3                            | INLVLx2 | INLVLx1 | INLVLx0 |

| bit 7            |         |                  |         |                                    |         |         | bit 0   |

|                  |         |                  |         |                                    |         |         |         |

| Legend:          |         |                  |         |                                    |         |         |         |

| R = Readable bit |         | W = Writable bit |         | U = Unimplemented bit, read as '0' |         |         |         |

### REGISTER 16-8: INLVLx: INPUT LEVEL CONTROL REGISTER

-n/n = Value at POR and BOR/Value at all other Resets

'0' = Bit is cleared

bit 7-0

'1' = Bit is set

- INLVLx<7:0>: Input Level Select on Pins Rx<7:0>, respectively

- 1 = ST input used for port reads and interrupt-on-change

0 = TTL input used for port reads and interrupt-on-change

TABLE 16-9: INPUT LEVEL PORT REGISTERS

| Name                  | Bit 7   | Bit 6   | Bit 5   | Bit 4                  | Bit 3                  | Bit 2                  | Bit 1                  | Bit 0                  |

|-----------------------|---------|---------|---------|------------------------|------------------------|------------------------|------------------------|------------------------|

| INLVLA                | INLVLA7 | INLVLA6 | INLVLA5 | INLVLA4                | INLVLA3                | INLVLA2                | INLVLA1                | INLVLA0                |

| INLVLB                | INLVLB7 | INLVLB6 | INLVLB5 | INLVLB4                | INLVLB3                | INLVLB2 <sup>(1)</sup> | INLVLB1 <sup>(1)</sup> | INLVLB0                |

| INLVLC                | INLVLC7 | INLVLC6 | INLVLC5 | INLVLC4 <sup>(1)</sup> | INLVLC3 <sup>(1)</sup> | INLVLC2                | INLVLC1                | INLVLC0                |

| INLVLD <sup>(2)</sup> | INLVLD7 | INLVLD6 | INLVLD5 | INLVLD4                | INLVLD3                | INLVLD2                | INLVLD1 <sup>(1)</sup> | INLVLD0 <sup>(1)</sup> |

| INLVLE                |         | _       | _       | —                      | INLVLE3                | INLVLE2 <sup>(2)</sup> | INLVLE1 <sup>(2)</sup> | INLVLE0 <sup>(2)</sup> |

| INLVLF <sup>(3)</sup> | INLVLF7 | INLVLF6 | INLVLF5 | INLVLF4                | INLVLF3                | INLVLF2                | INLVLF1                | INLVLF0                |

**Note 1:** Any peripheral using the  $I^2C$  pins read the  $I^2C$  ST inputs when enabled via Rxyl2C.

2: Unimplemented in PIC18(L)F26/27K42.

**3:** Unimplemented in PIC18(L)F26/27/45/46/47K42.

|                   | MODE  | <4:0>                  | Output                   | Onersting                                               |                          | Timer Control |                                        |

|-------------------|-------|------------------------|--------------------------|---------------------------------------------------------|--------------------------|---------------|----------------------------------------|

| Mode              | <4:3> | <2:0>                  | Operation                | Operation                                               | Start                    | Reset         | Stop                                   |

|                   |       | 000                    |                          | Software gate (Figure 22-6)                             | <b>ON =</b> 1            | _             | <b>ON =</b> 0                          |

|                   |       | 001                    | Period<br>Pulse          | Hardware gate, active-high<br>(Figure 22-7)             | ON = 1 &<br>TMRx_ers = 1 | _             | ON = 0 or<br>TMRx_ers = 0              |

|                   |       | 010                    | 1 0136                   | Hardware gate, active-low                               | ON = 1 &<br>TMRx_ers = 0 | _             | ON = 0 or<br>TMRx_ers = 1              |

| Free              |       | 011                    |                          | Rising or Falling Edge Reset                            |                          | TMRx_ers      |                                        |

| Running<br>Period | 00    | 100                    | Period                   | Rising Edge Reset (Figure 22-8)                         | _                        | TMRx_ers ↑    | <b>ON =</b> 0                          |

|                   |       | 101                    | Pulse                    | Falling Edge Reset                                      | ]                        | TMRx_ers ↓    |                                        |

|                   |       | 110                    | with<br>Hardware         | Low Level Reset                                         | <b>ON =</b> 1            | TMRx_ers = 0  | ON = 0 or<br>TMRx_ers = 0              |

|                   |       | 111                    | Reset                    | High Level Reset (Figure 22-9)                          |                          | TMRx_ers = 1  | ON = 0 or<br>TMRx_ers = 1              |

|                   |       | 000                    | One-Shot                 | Software Start (Figure 22-10)                           | <b>ON =</b> 1            | _             |                                        |

|                   |       | 001                    | Edge                     | Rising Edge Start (Figure 22-9)                         | ON = 1 &<br>TMRx_ers ↑   | _             |                                        |

|                   |       | 010 Triggered<br>Start | Falling Edge Start       | ON = 1 &<br>TMRx_ers ↓                                  | _                        |               |                                        |

|                   |       | 011                    | (Note 1)                 | Any eEdge Start                                         | ON = 1 &<br>TMRx_ers     | _             | ON = 0<br>or                           |

| One-shot          | 01    | 100                    | Edge                     | Rising Edge Start &<br>Rising Edge Reset (Figure 22-12) | ON = 1 &<br>TMRx_ers ↑   | TMRx_ers ↑    | Next clock after<br>TMRx = PRx         |

|                   |       | 101                    | Triggered<br>Start       | Falling Edge Start &<br>Falling Edge Reset              | ON = 1 &<br>TMRx_ers ↓   | TMRx_ers ↓    | (Note 2)                               |

|                   |       | 110                    | and<br>Hardware<br>Reset | Rising Edge Start &<br>Low Level Reset (Figure 22-13)   | ON = 1 &<br>TMRx_ers ↑   | TMRx_ers = 0  |                                        |

|                   |       | 111                    | (Note 1)                 | Falling Edge Start &<br>High Level Reset                | ON = 1 &<br>TMRx_ers ↓   | TMRx_ers = 1  |                                        |

|                   |       | 000                    |                          | Res                                                     |                          |               |                                        |

|                   |       | 001                    | Edge                     | Rising Edge Start<br>(Figure 22-12)                     | ON = 1 &<br>TMRx_ers ↑   | —             | ON=0                                   |

| Monostable        |       | 010                    | Triggered<br>Start       | Falling Edge Start                                      | ON = 1 &<br>TMRx_ers ↓   | —             | or<br>Next clock after<br>TxTMR = TxPR |

|                   |       | 011                    | (Note 1)                 | Any Edge Start                                          | ON = 1 &<br>TMRx_ers     | _             | (Note 3)                               |

| Reserved          | 10    | 100                    |                          | Res                                                     | erved                    |               |                                        |

| Reserved          |       | 101                    |                          | Res                                                     | erved                    |               |                                        |

|                   |       | 110                    | Level<br>Triggered       | High Level Start &<br>Low Level Reset (Figure 22-13)    | ON = 1 &<br>TMRx_ers = 1 | TMRx_ers = 0  | ON = 0 or                              |

| 0                 |       |                        | Start<br>and             | Low Level Start &                                       | ON = 1 &                 |               | Held in Reset                          |

| One-shot          |       | 111                    | Hardware<br>Reset        | High Level Reset                                        | TMRx_ers = 0             | TMRx_ers = 1  | (Note 2)                               |

### TABLE 22-1: TIMER2 OPERATING MODES

**Note 1:** If ON = 0 then an edge is required to restart the timer after ON = 1.

2: When TxTMR = TxPR then the next clock clears ON and stops TxTMR at 00h.

3: When TxTMR = TxPR then the next clock stops TxTMR at 00h but does not clear ON.

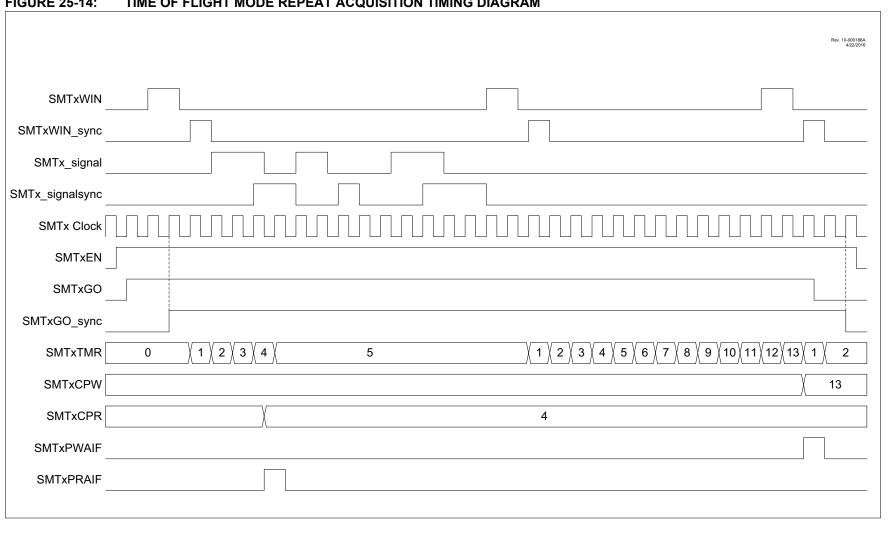

### FIGURE 25-14: TIME OF FLIGHT MODE REPEAT ACQUISITION TIMING DIAGRAM

| R/W/HC-0/0       | R/W-0/0                                                         | U-0                                                        | U-0           | R/W-0/0        | R/W-0/0         | R/W-0/0        | R/W-0/0      |  |  |

|------------------|-----------------------------------------------------------------|------------------------------------------------------------|---------------|----------------|-----------------|----------------|--------------|--|--|

| GO               | REPEAT                                                          |                                                            |               |                | MODE            | <3:0>          |              |  |  |

| bit 7            |                                                                 |                                                            |               |                |                 |                | bit (        |  |  |

| Legend:          |                                                                 |                                                            |               |                |                 |                |              |  |  |

| HC = Bit is clea | ared by hardv                                                   | vare                                                       |               | HS = Bit is se | t by hardware   |                |              |  |  |

| R = Readable     | bit                                                             | W = Writable                                               | bit           | U = Unimplen   | nented bit, rea | d as '0'       |              |  |  |

| u = Bit is unch  | anged                                                           | x = Bit is unkr                                            | iown          | -n/n = Value a | at POR and BC   | R/Value at all | other Resets |  |  |

| '1' = Bit is set |                                                                 | '0' = Bit is clea                                          | ared          | q = Value dep  | ends on condi   | tion           |              |  |  |

|                  |                                                                 |                                                            |               |                |                 |                |              |  |  |

| bit 7            | 1 = Increme                                                     | ta Acquisition bit<br>nting, acquiring<br>nting, acquiring | data is enabl |                |                 |                |              |  |  |

| bit 6            | 1 = Repeat I                                                    | MT Repeat Acqu<br>Data Acquisition<br>cquisition mode      | mode is ena   |                |                 |                |              |  |  |

| bit 5-4          | Unimpleme                                                       | nted: Read as '                                            | )'            |                |                 |                |              |  |  |

| bit 3-0          | MODE<3:0> SMT Operation Mode Select bits                        |                                                            |               |                |                 |                |              |  |  |

|                  | 1111 <b>= Res</b>                                               | erved                                                      |               |                |                 |                |              |  |  |

|                  | •                                                               |                                                            |               |                |                 |                |              |  |  |

|                  | •                                                               |                                                            |               |                |                 |                |              |  |  |

|                  | 1011 <b>= Res</b>                                               | erved                                                      |               |                |                 |                |              |  |  |

|                  |                                                                 | dowed counter                                              |               |                |                 |                |              |  |  |

|                  | 1001 = Gate<br>1000 = Cou                                       |                                                            |               |                |                 |                |              |  |  |

|                  | 0111 = Cap                                                      |                                                            |               |                |                 |                |              |  |  |

|                  | 0110 <b>= Time</b>                                              |                                                            |               |                |                 |                |              |  |  |

|                  |                                                                 | ed windowed me                                             | asure         |                |                 |                |              |  |  |

|                  | 0100 = Windowed measure<br>0011 = High and low time measurement |                                                            |               |                |                 |                |              |  |  |

|                  |                                                                 | od and Duty-Cyc                                            |               | n              |                 |                |              |  |  |

|                  | 0001 <b>= Gate</b>                                              |                                                            | ·             |                |                 |                |              |  |  |

|                  | 0000 = Time                                                     |                                                            |               |                |                 |                |              |  |  |

### REGISTER 25-2: SMT1CON1: SMT CONTROL REGISTER 1

| R/W-x/u          | R/W-x/u                                                                                                          | R/W-x/u                              | R/W-x/u         | R/W-x/u        | R/W-x/u          | R/W-x/u          | R/W-x/u     |  |

|------------------|------------------------------------------------------------------------------------------------------------------|--------------------------------------|-----------------|----------------|------------------|------------------|-------------|--|

| G4D4T            | G4D4N                                                                                                            | G4D3T                                | G4D3N           | G4D2T          | G4D2N            | G4D1T            | G4D1N       |  |

| bit 7            |                                                                                                                  |                                      |                 |                |                  |                  | bit C       |  |

|                  |                                                                                                                  |                                      |                 |                |                  |                  |             |  |

| Legend:          |                                                                                                                  |                                      |                 |                |                  |                  |             |  |

| R = Readable     | bit                                                                                                              | W = Writable                         | bit             | U = Unimpler   | mented bit, read | l as '0'         |             |  |

| u = Bit is unch  | anged                                                                                                            | x = Bit is unkr                      | nown            | -n/n = Value a | at POR and BO    | R/Value at all c | ther Resets |  |

| '1' = Bit is set |                                                                                                                  | '0' = Bit is clea                    | ared            |                |                  |                  |             |  |

|                  |                                                                                                                  |                                      |                 |                |                  |                  |             |  |

| bit 7            | G4D4T: Gate                                                                                                      | e 3 Data 4 True                      | (non-inverted)  | ) bit          |                  |                  |             |  |

|                  |                                                                                                                  | (true) is gated i                    |                 |                |                  |                  |             |  |

|                  |                                                                                                                  | (true) is not gat                    |                 |                |                  |                  |             |  |

| bit 6            |                                                                                                                  | e 3 Data 4 Nega                      | · · ·           | ·              |                  |                  |             |  |

|                  |                                                                                                                  | (inverted) is ga<br>(inverted) is no |                 |                |                  |                  |             |  |

| bit 5            |                                                                                                                  | e 3 Data 3 True                      | •               |                |                  |                  |             |  |

| bit 5            |                                                                                                                  | (true) is gated i                    |                 |                |                  |                  |             |  |

|                  |                                                                                                                  | (true) is not gat                    |                 |                |                  |                  |             |  |

| bit 4            | G4D3N: Gate                                                                                                      | e 3 Data 3 Nega                      | ated (inverted) | ) bit          |                  |                  |             |  |

|                  | 1 = CLCIN2                                                                                                       | (inverted) is ga                     | ted into CLCx   | Gate 3         |                  |                  |             |  |

|                  | 0 = CLCIN2                                                                                                       | (inverted) is no                     | t gated into C  | LCx Gate 3     |                  |                  |             |  |

| bit 3            | G4D2T: Gate                                                                                                      | e 3 Data 2 True                      | (non-inverted)  | ) bit          |                  |                  |             |  |

|                  |                                                                                                                  | (true) is gated i                    |                 |                |                  |                  |             |  |

|                  |                                                                                                                  | (true) is not gat                    |                 |                |                  |                  |             |  |

| bit 2            |                                                                                                                  | e 3 Data 2 Nega                      |                 |                |                  |                  |             |  |

|                  |                                                                                                                  | (inverted) is ga<br>(inverted) is no |                 |                |                  |                  |             |  |

| bit 1            |                                                                                                                  | e 4 Data 1 True                      | •               |                |                  |                  |             |  |

|                  |                                                                                                                  |                                      | •               | ,              |                  |                  |             |  |

|                  | <ol> <li>CLCIN0 (true) is gated into CLCx Gate 3</li> <li>CLCIN0 (true) is not gated into CLCx Gate 3</li> </ol> |                                      |                 |                |                  |                  |             |  |

| bit 0            | G4D1N: Gate                                                                                                      | e 3 Data 1 Nega                      | ated (inverted) | ) bit          |                  |                  |             |  |

|                  |                                                                                                                  | (inverted) is ga                     |                 |                |                  |                  |             |  |

|                  | 0 = CLCIN0                                                                                                       | (inverted) is no                     | t gated into C  | LCx Gate 3     |                  |                  |             |  |

### REGISTER 27-10: CLCxGLS3: GATE 3 LOGIC SELECT REGISTER

### 29.0 ZERO-CROSS DETECTION (ZCD) MODULE

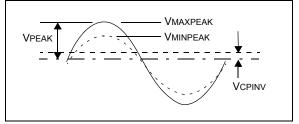

The ZCD module detects when an A/C signal crosses through the ground potential. The actual zero-crossing threshold is the zero-crossing reference voltage, VCPINV, which is typically 0.75V above ground.

The connection to the signal to be detected is through a series current-limiting resistor. The module applies a current source or sink to the ZCD pin to maintain a constant voltage on the pin, thereby preventing the pin voltage from forward biasing the ESD protection diodes. When the applied voltage is greater than the reference voltage, the module sinks current. When the applied voltage is less than the reference voltage, the module sources current. The current source and sink action keeps the pin voltage constant over the full range of the applied voltage. The ZCD module is shown in the simplified block diagram Figure 29-2.

The ZCD module is useful when monitoring an A/C waveform for, but not limited to, the following purposes:

- A/C period measurement

- Accurate long term time measurement

- Dimmer phase delayed drive

- Low EMI cycle switching

### 29.1 External Resistor Selection

The ZCD module requires a current-limiting resistor in series with the external voltage source. The impedance and rating of this resistor depends on the external source peak voltage. Select a resistor value that will drop all of the peak voltage when the current through the resistor is nominally 300  $\mu$ A. Refer to Equation 29-1 and Figure 29-1. Make sure that the ZCD I/O pin internal weak pull-up is disabled so it does not interfere with the current source and sink.

### EQUATION 29-1: EXTERNAL RESISTOR

$$RSERIES = \frac{VPEAK}{3 \times 10^{-4}}$$

FIGURE 29-1: EXTERNA

### 30.11 Register Definitions: Modulation Control

Long bit name prefixes for the Modulation peripheral is shown below. Refer to **Section 1.3.2.2 "Long Bit Names**" for more information.

| Peripheral | Bit Name Prefix |

|------------|-----------------|

| MD1        | MD1             |

### REGISTER 30-1: MD1CON0: MODULATION CONTROL REGISTER 0

| R/W-0/0 | U-0 | R-0/0 | R/W-0/0 | U-0 | U-0 | U-0 | R/W-0/0 |

|---------|-----|-------|---------|-----|-----|-----|---------|

| EN      | —   | OUT   | OPOL    | —   | —   | —   | BIT     |

| bit 7   |     |       |         |     |     |     | bit 0   |

| Legend:              |                      |                                                       |

|----------------------|----------------------|-------------------------------------------------------|

| R = Readable bit     | W = Writable bit     | U = Unimplemented bit, read as '0'                    |

| u = Bit is unchanged | x = Bit is unknown   | -n/n = Value at POR and BOR/Value at all other Resets |

| '1' = Bit is set     | '0' = Bit is cleared |                                                       |

| bit 7   | EN: Modulator Module Enable bit                                                                                                                                                             |

|---------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|         | 1 = Modulator module is enabled and mixing input signals                                                                                                                                    |

|         | 0 = Modulator module is disabled and has no output                                                                                                                                          |

| bit 6   | Unimplemented: Read as '0'                                                                                                                                                                  |

| bit 5   | OUT: Modulator Output bit                                                                                                                                                                   |

|         | Displays the current output value of the Modulator module. <sup>(1)</sup>                                                                                                                   |

| bit 4   | OPOL: Modulator Output Polarity Select bit                                                                                                                                                  |

|         | 1 = Modulator output signal is inverted; idle high output                                                                                                                                   |

|         | 0 = Modulator output signal is not inverted; idle low output                                                                                                                                |

| bit 3-1 | Unimplemented: Read as '0'                                                                                                                                                                  |

| bit 0   | BIT: Allows software to manually set modulation source input to module <sup>(2)</sup>                                                                                                       |

|         | 1 = Modulator selects Carrier High                                                                                                                                                          |

|         | 0 = Modulator selects Carrier Low                                                                                                                                                           |

| Note 1: | The modulated output frequency can be greater and asynchronous from the clock that updates this register bit, the bit value may not be valid for higher speed modulator or carrier signals. |

2: BIT bit must be selected as the modulation source in the MD1SRC register for this operation.

The SPI transmit output (SDO\_out) is available to the remappable PPS SDO pin and internally to the following peripherals:

- Configurable Logic Cell (CLC)

- Data Signal Modulator (DSM)

The SPI bus typically operates with a single master device and one or more slave devices. When multiple slave devices are used, an independent Slave Select connection is required from the master device to each slave device.

The master selects only one slave at a time. Most slave devices have tri-state outputs so their output signal appears disconnected from the bus when they are not selected.

Transmissions typically involve shift registers, eight bits in size, one in the master and one in the slave. With either the master or the slave device, data is always shifted out one bit at a time, with the Most Significant bit (MSb) shifted out first. At the same time, a new bit is shifted into the device. Unlike older Microchip devices, the SPI on the PIC18(L)F2X/4X/5XK42 contains two separate registers for incoming and outgoing data. Both registers also have 2-byte FIFO buffers and allow for DMA bus connections.

Figure 32-2 shows a typical connection between two PIC18F2X/4X/5XK42 devices configured as master and slave devices.

Data is shifted out of the transmit FIFO on the programmed clock edge and into the receive shift register on the opposite edge of the clock.

The master device transmits information on its SDO output pin which is connected to, and received by, the slave's SDI input pin. The slave device transmits information on its SDO output pin, which is connected to, and received by, the master's SDI input pin.

The master device sends out the clock signal. Both the master and the slave devices should be configured for the same clock polarity.

During each SPI clock cycle, a full-duplex data transmission occurs. This means that while the master device is sending out the MSb from its output register (on its SDO pin) and the slave device is reading this bit and saving as the LSb of its input register, that the slave device is also sending out the MSb from its shift register (on its SDO pin) and the master device is reading this bit and saving it as the LSb of its input register.

After eight bits have been shifted out, the master and slave have exchanged register values and stored the incoming data into the receiver FIFOs.

If there is more data to exchange, the registers are loaded with new data and the process repeats itself.

Whether the data is meaningful or not (dummy data) depends on the application software. This leads to three scenarios for data transmission:

· Master sends useful data and slave sends dummy

data

- Master sends useful data and slave sends useful data

- Master sends dummy data and slave sends useful data

In this particular SPI module, dummy data may be sent without software involvement, by clearing either the RXR bit (for receiving dummy data) or the TXR bit (for sending dummy data) (see Table 32-1 as well as Section 32.5 "Master mode" and Section 32.6 "Slave Mode" for further TXR/RXR setting details). This SPI module can send transmissions of any number of bits, and can send information in segments of varying size (from 1-8 bits in width). As such, transmissions may involve any number of clock cycles, depending on the amount of data to be transmitted.

When there is no more data to be transmitted, the master stops sending the clock signal and deselects the slave.

Every slave device connected to the bus that has not been selected through its slave select line disregards the clock and transmission signals and does not transmit out any data of its own.

### 32.7 SPI Operation in Sleep Mode

SPI master mode will operate in Sleep, provided the clock source selected by SPIxCLK is active in Sleep mode. FIFOs will operate as they would when the part is awake. When TXR = 1, the TXFIFO will need to contain data in order for transfers to take place in Sleep. All interrupts will still set the interrupt flags in Sleep but only enabled interrupts will wake the device from Sleep.

SPI Slave mode will operate in Sleep, because the clock is provided by an external master device. FIFOs will still operate and interrupts will set interrupt flags, and enabled interrupts will wake the device from Sleep.

### 32.8 SPI Interrupts

There are three top level SPI interrupts in the PIRx register:

- SPI Transmit

- SPI Receive

- · SPI Module status

The status interrupts are enabled at the module level in the SPIxINTE register. Only enabled status interrupts will cause the single top level SPIxIF flag to be set.

### 32.8.1 SPI RECEIVER DATA INTERRUPT

The SPI Receiver Data Interrupt is set when RXFIFO contains data, and is cleared when the RXFIFO is empty. The interrupt flag SPI1RXIF is located in PIRx and the interrupt enable SPI1RXIE is located in PIEx. This interrupt flag is read-only.

### 32.8.2 SPI TRANSMITTER DATA INTERRUPT

The SPI Transmitter Data Interrupt is set when TXFIFO is not full, and is cleared when the TXFIFO is full. The interrupt flag SPI1TXIF is located in PIRx and the interrupt enable SPI1TXIE is located in PIEx. The interrupt flag is read-only.

### 32.8.3 SPI MODULE STATUS INTERRUPTS

The SPIxIF flag in the respective PIR register is set when any of the individual status flags in SPIxINTF and their respective SPIxINTE bits are set. In order for the setting of any specific interrupt flag to interrupt normal program flow both the SPIxIE bit as well as the specific bit in SPIxINTE associated with that interrupt must be set.

The Status Interrupts are:

- Shift Register Empty Interrupt

- Transfer Counter is Zero Interrupt

- · Start of Slave Select Interrupt

- · End of Slave Select Interrupt

- · Receiver Overflow Interrupt

- Transmitter Underflow Interrupt

# PIC18(L)F26/27/45/46/47/55/56/57K42

| CPF              | SLT                                           | Compare                                                                                                                                                                    | Compare f with W, skip if f < W                                                                                                                                                                                                                                                                                                                                                                                   |           |  |  |  |  |