Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

E·XFI

| Product Status             | Active                                                                     |

|----------------------------|----------------------------------------------------------------------------|

| Core Processor             | PIC                                                                        |

| Core Size                  | 8-Bit                                                                      |

| Speed                      | 64MHz                                                                      |

| Connectivity               | I <sup>2</sup> C, LINbus, SPI, UART/USART                                  |

| Peripherals                | Brown-out Detect/Reset, LVD, POR, PWM, WDT                                 |

| Number of I/O              | 44                                                                         |

| Program Memory Size        | 32KB (16K x 16)                                                            |

| Program Memory Type        | FLASH                                                                      |

| EEPROM Size                | 256 x 8                                                                    |

| RAM Size                   | 2K x 8                                                                     |

| Voltage - Supply (Vcc/Vdd) | 2.3V ~ 5.5V                                                                |

| Data Converters            | A/D 43x12b; D/A 1x5b                                                       |

| Oscillator Type            | Internal                                                                   |

| Operating Temperature      | -40°C ~ 125°C (TA)                                                         |

| Mounting Type              | Surface Mount                                                              |

| Package / Case             | 48-UFQFN Exposed Pad                                                       |

| Supplier Device Package    | 48-UQFN (6x6)                                                              |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/pic18f55k42-e-mv |

|                            |                                                                            |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

| Ο                       |

|-------------------------|

| $\sim$                  |

| Ξ                       |

| 3                       |

|                         |

| .)                      |

|                         |

| N                       |

| 6                       |

| $\overline{\mathbf{N}}$ |

|                         |

|                         |

| 4                       |

| S                       |

| 4                       |

| 9                       |

| Ň                       |

| 4                       |

|                         |

| 5                       |

| 5                       |

| N N                     |

| 5                       |

| 6                       |

|                         |

| N                       |

| F                       |

|                         |

| 4                       |

| N                       |

\_

| 0/I  | 40-Pin PDIP | 44-Pin TQFP | 40-Pin UQFN | 44-Pin QFN | ADC                           | Voltage Reference | DAC              | Comparators      | Zero Cross Detect | I <sup>2</sup> C      | SPI                | UART                | WSQ                   | Timers/SMT                                                                                   | CCP and PWM         | CWG                   | СГС                   | NCO | Clock Reference (CLKR) | Interrupt-on-Change          | Basic          |

|------|-------------|-------------|-------------|------------|-------------------------------|-------------------|------------------|------------------|-------------------|-----------------------|--------------------|---------------------|-----------------------|----------------------------------------------------------------------------------------------|---------------------|-----------------------|-----------------------|-----|------------------------|------------------------------|----------------|

| RA0  | 2           | 19          | 17          | 19         | ANA0                          |                   | —                | C1IN0-<br>C2IN0- |                   | _                     | _                  | _                   | —                     | —                                                                                            |                     | -                     | CLCIN0 <sup>(1)</sup> | -   | _                      | IOCA0                        | _              |

| RA1  | 3           | 20          | 18          | 20         | ANA1                          | —                 | —                | C1IN1-<br>C2IN1- | —                 | —                     | —                  | —                   | _                     | —                                                                                            | -                   | —                     | CLCIN1 <sup>(1)</sup> | -   | —                      | IOCA1                        | —              |

| RA2  | 4           | 21          | 19          | 21         | ANA2                          | VREF-             | DAC1OUT1         | C1IN0+<br>C2IN0+ |                   | -                     | -                  | -                   | —                     | —                                                                                            | -                   | -                     | -                     | -   | -                      | IOCA2                        | —              |

| RA3  | 5           | 22          | 20          | 22         | ANA3                          | VREF+             | _                | C1IN1+           | _                 | _                     | _                  | _                   | MDCARL <sup>(1)</sup> | _                                                                                            |                     | _                     | _                     |     | _                      | IOCA3                        | _              |

| RA4  | 6           | 23          | 21          | 23         | ANA4                          | _                 | _                | _                | _                 | _                     | _                  | _                   | MDCARH <sup>(1)</sup> | T0CKI <sup>(1)</sup>                                                                         | -                   | _                     | _                     | _   | _                      | IOCA4                        | _              |

| RA5  | 7           | 24          | 22          | 24         | ANA5                          | -                 | _                | _                | _                 | _                     | SS1 <sup>(1)</sup> | _                   | MDSRC <sup>(1)</sup>  | _                                                                                            | _                   | _                     | _                     | _   | _                      | IOCA5                        | —              |

| RA6  | 14          | 31          | 29          | 33         | ANA6                          | _                 | —                | —                | —                 | —                     | —                  | —                   | —                     | —                                                                                            | -                   | —                     | —                     | —   | —                      | IOCA6                        | OSC2<br>CLKOUT |

| RA7  | 13          | 30          | 28          | 32         | ANA7                          | _                 | —                | —                | _                 | —                     | —                  | —                   | —                     | —                                                                                            | -                   | —                     | —                     | —   | —                      | IOCA7                        | OSC1<br>CLKIN  |

| RB0  | 33          | 8           | 8           | 9          | ANB0                          | -                 | —                | C2IN1+           | ZCD               | —                     | —                  | —                   | —                     | —                                                                                            | CCP4 <sup>(1)</sup> | CWG1IN <sup>(1)</sup> | -                     | -   | —                      | INT0 <sup>(1)</sup><br>IOCB0 | —              |

| RB1  | 34          | 9           | 9           | 10         | ANB1                          |                   | —                | C1IN3-<br>C2IN3- | —                 | SCL2 <sup>(3,4)</sup> | —                  | —                   | —                     | —                                                                                            | _                   | CWG2IN <sup>(1)</sup> | -                     | —   | —                      | INT1 <sup>(1)</sup><br>IOCB1 | —              |

| RB2  | 35          | 10          | 10          | 11         | ANB2                          | -                 | —                | —                | —                 | SDA2 <sup>(3,4)</sup> | —                  | —                   | -                     | —                                                                                            | -                   | CWG3IN <sup>(1)</sup> | -                     | -   | —                      | INT2 <sup>(1)</sup><br>IOCB2 | —              |

| RB3  | 36          | 11          | 11          | 12         | ANB3                          | _                 | —                | C1IN2-<br>C2IN2- | —                 | -                     | -                  | -                   | -                     | —                                                                                            | _                   | -                     | -                     | _   | -                      | IOCB3                        | —              |

| RB4  | 37          | 14          | 12          | 14         | ANB4<br>ADCACT <sup>(1)</sup> | _                 | —                | —                | —                 | -                     | -                  | -                   | —                     | T5G <sup>(1)</sup>                                                                           | _                   | -                     | -                     | -   | -                      | IOCB4                        | -              |

| RB5  | 38          | 15          | 13          | 15         | ANB5                          | -                 | _                | _                | _                 | -                     | _                  | _                   | _                     | T1G <sup>(1)</sup>                                                                           | CCP3 <sup>(1)</sup> | _                     | -                     | _   | _                      | IOCB5                        | _              |

| RB6  | 39          | 16          | 14          | 16         | ANB6                          | _                 | _                | —                | _                 | _                     | _                  | CTS2 <sup>(1)</sup> | _                     | -                                                                                            | _                   | _                     | CLCIN2 <sup>(1)</sup> | _   | —                      | IOCB6                        | ICSPCLK        |

| RB7  | 40          | 17          | 15          | 17         | ANB7                          | _                 | DAC1OUT2         | _                | _                 | _                     | _                  | RX2 <sup>(1)</sup>  | _                     | T6IN <sup>(1)</sup>                                                                          | _                   | _                     | CLCIN3 <sup>(1)</sup> |     | _                      | IOCB7                        | ICSPDAT        |

| RC0  | 15          | 32          | 30          | 34         | ANC0                          |                   | _                | —                | —                 | -                     | —                  | —                   | —                     | T1CKI <sup>(1)</sup><br>T3CKI <sup>(1)</sup><br>T3G <sup>(1)</sup><br>SMTWIN1 <sup>(1)</sup> | _                   | —                     | _                     | _   | —                      | IOCC0                        | SOSCO          |

| RC1  | 16          | 35          | 31          | 35         | ANC1                          |                   | —                | _                | _                 | _                     | _                  | _                   | —                     | SMTSIG1 <sup>(1)</sup>                                                                       | CCP2 <sup>(1)</sup> | _                     | _                     | _   | _                      | IOCC1                        | SOSCI          |

| RC2  | 17          | 36          | 32          | 36         | ANC2                          | —                 | -                | —                | _                 | _                     | _                  | —                   | _                     | T5CKI <sup>(1)</sup>                                                                         | CCP1 <sup>(1)</sup> | _                     | —                     |     | —                      | IOCC2                        | —              |

| Note | 1:          | This        | is a F      | PS re      | mappable inpu                 | t signal. Th      | e input function | may be me        | oved fro          | om the default        | location sh        | own to one          | of several othe       | er PORTx pins.                                                                               |                     |                       |                       |     |                        |                              |                |

2:

40/44-PIN ALLOCATION TABLE FOR PIC18(L)F4XK42

All output signals shown in this row are PPS remappable. This is a bidirectional signal. For normal module operation, the firmware should map this signal to the same pin in both the PPS input and PPS output registers. 3:

These pins can be configured for I<sup>2</sup>C and SMB<sup>TM</sup> 3.0/2.0 logic levels; The SCLx/SDAx signals may be assigned to any of the RB1/RB2/RC3/RC4/RD0/RD1 pins. PPS assignments to the other pins (e.g., RA5) will operate, but input logic levels will be standard TTL/ST as selected by the INLVL register, instead of the I<sup>2</sup>C specific or SMBus input buffer thresholds. 4:

TABLE 2:

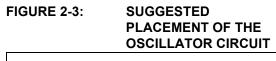

## 2.5 External Oscillator Pins

Many microcontrollers have options for at least two oscillators: a high-frequency primary oscillator and a low-frequency secondary oscillator (refer to Section 7.0 "Oscillator Module (with Fail-Safe Clock Monitor)" for details).

The oscillator circuit should be placed on the same side of the board as the device. Place the oscillator circuit close to the respective oscillator pins with no more than 0.5 inch (12 mm) between the circuit components and the pins. The load capacitors should be placed next to the oscillator itself, on the same side of the board.

Use a grounded copper pour around the oscillator circuit to isolate it from surrounding circuits. The grounded copper pour should be routed directly to the MCU ground. Do not run any signal traces or power traces inside the ground pour. Also, if using a two-sided board, avoid any traces on the other side of the board where the crystal is placed.

Layout suggestions are shown in Figure 2-3. In-line packages may be handled with a single-sided layout that completely encompasses the oscillator pins. With fine-pitch packages, it is not always possible to completely surround the pins and components. A suitable solution is to tie the broken guard sections to a mirrored ground layer. In all cases, the guard trace(s) must be returned to ground.

In planning the application's routing and I/O assignments, ensure that adjacent port pins, and other signals in close proximity to the oscillator, are benign (i.e., free of high frequencies, short rise and fall times, and other similar noise).

For additional information and design guidance on oscillator circuits, refer to these Microchip application notes, available at the corporate website (www.microchip.com):

- AN826, "Crystal Oscillator Basics and Crystal Selection for rfPIC<sup>™</sup> and PICmicro<sup>®</sup> Devices"

- AN849, "Basic PICmicro<sup>®</sup> Oscillator Design"

- AN943, "Practical PICmicro<sup>®</sup> Oscillator Analysis and Design"

- AN949, "Making Your Oscillator Work"

# 2.6 Unused I/Os

Unused I/O pins should be configured as outputs and driven to a logic low state. Alternatively, connect a 1 k $\Omega$  to 10 k $\Omega$  resistor to Vss on unused pins and drive the output to logic low.

| U-1              | U-1         | U-1              | U-1 | U-1                                | U-1   | U-1             | R/W-1 |  |  |  |  |

|------------------|-------------|------------------|-----|------------------------------------|-------|-----------------|-------|--|--|--|--|

| _                | _           | -                | -   | _                                  | —     | _               | CP    |  |  |  |  |

| bit 7 bit 0      |             |                  |     |                                    |       |                 |       |  |  |  |  |

|                  |             |                  |     |                                    |       |                 |       |  |  |  |  |

| Legend:          |             |                  |     |                                    |       |                 |       |  |  |  |  |

| R = Readable b   | bit         | W = Writable     | bit | U = Unimplemented bit, read as '1' |       |                 |       |  |  |  |  |

| -n = Value for b | lank device | '1' = Bit is set |     | '0' = Bit is cle                   | eared | x = Bit is unkr | nown  |  |  |  |  |

#### REGISTER 5-9: CONFIGURATION WORD 5L (30 0008h)

#### bit 7-1 Unimplemented: Read as '1'

bit 0

CP: User Program Flash Memory and Data EEPROM Code Protection bit

1 = User Program Flash Memory and Data EEPROM code protection is disabled

0 = User Program Flash Memory and Data EEPROM code protection is enabled

#### REGISTER 5-10: CONFIGURATION WORD 5H (30 0009h)

| U-1   | U-1 | U-1 | U-1 | U-1 | U-1 | U-1 | U-1   |

|-------|-----|-----|-----|-----|-----|-----|-------|

|       | _   | _   | _   | _   | _   | _   |       |

| bit 7 | I   |     |     |     |     |     | bit 0 |

| Sit 7 |     |     |     |     |     |     | b     |

| Legend:                     |                  |                            |                    |

|-----------------------------|------------------|----------------------------|--------------------|

| R = Readable bit            | W = Writable bit | U = Unimplemented bit, rea | id as '1'          |

| -n = Value for blank device | '1' = Bit is set | '0' = Bit is cleared       | x = Bit is unknown |

bit 7-0 Unimplemented: Read as '1'

#### TABLE 5-2:SUMMARY OF CONFIGURATION WORDS

| Address  | Name     | Bit 7  | Bit 6  | Bit 5      | Bit 4      | Bit 3   | Bit 2         | Bit 1      | Bit 0     | Default/<br>Unprogrammed<br>Value |

|----------|----------|--------|--------|------------|------------|---------|---------------|------------|-----------|-----------------------------------|

| 30 0000h | CONFIG1L | _      | I      | RSTOSC<2:0 | >          | —       |               | FEXTOSC<2  | 1111 1111 |                                   |

| 30 0001h | CONFIG1H | -      | _      | FCMEN      | _          | CSWEN   | _             | PR1WAY     | CLKOUTEN  | 1111 1111                         |

| 30 0002h | CONFIG2L | BOREI  | N<1:0> | LPBOREN    | IVT1WAY    | MVECEN  | PWRT          | PWRTS<1:0> |           | 1111 1111                         |

| 30 0003h | CONFIG2H | XINST  | _      | DEBUG      | STVREN     | PPS1WAY | ZCD BORV<1:0> |            |           | 1111 1111                         |

| 30 0004h | CONFIG3L | _      | WDT    | E<1:0>     |            |         | WDTCPS        | <4:0>      |           | 1111 1111                         |

| 30 0005h | CONFIG3H | _      | _      | v          | VDTCCS<2:0 | >       |               | WDTCWS<2   | :0>       | 1111 1111                         |

| 30 0006h | CONFIG4L | WRTAPP | _      | _          | SAFEN      | BBEN    |               | BBSIZE<2:0 | )>        | 1111 1111                         |

| 30 0007h | CONFIG4H | _      |        | LVP        | _          | WRTSAF  | WRTD WRTC     |            | WRTB      | 1111 1111                         |

| 30 0008h | CONFIG5L | —      | _      | —          | _          | —       | _             | —          | CP        | 1111 1111                         |

| 30 0009h | CONFIG5H | _      | —      | —          | _          | —       | _             | _          | _         | 1111 1111                         |

© 2017 Microchip Technology Inc.

### 7.5 Register Definitions: Oscillator Control

#### REGISTER 7-1: OSCCON1: OSCILLATOR CONTROL REGISTER 1

| U-0   | R/W-f/f | R/W-f/f   | R/W-f/f | R/W-q/q   | R/W-q/q | R/W-q/q | R/W-q/q |  |

|-------|---------|-----------|---------|-----------|---------|---------|---------|--|

| —     |         | NOSC<2:0> |         | NDIV<3:0> |         |         |         |  |

| bit 7 |         |           |         |           |         |         | bit 0   |  |

| Legend:              |                      |                                                       |

|----------------------|----------------------|-------------------------------------------------------|

| R = Readable bit     | W = Writable bit     | U = Unimplemented bit, read as '0'                    |

| u = Bit is unchanged | x = Bit is unknown   | -n/n = Value at POR and BOR/Value at all other Resets |

| '1' = Bit is set     | '0' = Bit is cleared | f = determined by Configuration bit setting           |

|                      |                      | q = Reset value is determined by hardware             |

| bit 7 | Unimplemented: Read as '0' |

|-------|----------------------------|

|-------|----------------------------|

- 2: If NOSC is written with a reserved value (Table 7-1), the operation is ignored and neither NOSC nor NDIV is written.

- **3:** When CSWEN = 0, this register is read-only and cannot be changed from the POR value.

| RSTOSC | SF        | R Reset Value |          |                               |  |  |  |

|--------|-----------|---------------|----------|-------------------------------|--|--|--|

| K3103C | NOSC/COSC | CDIV          | OSCFRQ   | Initial Fosc Frequency        |  |  |  |

| 111    | 111       | 1:1           |          | EXTOSC per FEXTOSC            |  |  |  |

| 110    | 110       | 4:1           |          | Fosc = 1 MHz (4 MHz/4)        |  |  |  |

| 101    | 101       | 1:1           | 4 MHz    | LFINTOSC                      |  |  |  |

| 100    | 100       | 1:1           |          | SOSC                          |  |  |  |

| 011    |           |               | Reserved | d                             |  |  |  |

| 010    | 010       | 1:1 4 MHz     |          | EXTOSC + 4xPLL <sup>(1)</sup> |  |  |  |

| 001    |           |               | Reserved | 1                             |  |  |  |

| 000    | 110       | 1:1           | 64 MHz   | Fosc = 64 MHz                 |  |  |  |

#### TABLE 7-2: DEFAULT OSCILLATOR SETTINGS

**Note 1:** EXTOSC must meet the PLL specifications (Table 44-11).

bit 6-4NOSC<2:0>: New Oscillator Source Request bitsThe setting requests a source oscillator and PLL combination per Table 7-1.<br/>POR value = RSTOSC (Register 5-1).bit 3-0NDIV<3:0>: New Divider Selection Request bits

The setting determines the new postscaler division ratio per Table 7-1.

Note 1: The default value (f/f) is determined by the RSTOSC Configuration bits. See Table 7-2 below.

| R-0/0                  | R-0/0                               | R-0/0                              | R-0/0                   | R/W/HS-0/0        | R/W/HS-0/0        | R/W/HS-0/0                                  | R/W/HS-0/0     |

|------------------------|-------------------------------------|------------------------------------|-------------------------|-------------------|-------------------|---------------------------------------------|----------------|

| I2C1RXIF <sup>(2</sup> | <sup>2)</sup> SPI1IF <sup>(3)</sup> | SPI1TXIF <sup>(4)</sup>            | SPI1RXIF <sup>(4)</sup> | DMA1AIF           | DMA10RIF          | DMA1DCNTIF                                  | DMA1SCNTIF     |

| bit 7                  |                                     |                                    |                         |                   |                   |                                             | bit (          |

|                        |                                     |                                    |                         |                   |                   |                                             |                |

| Legend:                |                                     |                                    |                         |                   |                   |                                             |                |

| R = Reada              |                                     | W = Writable                       |                         | •                 | ented bit, read   |                                             |                |

| u = Bit is u           | -                                   | x = Bit is unk                     |                         |                   |                   | Value at all othe                           | er Resets      |

| '1' = Bit is s         | set                                 | '0' = Bit is cle                   | ared                    | HS = Hardwar      | e set             |                                             |                |

| bit 7                  | I2C1RXIF:                           | <sup>2</sup> C1 Receive Ir         | nterrupt Flag b         | it(2)             |                   |                                             |                |

|                        |                                     | ot has occurred                    |                         |                   |                   |                                             |                |

|                        | 0 = Interrup                        | ot event has no                    | t occurred              |                   |                   |                                             |                |

| bit 6                  |                                     | 1 Interrupt Flag                   | -                       |                   |                   |                                             |                |

|                        |                                     | ot has occurred                    |                         |                   |                   |                                             |                |

|                        | -                                   | ot event has no                    |                         |                   |                   |                                             |                |

| bit 5                  |                                     | SPI1 Transmit I                    |                         | DIL               |                   |                                             |                |

|                        |                                     | ot has occurred<br>ot event has no |                         |                   |                   |                                             |                |

| bit 4                  | •                                   | SPI1 Receive I                     |                         | oit(4)            |                   |                                             |                |

|                        |                                     | ot has occurred                    | 1 0                     |                   |                   |                                             |                |

|                        |                                     | ot event has no                    |                         |                   |                   |                                             |                |

| bit 3                  | DMA1AIF: [                          | DMA1 Abort In                      | terrupt Flag bit        | t                 |                   |                                             |                |

|                        | 1 = Interrup                        | ot has occurred                    | (must be clea           | red by software   | e)                |                                             |                |

|                        | •                                   | ot event has no                    |                         |                   |                   |                                             |                |

| bit 2                  |                                     | : DMA1 Overru                      | •                       | •                 |                   |                                             |                |

|                        | -                                   |                                    | -                       | red by software   | e)                |                                             |                |

| bit 1                  |                                     | ot event has no                    |                         | t Interrupt Flag  | hit               |                                             |                |

|                        |                                     |                                    |                         | red by software   |                   |                                             |                |

|                        |                                     | ot event has no                    |                         | incu by software  | -)                |                                             |                |

| bit 0                  | •                                   | <b>FIF:</b> DMA1 Sou               |                         | errupt Flag bit   |                   |                                             |                |

|                        |                                     |                                    |                         | red by software   | e)                |                                             |                |

|                        | 0 = Interrup                        | ot event has no                    | toccurred               | -                 |                   |                                             |                |

|                        |                                     | e global enable                    |                         |                   |                   | the state of its co<br>priate interrupt fla |                |

| 2:                     | -                                   | 2CxRXIF are r                      | ead-only bits.          | To clear the inte | errupt condition  | , the CLRBF bit i                           | n I2CxSTAT1    |

| 3:                     | SPIxIF is a rea                     | d-only bit. To c                   | lear the interru        | pt condition, al  | l bits in the SPI | kINTF register m                            | ust be cleared |

|                        |                                     |                                    |                         |                   |                   |                                             |                |

# REGISTER 9-5: PIR2: PERIPHERAL INTERRUPT REGISTER 2<sup>(1)</sup>

4: SPIxTXIF and SPIxRXIF are read-only bits and cannot be set/cleared by the software.

| R/W-0/0          | R/W-0/0                                           | R/W-0/0           | U-0            | R/W-0/0        | R/W-0/0          | R/W-0/0          | R/W-0/0     |

|------------------|---------------------------------------------------|-------------------|----------------|----------------|------------------|------------------|-------------|

| CLC1IE           | CWG1IE                                            | NCO1IE            | _              | CCP1IE         | TMR2IE           | TMR1GIE          | TMR1IE      |

| bit 7            |                                                   |                   |                |                |                  |                  | bit         |

|                  |                                                   |                   |                |                |                  |                  |             |

| Legend:          |                                                   |                   |                |                |                  |                  |             |

| R = Readable     |                                                   | W = Writable      |                | •              | nented bit, read |                  |             |

| u = Bit is unch  | •                                                 | x = Bit is unkr   |                | -n/n = Value a | at POR and BC    | R/Value at all o | ther Resets |

| '1' = Bit is set |                                                   | '0' = Bit is clea | ared           |                |                  |                  |             |

| bit 7            | CLC1IE: CI (                                      | C1 Interrupt Ena  | able bit       |                |                  |                  |             |

|                  | 1 = Enabled<br>0 = Disabled                       |                   |                |                |                  |                  |             |

| bit 6            | <b>CWG1IE:</b> CV<br>1 = Enabled<br>0 = Disabled  | VG1 Interrupt E   | nable bit      |                |                  |                  |             |

| bit 5            | NCO1IE: NC<br>1 = Enabled<br>0 = Disabled         | O1 Interrupt En   | able bit       |                |                  |                  |             |

| bit 4            | Unimplemen                                        | ted: Read as '    | )'             |                |                  |                  |             |

| bit 3            | <b>CCP1IE:</b> CCI<br>1 = Enabled<br>0 = Disabled | P1 Interrupt En   | able bit       |                |                  |                  |             |

| bit 2            | <b>TMR2IE:</b> TM<br>1 = Enabled<br>0 = Disabled  | R2 Interrupt En   | able bit       |                |                  |                  |             |

| bit 1            | <b>TMR1GIE:</b> TI<br>1 = Enabled<br>0 = Disabled | MR1 Gate Inter    | rupt Enable bi | t              |                  |                  |             |

| bit 0            | TMR1IE: TM<br>1 = Enabled<br>0 = Disabled         | R1 Interrupt En   | able bit       |                |                  |                  |             |

# REGISTER 9-18: PIE4: PERIPHERAL INTERRUPT ENABLE REGISTER 4

#### 13.3.8 ERASING THE DATA EEPROM MEMORY

Data EEPROM Memory can be erased by writing 0xFF to all locations in the Data EEPROM Memory that needs to be erased.

|      | CLRF   | NVMADRL     | ; Sta    | rt at address 0         |

|------|--------|-------------|----------|-------------------------|

|      | BCF    | NVMCON1, CF | GS ; Set | for memory              |

|      | BCF    | NVMCON1, EE |          | for Data EEPROM         |

|      | BCF    | INTCONO, GI | E ; Dis  | able interrupts         |

|      | BSF    | NVMCON1, WR | EN ; Ena | ble writes              |

| Loop |        |             | ; Loc    | p to refresh array      |

|      | BSF    | NVMCON1, RD | ; Rea    | d current address       |

|      | MOVLW  | 55h         | ;        |                         |

|      | MOVWF  | NVMCON2     | ; Wri    | te 55h                  |

|      | MOVLW  | 0AAh        | ;        |                         |

|      | MOVWF  | NVMCOM2     | ; Wri    | te OAAh                 |

|      | BSF    | NVMCON1, WR | ; Set    | WR bit to begin write   |

|      | BTFSC  | NVMCON1, WR | ; Wai    | t for write to complete |

|      | BRA    | \$-2        |          |                         |

|      | INCFSZ | NVMADRL, F  | ; Inc    | rement address          |

|      | BRA    | LOOP        | ; Not    | zero, do it again       |

|      | BCF    | NVMCON1, WR | EN ; Dis | able writes             |

|      | BSF    | INTCON0, GI | E ; Ena  | ble interrupts          |

#### 15.8.4 OVERRUN INTERRUPT

When the DMA receives a trigger to start a new message before the current message is completed, then the DMAxORIF Overrun interrupt flag is set.

This condition indicates that the DMA is being requested before its current transaction is finished. This implies that the active DMA may not be able to keep up with the demands from the peripheral module being serviced, which may result in data loss.

The DMAxORIF flag being set does not cause the current DMA transfer to terminate.

The Overrun interrupt is only available for trigger sources that are edge based and not available for sources that are level-based. Therefore a level-based interrupt source does not trigger a DMA overrun error due to the potential latency issues in the system.

An example of an interrupt that could use the overrun interrupt would be a timer overflow (or period match) interrupt. This event only happens every time the timer rolls over and is not dependent on any other system conditions.

An example of an interrupt that does not allow the overrun interrupt would be the UARTTX buffer. The UART will continue to assert the interrupt until the DMA is able to process the MSG. Due to latency issues, the DMA may not be able to service an empty buffer immediately, but the UART continues to assert its transmit interrupt until it is serviced. If overrun was allowed in this case, the overrun would occur almost immediately as the module samples the interrupt sources every instruction cycle.

#### 15.9 DMA Setup and Operation

The following steps illustrate how to configure the DMA for data transfer:

- 1. Program the appropriate Source and Destination addresses for the transaction into the DMAxSSA and DMAxDSA registers

- Select the source memory region that is being addressed by DMAxSSA register, using the SMR<1:0> bits.

- 3. Program the SMODE and DMODE bits to select the addressing mode.

- 4. Program the Source size DMAxSSZ and Destination size DMAxDSZ registers with the number of bytes to be transferred. It is recommended for proper operation that the size registers be a multiple of each other.

- If the user desires to disable data transfers once the message has completed, then the SSTP and DSTP bits in DMAxCON0 register need to be set. (see Section 15.5.3.2 "Source/Destination Stop").

- If using hardware triggers for data transfer, setup the hardware trigger interrupt sources for the starting and aborting DMA transfers (DMAxSIRQ and DMAxAIRQ), and set the corresponding interrupt request enable bits (SIRQEN and AIRQEN).

- Select the priority level for the DMA (see Section 3.1 "System Arbitration") and lock the priorities (see Section 3.1.1 "Priority Lock")

- 8. Enable the DMA (DMAxCON1bits. EN = 1)

- 9. If using software control for data transfer, set the DGO bit, else this bit will be set by the hardware trigger.

Once the DMA is set up, the following flow chart describes the sequence of operation when the DMA uses hardware triggers and utilizes the unused CPU cycles (bubble) for DMA transfers.

#### **FIGURE 21-2:** TIMER1/3/5 16-BIT READ/ WRITE MODE BLOCK DIAGRAM From Timer1 Circuitry Set TMR1IF TMR1 TMR1L High Byte on Overflow . 8 Read TMR1L Write TMR1L 8 .8 TMR1H 8 Internal Data Bus

#### Block Diagram of Timer1 Example of TIMER1/3/5

# 21.6 Timer1/3/5 Gate

Timer1/3/5 can be configured to count freely or the count can be enabled and disabled using Timer1/3/5 gate circuitry. This is also referred to as Timer1/3/5 gate enable.

Timer1/3/5 gate can also be driven by multiple selectable sources.

#### 21.6.1 TIMER1/3/5 GATE ENABLE

The Timer1/3/5 Gate Enable mode is enabled by setting the TMRxGE bit of the TxGCON register. The polarity of the Timer1/3/5 Gate Enable mode is configured using the TxGPOL bit of the TxGCON register.

When Timer1/3/5 Gate Enable mode is enabled, Timer1/3/5 will increment on the rising edge of the Timer1/3/5 clock source. When Timer1/3/5 Gate signal is inactive, the timer will not increment and hold the current count. See Figure 21-4 for timing details.

# TABLE 21-2: TIMER1/3/5 GATE ENABLE SELECTIONS

| TMRxCLK    | TxGPOL | TxG | Timer1/3/5<br>Operation |

|------------|--------|-----|-------------------------|

| $\uparrow$ | 1      | 1   | Counts                  |

| $\uparrow$ | 1      | 0   | Holds Count             |

| $\uparrow$ | 0      | 1   | Holds Count             |

| 1          | 0      | 0   | Counts                  |

# 27.1 CLCx Setup

Programming the CLCx module is performed by configuring the four stages in the logic signal flow. The four stages are:

- Data selection

- Data gating

- Logic function selection

- Output polarity

Each stage is setup at run time by writing to the corresponding CLCx Special Function Registers. This has the added advantage of permitting logic reconfiguration on-the-fly during program execution.

#### 27.1.1 DATA SELECTION

There are 32 signals available as inputs to the configurable logic. Four 32-input multiplexers are used to select the inputs to pass on to the next stage.

Data selection is through four multiplexers as indicated on the left side of Figure 27-2. Data inputs in the figure are identified by a generic numbered input name.

Table 27-1 correlates the generic input name to the actual signal for each CLC module. The column labeled 'DyS<4:0> Value' indicates the MUX selection code for the selected data input. DyS is an abbreviation for the MUX select input codes: D1S<4:0> through D4S<4:0>.

Data inputs are selected with CLCxSEL0 through CLCxSEL3 registers (Register 27-3 through Register 27-6).

**Note:** Data selections are undefined at power-up.

# 31.13 Checksum (UART1 only)

This section does not apply to the LIN mode, which handles checksums automatically.

The transmit and receive checksum adders are enabled when the C0EN bit in the UxCON2 register is set. When enabled, the adders accumulate every byte that is transmitted or received. The accumulated sum includes the carry of the addition. Software is responsible for clearing the checksum registers before a transaction and performing the check at the end of the transaction.

The following is an example of how the checksum registers could be used in the asynchronous modes.

#### 31.13.1 TRANSMIT CHECKSUM METHOD

- 1. Clear the UxTXCHK register.

- 2. Set the COEN bit.

- 3. Send all bytes of the transaction output.

- 4. Invert UxTXCHK and send the result as the last byte of the transaction.

#### 31.13.2 RECEIVE CHECKSUM METHOD

- 1. Clear the UxRXCHK register.

- 2. Set the COEN bit.

- 3. Receive all bytes in the transaction including the checksum byte.

- 4. Set MSb of UxRXCHK if 7-bit mode is selected.

- 5. Add 1 to UxRXCHK.

- 6. If the result is '0', the checksum passes, otherwise it fails.

The CERIF checksum interrupt flag is not active in any mode other than LIN.

# 31.14 Collision Detection

External forces that interfere with the transmit line are detected in all modes of operation with collision detection. Collision detection is always active when RXEN and TXEN are both set.

When the receive input is connected to the transmit output through either the same I/O pin or external circuitry, a character will be received for every character transmitted. The collision detection circuit provides a warning when the word received does not match the word transmitted. The TXCIF flag in the UxERRIR register is used to signal collisions. This signal is only useful when the TX output is looped back to the RX input and everything that is transmitted is expected to be received. If more than one transmitter is active at the same time, it can be assumed that the TX word will not match the RX word. The TXCIF detects this mismatch and flags an interrupt. The TXCIF bit will also be set in DALI mode transmissions when the received bit is missing the expected mid-bit transition.

Collision detection is always active, regardless of whether or not the RX input is connected to the TX output. It is up to the user to disable the TXCIE bit when collision interrupts are not required.

The software overhead of unloading the receive buffer of transmitted data is avoided by setting the RUNOVF bit in UxCON2 and ignoring the receive interrupt and letting the receive buffer overflow. When the transmission is complete, prepare for receiving data by flushing the receive buffer (see Section 31.11.2, FIFO Reset) and clearing the RXFOIF overflow flag in the UxERRIR register.

# 31.15 RX/TX Activity Timeout

The UART works in conjunction with the HLT timers to monitor activity on the RX and TX lines. Use this feature to determine when there has been no activity on the receive or transmit lines for a user specified period of time.

To use this feature, set the HLT to the desired timeout period by a combination of the HLT clock source, timer prescale value, and timer period registers. Configure the HLT to reset on the UART TX or RX line and start the HLT at the same time the UART is started. UART activity will keep resetting the HLT to prevent a full HLT period from elapsing. When there has been no activity on the selected TX or RX line for longer than the HLT period then an HLT interrupt will occur signaling the timeout event.

For example, the following register settings will configure HLT2 for a 5 ms timeout of no activity on U1RX:

- T2PR = 0x9C (156 prescale periods)

- T2CLKCON = 0x05 (500 kHz internal oscillator)

- T2HLT = 0x04 (free running, reset on rising edge)

- T2RST = 0x15 (reset on U1RX)

- T2CON = 0xC0 (Timer2 on with 1:16 prescale)

# 32.4 Transfer Counter

In all master modes, the transfer counter can be used to determine how many data transfers the SPI will send/receive. The transfer counter is comprised of the SPIxTCTH/L set of registers, and is also partially controlled by the SPIxTWIDTH register. The Transfer Counter has two primary modes, determined by the BMODE bit of the SPIxCON0 register. Each mode uses the SPIxTCTH/L and SPIxTWIDTH registers to determine the number and size of the transfers. In both modes, when the transfer counter reaches zero, the TCZIF interrupt flag is set.

- Note: When BMODE=1 in all master modes (and at all times in slave modes), the Transfer Counter will still decrement as transfers occur and can be used to count the number of messages sent/received, as well as to control SS(out) and to trigger TCZIF. Also when BMODE = 1, the SPIxTWIDTH register can be used in Master and Slave modes to determine the size of messages sent and received by the SPI, even if the Transfer Counter is not being actively used to control the number of messages being sent/received by the SPI module.

- 32.4.1 TOTAL BIT COUNT MODE (BMODE = 0)

In this mode, SPIxTCTH/L and SPIxTWIDTH are concatenated to determine the total number of bits to be transferred. These bits will be loaded from/into the transmit/receive FIFOs in 8-bit increments and the transfer counter will be decremented by eight until the total number of remaining bits is less than eight. If there are any remaining bits (SPIxTWIDTH  $\neq$  0), the transmit FIFO will send out one final message with any extra bits greater than the remainder ignored. The SPIxTWIDTH is the remaining bit count but the value does not change as it does for the SPIxTCT value. Similarly, the receiver will load a final byte into the receiver FIFO, and pad the extra bits with zeros. The LSBF bit of SPIxCON0 determines whether the Most Significant or Least Significant bits of this final byte are ignored/ padded. For example, when LSBF = 0 and the final transfer contains only two bits then if the last byte sent was 5Fh then the RXB of the receiver will contain 40h which are the two MSbits of the final byte padded with zeros in the LSbits.

In this mode, the SPI master will only transmit messages when the SPIxTCT value is greater than zero, regardless of TXR and RXR settings. In Master Transmit mode, the transfer starts with the data write to the SPIxTXB register or the count value written to the SPIxTCTL register, which ever occurs last. In Master Receive-only mode, the transfer clocks start when the SPIxTCTL value is written. Transfer clocks are suspended when the receive FIFO is full and resume as the FIFO is read.

#### 32.4.2 VARIABLE TRANSFER SIZE MODE (BMODE = 1)

In this mode, SPIxTWIDTH specifies the width of every individual piece of the data transfer in bits. SPIxTCTH/ SPIxTCTL specifies the number of transfers of this bit length. If SPIxTWIDTH = 0, each piece is a full byte of data. If SPIxTWIDTH  $\neq$  0, then only the specified number of bits from the transmit FIFO are shifted out, with the unused bits ignored. Received data is padded with zeros in the unused bit areas when transfered into the receive FIFO. The LSBF bit of SPIxCON0 determines whether the Most Significant or Least Significant bits of the transfers are ignored/padded. In this mode, the transfer counter being zero only stops messages from being sent/received when in "Receive only" mode.

Note: With BMODE = 1, it is possible for the transfer counter (SPIxTCTH/L) to decrement below zero, although when in "Receive only" Master mode, transfer clocks will cease when the transfer counter reaches zero.

| R/W-0           | R/W-0                           | U-0                                                                                    | R/W-0                         | R/W-0          | R/W-0       | R/W-0               | R/W-0       |

|-----------------|---------------------------------|----------------------------------------------------------------------------------------|-------------------------------|----------------|-------------|---------------------|-------------|

| CNTIE           | ACKTIE                          | —                                                                                      | WRIE                          | ADRIE          | PCIE        | RSCIE               | SCIE        |

| bit 7           | ·                               |                                                                                        | ·                             |                |             | · · ·               | bit         |

|                 |                                 |                                                                                        |                               |                |             |                     |             |

| Legend:         |                                 |                                                                                        |                               |                |             |                     |             |

| R = Readable    | bit                             | W = Writable                                                                           | bit                           | U = Unimplem   | nented bit, | read as '0'         |             |

| u = Bit is unch | anged                           | x = Bit is unk                                                                         | nown                          | -n/n = Value a | t POR and   | BOR/Value at all of | ther Resets |

| 1' = Bit is set |                                 | '0' = Bit is cle                                                                       | ared                          | HS = Hardwa    | re set H    | C = Hardware clear  |             |

| bit 7           | 1 = When Cl                     | Count Interrup<br>NTIF is set<br>int interrupts ar                                     |                               |                |             |                     |             |

| bit 6           | 1 = When A<br>If ACK<br>If NACK | knowledge Inte<br>CKTIF is set<br>is generated, C<br>K is generated,<br>edge holding a | STR is also s<br>CSTR is uncl | et.<br>nanged  |             |                     |             |

| bit 5           | Unimplemer                      | ted: Read as                                                                           | ·0'                           |                |             |                     |             |

| bit 4           | 1 = When W                      | Write Interrupt<br>RIF is set; CS <sup>-</sup><br>te holding and                       | TR is set                     |                |             |                     |             |

| bit 3           | 1 = When Al                     | ess Interrupt a<br>DRIF is set; CS<br>holding and in                                   | STR is set                    |                |             |                     |             |

| bit 2           | 1 = Enable i                    | condition Intern<br>nterrupt on det<br>ection interrupt                                | ection of Stop                |                |             |                     |             |

| bit 1           | 1 = Enable i                    | art Condition Ir<br>nterrupt on det<br>ection interrupt                                | ection of Rest                | art condition  |             |                     |             |

| bit 0           | 1 = Enable i                    | Condition Interrent<br>Interrupt on det<br>ection interrupt                            | ection of Start               |                |             |                     |             |

|                 |                                 |                                                                                        |                               |                |             |                     |             |

# REGISTER 33-11: I2CxPIE: I2CxIE INTERRUPT AND HOLD ENABLE REGISTER

#### 36.1.5 INTERRUPTS

The ADC module allows for the ability to generate an interrupt upon completion of an Analog-to-Digital conversion. The ADC Interrupt Flag is the ADIF bit in the PIRx register. The ADC Interrupt Enable is the ADIE bit in the PIEx register. The ADIF bit must be cleared in software.

- **Note 1:** The ADIF bit is set at the completion of every conversion, regardless of whether or not the ADC interrupt is enabled.

- **2:** The ADC operates during Sleep only when the FRC oscillator is selected.

This interrupt can be generated while the device is operating or while in Sleep. If the device is in Sleep, the interrupt will wake up the device. Upon waking from Sleep, the next instruction following the SLEEP instruction is always executed. If the user is attempting to wake up from Sleep and resume in-line code execution, the ADIE bit of the PIEx register and the GIE bits of the INTCON0 register must both be set. If all these bits are set, the execution will switch to the Interrupt Service Routine.

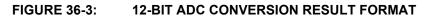

#### 36.1.6 RESULT FORMATTING

The 12-bit ADC conversion result can be supplied in two formats, left justified or right justified. The FM bits of the ADCON0 register controls the output format.

Figure 36-3 shows the two output formats.

Writes to the ADRES register pair are always right justified regardless of the selected format mode. Therefore, data read after writing to ADRES when ADFRM0 = 0 will be shifted left four places.

# 36.4 ADC Charge Pump

The ADC module has a dedicated charge pump which can be controlled through the ADCP register (Register 36-36). The primary purpose of the charge pump is to supply a constant voltage to the gates of transistor devices in the A/D converter, signal and reference input pass-gates, to prevent degradation of transistor performance at low operating voltage.

The charge pump can be enabled by setting the CPON bit in the ADC register. Once enabled, the pump will undergo a start-up time to stabilize the charge pump output. Once the output stabilizes and is ready for use, the CPRDY bit of the ADCP register will be set.

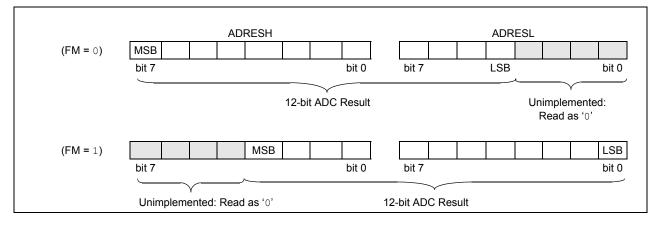

#### 36.5 Capacitive Voltage Divider (CVD) Features

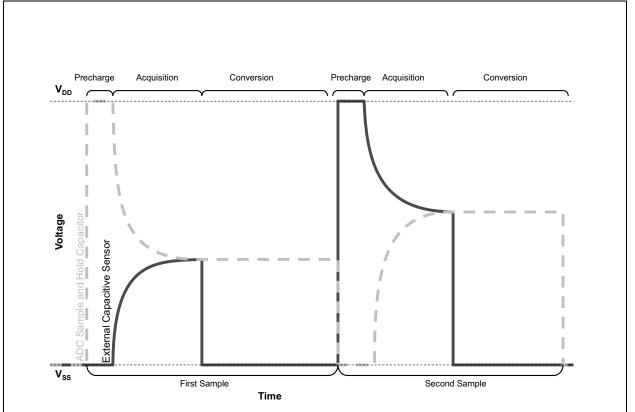

The ADC module contains several features that allow the user to perform a relative capacitance measurement on any ADC channel using the internal ADC sample and hold capacitance as a reference. This relative capacitance measurement can be used to implement capacitive touch or proximity sensing applications. Figure 36-6 shows the basic block diagram of the CVD portion of the ADC module.

#### 36.5.1 CVD OPERATION

A CVD operation begins with the ADC's internal and hold capacitor sample (C<sub>HOLD</sub>) being disconnected from the path which connects it to the external capacitive sensor node. While disconnected, C<sub>HOLD</sub> is precharged to VDD or Vss, while the path to the sensor node is precharged to the level opposite that of CHOLD. When the precharge phase is complete, the VDD/VSS precharge paths for the two nodes are shut off and CHOLD and the path to the external sensor node are re-connected, at which time the acquisition phase of the CVD operation begins. During acquisition, a capacitive voltage divider is formed between the precharged CHOLD and sensor nodes, which results in a final voltage level setting on CHOLD which is determined by the capacitances and precharge levels of the two nodes. After acquisition, the ADC converts the voltage level on CHOLD. This process is then repeated with inverted precharge levels for both the CHOLD and external sensor nodes. Figure 36-7 shows the waveform for two inverted CVD measurements, which is known as differential CVD measurement.

**REGISTER 36-8: ADPCH: ADC POSITIVE CHANNEL SELECTION REGISTER**

| U-0             | U-0                | R/W-0/0                     | R/W-0/0             | R/W-0/0         | R/W-0/0               | R/W-0/0            | R/W-0/0 |

|-----------------|--------------------|-----------------------------|---------------------|-----------------|-----------------------|--------------------|---------|

| _               | —                  |                             |                     | ADPC            | H<5:0>                |                    |         |

| it 7            |                    |                             |                     |                 |                       |                    | bit     |

|                 |                    |                             |                     |                 |                       |                    |         |

| .egend:         |                    |                             |                     |                 |                       |                    |         |

| R = Readable    | e bit              | W = Writable bit            | t                   | U = Unimpleme   | ented bit, read as    | s 'O'              |         |

| u = Bit is unc  | hanged             | x = Bit is unknow           | wn                  | -n/n = Value at | POR and BOR/          | /alue at all other | Resets  |

| '1' = Bit is se | t                  | '0' = Bit is cleare         | ed                  |                 |                       |                    |         |

|                 |                    |                             |                     |                 |                       |                    |         |

| bit 7-6         | Unimplement        | ed: Read as '0'             |                     |                 |                       |                    |         |

| bit 5-0         | ADPCH<5:0>:        | ADC Positive Inp            | out Channel Se      | lection bits    |                       |                    |         |

|                 | 111111 - 1         | FVR buffer 2 <sup>(2)</sup> |                     | 01011           | 1 = ANC7              |                    |         |

|                 |                    | =VR buffer 1 <sup>(2)</sup> |                     |                 | 1 = ANC7<br>0 = ANC6  |                    |         |

|                 |                    | DAC1 output <sup>(1)</sup>  |                     |                 | 1 = ANC5              |                    |         |

|                 |                    | Temperature indic           | ator <sup>(3)</sup> |                 | 00 = ANC4             |                    |         |

|                 |                    | √ss (Analog Grou            |                     | 01001           | 1 = ANC3              |                    |         |

|                 | 111010 <b>=  </b>  | Reserved. No cha            | nnel connecte       | <b>d.</b> 01001 | 0 = ANC2              |                    |         |

|                 | •                  |                             |                     |                 | 1 = ANC1              |                    |         |

|                 | •                  |                             |                     |                 | 0 = ANCO              |                    |         |

|                 | •                  |                             |                     | 0.0111          | 1 = ANB7<br>0 = ANB6  |                    |         |

|                 |                    | Reserved. No cha            | innel connecte      | u.              | 1 = ANB5              |                    |         |

|                 | 101111 = /         | ANF7 <sup>(4)</sup>         |                     |                 | 0 = ANB4              |                    |         |

|                 | 101110 = /         | ANF6 <sup>(4)</sup>         |                     | 00101           | 1 = ANB3              |                    |         |

|                 | 101101 = /         | ANF5 <sup>(4)</sup>         |                     |                 | 0 = ANB2              |                    |         |

|                 | 101100 = /         | ANF4 <sup>(4)</sup>         |                     |                 | 1 = ANB1              |                    |         |

|                 | 101011 = /         |                             |                     |                 | 00 = ANB0<br>1 = ANA7 |                    |         |

|                 |                    |                             |                     |                 | 0 = ANA6              |                    |         |

|                 | 101010 = /         |                             |                     |                 | 1 = ANA5              |                    |         |

|                 | 101001 = /         |                             |                     | 00010           | 00 <b>= ANA4</b>      |                    |         |

|                 | 101000 = /         | ANF0 <sup>(4)</sup>         |                     | 00001           | 1 = ANA3              |                    |         |

|                 | 100111 <b>=  </b>  | Reserved. No cha            | nnel connecte       | u.              | 0 = ANA2              |                    |         |

|                 | •                  |                             |                     |                 | 1 = ANA1              |                    |         |

|                 | •                  |                             |                     | 00000           | 00 <b>= ANA0</b>      |                    |         |

|                 | 100011 <b>=  </b>  | Reserved. No cha            | nnel connecte       | d.              |                       |                    |         |

|                 | 100010 = /         | ANE2 <sup>(5)</sup>         |                     |                 |                       |                    |         |

|                 | 100001 = /         | ANE1 <sup>(5)</sup>         |                     |                 |                       |                    |         |

|                 | 100000 = /         |                             |                     |                 |                       |                    |         |

|                 | 011111 =           |                             |                     |                 |                       |                    |         |

|                 |                    |                             |                     |                 |                       |                    |         |

|                 | 011110 =           |                             |                     |                 |                       |                    |         |

|                 | 011101 =           |                             |                     |                 |                       |                    |         |

|                 | 011100 = /         | 4ND4 <sup>(5)</sup>         |                     |                 |                       |                    |         |

|                 | 011011 =           | AND3 <sup>(5)</sup>         |                     |                 |                       |                    |         |

|                 | 011010 = /         |                             |                     |                 |                       |                    |         |

|                 | 011001 =           |                             |                     |                 |                       |                    |         |

|                 | 011000 = /         |                             |                     |                 |                       |                    |         |

| Note 1: S       | See Section 37.0 " | 5-Bit Digital-to-A          | nalog Conver        | ter (DAC) Modul | e" for more infor     | mation.            |         |

|                 | See Section 34.0 " |                             |                     |                 |                       |                    |         |

|                 | See Section 35.0 " |                             |                     |                 |                       |                    |         |

| <b>4</b> : F    | Reserved on PIC18  | (L)F26/27/45/46/4           | 7K42 parts.         |                 |                       |                    |         |

| 5. 5            | Peserved on PIC18  | (I)E26/27K42 par            | to                  |                 |                       |                    |         |

5: Reserved on PIC18(L)F26/27K42 parts.

#### **REGISTER 36-18:** ADRESH: ADC RESULT REGISTER HIGH, FM = 0

| R/W-x/u          | R/W-x/u | R/W-x/u             | R/W-x/u | R/W-x/u        | R/W-x/u          | R/W-x/u        | R/W-x/u      |

|------------------|---------|---------------------|---------|----------------|------------------|----------------|--------------|

|                  |         |                     | ADRE    | S<11:4>        |                  |                |              |

| bit 7            |         |                     |         |                |                  |                | bit 0        |

|                  |         |                     |         |                |                  |                |              |

| Legend:          |         |                     |         |                |                  |                |              |

| R = Readable I   | bit     | W = Writable bit    | :       | U = Unimpler   | nented bit, read | d as '0'       |              |

| u = Bit is uncha | anged   | x = Bit is unknow   | wn      | -n/n = Value a | at POR and BC    | R/Value at all | other Resets |

| '1' = Bit is set |         | '0' = Bit is cleare | ed      |                |                  |                |              |

bit 7-0 **ADRES<11:4>**: ADC Result Register bits Upper eight bits of 12-bit conversion result.

#### **REGISTER 36-19:** ADRESL: ADC RESULT REGISTER LOW, FM = 0

| R/W-x/u | R/W-x/u | R/W-x/u | R/W-x/u | U-0 | U-0 | U-0 | U-0   |

|---------|---------|---------|---------|-----|-----|-----|-------|

|         | ADRES   | 6<3:0>  |         | —   | —   | —   | —     |

| bit 7   |         |         |         |     |     |     | bit 0 |

| Legend:              |                      |                                                       |

|----------------------|----------------------|-------------------------------------------------------|

| R = Readable bit     | W = Writable bit     | U = Unimplemented bit, read as '0'                    |

| u = Bit is unchanged | x = Bit is unknown   | -n/n = Value at POR and BOR/Value at all other Resets |

| '1' = Bit is set     | '0' = Bit is cleared |                                                       |

bit 7-4 ADRES<3:0>: ADC Result Register bits. Lower four bits of 12-bit conversion result.

bit 3-0 Reserved

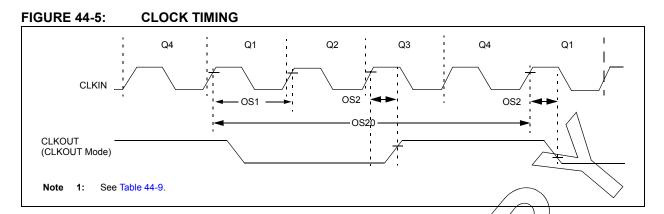

#### TABLE 44-9: EXTERNAL CLOCK/OSCILLATOR TIMING REQUIREMENTS

| Standard Operating Conditions (unless otherwise stated) |                                                                                                                                                                                                                                                                                                                                                         |                                                                                                                                                                                                                                                                                                                                                                                                         |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |  |  |  |

|---------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|