Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

#### Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

E·XF

| Details                    |                                                                             |

|----------------------------|-----------------------------------------------------------------------------|

| Product Status             | Active                                                                      |

| Core Processor             | PIC                                                                         |

| Core Size                  | 8-Bit                                                                       |

| Speed                      | 64MHz                                                                       |

| Connectivity               | I <sup>2</sup> C, LINbus, SPI, UART/USART                                   |

| Peripherals                | Brown-out Detect/Reset, LVD, POR, PWM, WDT                                  |

| Number of I/O              | 44                                                                          |

| Program Memory Size        | 64KB (32K x 16)                                                             |

| Program Memory Type        | FLASH                                                                       |

| EEPROM Size                | 1K x 8                                                                      |

| RAM Size                   | 4K x 8                                                                      |

| Voltage - Supply (Vcc/Vdd) | 2.3V ~ 5.5V                                                                 |

| Data Converters            | A/D 43x12b; D/A 1x5b                                                        |

| Oscillator Type            | Internal                                                                    |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                           |

| Mounting Type              | Surface Mount                                                               |

| Package / Case             | 48-TQFP Exposed Pad                                                         |

| Supplier Device Package    | 48-TQFP-EP (7x7)                                                            |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/pic18f56k42t-i-pt |

|                            |                                                                             |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

## 7.2.2.6 Oscillator Status and Manual Enable

The Ready status of each oscillator (including the ADCRC oscillator) is displayed in OSCSTAT (Register 7-4). The oscillators (but not the PLL) may be explicitly enabled through OSCEN (Register 7-7).

### 7.2.2.7 HFOR and MFOR Bits

The HFOR and MFOR bits indicate that the HFINTOSC and MFINTOSC is ready. These clocks are always valid for use at all times, but only accurate after they are ready.

When a new value is loaded into the OSCFRQ register, the HFOR and MFOR bits will clear, and set again when the oscillator is ready. During pending OSCFRQ changes the MFINTOSC clock will stall at a high or a low state, until the HFINTOSC resumes operation.

## 7.3 Clock Switching

The system clock source can be switched between external and internal clock sources via software using the New Oscillator Source (NOSC) bits of the OSCCON1 register. The following clock sources can be selected using the following:

- External oscillator

- Internal Oscillator Block (INTOSC)

| Note: | The Clock Switch Enable bit in          |

|-------|-----------------------------------------|

|       | Configuration Word 1 can be used to     |

|       | enable or disable the clock switching   |

|       | capability. When cleared, the NOSC and  |

|       | NDIV bits cannot be changed by user     |

|       | software. When set, writing to NOSC and |

|       | NDIV is allowed and would switch the    |

|       | clock frequency.                        |

### 7.3.1 NEW OSCILLATOR SOURCE (NOSC) AND NEW DIVIDER SELECTION REQUEST (NDIV) BITS

The New Oscillator Source (NOSC) and New Divider Selection Request (NDIV) bits of the OSCCON1 register select the system clock source and frequency that are used for the CPU and peripherals.

When new values of NOSC and NDIV are written to OSCCON1, the current oscillator selection will continue to operate while waiting for the new clock source to indicate that it is stable and ready. In some cases, the newly requested source may already be in use, and is ready immediately. In the case of a divider-only change, the new and old sources are the same, so the old source will be ready immediately. The device may enter Sleep while waiting for the switch as described in Section 7.3.2 "Clock Switch and Sleep".

When the new oscillator is ready, the New Oscillator Ready (NOSCR) bit of OSCCON3 and the Clock Switch Interrupt Flag (CSWIF) bit of the respective PIR register are set. If Clock Switch Interrupts are enabled (CSWIE = 1), an interrupt will be generated at that time. The Oscillator Ready (ORDY) bit of OSCCON3 can also be polled to determine when the oscillator is ready in lieu of an interrupt.

Note: The CSWIF interrupt will not wake the system from Sleep.

If the Clock Switch Hold (CSWHOLD) bit of OSCCON3 is clear, the oscillator switch will occur when the New Oscillator is Ready bit (NOSCR) is set, and the interrupt (if enabled) will be serviced at the new oscillator setting.

If CSWHOLD is set, the oscillator switch is suspended, while execution continues using the current (old) clock source. When the NOSCR bit is set, software should:

- Set CSWHOLD = 0 so the switch can complete, or

- Copy COSC into NOSC to abandon the switch.

If DOZE is in effect, the switch occurs on the next clock cycle, whether or not the CPU is operating during that cycle.

Changing the clock post-divider without changing the clock source (i.e., changing Fosc from 1 MHz to 2 MHz) is handled in the same manner as a clock source change, as described previously. The clock source will already be active, so the switch is relatively quick. CSWHOLD must be clear (CSWHOLD = 0) for the switch to complete.

The current COSC and CDIV are indicated in the OSCCON2 register up to the moment when the switch actually occurs, at which time OSCCON2 is updated and ORDY is set. NOSCR is cleared by hardware to indicate that the switch is complete.

### TABLE 9-1: IVT ADDRESS CALCULATION SUMMARY

| IVT Address Calculation                                 |   | Interrupt Priority<br>INTCON0 Register, IPEN bit |                                   |  |  |

|---------------------------------------------------------|---|--------------------------------------------------|-----------------------------------|--|--|

|                                                         |   | 0                                                | 1                                 |  |  |

| Multi-Vector Enable<br>CONFIG 2L register<br>MVECEN bit | 0 | IVTBASE                                          | High Priority<br>IVTBASE          |  |  |

|                                                         | 0 | IVIDASE                                          | Low Priority<br>IVTBASE + 8 words |  |  |

|                                                         | 1 | IVTBASE + 2*(                                    | Vector Number)                    |  |  |

## 9.2.4 ACCESS CONTROL FOR IVTBASE REGISTERS

The Interrupt controller has an IVTLOCKED bit which can be set to avoid inadvertent changes to the IVT-BASE registers contents. Setting and clearing this bit requires a special sequence as an extra precaution against inadvertent changes.

To allow writes to IVTBASE registers, the interrupts must be disabled (GIEH = 0) and the IVTLOCKED bit must be cleared. The user must follow the sequence shown in Example 9-1 to clear the IVTLOCKED bit.

## EXAMPLE 9-1: IVT UNLOCK SEQUENCE

| ; | Disable Interrupts:  |                     |

|---|----------------------|---------------------|

|   | BCF                  | INTCON0, GIE;       |

| ; | Bank to IVTLOCK regi | ster                |

|   | BANKSEL              | IVTLOCK;            |

|   | MOVLW                | 55h;                |

|   |                      |                     |

| ; | Required sequence, n | ext 4 instructions  |

|   | MOVWF                | IVTLOCK;            |

|   | MOVLW                | AAh;                |

|   | MOVWF                | IVTLOCK;            |

|   |                      |                     |

| ; | Clear IVTLOCKED bit  | to enable writes    |

|   | BCF                  | IVTLOCK, IVTLOCKED; |

|   |                      |                     |

| ; | Enable Interrupts    |                     |

|   | BSF                  | INTCON0, GIE;       |

| 1 |                      |                     |

The user must follow the sequence shown in Example 9-2 to set the IVTLOCKED bit.

#### EXAMPLE 9-2: IVT LOCK SEQUENCE

| ; Disable Interrupts: |                     |

|-----------------------|---------------------|

| BCF                   | INTCONO, GIE;       |

| ; Bank to IVTLOCK reg | ister               |

| BANKSEL               | IVTLOCK;            |

| MOVLW                 | 55h;                |

|                       |                     |

| ; Required sequence,  | next 4 instructions |

| MOVWF                 | IVTLOCK;            |

| MOVLW                 | AAh;                |

| MOVWF                 | IVTLOCK;            |

|                       |                     |

| ; Set IVTLOCKED bit t | o enable writes     |

| BSF                   | IVTLOCK, IVTLOCKED; |

|                       |                     |

| ; Enable Interrupts   |                     |

| BSF                   | INTCON0, GIE;       |

|                       |                     |

When the IVT1WAY Configuration bit is set, the IVTLOCKED bit can be cleared and set only once after a device Reset. The unlock operation in Example 9-1 will have no effect after the lock sequence in Example 9-2 is used to set the IVTLOCK. Unlocking is inhibited until a system Reset occurs.

### 9.7.1 ABORTING INTERRUPTS

If the last instruction before the interrupt controller vectors to the ISR from main routine clears the GIE, PIE or PIR bit associated with the interrupt, the controller executes one force NOP cycle before it returns to the main routine.

Figure 9-10 illustrates the sequence of events when a peripheral interrupt is asserted and then cleared on the last executed instruction cycle.

If the GIE, PIE or PIR bit associated with the interrupt is cleared prior to vectoring to the ISR, then the controller continues executing the main routine.

### FIGURE 9-10: INTERRUPT TIMING DIAGRAM - ABORTING INTERRUPTS

|                         |      |                         |      |            |            | Rev. 10-002269D<br>7/6/2018 |

|-------------------------|------|-------------------------|------|------------|------------|-----------------------------|

|                         |      | 2                       | 3    | 4          | 5          |                             |

| Instruction<br>Clock    |      |                         |      |            |            |                             |

| Program<br>Counter      | X    | X+2                     | X+2  | X+4        | X+6        |                             |

| Instruction<br>Register |      | Inst @ X <sup>(1)</sup> | FNOP | Inst @ X+2 | Inst @ X+4 |                             |

| Interrupt               |      |                         |      |            |            |                             |

| Routine                 | MAII | N                       | FNOP | X MA       | N          | $\rangle$                   |

|                         |      |                         |      |            |            |                             |

Note 1: Inst @ X clears the interrupt flag, Example BCF INTCON0, GIE.

## TABLE 16-11: SUMMARY OF REGISTERS ASSOCIATED WITH I/O (CONTINUED)

| Name                  | Bit 7   | Bit 6   | Bit 5   | Bit 4                  | Bit 3                  | Bit 2   | Bit 1                  | Bit 0                  | Register on<br>Page |

|-----------------------|---------|---------|---------|------------------------|------------------------|---------|------------------------|------------------------|---------------------|

| INLVLC                | INLVLC7 | INLVLC6 | INLVLC5 | INLVLC4 <sup>(5)</sup> | INLVLC3 <sup>(5)</sup> | INLVLC2 | INLVLC1                | INLVLC0                | 270                 |

| INLVLD <sup>(6)</sup> | INLVLD7 | INLVLD6 | INLVLD5 | INLVLD4                | INLVLD3                | INLVLD2 | INLVLD1 <sup>(5)</sup> | INLVLD0 <sup>(5)</sup> | 270                 |

| INLVLF <sup>(7)</sup> | INLVLF7 | INLVLF6 | INLVLF5 | INLVLF4                | INLVLF3                | INLVLF2 | INLVLF1                | INLVLF0                | 270                 |

| INLVLE                | _       | _       | _       | _                      | INLVLE3                | _       | —                      | _                      | 270                 |

| RB1I2C                | _       | SLEW    | PU<     | 1:0>                   | _                      | _       | TH<                    | 1:0>                   | 271                 |

| RB2I2C                | _       | SLEW    | PU<     | 1:0>                   | _                      | _       | TH<                    | 1:0>                   | 271                 |

| RC3I2C                | _       | SLEW    | PU<     | 1:0>                   | _                      | _       | TH<                    | 1:0>                   | 271                 |

| RC4I2C                | _       | SLEW    | PU<1:0> |                        | _                      | _       | TH<1:0>                |                        | 271                 |

| RD0I2C <sup>(6)</sup> | _       | SLEW    | PU<1:0> |                        | _                      | _       | TH<1:0>                |                        | 271                 |

| RD1I2C <sup>(6)</sup> | —       | SLEW    | PU<     | 1:0>                   | —                      | _       | TH<                    | 1:0>                   | 271                 |

Legend: - = unimplemented location, read as '0'. Shaded cells are not used by I/O Ports.

Note 1:

Bits RB6 and RB7 read '1' while in Debug mode. Bit PORTE3 is read-only, and will read '1' when MCLRE = 1 (Master Clear enabled). Bits RB6 and RB7 read '1' while in Debug mode. 2:

3:

4: If MCLRE = 1, the weak pull-up in RE3 is always enabled; bit WPUE3 is not affected.

5: Any peripheral using the I<sup>2</sup>C pins read the I<sup>2</sup>C ST inputs when enabled via RxyI2C.

Unimplemented in PIC18(L)F26/27K42. 6:

7: Unimplemented in PIC18(L)F26/27/45/46/47K42 parts.

## REGISTER 17-3: PPSLOCK: PPS LOCK REGISTER

| U-0         | U-0 | U-0 | U-0 | U-0 | U-0 | U-0 | R/W-0/0   |  |  |

|-------------|-----|-----|-----|-----|-----|-----|-----------|--|--|

| —           | —   | —   | —   | —   | —   | —   | PPSLOCKED |  |  |

| bit 7 bit 0 |     |     |     |     |     |     |           |  |  |

|             |     |     |     |     |     |     |           |  |  |

| Legend:     |     |     |     |     |     |     |           |  |  |

| v                    |                      |                                                       |

|----------------------|----------------------|-------------------------------------------------------|

| R = Readable bit     | W = Writable bit     | U = Unimplemented bit, read as '0'                    |

| u = Bit is unchanged | x = Bit is unknown   | -n/n = Value at POR and BOR/Value at all other Resets |

| '1' = Bit is set     | '0' = Bit is cleared |                                                       |

#### bit 7-1 Unimplemented: Read as '0'

bit 0 **PPSLOCKED:** PPS Locked bit

1 = PPS is locked.

0 = PPS is not locked. PPS selections can be changed.

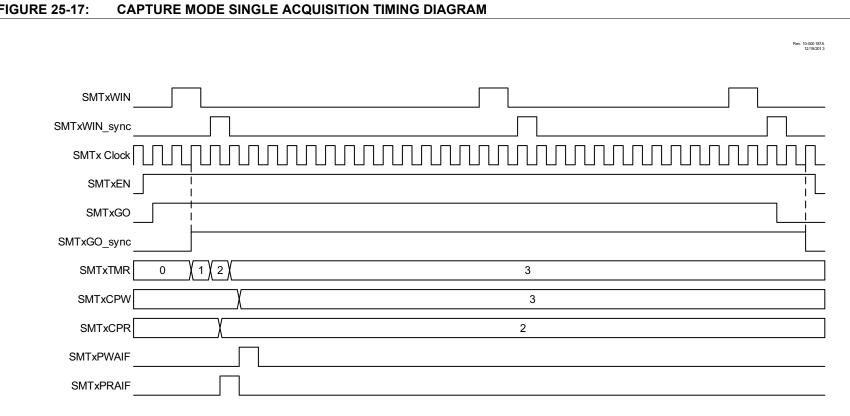

## FIGURE 25-17:

## 25.7 Interrupts

The SMT can trigger an interrupt under three different conditions:

- PW Acquisition Complete

- PR Acquisition Complete

- Counter Period Match

The interrupts are controlled by the PIR and PIE registers of the device.

#### 25.7.1 PW AND PR ACQUISITION INTERRUPTS

The SMT can trigger interrupts whenever it updates the SMT1CPW and SMT1CPR registers, the circumstances for which are dependent on the SMT mode, and are discussed in each mode's specific section. The SMT1CPW interrupt is controlled by SMT1PWAIF and SMT1PWAIE bits in the respective PIR and PIE registers. The SMT1CPR interrupt is controlled by the SMT1PRAIF and SMT1PRAIE bits, also located in the respective PIR and PIE registers.

In synchronous SMT modes, the interrupt trigger is synchronized to the SMT1CLK. In Asynchronous modes, the interrupt trigger is asynchronous. In either mode, once triggered, the interrupt will be synchronized to the CPU clock.

### 25.7.2 COUNTER PERIOD MATCH INTERRUPT

As described in Section 25.1.2 "Period Match interrupt", the SMT will also interrupt upon SMT1TMR, matching SMT1PR with its period match limit functionality described in Section 25.3 "Halt Operation". The period match interrupt is controlled by SMT1IF and SMT1IE, located in the respective PIR and PIE registers. Measuring VCPINV can be difficult, especially when the waveform is relative to VDD. However, by combining Equations 29-2 and 29-3, the resistor value can be determined from the time difference between the ZCD\_output high and low intervals. Note that the time difference,  $\Delta T$ , is 4\*TOFFSET. The equation for determining the pull-up and pull-down resistor values from the high and low ZCD\_output periods is shown in Equation 29-4.

### EQUATION 29-4: PULL-UP/DOWN RESISTOR VALUES

$$R = R_{SERIES} \left( \frac{V_{BIAS}}{V_{PEAK} \left( \sin\left( \pi Freq \frac{(\Delta T)}{2} \right) \right)} - 1 \right)$$

R is pull-up or pull-down resistor.

$\mathsf{VBIAS}\xspace$  is  $\mathsf{VPULLUP}\xspace$  when R is pull-up or  $\mathsf{VDD}\xspace$  when R is pull-down.

$\Delta T$  is the ZCDOUT high and low period difference.

## 29.6 Handling VPEAK Variations

If the peak amplitude of the external voltage is expected to vary, the series resistor must be selected to keep the ZCD current source and sink below the design maximum range of  $\pm 600 \ \mu$ A and above a reasonable minimum range. A general rule of thumb is that the maximum peak voltage can be no more than six times the minimum peak voltage. To ensure that the maximum current does not exceed  $\pm 600 \ \mu$ A and the minimum is at least  $\pm 100 \ \mu$ A, compute the series resistance as shown in Equation 29-5. The compensating pull-up for this series resistance can be determined with Equation 29-3 because the pull-up value is not dependent to the peak voltage.

## EQUATION 29-5: SERIES R FOR V RANGE

$$R_{SERIES} = \frac{V_{MAXPEAK} + V_{MINPEAK}}{7 \times 10^{-4}}$$

## 29.7 Operation During Sleep

The ZCD current sources and interrupts are unaffected by Sleep.

## 29.8 Effects of a Reset

The ZCD circuit can be configured to default to the active or inactive state on Power-on-Reset (POR). When the ZCD Configuration bit is cleared, the ZCD circuit will be active at POR. When the ZCD Configuration bit is set, the SEN bit of the ZCDCON register must be set to enable the ZCD module.

## 29.9 Disabling the ZCD Module

The ZCD module can be disabled in two ways:

- Configuration Word 2H has the ZCD bit which disables the ZCD module when set, but it can be enabled using the SEN bit of the ZCDCON register (Register 29-1). If the ZCD bit is clear, the ZCD is always enabled.

- The ZCD can also be disabled using the ZCDMD bit of the respective PMD2 register (Register 19-3). This is subject to the status of the ZCD bit.

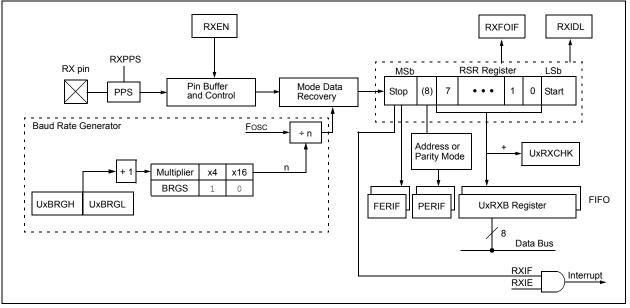

### FIGURE 31-2: UART RECEIVE BLOCK DIAGRAM

The operation of the UART module is controlled through nineteen registers:

- Three control registers (UxCON0-UxCON2)

- Error enable and status (UxERRIE, UxERRIR, UxUIR)

- UART buffer status and control (UxFIFO)

- Three 9-bit protocol parameters (UxP1-UxP3)

- 16-bit baud rate generator (UxBRGH:L)

- Transmit buffer write (UxTXB)

- Receive buffer read (UxRXB)

- Receive checksum (UxRXCHK)

- Transmit checksum (UxTXCHK)

These registers are detailed in Section 31.21 "Register Definitions: UART Control".

## 31.1 UART I/O Pin Configuration

The RX input pin is selected with the UxRPPS register. The TX output pin is selected with each pin's RxyPPS register. When the TRIS control for the pin corresponding to the TX output is cleared, then the UART will maintain control and the logic level on the TX pin. Changing the TXPOL bit in UxCON2 will immediately change the TX pin logic level regardless of the value of EN or TXEN.

## 31.2 UART Asynchronous Modes

The UART has five asynchronous modes:

- 7-bit

- 8-bit

- 8-bit with even parity in the 9th bit

- 8-bit with odd parity in the 9th bit

- 8-bit with address indicator in the 9th bit

The UART transmits and receives data using the standard Non-Return-to-Zero (NRZ) format. NRZ is implemented with two levels: a VOH mark state, which

represents a '1' data bit, and a VOL space state, which represents a '0' data bit. NRZ refers to the fact that consecutively transmitted data bits of the same value stay at the output level of that bit without returning to a neutral level between each bit transmission. An NRZ transmission port idles in the Mark state. Each character transmission consists of one Start bit followed by seven or eight data bits, one optional parity or address bit, and is always terminated by one or more Stop bits. The Start bit is always a space and the Stop bits are always marks. The most common data format is eight bits with no parity. Each transmitted bit persists for a period of 1/ (Baud Rate). An on-chip dedicated 16-bit Baud Rate Generator is used to derive standard baud rate frequencies from the system oscillator. See Section 31.17 "UART Baud Rate Generator (BRG)" for more information.

In all the asynchronous modes, the UART transmits and receives the LSb first. The UART's transmitter and receiver are functionally independent, but share the same data format and baud rate. Parity is supported by the hardware by even and odd parity modes.

### 31.2.1 UART ASYNCHRONOUS TRANSMITTER

The UART transmitter block diagram is shown in Figure 31-1. The heart of the transmitter is the serial Transmit Shift Register (TSR), which is not directly accessible by software. The TSR obtains its data from the transmit buffer, which is the UxTXB register.

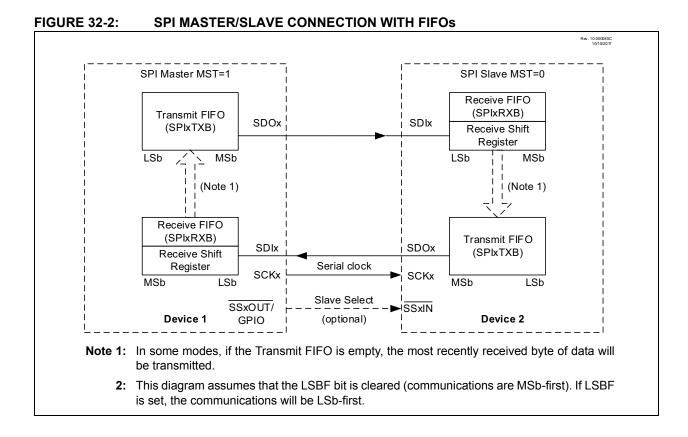

### 32.8.3.4 Receiver Overflow and Transmitter Underflow Interrupts

The receiver overflow interrupt triggers if data is received when the RXFIFO is already full and RXR = 1. In this case, the data will be discarded and the RXOIF bit will be set. The receiver overflow interrupt flag is the RXOIF bit of SPIxINTF. The receiver overflow interrupt enable bit is the RXOIE bit of SPIxINTE.

The Transmitter Underflow interrupt flag triggers if a data transfer begins when the TXFIFO is empty and TXR = 1. In this case, the most recently received data will be transmitted and the TXUIF bit will be set. The transmitter underflow interrupt flag is the TXUIF bit of SPIxINTF. The transmitter underflow interrupt enable bit is the TXUIE bit of SPIxINTE.

Both of these interrupts will only occur in Slave mode, as Master mode will not allow the RXFIFO to overflow or the TXFIFO to underflow.

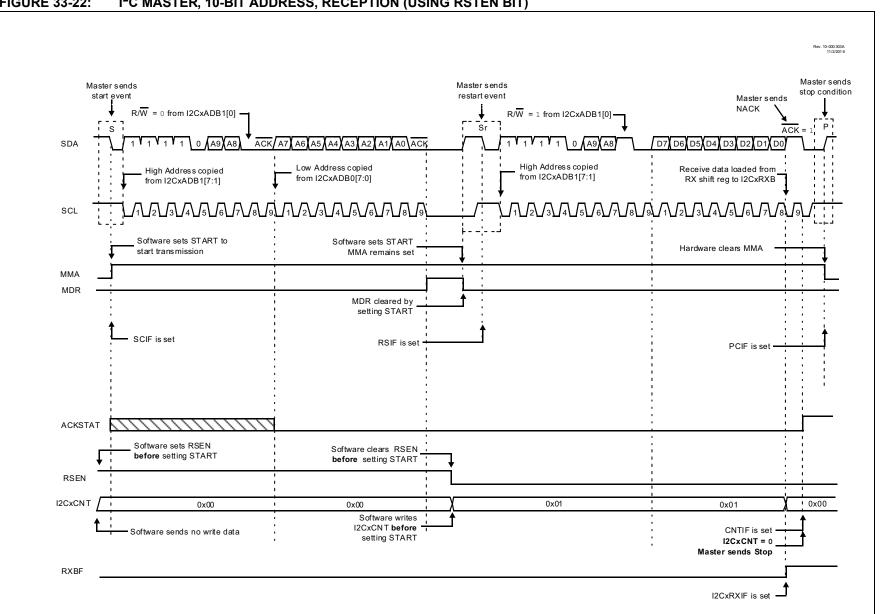

## FIGURE 33-22: I<sup>2</sup>C MASTER, 10-BIT ADDRESS, RECEPTION (USING RSTEN BIT)

© 2016-2017 Microchip Technology Inc

## 36.5.2 PRECHARGE CONTROL

The precharge stage is an optional period of time that brings the external channel and internal sample and hold capacitor to known voltage levels. Precharge is enabled by writing a non-zero value to the ADPRE register. This stage is initiated when an ADC conversion begins, either from setting the GO bit, a special event trigger, or a conversion restart from the computation functionality. If the ADPRE register is cleared when an ADC conversion begins, this stage is skipped.

During the precharge time, CHOLD is disconnected from the outer portion of the sample path that leads to the external capacitive sensor and is connected to either VDD or VSS, depending on the value of the PPOL bit of ADCON1. At the same time, the port pin logic of the selected analog channel is overridden to drive a digital high or low out, in order to precharge the outer portion of the ADC's sample path, which includes the external sensor. The output polarity of this override is also determined by the PPOL bit of ADCON1. The amount of time that this charging receives is controlled by the ADPRE register.

- **Note 1:** The external charging overrides the TRIS setting of the respective I/O pin.

- **2:** If there is a device attached to this pin, Precharge should not be used.

## 36.5.3 ACQUISITION CONTROL

The Acquisition stage is an optional time for the voltage on the internal sample and hold capacitor to charge or discharge from the selected analog channel. This acquisition time is controlled by the ADACQ register. If PRE = 0, acquisition starts at the beginning of conversion. When PRE = 1, the acquisition stage begins when precharge ends.

At the start of the acquisition stage, the port pin logic of the selected analog channel is overridden to turn off the digital high/low output drivers so they do not affect the final result of the charge averaging. Also, the selected ADC channel is connected to CHOLD. This allows charge averaging to proceed between the precharged channel and the CHOLD capacitor.

Note: When PRE! = 0, acquisition time cannot be '0'. In this case, setting ADACQ to '0' will set a maximum acquisition time (8191 ADC clock cycles). When precharge is disabled, setting ADACQ to '0' will disable hardware acquisition time control.

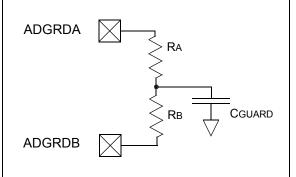

## 36.5.4 GUARD RING OUTPUTS

Figure 36-8 shows a typical guard ring circuit. CGUARD represents the capacitance of the guard ring trace placed on the PCB board. The user selects values for RA and RB that will create a voltage profile on CGUARD, which will match the selected acquisition channel.

The purpose of the guard ring is to generate a signal in phase with the CVD sensing signal to minimize the effects of the parasitic capacitance on sensing electrodes. It also can be used as a mutual drive for mutual capacitive sensing. For more information about active guard and mutual drive, see Application Note AN1478, "*mTouch*<sup>TM</sup> Sensing Solution Acquisition Methods Capacitive Voltage Divider" (DS01478).

The ADC has two guard ring drive outputs, ADGRDA and ADGRDB. These outputs can be routed through PPS controls to I/O pins (see Section **17.0 "Peripheral Pin Select (PPS) Module**" for details) and the polarity of these outputs are controlled by the ADGPOL and ADIPEN bits of ADCON1.

At the start of the first precharge stage, both outputs are set to match the ADGPOL bit of ADCON1. Once the acquisition stage begins, ADGRDA changes polarity, while ADGRDB remains unchanged. When performing a double sample conversion, setting the ADIPEN bit of ADCON1 causes both guard ring outputs to transition to the opposite polarity of ADGPOL at the start of the second precharge stage, and ADGRDA toggles again for the second acquisition. For more information on the timing of the guard ring output, refer to Figure 36-8 and Figure 36-9.

## 38.13 Register Definitions: Comparator Control

Long bit name prefixes for the Comparators are shown in Table 38-2. Refer to **Section 1.3.2.2 "Long Bit Names"** for more information.

#### TABLE 38-2:

| Peripheral | Bit Name Prefix |

|------------|-----------------|

| C1         | C1              |

| C2         | C2              |

### REGISTER 38-1: CMxCON0: COMPARATOR x CONTROL REGISTER 0

| R/W-0/0 | R-0/0 | U-0 | R/W-0/0 | U-0 | U-1 | R/W-0/0 | R/W-0/0 |

|---------|-------|-----|---------|-----|-----|---------|---------|

| EN      | OUT   | —   | POL     | —   | —   | HYS     | SYNC    |

| bit 7   |       |     |         |     |     |         | bit 0   |

| Legend:           |                  |                             |                    |

|-------------------|------------------|-----------------------------|--------------------|

| R = Readable bit  | W = Writable bit | U = Unimplemented bit, read | as '0'             |

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared        | x = Bit is unknown |

| bit 7 | EN: Comparator Enable bit                                                                            |

|-------|------------------------------------------------------------------------------------------------------|

|       | 1 = Comparator is enabled                                                                            |

|       | 0 = Comparator is disabled and consumes no active power                                              |

| bit 6 | OUT: Comparator Output bit                                                                           |

|       | <u>If POL = 0 (noninverted polarity)</u> :<br>1 = CxVP > CxVN                                        |

|       | 0 = CxVP < CxVN                                                                                      |

|       | If POL = 1 (inverted polarity):                                                                      |

|       | 1 = CxVP < CxVN                                                                                      |

|       | 0 = CxVP > CxVN                                                                                      |

| bit 5 | Unimplemented: Read as '0'                                                                           |

| bit 4 | POL: Comparator Output Polarity Select bit                                                           |

|       | <ul> <li>1 = Comparator output is inverted</li> <li>0 = Comparator output is not inverted</li> </ul> |

| bit 3 | Unimplemented: Read as '0'                                                                           |

| bit 2 | Unimplemented: Read as '1'                                                                           |

| bit 1 | HYS: Comparator Hysteresis Enable bit                                                                |

|       | 1 = Comparator hysteresis enabled                                                                    |

|       | 0 = Comparator hysteresis disabled                                                                   |

| bit 0 | SYNC: Comparator Output Synchronous Mode bit                                                         |

|       | 1 = Comparator output to Timer1/3/5 and I/O pin is synchronous to changes on Timer1 clock source.    |

|       | 0 = Comparator output to Timer1/3/5 and I/O pin is asynchronous                                      |

|       | Output updated on the falling edge of Timer1/3/5 clock source.                                       |

|       |                                                                                                      |

| ANDWF                                          | AND W with f                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | BC                                                                                    | Branch if Carry                                                                                                                                                                                                                                                                                    |  |  |

|------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|

| Syntax:                                        | ANDWF f {,d {,a}}                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | Syntax:                                                                               | BC n                                                                                                                                                                                                                                                                                               |  |  |

| Operands:                                      | $0 \leq f \leq 255$                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | Operands:                                                                             | $-128 \le n \le 127$                                                                                                                                                                                                                                                                               |  |  |

|                                                | d ∈ [0,1]<br>a ∈ [0,1]                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | Operation:                                                                            | if CARRY bit is '1'<br>(PC) + 2 + 2n $\rightarrow$ PC                                                                                                                                                                                                                                              |  |  |

| Operation:                                     | (W) .AND. (f) $\rightarrow$ dest                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | Status Affected:                                                                      | None                                                                                                                                                                                                                                                                                               |  |  |

| Status Affected:                               | N, Z                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | Encoding:                                                                             | 1110 0010 nnnn nnnn                                                                                                                                                                                                                                                                                |  |  |

| Encoding:<br>Description:                      | 000101daffffffffThe contents of W are AND'ed with<br>register 'f'. If 'd' is '0', the result is stored<br>in W. If 'd' is '1', the result is stored back<br>in register 'f' (default).If 'a' is '0', the Access Bank is selected.If 'a' is '0', the BSR is used to select the<br>GPR bank.If 'a' is '0' and the extended instruction<br>set is enabled, this instruction operates<br>in Indexed Literal Offset Addressing<br>mode whenever f ≤ 95 (5Fh). See Section 41.2.3 "Byte-Oriented and Bit- | Description:<br>Words:<br>Cycles:<br>Q Cycle Activity:<br>If Jump:                    | If the CARRY bit is '1', then the program<br>will branch.<br>The 2's complement number '2n' is<br>added to the PC. Since the PC will have<br>incremented to fetch the next<br>instruction, the new address will be<br>PC + 2 + 2n. This instruction is then a<br>2-cycle instruction.<br>1<br>1(2) |  |  |

|                                                | Oriented Instructions in Indexed Lit-<br>eral Offset Mode" for details.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | Q1                                                                                    | Q2 Q3 Q4                                                                                                                                                                                                                                                                                           |  |  |

| Words:                                         | 1                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | Decode                                                                                | Read literalProcessWrite to PC'n'Data                                                                                                                                                                                                                                                              |  |  |

| Cycles:                                        | 1                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | No                                                                                    | No No No                                                                                                                                                                                                                                                                                           |  |  |

| Q Cycle Activity:                              |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | operation                                                                             | operation operation operation                                                                                                                                                                                                                                                                      |  |  |

| Q1                                             | Q2 Q3 Q4                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | If No Jump:                                                                           |                                                                                                                                                                                                                                                                                                    |  |  |

| Decode                                         | Read Process Write to                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | Q1<br>Decode                                                                          | Q2 Q3 Q4<br>Read literal Process No                                                                                                                                                                                                                                                                |  |  |

|                                                | register 'f' Data destination                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | Decode                                                                                | 'n' Data operation                                                                                                                                                                                                                                                                                 |  |  |

| <u>Example</u> :<br>Before Instruc<br>W<br>REG | ANDWF REG, 0, 0<br>tion<br>= 17h<br>= C2h                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | <u>Example</u> :<br>Before Instruc<br>PC<br>After Instructi                           | = address (HERE)                                                                                                                                                                                                                                                                                   |  |  |

| After Instructio<br>W<br>REG                   | on<br>= 02h<br>= C2h                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | If CARRY = 1;<br>PC = address (HERE + 12)<br>If CARRY = 0;<br>PC = address (HERE + 2) |                                                                                                                                                                                                                                                                                                    |  |  |

|                                                                                        |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |                 |                          |                               | Branch if           |                                                        |             |  |  |  |

|----------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------|--------------------------|-------------------------------|---------------------|--------------------------------------------------------|-------------|--|--|--|

| Syntax:                                                                                | BNOV n                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |                 |                          | Syntax:                       | BNZ n               | BNZ n                                                  |             |  |  |  |

| Operands:                                                                              | -128 ≤ n ≤ 1                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | 27              |                          | Operands:                     | -128 ≤ n ≤ 1        | -128 ≤ n ≤ 127                                         |             |  |  |  |

| Operation:                                                                             | if OVERFLOW bit is '0' Operation: if ZERO bit is '0' $(PC) + 2 + 2n \rightarrow PC$ $(PC) + 2 + 2n \rightarrow FC$                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |                 |                          |                               |                     |                                                        |             |  |  |  |

| Status Affected:                                                                       | None                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |                 |                          | Status Affected:              | None                | None                                                   |             |  |  |  |

| Encoding:                                                                              | 1110                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | 0101 nn:        | nn nnnn                  | Encoding:                     | 1110                | 1110 0001 nnnn                                         |             |  |  |  |

| Description:                                                                           | Description:<br>If the OVERFLOW bit is '0', then the<br>program will branch.<br>The 2's complement number '2n' is<br>added to the PC. Since the PC will have<br>incremented to fetch the next<br>instruction, the new address will be<br>PC + 2 + 2n. This instruction is then a<br>2-cycle instruction.<br>If the ZERO bit is '0', then<br>mill branch.<br>The 2's complement number<br>added to the PC. Since the PC will have<br>incremented to fetch the next<br>instruction, the new address will be<br>PC + 2 + 2n. This instruction is then a<br>2-cycle instruction.<br>2-cycle instruction. |                 |                          |                               |                     | nber '2n' is<br>ne PC will have<br>next<br>ess will be |             |  |  |  |

| Words:                                                                                 | 1                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |                 |                          | Words:                        | 1                   |                                                        |             |  |  |  |

| Cycles:                                                                                | 1(2)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |                 |                          | Cycles:                       | 1(2)                |                                                        |             |  |  |  |

| Q Cycle Activity:<br>If Jump:                                                          |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |                 |                          | Q Cycle Activity:<br>If Jump: |                     |                                                        |             |  |  |  |

| Q1                                                                                     | Q2                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | Q3              | Q4                       | Q1                            | Q2                  | Q3                                                     | Q4          |  |  |  |

| Decode                                                                                 | Read literal<br>'n'                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | Process<br>Data | Write to PC              | Decode                        | Read literal<br>'n' | Process<br>Data                                        | Write to PC |  |  |  |

| No                                                                                     | No                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | No              | No                       | No                            | No                  | No                                                     | No          |  |  |  |

| operation                                                                              | operation                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | operation       | operation                | operation                     | operation           | operation                                              | operation   |  |  |  |

| If No Jump:                                                                            | 00                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | 00              | 04                       | If No Jump:                   | 00                  | 00                                                     | 04          |  |  |  |

| Q1<br>Decode                                                                           | Q2<br>Read literal                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | Q3<br>Process   | Q4<br>No                 | Q1<br>Decode                  | Q2<br>Read literal  | Q3<br>Process                                          | Q4<br>No    |  |  |  |

| Decode                                                                                 | 'n'                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | Data            | operation                | Decode                        | 'n'                 | Data                                                   | operation   |  |  |  |

| Example:<br>Before Instru                                                              |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | BNOV Jump       | <u> </u>                 | Example:<br>Before Instr      |                     | BNZ Jump                                               |             |  |  |  |

| PC = address (HERE)<br>After Instruction                                               |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |                 | PC<br>After Instruc      |                               | dress (HERE)        | )                                                      |             |  |  |  |

| If OVERFLOW = 0;<br>PC = address (Jump)<br>If OVERFLOW = 1;<br>PC = address (HERE + 2) |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |                 | After Instruct<br>If ZER |                               |                     |                                                        |             |  |  |  |

| SUBFWB                                                                                     | Subtract                                                                                                                                                                                                           | Subtract f from W with borrow                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |                      |  |  |  |  |

|--------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------|--|--|--|--|

| Syntax:                                                                                    | SUBFWB                                                                                                                                                                                                             | SUBFWB f {,d {,a}}                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |                      |  |  |  |  |

| Operands:                                                                                  | 0 ≤ f ≤ 255<br>d ∈ [0,1]<br>a ∈ [0,1]                                                                                                                                                                              |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |                      |  |  |  |  |

| Operation:                                                                                 |                                                                                                                                                                                                                    | $(\overline{C}) \rightarrow dest$                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |                      |  |  |  |  |

| Status Affected:                                                                           | N, OV, C,                                                                                                                                                                                                          | DC, Z                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |                      |  |  |  |  |

| Encoding:                                                                                  | 0101                                                                                                                                                                                                               | 01da ffi                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | ff ffff              |  |  |  |  |

| Description:                                                                               | (borrow) fr<br>method). If<br>in W. If 'd'<br>register 'f'<br>If 'a' is '0',<br>selected. I<br>to select th<br>If 'a' is '0' a<br>set is enab<br>operates in<br>Addressing<br>$f \le 95$ (5FH<br><b>41.2.3 "By</b> | Subtract register 'f' and CARRY flag<br>(borrow) from W (2's complement<br>method). If 'd' is '0', the result is stored<br>in W. If 'd' is '1', the result is stored in<br>register 'f' (default).<br>If 'a' is '0', the Access Bank is<br>selected. If 'a' is '1', the BSR is used<br>to select the GPR bank.<br>If 'a' is '0' and the extended instruction<br>set is enabled, this instruction<br>operates in Indexed Literal Offset<br>Addressing mode whenever<br>$f \le 95$ (5Fh). See Section<br>41.2.3 "Byte-Oriented and Bit-Ori-<br>ented Instructions in Indexed Literal |                      |  |  |  |  |

| Words:                                                                                     | UTTSET MO                                                                                                                                                                                                          | de" for details.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |                      |  |  |  |  |

| Cycles:                                                                                    | 1                                                                                                                                                                                                                  |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |                      |  |  |  |  |

| Q Cycle Activity:                                                                          |                                                                                                                                                                                                                    |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |                      |  |  |  |  |