Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

### Details

E·XFI

| Product Status             | Active                                                                     |

|----------------------------|----------------------------------------------------------------------------|

| Core Processor             | PIC                                                                        |

| Core Size                  | 8-Bit                                                                      |

| Speed                      | 64MHz                                                                      |

| Connectivity               | I <sup>2</sup> C, LINbus, SPI, UART/USART                                  |

| Peripherals                | Brown-out Detect/Reset, DMA, HLVD, POR, PWM, WDT                           |

| Number of I/O              | 44                                                                         |

| Program Memory Size        | 128KB (64K x 16)                                                           |

| Program Memory Type        | FLASH                                                                      |

| EEPROM Size                | 1K x 8                                                                     |

| RAM Size                   | 8K x 8                                                                     |

| Voltage - Supply (Vcc/Vdd) | 2.3V ~ 5.5V                                                                |

| Data Converters            | A/D 43x12b; D/A 1x5b                                                       |

| Oscillator Type            | Internal                                                                   |

| Operating Temperature      | -40°C ~ 125°C (TA)                                                         |

| Mounting Type              | Surface Mount                                                              |

| Package / Case             | 48-UFQFN Exposed Pad                                                       |

| Supplier Device Package    | 48-UQFN (6x6)                                                              |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/pic18f57k42-e-mv |

|                            |                                                                            |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

| Ο                       |

|-------------------------|

| $\sim$                  |

| Ξ                       |

| 3                       |

|                         |

| .)                      |

|                         |

| N                       |

| 6                       |

| $\overline{\mathbf{N}}$ |

|                         |

|                         |

| 4                       |

| S                       |

| 4                       |

| 9                       |

| Ň                       |

| 4                       |

|                         |

| 5                       |

| 5                       |

| N N                     |

| 5                       |

| 6                       |

|                         |

| N                       |

| F                       |

|                         |

| 4                       |

| N                       |

\_

| 0/I  | 40-Pin PDIP | 44-Pin TQFP | 40-Pin UQFN | 44-Pin QFN | ADC                           | Voltage Reference | DAC              | Comparators      | Zero Cross Detect | I <sup>2</sup> C      | SPI                | UART                | MSQ                   | Timers/SMT                                                                                   | CCP and PWM         | CWG                   | СГС                   | NCO | Clock Reference (CLKR) | Interrupt-on-Change          | Basic          |

|------|-------------|-------------|-------------|------------|-------------------------------|-------------------|------------------|------------------|-------------------|-----------------------|--------------------|---------------------|-----------------------|----------------------------------------------------------------------------------------------|---------------------|-----------------------|-----------------------|-----|------------------------|------------------------------|----------------|

| RA0  | 2           | 19          | 17          | 19         | ANA0                          |                   | —                | C1IN0-<br>C2IN0- |                   | _                     | _                  | _                   | —                     | —                                                                                            |                     | -                     | CLCIN0 <sup>(1)</sup> | -   | _                      | IOCA0                        | _              |

| RA1  | 3           | 20          | 18          | 20         | ANA1                          | —                 | —                | C1IN1-<br>C2IN1- | —                 | —                     | —                  | —                   | _                     | —                                                                                            | —                   | —                     | CLCIN1 <sup>(1)</sup> | -   | —                      | IOCA1                        | —              |

| RA2  | 4           | 21          | 19          | 21         | ANA2                          | VREF-             | DAC1OUT1         | C1IN0+<br>C2IN0+ |                   | -                     | -                  | -                   | —                     | —                                                                                            | -                   | -                     | -                     | -   | -                      | IOCA2                        | —              |

| RA3  | 5           | 22          | 20          | 22         | ANA3                          | VREF+             | _                | C1IN1+           | _                 | _                     | _                  | _                   | MDCARL <sup>(1)</sup> | _                                                                                            |                     | _                     | _                     |     | _                      | IOCA3                        | _              |

| RA4  | 6           | 23          | 21          | 23         | ANA4                          | _                 | _                | _                | _                 | _                     | _                  | _                   | MDCARH <sup>(1)</sup> | T0CKI <sup>(1)</sup>                                                                         | -                   | _                     | _                     | _   | _                      | IOCA4                        | _              |

| RA5  | 7           | 24          | 22          | 24         | ANA5                          | -                 | _                | _                | _                 | _                     | SS1 <sup>(1)</sup> | _                   | MDSRC <sup>(1)</sup>  | _                                                                                            | _                   | _                     | _                     | _   | _                      | IOCA5                        | —              |

| RA6  | 14          | 31          | 29          | 33         | ANA6                          | _                 | —                | —                | —                 | _                     | —                  | —                   | —                     | —                                                                                            | -                   | —                     | —                     | —   | —                      | IOCA6                        | OSC2<br>CLKOUT |

| RA7  | 13          | 30          | 28          | 32         | ANA7                          | _                 | —                | —                | _                 | —                     | —                  | —                   | —                     | —                                                                                            | -                   | —                     | —                     | —   | —                      | IOCA7                        | OSC1<br>CLKIN  |

| RB0  | 33          | 8           | 8           | 9          | ANB0                          | -                 | —                | C2IN1+           | ZCD               | —                     | —                  | —                   | —                     | —                                                                                            | CCP4 <sup>(1)</sup> | CWG1IN <sup>(1)</sup> | -                     | -   | —                      | INT0 <sup>(1)</sup><br>IOCB0 | —              |

| RB1  | 34          | 9           | 9           | 10         | ANB1                          |                   | —                | C1IN3-<br>C2IN3- | —                 | SCL2 <sup>(3,4)</sup> | —                  | —                   | —                     | —                                                                                            | _                   | CWG2IN <sup>(1)</sup> | -                     | —   | —                      | INT1 <sup>(1)</sup><br>IOCB1 | —              |

| RB2  | 35          | 10          | 10          | 11         | ANB2                          | -                 | —                | —                | —                 | SDA2 <sup>(3,4)</sup> | —                  | —                   | -                     | —                                                                                            | -                   | CWG3IN <sup>(1)</sup> | -                     | -   | —                      | INT2 <sup>(1)</sup><br>IOCB2 | —              |

| RB3  | 36          | 11          | 11          | 12         | ANB3                          | _                 | —                | C1IN2-<br>C2IN2- | —                 | -                     | -                  | -                   | -                     | —                                                                                            | _                   | -                     | -                     | _   | -                      | IOCB3                        | —              |

| RB4  | 37          | 14          | 12          | 14         | ANB4<br>ADCACT <sup>(1)</sup> | _                 | —                | —                | —                 | -                     | -                  | -                   | —                     | T5G <sup>(1)</sup>                                                                           | _                   | -                     | -                     | -   | -                      | IOCB4                        | —              |

| RB5  | 38          | 15          | 13          | 15         | ANB5                          | -                 | _                | _                | _                 | -                     | _                  | _                   | _                     | T1G <sup>(1)</sup>                                                                           | CCP3 <sup>(1)</sup> | _                     | -                     | _   | _                      | IOCB5                        | _              |

| RB6  | 39          | 16          | 14          | 16         | ANB6                          | _                 | _                | —                | _                 | _                     | _                  | CTS2 <sup>(1)</sup> | _                     | -                                                                                            | _                   | _                     | CLCIN2 <sup>(1)</sup> | _   | —                      | IOCB6                        | ICSPCLK        |

| RB7  | 40          | 17          | 15          | 17         | ANB7                          | _                 | DAC1OUT2         | _                | _                 | _                     | _                  | RX2 <sup>(1)</sup>  | _                     | T6IN <sup>(1)</sup>                                                                          | _                   | _                     | CLCIN3 <sup>(1)</sup> |     | _                      | IOCB7                        | ICSPDAT        |

| RC0  | 15          | 32          | 30          | 34         | ANC0                          |                   | _                | —                | —                 | -                     | —                  | —                   | —                     | T1CKI <sup>(1)</sup><br>T3CKI <sup>(1)</sup><br>T3G <sup>(1)</sup><br>SMTWIN1 <sup>(1)</sup> | _                   | —                     | _                     | _   | —                      | IOCC0                        | SOSCO          |

| RC1  | 16          | 35          | 31          | 35         | ANC1                          |                   | —                | _                | _                 | _                     | _                  | _                   | —                     | SMTSIG1 <sup>(1)</sup>                                                                       | CCP2 <sup>(1)</sup> | _                     | _                     | _   | _                      | IOCC1                        | SOSCI          |

| RC2  | 17          | 36          | 32          | 36         | ANC2                          | —                 | _                | —                | _                 | _                     | _                  | —                   | _                     | T5CKI <sup>(1)</sup>                                                                         | CCP1 <sup>(1)</sup> | _                     | —                     |     | —                      | IOCC2                        | —              |

| Note | 1:          | This        | is a F      | PS re      | mappable inpu                 | t signal. Th      | e input function | may be me        | oved fro          | om the default        | location sh        | own to one          | of several othe       | er PORTx pins.                                                                               |                     |                       |                       |     |                        |                              |                |

2:

40/44-PIN ALLOCATION TABLE FOR PIC18(L)F4XK42

All output signals shown in this row are PPS remappable. This is a bidirectional signal. For normal module operation, the firmware should map this signal to the same pin in both the PPS input and PPS output registers. 3:

These pins can be configured for I<sup>2</sup>C and SMB<sup>TM</sup> 3.0/2.0 logic levels; The SCLx/SDAx signals may be assigned to any of the RB1/RB2/RC3/RC4/RD0/RD1 pins. PPS assignments to the other pins (e.g., RA5) will operate, but input logic levels will be standard TTL/ST as selected by the INLVL register, instead of the I<sup>2</sup>C specific or SMBus input buffer thresholds. 4:

TABLE 2:

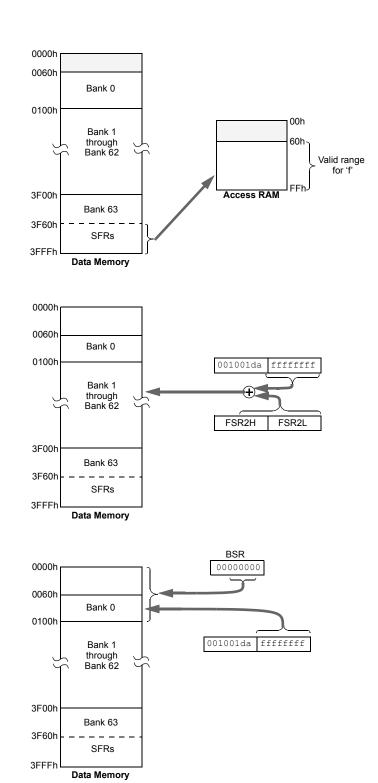

## FIGURE 4-7: COMPARING ADDRESSING OPTIONS FOR BIT-ORIENTED AND BYTE-ORIENTED INSTRUCTIONS (EXTENDED INSTRUCTION SET ENABLED)

**EXAMPLE INSTRUCTION:** ADDWF, f, d, a (Opcode: 0010 01da ffff ffff)

## When 'a' = 0 and $f \ge 60h$ :

The instruction executes in Direct Forced mode. 'f' is interpreted as a location in the Access RAM between 060h and 0FFh. This is the same as locations 3F60h to 3FFFh (Bank 63) of data memory.

Locations below 60h are not available in this Addressing mode.

#### When 'a' = 0 and $f \le 5Fh$ :

The instruction executes in Indexed Literal Offset mode. 'f' is interpreted as an offset to the address value in FSR2. The two are added together to obtain the address of the target register for the instruction. The address can be anywhere in the data memory space.

Note that in this mode, the correct syntax is now: ADDWF [k], d where 'k' is the same as 'f'.

#### When 'a' = 1 (all values of f):

The instruction executes in Direct mode (also known as Direct Long mode). 'f' is interpreted as a location in one of the 63 banks of the data memory space. The bank is designated by the Bank Select Register (BSR). The address can be in any implemented bank in the data memory space.

# 5.0 DEVICE CONFIGURATION

Device configuration consists of the Configuration Words, User ID, Device ID, Rev ID, Device Information Area (DIA), (see Section 5.7 "Device Information Area"), and the Device Configuration Information (DCI) regions, (see Section 5.8 "Device Configuration Information").

## 5.1 Configuration Words

There are six Configuration Word bits that allow the user to setup the device with several choices of oscillators, Resets and memory protection options. These are implemented as Configuration Word 1 through Configuration Word 6 at 300000h through 30000Bh.

| BOREN<1:0> | SBOREN | Device Mode | BOR Mode  | Instruction Execution upon:             |                                         |  |  |

|------------|--------|-------------|-----------|-----------------------------------------|-----------------------------------------|--|--|

| BOREN 1.02 | JOREN  | Device Mode | BOR WOUL  | Release of POR                          | Wake-up from Sleep                      |  |  |

| 11         | Х      | х           | Active    | Wait for release of BOR<br>(BORRDY = 1) | Begins immediately                      |  |  |

| 1.0        | Awake  |             | Active    | Wait for release of BOR<br>(BORRDY = 1) | N/A                                     |  |  |

| 10         | Х      | Sleep       | Hibernate | N/A                                     | Wait for release of BOR<br>(BORRDY = 1) |  |  |

| 01         | 1 X    |             | Active    | Wait for release of BOR                 | Desine immediately                      |  |  |

| UI         | 0      | 0 X Hiberna |           | (BORRDY = 1)                            | Begins immediately                      |  |  |

| 00         | Х      | Х           | Disabled  | Begins im                               | s immediately                           |  |  |

## TABLE 6-1: BOR OPERATING MODES

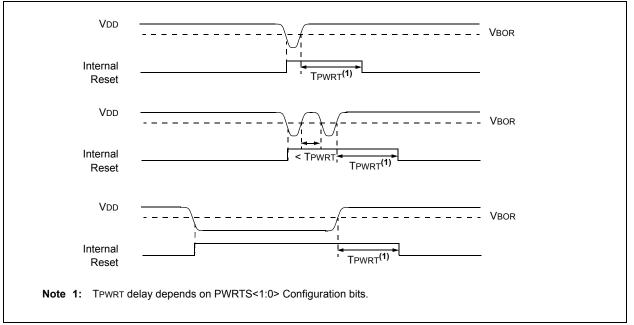

## FIGURE 6-3: BROWN-OUT SITUATIONS

| R/W-0/0        | R/W-0/0                                                            | R/W-0/0                   | R/W-0/0                                                         | R/W-0/0           | R/W-0/0           | R/W-0/0    | R/W-0/0    |  |  |  |  |  |

|----------------|--------------------------------------------------------------------|---------------------------|-----------------------------------------------------------------|-------------------|-------------------|------------|------------|--|--|--|--|--|

| I2C1RXIE       | SPI1IE                                                             | SPI1TXIE                  | SPI1RXIE                                                        | DMA1AIE           | DMA10RIE          | DMA1DCNTIE | DMA1SCNTIE |  |  |  |  |  |

| bit 7          |                                                                    |                           |                                                                 |                   |                   |            | bit C      |  |  |  |  |  |

| Legend:        |                                                                    |                           |                                                                 |                   |                   |            |            |  |  |  |  |  |

| R = Readab     | ole bit                                                            | W = Writable              | bit                                                             | U = Unimplem      | ented bit, read a | as '0'     |            |  |  |  |  |  |

| u = Bit is un  |                                                                    |                           | x = Bit is unknown -n/n = Value at POR and BOR/Value at all oth |                   |                   |            |            |  |  |  |  |  |

| '1' = Bit is s | -                                                                  | '0' = Bit is cle          |                                                                 |                   |                   |            |            |  |  |  |  |  |

|                |                                                                    |                           |                                                                 |                   |                   |            |            |  |  |  |  |  |

| bit 7          | I2C1RXIE:                                                          | <sup>2</sup> C1 Receive I | nterrupt Enab                                                   | le bit            |                   |            |            |  |  |  |  |  |

|                | 1 = Enable                                                         | = Enabled                 |                                                                 |                   |                   |            |            |  |  |  |  |  |

| 0 = Disabled   |                                                                    |                           |                                                                 |                   |                   |            |            |  |  |  |  |  |

| bit 6          | SPI1IE: SPI                                                        |                           |                                                                 |                   |                   |            |            |  |  |  |  |  |

|                | 1 = Enabled<br>0 = Disabled                                        |                           |                                                                 |                   |                   |            |            |  |  |  |  |  |

| bit 5          |                                                                    |                           |                                                                 |                   |                   |            |            |  |  |  |  |  |

| DIUD           | <b>SPI1TXIE:</b> SPI1 Transmit Interrupt Enable bit<br>1 = Enabled |                           |                                                                 |                   |                   |            |            |  |  |  |  |  |

|                | 0 = Disabled                                                       |                           |                                                                 |                   |                   |            |            |  |  |  |  |  |

| bit 4          | SPI1RXIE: SPI1 Receive Interrupt Enable bit                        |                           |                                                                 |                   |                   |            |            |  |  |  |  |  |

|                | 1 = Enabled                                                        |                           |                                                                 |                   |                   |            |            |  |  |  |  |  |

|                | 0 = Disabled                                                       |                           |                                                                 |                   |                   |            |            |  |  |  |  |  |

| bit 3          | DMA1AIE: DMA1 Abort Interrupt Enable bit                           |                           |                                                                 |                   |                   |            |            |  |  |  |  |  |

|                | 1 = Enabled                                                        |                           |                                                                 |                   |                   |            |            |  |  |  |  |  |

| bit 2          | 0 = Disable                                                        |                           | un Interrunt E                                                  | nabla bit         |                   |            |            |  |  |  |  |  |

|                | 1 = Enable                                                         | : DMA1 Overru<br>d        | in interrupt E                                                  |                   |                   |            |            |  |  |  |  |  |

|                | 0 = Disable                                                        |                           |                                                                 |                   |                   |            |            |  |  |  |  |  |

| bit 1          | DMA1DCN                                                            | TIE: DMA1 De              | stination Cour                                                  | nt Interrupt Enal | ble bit           |            |            |  |  |  |  |  |

|                | 1 = Enable                                                         | d                         |                                                                 |                   |                   |            |            |  |  |  |  |  |

|                | 0 = Disabled                                                       |                           |                                                                 |                   |                   |            |            |  |  |  |  |  |

| bit 0          |                                                                    |                           | irce Count Inf                                                  | terrupt Enable b  | bit               |            |            |  |  |  |  |  |

|                | 1 = Enable<br>0 = Disable                                          | 1 = Enabled               |                                                                 |                   |                   |            |            |  |  |  |  |  |

|                |                                                                    |                           |                                                                 |                   |                   |            |            |  |  |  |  |  |

# REGISTER 9-16: PIE2: PERIPHERAL INTERRUPT ENABLE REGISTER 2

## REGISTER 11-3: WDTPSL: WWDT PRESCALE SELECT LOW BYTE REGISTER (READ-ONLY)

| R-0/0            | R-0/0 | R-0/0                | R-0/0 | R-0/0                                               | R-0/0            | R-0/0    | R-0/0 |  |  |  |  |

|------------------|-------|----------------------|-------|-----------------------------------------------------|------------------|----------|-------|--|--|--|--|

| PSCNT<7:0>       |       |                      |       |                                                     |                  |          |       |  |  |  |  |

| bit 7            |       |                      |       |                                                     |                  |          | bit 0 |  |  |  |  |

|                  |       |                      |       |                                                     |                  |          |       |  |  |  |  |

| Legend:          |       |                      |       |                                                     |                  |          |       |  |  |  |  |

| R = Readable     | bit   | W = Writable bit     |       | U = Unimpler                                        | nented bit, read | 1 as '0' |       |  |  |  |  |

| u = Bit is uncha | anged | x = Bit is unknow    | n     | -n/n = Value at POR and BOR/Value at all other Rese |                  |          |       |  |  |  |  |

| '1' = Bit is set |       | '0' = Bit is cleared | b     |                                                     |                  |          |       |  |  |  |  |

## bit 7-0 **PSCNT<7:0>:** Prescale Select Low Byte bits<sup>(1)</sup>

**Note 1:** The 18-bit WDT prescale value, PSCNT<17:0> includes the WDTPSL, WDTPSH and the lower bits of the WDTTMR registers. PSCNT<17:0> is intended for debug operations and should not be read during normal operation.

## REGISTER 11-4: WDTPSH: WWDT PRESCALE SELECT HIGH BYTE REGISTER (READ-ONLY)

| R-0/0       | R-0/0 | R-0/0 | R-0/0 | R-0/0 | R-0/0 | R-0/0 | R-0/0 |  |  |  |

|-------------|-------|-------|-------|-------|-------|-------|-------|--|--|--|

| PSCNT<15:8> |       |       |       |       |       |       |       |  |  |  |

| bit 7       |       |       |       |       |       |       | bit 0 |  |  |  |

|             |       |       |       |       |       |       |       |  |  |  |

| Legend:              |                      |                                                       |

|----------------------|----------------------|-------------------------------------------------------|

| R = Readable bit     | W = Writable bit     | U = Unimplemented bit, read as '0'                    |

| u = Bit is unchanged | x = Bit is unknown   | -n/n = Value at POR and BOR/Value at all other Resets |

| '1' = Bit is set     | '0' = Bit is cleared |                                                       |

## bit 7-0 **PSCNT<15:8>:** Prescale Select High Byte bits<sup>(1)</sup>

**Note 1:** The 18-bit WDT prescale value, PSCNT<17:0> includes the WDTPSL, WDTPSH and the lower bits of the WDTTMR registers. PSCNT<17:0> is intended for debug operations and should not be read during normal operation.

# 13.0 NONVOLATILE MEMORY (NVM) CONTROL

Nonvolatile Memory (NVM) is separated into two types: Program Flash Memory (PFM) and Data EEPROM Memory.

PFM, Data EEPROM, User IDs and Configuration bits can all be accessed using the REG<1:0> bits of the NVMCON1 register.

The write time is controlled by an on-chip timer. The write/erase voltages are generated by an on-chip charge pump rated to operate over the operating voltage range of the device.

NVM can be protected in two ways, by either code protection or write protection. Code protection (CP and CPD bits in Configuration Word 5L) disables access, reading and writing to both PFM and Data EEPROM Memory via external device programmers. Code protection does not affect the self-write and erase functionality. Code protection can only be reset by a device programmer performing a Bulk Erase to the device, clearing all nonvolatile memory, Configuration bits and User IDs.

Write protection prohibits self-write and erase to a portion or all of the PFM, as defined by the WRT bits of Configuration Word 4H. Write protection does not affect a device programmer's ability to read, write or erase the device.

|                                           | PC<20:0>                                         | Execution        | User Access |                               |                               |  |

|-------------------------------------------|--------------------------------------------------|------------------|-------------|-------------------------------|-------------------------------|--|

| Memory                                    | ICSP™ Addr<21:0><br>TBLPTR<21:0><br>NVMADDR<9:0> | CPU<br>Execution | REG         | TABLAT                        | NVMDAT                        |  |

| Program Flash Memory<br>(PFM)             | 00 0000h<br>•••<br>01 FFFFh                      | Read             | 10          | Read/<br>Write <sup>(1)</sup> | (3)                           |  |

| User IDs <sup>(2)</sup>                   | 20 0000h<br>•••<br>20 000Fh                      | No Access        | x1          | Read/<br>Write                | (3)                           |  |

| Reserved                                  | 20 0010h<br>2F FFFFh                             | No Access        |             | (3)                           |                               |  |

| Configuration                             | 30 0000h<br>•••<br>30 0009h                      | No Access        | x1          | Read/<br>Write <sup>(1)</sup> | (3)                           |  |

| Reserved                                  | 30 000Ah<br>30 FFFFh                             | No Access        | (3)         |                               |                               |  |

| User Data Memory<br>(Data EEPROM)         | 31 0000h<br>•••<br>31 03FFh                      | No Access        | 00          | (3)                           | Read/<br>Write <sup>(1)</sup> |  |

| Reserved                                  | 31 0400h<br>3E FFFFh                             | No Access        |             | (3)                           |                               |  |

| Device Information Area<br>(DIA)          | 3F 0000h<br>•••<br>3F 003Fh                      | No Access        | xl          | Read                          | (3)                           |  |

| Reserved                                  | 3F 0040h<br>3F FF09h                             | No Access        |             | (3)                           |                               |  |

| Device Configuration Information<br>(DCI) | 3F FF00h<br>•••<br>3F FF09h                      | No Access        | x1          | Read                          | (3)                           |  |

| Reserved                                  | 3F FF0Ah<br>3F FFFBh                             | No Access        | _(3)        |                               |                               |  |

| Revision ID/<br>Device ID                 | 3F FFFCh<br>•••<br>3F FFFFh                      | No Access        | x1          | Read                          | (3)                           |  |

# TABLE 13-1: NVM ORGANIZATION AND ACCESS INFORMATION

Note 1: Subject to Memory Write Protection settings.

2: User IDs are eight words ONLY. There is no code protection, table read protection or write protection implemented for this region.

**3:** Reads as '0', writes clear the WR bit and WRERR bit is set.

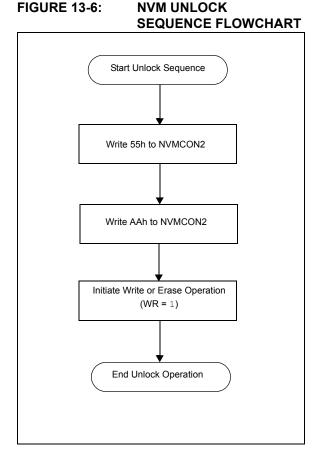

## 13.1.4 NVM UNLOCK SEQUENCE

The unlock sequence is a mechanism that protects the NVM from unintended self-write programming or erasing. The sequence must be executed and completed without interruption to successfully complete any of the following operations:

- PFM Row Erase

- Write of PFM write latches to PFM memory

- Write of PFM write latches to User IDs

- Write to Data EEPROM Memory

- Write to Configuration Words

The unlock sequence consists of the following steps and must be completed in order:

- Write 55h to NVMCON2

- Write AAh to NMVCON2

- · Set the WR bit of NVMCON1

Once the WR bit is set, the processor will stall internal operations until the operation is complete and then resume with the next instruction.

Since the unlock sequence must not be interrupted, global interrupts should be disabled prior to the unlock sequence and re-enabled after the unlock sequence is completed.

|                |                              | -    |                                                       |

|----------------|------------------------------|------|-------------------------------------------------------|

| BCF            | INTCON0,GIE                  | ;    | Recommended so sequence is not interrupted            |

| BANKSEL        | NVMCON1                      |      |                                                       |

| BSF            | NVMCON1,WREN                 | ;    | Enable write/erase                                    |

| MOVLW          | 55h                          | ;    | Load 55h                                              |

| MOVWF          | NVMCON2                      | ;    | Step 1: Load 55h into NVMCON2                         |

| MOVLW          | AAh                          | ;    | Step 2: Load W with AAh                               |

| MOVWF          | NVMCON2                      | ;    | Step 3: Load AAh into NVMCON2                         |

| BSF            | INTCON1,WR                   | ;    | Step 4: Set WR bit to begin write/erase               |

| BSF            | INTCON0,GIE                  | ;    | Re-enable interrupts                                  |

| Note 1: Sequen | ce begins when NVMCON2 is wr | itte | en; steps 1-4 must occur in the cycle-accurate order  |

|                | 0                            |      | rupted by an interrupt or a debugger Halt, the action |

|                | take place.                  |      |                                                       |

2: Opcodes shown are illustrative; any instruction that has the indicated effect may be used.

## EXAMPLE 13-2: NVM UNLOCK SEQUENCE

# 16.0 I/O PORTS

The PIC18(L)F26/27/45/46/47/55/56/57K42 devices have six I/O ports, allocated as shown in Table 16-1.

## TABLE 16-1: PORT ALLOCATION TABLE FOR PIC18(L)F26/27/45/46/47/ 55/56/57K42 DEVICES

| Device         | PORTA | PORTB | PORTC | PORTD | PORTE        | PORTF |

|----------------|-------|-------|-------|-------|--------------|-------|

| PIC18(L)F26K42 | •     | •     | •     |       | <b>.</b> (1) |       |

| PIC18(L)F27K42 | •     | •     | •     |       | <b>.</b> (1) |       |

| PIC18(L)F45K42 | •     | •     | •     | •     | •(2)         |       |

| PIC18(L)F46K42 | •     | •     | •     | •     | •(2)         |       |

| PIC18(L)F47K42 | •     | •     | •     | •     | •(2)         |       |

| PIC18(L)F55K42 | •     | •     | •     | •     | •(2)         | •     |

| PIC18(L)F56K42 | •     | •     | •     | •     | •(2)         | •     |

| PIC18(L)F57K42 | •     | •     | •     | •     | •(2)         | •     |

Note 1: Pin RE3 only.

2: Pins RE0, RE1, RE2 and RE3 only.

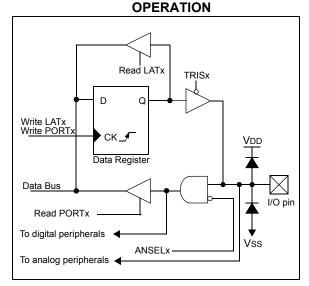

Each port has ten registers to control the operation. These registers are:

- PORTx registers (reads the levels on the pins of the device)

- LATx registers (output latch)

- TRISx registers (data direction)

- ANSELx registers (analog select)

- WPUx registers (weak pull-up)

- INLVLx (input level control)

- SLRCONx registers (slew rate control)

- ODCONx registers (open-drain control)

Most port pins share functions with device peripherals, both analog and digital. In general, when a peripheral is enabled on a port pin, that pin cannot be used as a general purpose output; however, the pin can still be read.

The Data Latch (LATx registers) is useful for read-modify-write operations on the value that the I/O pins are driving.

A write operation to the LATx register has the same effect as a write to the corresponding PORTx register. A read of the LATx register reads of the values held in the I/O PORT latches, while a read of the PORTx register reads the actual I/O pin value.

Ports that support analog inputs have an associated ANSELx register. When an ANSELx bit is set, the digital input buffer associated with that bit is disabled.

Disabling the input buffer prevents analog signal levels on the pin between a logic high and low from causing excessive current in the logic input circuitry. A simplified model of a generic I/O port, without the interfaces to other peripherals, is shown in Figure 16-1.

# FIGURE 16-1: GENERIC I/O PORT

# 16.1 I/O Priorities

Each pin defaults to the PORT data latch after Reset. Other functions are selected with the peripheral pin select logic. See Section 17.0 "Peripheral Pin Select (PPS) Module" for more information.

Analog input functions, such as ADC and comparator inputs, are not shown in the peripheral pin select lists. These inputs are active when the I/O pin is set for Analog mode using the ANSELx register. Digital output functions may continue to control the pin when it is in Analog mode.

Analog outputs, when enabled, take priority over digital outputs and force the digital output driver into a high-impedance state.

The pin function priorities are as follows:

- 1. Configuration bits

- 2. Analog outputs (disable the input buffers)

- 3. Analog inputs

- 4. Port inputs and outputs from PPS

# 16.2 PORTx Registers

In this section, the generic names such as PORTx, LATx, TRISx, etc. can be associated with PORTA, PORTB, and PORTC. The functionality of PORTE is different compared to other ports and is explained in a separate section.

| Name  | Bit 7  | Bit 6  | Bit 5  | Bit 4  | Bit 3                 | Bit 2  | Bit 1  | Bit 0  |

|-------|--------|--------|--------|--------|-----------------------|--------|--------|--------|

| IOCAP | IOCAP7 | IOCAP6 | IOCAP5 | IOCAP4 | IOCAP3                | IOCAP2 | IOCAP1 | IOCAP0 |

| IOCAN | IOCAN7 | IOCAN6 | IOCAN5 | IOCAN4 | IOCAN3                | IOCAN2 | IOCAN1 | IOCAN0 |

| IOCAF | IOCAF7 | IOCAF6 | IOCAF5 | IOCAF4 | IOCAF3                | IOCAF2 | IOCAF1 | IOCAF0 |

| IOCBP | IOCBP7 | IOCBP6 | IOCBP5 | IOCBP4 | IOCBP3                | IOCBP2 | IOCBP1 | IOCBP0 |

| IOCBN | IOCBN7 | IOCBN6 | IOCBN5 | IOCBN4 | IOCBN3                | IOCBN2 | IOCBN1 | IOCBN0 |

| IOCBF | IOCBF7 | IOCBF6 | IOCBF5 | IOCBF4 | IOCBF3                | IOCBF2 | IOCBF1 | IOCBF0 |

| IOCCP | IOCCP7 | IOCCP6 | IOCCP5 | IOCCP4 | IOCCP3                | IOCCP2 | IOCCP1 | IOCCP0 |

| IOCCN | IOCCN7 | IOCCN6 | IOCCN5 | IOCCN4 | IOCCN3                | IOCCN2 | IOCCN1 | IOCCN0 |

| IOCCF | IOCCF7 | IOCCF6 | IOCCF5 | IOCCF4 | IOCCF3                | IOCCF2 | IOCCF1 | IOCCF0 |

| IOCEP | —      | _      | _      | _      | IOCEP3 <sup>(1)</sup> | _      | —      | —      |

| IOCEN | —      | —      | _      | —      | IOCEN3 <sup>(1)</sup> |        | —      |        |

| IOCEF |        | _      | _      |        | IOCEF3 <sup>(1)</sup> | _      | _      |        |

## TABLE 18-1: IOC REGISTERS

Note 1: If MCLRE = 1 or LVP = 1, RE3 port functionality is disabled and IOC on RE3 is not available.

### TABLE 18-2: SUMMARY OF REGISTERS ASSOCIATED WITH INTERRUPT-ON-CHANGE

| Name  | Bit 7  | Bit 6  | Bit 5  | Bit 4  | Bit 3  | Bit 2  | Bit 1  | Bit 0  | Register<br>on Page |

|-------|--------|--------|--------|--------|--------|--------|--------|--------|---------------------|

| IOCxF | IOCxF7 | IOCxF6 | IOCxF5 | IOCxF4 | IOCxF3 | IOCxF2 | IOCxF1 | IOCxF0 | 287                 |

| IOCxN | IOCxN7 | IOCxN6 | IOCxN5 | IOCxN4 | IOCxN3 | IOCxN2 | IOCxN1 | IOCxN0 | 287                 |

| IOCxP | IOCxP7 | IOCxP6 | IOCxP5 | IOCxP4 | IOCxP3 | IOCxP2 | IOCxP1 | IOCxP0 | 287                 |

Legend: — = unimplemented location, read as '0'. Shaded cells are not used by interrupt-on-change.

| REGISTER      | 21-2: IXGC                                          | UN: HMER                                                          | X GATE CO                        | NIROL REGIS                                                                       | IER                                |                  |       |

|---------------|-----------------------------------------------------|-------------------------------------------------------------------|----------------------------------|-----------------------------------------------------------------------------------|------------------------------------|------------------|-------|

| R/W-0/u       | R/W-0/u                                             | R/W-0/u                                                           | R/W-0/u                          | R/W-0/u                                                                           | R-x                                | U-0              | U-0   |

| GE            | GPOL                                                | GTM                                                               | GSPM                             | GGO/DONE                                                                          | GVAL                               | _                | _     |

| bit 7         |                                                     |                                                                   |                                  |                                                                                   |                                    |                  | bit 0 |

|               |                                                     |                                                                   |                                  |                                                                                   |                                    |                  |       |

| Legend:       |                                                     |                                                                   |                                  |                                                                                   |                                    |                  |       |

| R = Readable  | e bit                                               | W = Writable                                                      | bit                              | U = Unimpleme                                                                     | nted bit, read as                  | s 'O'            |       |

| -n = Value at | POR                                                 | '1' = Bit is se                                                   | t                                | '0' = Bit is cleare                                                               | ed                                 | x = Bit is unkno | own   |

| bit 7         | If TMRxON =   1 = Timerx   0 = Timerx   If TMRxON = | counting is co<br>is always cour                                  | ntrolled by th                   | e Timerx gate fur                                                                 | nction                             |                  |       |

| bit 6         | 1 = Timerx                                          |                                                                   | -high (Timerx                    | counts when gat                                                                   |                                    |                  |       |

| bit 5         | 1 = Timerx<br>0 = Timerx                            | Gate Toggle I<br>Gate Toggle m<br>Gate Toggle m<br>Flip Flop Togg | node is enabl<br>node is disabl  | ed and Toggle flip                                                                | p-flop is cleared                  |                  |       |

| bit 4         | 1 = Timerx                                          | rx Gate Single<br>Gate Single P<br>Gate Single P                  | ulse mode is                     | enabled and is co                                                                 | ontrolling Timer                   | gate)            |       |

| bit 3         | 1 = Timerx<br>0 = Timerx                            | Gate Single P<br>Gate Single P                                    | ulse Acquisiti<br>ulse Acquisiti | Acquisition Status<br>on is ready, waitii<br>on has completed<br>(GSPM is cleared | ng for an edge<br>d or has not bee | n started.       |       |

| bit 2         | Indicates the                                       | rx Gate Currer<br>current state o<br>y Timerx Gate                | of the Timerx                    | gate that could b<br>RxGE)                                                        | e provided to TN                   | MRxH:TMRxL       |       |

| bit 1-0       | Unimpleme                                           | nted: Read as                                                     | ʻ0 <b>'</b>                      |                                                                                   |                                    |                  |       |

|               |                                                     |                                                                   |                                  |                                                                                   |                                    |                  |       |

## REGISTER 21-2: TxGCON: TIMERx GATE CONTROL REGISTER

## REGISTER 28-5: NCO1ACCU: NCO1 ACCUMULATOR REGISTER – UPPER BYTE<sup>(1)</sup>

| U-0   | U-0 | U-0 | U-0 | R/W-0/0 | R/W-0/0 | R/W-0/0 | R/W-0/0 |

|-------|-----|-----|-----|---------|---------|---------|---------|

| _     | —   | _   | —   |         | ACC<    | 19:16>  |         |

| bit 7 |     |     |     |         |         |         | bit 0   |

| Legend:              |                      |                                                       |

|----------------------|----------------------|-------------------------------------------------------|

| R = Readable bit     | W = Writable bit     | U = Unimplemented bit, read as '0'                    |

| u = Bit is unchanged | x = Bit is unknown   | -n/n = Value at POR and BOR/Value at all other Resets |

| '1' = Bit is set     | '0' = Bit is cleared |                                                       |

### bit 7-4 Unimplemented: Read as '0'

### bit 3-0 ACC<19:16>: NCO1 Accumulator, Upper Byte

**Note 1:** The accumulator spans registers NCO1ACCU:NCO1ACCH: NCO1ACCL. The 24 bits are reserved but not all are used. This register updates in real time, asynchronously to the CPU; there is no provision to guarantee atomic access to this 24-bit space using an 8-bit bus. Writing to this register while the module is operating will produce undefined results.

# **REGISTER 28-6:** NCO1INCL: NCO1 INCREMENT REGISTER – LOW BYTE<sup>(1,2)</sup>

| R/W-0/0 | R/W-1/1 |

|---------|---------|---------|---------|---------|---------|---------|---------|

|         |         |         | INC<    | <7:0>   |         |         |         |

| bit 7   |         |         |         |         |         |         | bit 0   |

|         |         |         |         |         |         |         |         |

| Legend:              |                      |                                                       |

|----------------------|----------------------|-------------------------------------------------------|

| R = Readable bit     | W = Writable bit     | U = Unimplemented bit, read as '0'                    |

| u = Bit is unchanged | x = Bit is unknown   | -n/n = Value at POR and BOR/Value at all other Resets |

| '1' = Bit is set     | '0' = Bit is cleared |                                                       |

bit 7-0 INC<7:0>: NCO1 Increment, Low Byte

Note 1: The logical increment spans NCO1INCU:NCO1INCH:NCO1INCL.

2: NCO1INC is double-buffered as INCBUF; INCBUF is updated on the next falling edge of NCOCLK after writing to NCO1INCL; NCO1INCU and NCO1INCH should be written prior to writing NCO1INCL.

## **REGISTER 28-7:** NCO1INCH: NCO1 INCREMENT REGISTER – HIGH BYTE<sup>(1)</sup>

| R/W-0/0 |

|---------|---------|---------|---------|---------|---------|---------|---------|

|         |         |         | INC<    | 15:8>   |         |         |         |

| bit 7   |         |         |         |         |         |         | bit 0   |

|         |         |         |         |         |         |         |         |

| Legend:              |                      |                                                       |

|----------------------|----------------------|-------------------------------------------------------|

| R = Readable bit     | W = Writable bit     | U = Unimplemented bit, read as '0'                    |

| u = Bit is unchanged | x = Bit is unknown   | -n/n = Value at POR and BOR/Value at all other Resets |

| '1' = Bit is set     | '0' = Bit is cleared |                                                       |

## bit 7-0 INC<15:8>: NCO1 Increment, High Byte

Note 1: The logical increment spans NCO1INCU:NCO1INCH:NCO1INCL.

# REGISTER 33-5: I2CxBTO: I<sup>2</sup>C BUS TIMEOUT SELECTION REGISTER

| U-0   | U-0 | U-0 | U-0 | U-0 | R/W-0/0 | R/W-0/0  | R/W-0/0 |

|-------|-----|-----|-----|-----|---------|----------|---------|

|       | —   | —   | —   | _   |         | BTO<2:0> |         |

| bit 7 |     |     |     |     |         |          | bit 0   |

| Legend:              |                      |                                                       |

|----------------------|----------------------|-------------------------------------------------------|

| R = Readable bit     | W = Writable bit     | U = Unimplemented bit, read as '0'                    |

| u = Bit is unchanged | x = Bit is unknown   | -n/n = Value at POR and BOR/Value at all other Resets |

| '1' = Bit is set     | '0' = Bit is cleared | HS = Hardware set HC = Hardware clear                 |

| bit 7-3 | Unimplemented: Read as '0' |

|---------|----------------------------|

|         |                            |

bit 2-0

Г

BTO<2:0>: I<sup>2</sup>C Bus Timeout Selection bits

| BTO<2:0> | I <sup>2</sup> Cx Bus Timeout Selection |

|----------|-----------------------------------------|

| 111      | CLC4OUT                                 |

| 110      | CLC3OUT                                 |

| 101      | CLC2OUT                                 |

| 100      | CLC1OUT                                 |

| 011      | TMR6 post scaled output                 |

| 010      | TMR4 post scaled output                 |

| 001      | TMR2 post scaled output                 |

| 000      | Reserved                                |

HS = Hardware set

HC = Hardware clear

| R/W-x/u                                 | R/W-x/u                           | R/W-x/u | R/W-x/u                                               | R/W-x/u                            | R/W-x/u | R/W-x/u | R/W-x/u |  |  |

|-----------------------------------------|-----------------------------------|---------|-------------------------------------------------------|------------------------------------|---------|---------|---------|--|--|

| ADB7                                    | ADB6                              | ADB5    | ADB4                                                  | ADB3                               | ADB2    | ADB1    | ADB0    |  |  |

| bit 7 bit 0                             |                                   |         |                                                       |                                    |         |         |         |  |  |

|                                         |                                   |         |                                                       |                                    |         |         |         |  |  |

| Legend:                                 |                                   |         |                                                       |                                    |         |         |         |  |  |

| R = Readable                            | R = Readable bit W = Writable bit |         |                                                       | U = Unimplemented bit, read as '0' |         |         |         |  |  |

| u = Bit is unchanged x = Bit is unknown |                                   |         | -n/n = Value at POR and BOR/Value at all other Resets |                                    |         |         |         |  |  |

# REGISTER 33-16: I2CxADB0: I<sup>2</sup>C ADDRESS DATA BUFFER 0 REGISTER<sup>(1)</sup>

'0' = Bit is cleared

| bit 7-0 | MODE<2:0> = 00x                                             |

|---------|-------------------------------------------------------------|

|         | ADB<7:1>: Address Data byte                                 |

|         | Received matching 7-bit slave address data                  |

|         | R/W: Read/not-Write Data bit                                |

|         | Received read/write value from 7-bit address byte           |

|         | MODE<2:0> = 01x                                             |

|         | ADB<7:0>: Address Data byte                                 |

|         | Received matching lower 8-bits of 10-bit slave address data |

|         | MODE<2:0> = 100                                             |

|         | Unused in this mode; bit state is a don't care              |

|         | MODE<2:0> = 101                                             |

|         | ADB<7:0>: Low Address Data byte                             |

|         | Low 10-bit address value copied to transmit shift register  |

|         | MODE<2:0> = 11x                                             |

|         | ADB<7:1>: Address Data byte                                 |

|         | Received matching 7-bit slave address                       |

|         | R/W: Read/not-Write Data bit                                |

|         | Received read/write value received 7-bit slave address byte |

## Note 1: This register is read only except in master, 10-bit Address mode (MODE<2:0> = 101).

' = Bit is set

'1

## 36.2 ADC Operation

## 36.2.1 STARTING A CONVERSION

To enable the ADC module, the ON bit of the ADCON0 register must be set to a '1'. A conversion may be started by any of the following:

- Software setting the GO bit of ADCON0 to '1'

- An external trigger (selected by Register 36-3)

- A continuous-mode retrigger (see section Section 36.6.8 "Continuous Sampling mode")

Note: The GO bit should not be set in the same instruction that turns on the ADC. Refer to Section 36.2.6 "ADC Conversion Procedure (Basic Mode)".

## 36.2.2 COMPLETION OF A CONVERSION

When any individual conversion is complete, the value already in ADRES is written into PREV (if ADPSIS = 1) and the new conversion results appear in ADRES. When the conversion completes, the ADC module will:

- Clear the GO bit (unless the CONT bit of ADCON0 is set)

- Set the ADIF Interrupt Flag bit

- Set the MATH bit

- Update ACC

When ADDSEN = 0 then after every conversion, or when ADDSEN = 1 then after every other conversion, the following events occur:

- ERR is calculated

- ADTIF is set if ERR calculation meets threshold comparison

Importantly, filter and threshold computations occur after the conversion itself is complete. As such, interrupt handlers responding to ADIF should check ADTIF before reading filter and threshold results.

## 36.2.3 ADC OPERATION DURING SLEEP

The ADC module can operate during Sleep. This requires the ADC clock source to be set to the FRC option. When the FRC oscillator source is selected, the ADC waits one additional instruction before starting the conversion. This allows the SLEEP instruction to be executed, which can reduce system noise during the conversion. If the ADC interrupt is enabled, the device will wake-up from Sleep when the conversion completes. If the ADC interrupt is disabled, the ADC module is turned off after the conversion completes, although the ON bit remains set.

## 36.2.4 EXTERNAL TRIGGER DURING SLEEP

If the external trigger is received during sleep while ADC clock source is set to the FRC, ADC module will perform the conversion and set the ADIF bit upon completion.

If an external trigger is received when the ADC clock source is something other than FRC, the trigger will be recorded, but the conversion will not begin until the device exits Sleep.

| U-0              | U-0                                                                                                                                                       | U-0             | R/W-0/0       | R/W-0/0          | R/W-0/0          | R/W-0/0        | R/W-0/0      |

|------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------|---------------|------------------|------------------|----------------|--------------|

| —                | —                                                                                                                                                         | —               |               |                  | ADCAP<4:0>       |                |              |

| bit 7            |                                                                                                                                                           |                 |               |                  |                  |                | bit 0        |

|                  |                                                                                                                                                           |                 |               |                  |                  |                |              |

| Legend:          |                                                                                                                                                           |                 |               |                  |                  |                |              |

| R = Readable     | bit                                                                                                                                                       | W = Writable    | bit           | U = Unimplen     | nented bit, read | as '0'         |              |

| u = Bit is uncha | anged                                                                                                                                                     | x = Bit is unkr | nown          | -n/n = Value a   | at POR and BO    | R/Value at all | other Resets |

| '1' = Bit is set | '1' = Bit is set '0' = Bit is cleare                                                                                                                      |                 |               |                  |                  |                |              |

|                  |                                                                                                                                                           |                 |               |                  |                  |                |              |

| bit 7-5          | Unimplemen                                                                                                                                                | ted: Read as '  | D'            |                  |                  |                |              |

| bit 4-0          | ADCAP<4:0><br>11111 = 31 p<br>11110 = 30 p<br>11101 = 29 p<br>•<br>•<br>•<br>•<br>•<br>•<br>•<br>•<br>•<br>•<br>•<br>•<br>•<br>•<br>•<br>•<br>•<br>•<br>• | F<br>F          | nal Sample Ca | pacitor Selectio | on bits          |                |              |

# REGISTER 36-13: ADCAP: ADC ADDITIONAL SAMPLE CAPACITOR SELECTION REGISTER

## REGISTER 36-14: ADRPT: ADC REPEAT SETTING REGISTER

|          |         |         |                         | -                               |                                 |         |  |  |  |  |  |

|----------|---------|---------|-------------------------|---------------------------------|---------------------------------|---------|--|--|--|--|--|

| R/W-0/0  | R/W-0/0 | R/W-0/0 | R/W-0/0                 | R/W-0/0                         | R/W-0/0                         | R/W-0/0 |  |  |  |  |  |

| RPT<7:0> |         |         |                         |                                 |                                 |         |  |  |  |  |  |

|          |         |         |                         |                                 |                                 | bit 0   |  |  |  |  |  |

|          |         |         |                         |                                 |                                 |         |  |  |  |  |  |

|          |         |         |                         |                                 |                                 |         |  |  |  |  |  |

| -        | -       | -       | R/W-0/0 R/W-0/0 R/W-0/0 | R/W-0/0 R/W-0/0 R/W-0/0 R/W-0/0 | R/W-0/0 R/W-0/0 R/W-0/0 R/W-0/0 |         |  |  |  |  |  |

| Ecgenia.             |                      |                                                       |

|----------------------|----------------------|-------------------------------------------------------|

| R = Readable bit     | W = Writable bit     | U = Unimplemented bit, read as '0'                    |

| u = Bit is unchanged | x = Bit is unknown   | -n/n = Value at POR and BOR/Value at all other Resets |

| '1' = Bit is set     | '0' = Bit is cleared |                                                       |

## bit 7-0 **RPT<7:0>**: ADC Repeat Threshold bits

Determines the number of times that the ADC is triggered before the threshold is checked when the computation is Low-pass Filter, Burst Average, or Average modes. See Table 36-2 for more details.

## REGISTER 36-32: ADLTHL: ADC LOWER THRESHOLD LOW BYTE REGISTER

| R/W-0/0                                                                                       | R/W-0/0                           | R/W-0/0 | R/W-0/0 | R/W-0/0                            | R/W-0/0 | R/W-0/0 | R/W-0/0 |  |  |  |  |

|-----------------------------------------------------------------------------------------------|-----------------------------------|---------|---------|------------------------------------|---------|---------|---------|--|--|--|--|

| LTH<7:0>                                                                                      |                                   |         |         |                                    |         |         |         |  |  |  |  |

| bit 7                                                                                         |                                   |         |         |                                    |         |         | bit 0   |  |  |  |  |

|                                                                                               |                                   |         |         |                                    |         |         |         |  |  |  |  |

| Legend:                                                                                       |                                   |         |         |                                    |         |         |         |  |  |  |  |

| R = Readable                                                                                  | R = Readable bit W = Writable bit |         |         | U = Unimplemented bit, read as '0' |         |         |         |  |  |  |  |

| u = Bit is unchanged x = Bit is unknown -n/n = Value at POR and BOR/Value at all other Resets |                                   |         |         |                                    |         |         |         |  |  |  |  |

bit 7-0 LTH<7:0>: ADC Lower Threshold LSB. LTH and UTH are compared with ERR to set the ADUTHR and ADLTHR bits of ADSTAT. Depending on the setting of ADTMD, an interrupt may be triggered by the results of this comparison.

## REGISTER 36-33: ADUTHH: ADC UPPER THRESHOLD HIGH BYTE REGISTER

'0' = Bit is cleared

| R/W-0/0   | R/W-0/0 | R/W-0/0       | R/W-0/0 | R/W-0/0 | R/W-0/0 | R/W-0/0 | R/W-0/0 |  |  |  |

|-----------|---------|---------------|---------|---------|---------|---------|---------|--|--|--|

| UTH<15:8> |         |               |         |         |         |         |         |  |  |  |

| bit 7     |         |               |         |         |         |         | bit 0   |  |  |  |

|           |         |               |         |         |         |         |         |  |  |  |

| Legend:   |         |               |         |         |         |         |         |  |  |  |

|           |         | 14/ 14/2010 L |         |         |         | 1 (0)   |         |  |  |  |

| Legena.              |                      |                                                       |

|----------------------|----------------------|-------------------------------------------------------|

| R = Readable bit     | W = Writable bit     | U = Unimplemented bit, read as '0'                    |

| u = Bit is unchanged | x = Bit is unknown   | -n/n = Value at POR and BOR/Value at all other Resets |

| '1' = Bit is set     | '0' = Bit is cleared |                                                       |

bit 7-0 **UTH<15:8>**: ADC Upper Threshold MSB. LTH and UTH are compared with ERR to set the ADUTHR and ADLTHR bits of ADSTAT. Depending on the setting of ADTMD, an interrupt may be triggered by the results of this comparison.

## REGISTER 36-34: ADUTHL: ADC UPPER THRESHOLD LOW BYTE REGISTER

| R/W-0/0   | R/W-0/0  | R/W-0/0 | R/W-0/0 | R/W-0/0 | R/W-0/0 | R/W-0/0 | R/W-0/0 |  |  |  |  |

|-----------|----------|---------|---------|---------|---------|---------|---------|--|--|--|--|

|           | UTH<7:0> |         |         |         |         |         |         |  |  |  |  |

| bit 7 bit |          |         |         |         |         |         |         |  |  |  |  |

| Legend:              |                      |                                                       |

|----------------------|----------------------|-------------------------------------------------------|

| R = Readable bit     | W = Writable bit     | U = Unimplemented bit, read as '0'                    |

| u = Bit is unchanged | x = Bit is unknown   | -n/n = Value at POR and BOR/Value at all other Resets |

| '1' = Bit is set     | '0' = Bit is cleared |                                                       |

bit 7-0 **UTH<7:0>**: ADC Upper Threshold LSB. LTH and UTH are compared with ERR to set the ADUTHR and ADLTHR bits of ADSTAT. Depending on the setting of ADTMD, an interrupt may be triggered by the results of this comparison.

© 2017 Microchip Technology Inc.

= Bit is set

| Address          | Name      | Bit 7       | Bit 6          | Bit 5          | Bit 4 | Bit 3 | Bit 2  | Bit 1 | Bit 0 | Register<br>on page |

|------------------|-----------|-------------|----------------|----------------|-------|-------|--------|-------|-------|---------------------|

| 3BFEh            | DMA1AIRQ  | _           |                |                |       | AIRQ  |        |       |       | 256                 |

| 3BFDh            | DMA1CON1  | EN          | SIRQEN         | DGO            | _     | _     | AIRQEN | —     | XIP   | 249                 |

| 3BFCh            | DMA1CON0  | DN          | IODE           | DSTP           | SN    | /IR   | SMC    | DDE   | SSTP  | 248                 |

| 3BFBh            | DMA1SSAU  | _           | _              |                | •     |       | SSA    |       |       | 251                 |

| 3BFAh            | DMA1SSAH  |             |                |                | SS    | SA    |        |       |       | 250                 |

| 3BF9h            | DMA1SSAL  |             |                |                | SS    | SA    |        |       |       | 250                 |

| 3BF8h            | DMA1SSZH  | _           | _              | _              | _     |       | 5      | SSZ   |       | 252                 |

| 3BF7h            | DMA1SSZL  |             |                |                | SS    | SZ    |        |       |       | 252                 |

| 3BF6h            | DMA1SPTRU | _           | _              |                |       | Ş     | SPTR   |       |       | 252                 |

| 3BF5h            | DMA1SPTRH |             |                |                | SP    | TR    |        |       |       | 251                 |

| 3BF4h            | DMA1SPTRL |             |                |                | SP    | TR    |        |       |       | 251                 |

| 3BF3h            | DMA1SCNTH | _           | _              | —              | _     |       | S      | CNT   |       | 253                 |

| 3BF2h            | DMA1SCNTL |             |                |                | SC    | NT    |        |       |       | 253                 |

| 3BF1h            | DMA1DSAH  |             |                |                | DS    | SA    |        |       |       | 254                 |

| 3BF0h            | DMA1DSAL  |             |                |                | SS    | SA    |        |       |       | 253                 |

| 3BEFh            | DMA1DSZH  | _           | _              | —              | _     |       | C      | OSZ   |       | 255                 |

| 3BEEh            | DMA1DSZL  |             |                |                | DS    | SZ    |        |       |       | 255                 |

| 3BEDh            | DMA1DPTRH |             |                |                | DP    | TR    |        |       |       | 254                 |

| 3BECh            | DMA1DPTRL |             |                |                | DP    | TR    |        |       |       | 254                 |

| 3BEBh            | DMA1DCNTH | _           | _              | _              | _     |       | D      | CNT   |       | 256                 |

| 3BEAh            | DMA1DCNTL |             |                |                | DC    | NT    |        |       |       | 255                 |

| 3BE9h            | DMA1BUF   |             | BUF            |                |       |       |        |       |       |                     |

| 3BE8h -<br>3BE0h | —         |             | Unimplemented  |                |       |       |        |       |       |                     |

| 3BDFh            | DMA2SIRQ  | _           |                |                |       | SIRQ  |        |       |       | 256                 |

| 3BDEh            | DMA2AIRQ  | _           |                |                |       | AIRQ  |        |       |       | 256                 |

| 3BDDh            | DMA2CON1  | EN          | SIRQEN         | DGO            | _     | _     | AIRQEN | _     | XIP   | 249                 |

| 3BDCh            | DMA2CON0  | DN          | IODE           | DSTP           | SN    | /IR   | SMO    | DDE   | SSTP  | 248                 |

| 3BDBh            | DMA2SSAU  | —           | _              |                |       |       | SSA    |       | 1     | 251                 |

| 3BDAh            | DMA2SSAH  |             |                |                | SS    | SA    |        |       |       | 250                 |

| 3BD9h            | DMA2SSAL  |             |                |                | SS    | SA    |        |       |       | 250                 |

| 3BD8h            | DMA2SSZH  | —           | _              | —              | _     |       | S      | SSZ   |       | 252                 |

| 3BD7h            | DMA2SSZL  |             | -1             |                | SS    | SZ    |        |       |       | 252                 |

| 3BD6h            | DMA2SPTRU | —           | _              |                |       | 5     | SPTR   |       |       | 252                 |

| 3BD5h            | DMA2SPTRH |             | -1             |                | SP    | TR    |        |       |       | 251                 |

| 3BD4h            | DMA2SPTRL |             |                |                | SP    | TR    |        |       |       | 251                 |

| 3BD3h            | DMA2SCNTH | _           | _              | _              | _     |       | S      | CNT   |       | 253                 |

| 3BD2h            | DMA2SCNTL |             |                |                | SC    | NT    |        |       |       | 253                 |

| 3BD1h            | DMA2DSAH  |             |                |                | DS    |       |        |       |       | 254                 |

| 3BD0h            | DMA2DSAL  |             |                |                | SS    | SA    |        |       |       | 253                 |

| 3BCFh            | DMA2DSZH  | _           | _              | _              |       |       | C      | OSZ   |       | 255                 |

| 3BCEh            | DMA2DSZL  |             |                |                | DS    | SZ    |        |       |       | 255                 |

| 3BCDh            | DMA2DPTRH |             |                |                | DP    |       |        |       |       | 254                 |

| 3BCCh            | DMA2DPTRL |             |                |                | DP    |       |        |       |       | 254                 |

| 3BCBh            | DMA2DCNTH | _           | _              | _              | _     |       | D      | CNT   |       | 256                 |

| 3BCAh            | DMA2DCNTL |             |                |                | DC    | NT    |        |       |       | 255                 |

| 3BC9h            | DMA2BUF   |             |                |                | BL    |       |        |       |       | 250                 |