Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Product Status             | Active                                                                      |

|----------------------------|-----------------------------------------------------------------------------|

| Core Processor             | PIC                                                                         |

| Core Size                  | 8-Bit                                                                       |

| Speed                      | 64MHz                                                                       |

| Connectivity               | I <sup>2</sup> C, LINbus, SPI, UART/USART                                   |

| Peripherals                | Brown-out Detect/Reset, DMA, HLVD, POR, PWM, WDT                            |

| Number of I/O              | 25                                                                          |

| Program Memory Size        | 64KB (32K x 16)                                                             |

| Program Memory Type        | FLASH                                                                       |

| EEPROM Size                | 1K x 8                                                                      |

| RAM Size                   | 4K x 8                                                                      |

| Voltage - Supply (Vcc/Vdd) | 1.8V ~ 3.6V                                                                 |

| Data Converters            | A/D 24x12b; D/A 1x5b                                                        |

| Oscillator Type            | Internal                                                                    |

| Operating Temperature      | -40°C ~ 125°C (TA)                                                          |

| Mounting Type              | Surface Mount                                                               |

| Package / Case             | 28-VQFN Exposed Pad                                                         |

| Supplier Device Package    | 28-QFN (6x6)                                                                |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/pic18lf26k42-e-ml |

|                            |                                                                             |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

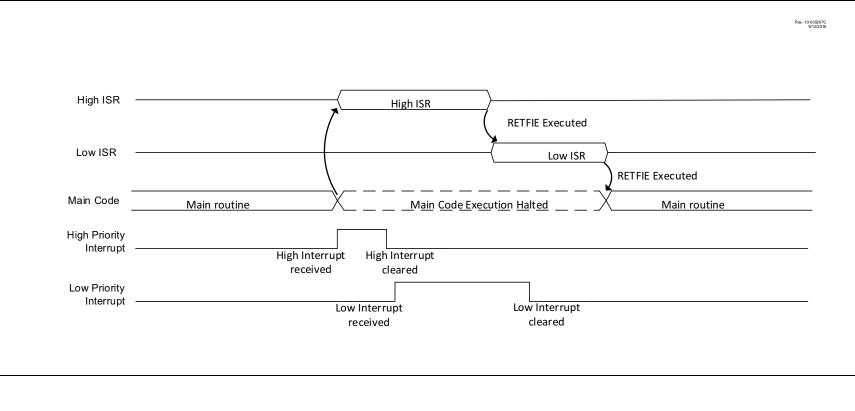

# 9.4.2 SERVING A HIGH PRIORITY INTERRUPT WHILE A LOW PRIORITY INTERRUPT PENDING

A high priority interrupt request will always take precedence over any interrupt of a lower priority. The high priority interrupt is acknowledged first, then the low-priority interrupt is acknowledged. Upon a return from the high priority ISR (by executing the RETFIE instruction), the low priority interrupt is serviced, see Figure 9-3.

If any other high priority interrupts are pending and enabled, then they are serviced before servicing the pending low priority interrupt. If no other high priority interrupt requests are active, the low priority interrupt is serviced.

# FIGURE 9-3: INTERRUPT EXECUTION: HIGH PRIORITY INTERRUPT WITH A LOW PRIORITY INTERRUPT PENDING

### FIGURE 10-2: WAKE-UP FROM SLEEP THROUGH INTERRUPT

| Q1 Q2 Q3 Q4 Q1 Q2 Q3 Q4 Q1                         | 01/02/03/04         |                    | Q3 Q4 Q1 Q2 Q3 Q4   |

|----------------------------------------------------|---------------------|--------------------|---------------------|

|                                                    |                     |                    |                     |

|                                                    | Tost <sup>(3)</sup> | ·/                 |                     |

| Interrupt flag                                     | / Interrupt Late    | ncy <sup>(4)</sup> |                     |

| GIE bit<br>(INTCON reg.)<br>Sleet                  |                     | <u>.</u>           |                     |

| Instruction Flow<br>PC X PC X PC + 1 X             | PC + 2 X PC + 2     | PC+2 00            | 004h X 0005h        |

| Instruction { Inst(PC) = Sleep Inst(PC + 1)        | Inst(PC + 2)        | Inst               | (0004h) Inst(0005h) |

| Instruction { Inst(PC - 1) Sleep                   | Inst(PC + 1)        | Forced NOP Force   | ed NOP Inst(0004h)  |

| Note 1: External clock. High, Medium, Low mode ass | umed.               |                    |                     |

2: CLKOUT is shown here for timing reference.

3: TOST = 1024 TOSC. This delay does not apply to EC and INTOSC Oscillator modes.

4: GIE = 1 assumed. In this case after wake-up, the processor calls the ISR at 0004h. If GIE = 0, execution will continue in-line.

#### 10.2.3 LOW-POWER SLEEP MODE

The PIC18F26/27/45/46/47/55/56/57K42 device family contains an internal Low Dropout (LDO) voltage regulator, which allows the device I/O pins to operate at voltages up to 5.5V while the internal device logic operates at a lower voltage. The LDO and its associated reference circuitry must remain active when the device is in Sleep mode.

The PIC18F26/27/45/46/47/55/56/57K42 devices allow the user to optimize the operating current in Sleep, depending on the application requirements.

Low-Power Sleep mode can be selected by setting the VREGPM bit of the VREGCON register.

### 10.2.3.1 Sleep Current vs. Wake-up Time

In the default operating mode, the LDO and reference circuitry remain in the normal configuration while in Sleep. The device is able to exit Sleep mode quickly since all circuits remain active. In Low-Power Sleep mode, when waking-up from Sleep, an extra delay time is required for these circuits to return to the normal configuration and stabilize.

The Low-Power Sleep mode is beneficial for applications that stay in Sleep mode for long periods of time. The Normal mode is beneficial for applications that need to wake from Sleep quickly and frequently.

# 11.7 Register Definitions: Windowed Watchdog Timer Control

### REGISTER 11-1: WDTCON0: WATCHDOG TIMER CONTROL REGISTER 0

| U-0           | U-0                     | R/W <sup>(3)</sup> -q/q <sup>(2)</sup>         | R/W <sup>(3)</sup> -q/q <sup>(2)</sup> | R/W <sup>(3)</sup> -q/q <sup>(2)</sup> | R/W <sup>(3)</sup> -q/q <sup>(2)</sup> | R/W <sup>(3)</sup> -q/q <sup>(2)</sup> | R/W-0/0      |

|---------------|-------------------------|------------------------------------------------|----------------------------------------|----------------------------------------|----------------------------------------|----------------------------------------|--------------|

| _             | -                       |                                                |                                        | PS<4:0>                                |                                        |                                        | SEN          |

| oit 7         |                         |                                                |                                        |                                        |                                        |                                        | bit          |

|               |                         |                                                |                                        |                                        |                                        |                                        |              |

| _egend:       |                         |                                                |                                        |                                        |                                        |                                        |              |

| R = Reada     | ble bit                 | W = Writable bit                               |                                        | U = Unimpleme                          | nted bit, read as                      | '0'                                    |              |

| u = Bit is ur | nchanged                | x = Bit is unknow                              | vn                                     | -n/n = Value at                        | POR and BOR/V                          | alue at all other Re                   | esets        |

| 1' = Bit is s | et                      | '0' = Bit is cleare                            | d                                      | q = Value deper                        | nds on condition                       |                                        |              |

| oit 7-6       | Unimplem                | nented: Read as '0'                            |                                        |                                        |                                        |                                        |              |

| bit 5-1       | •                       | Watchdog Timer Preso                           | ala Salaat hita(                       | )                                      |                                        |                                        |              |

| JIL J- I      |                         | = Prescale Rate                                | ale Select bits.                       |                                        |                                        |                                        |              |

|               |                         | Reserved. Results in                           | minimum inten                          | al (1·32)                              |                                        |                                        |              |

|               | •                       |                                                |                                        | ar(1.52)                               |                                        |                                        |              |

|               | •                       |                                                |                                        |                                        |                                        |                                        |              |

|               | •                       |                                                |                                        |                                        |                                        |                                        |              |

|               | 10011 =                 | Reserved. Results in                           | minimum interv                         | al (1:32)                              |                                        |                                        |              |

|               | 10010 =                 | 1:8388608 (2 <sup>23</sup> ) (Inte             | erval 256s nomir                       | nal)                                   |                                        |                                        |              |

|               |                         | 1:4194304 (2 <sup>22</sup> ) (Inte             |                                        |                                        |                                        |                                        |              |

|               |                         | 1:2097152 (2 <sup>21</sup> ) (Inte             |                                        |                                        |                                        |                                        |              |

|               | 01111 =                 | 1:1048576 (2 <sup>20</sup> ) (Inte             | erval 32s nomina                       | al)                                    |                                        |                                        |              |

|               | 01110 =                 | 1:524288 (219) (Inter                          | val 16s nominal                        | )                                      |                                        |                                        |              |

|               | 01101 =                 | 1:262144 (2 <sup>18</sup> ) (Inter             | val 8s nominal)                        |                                        |                                        |                                        |              |

|               | 01100 =                 | 1:131072 (2 <sup>17</sup> ) (Inter             | val 4s nominal)                        |                                        |                                        |                                        |              |

|               |                         | 1:65536 (Interval 2s                           | , ,                                    | value)                                 |                                        |                                        |              |

|               |                         | 1:32768 (Interval 1s                           | ,                                      |                                        |                                        |                                        |              |

|               |                         | 1:16384 (Interval 512                          |                                        |                                        |                                        |                                        |              |

|               |                         | 1:8192 (Interval 256                           | ,                                      |                                        |                                        |                                        |              |

|               |                         | 1:4096 (Interval 128                           |                                        |                                        |                                        |                                        |              |

|               |                         | 1:2048 (Interval 64 m<br>1:1024 (Interval 32 m |                                        |                                        |                                        |                                        |              |

|               |                         | 1:512 (Interval 16 ms                          | ,                                      |                                        |                                        |                                        |              |

|               |                         | 1:256 (Interval 8 ms                           | ,                                      |                                        |                                        |                                        |              |

|               |                         | 1:128 (Interval 4 ms                           | ,                                      |                                        |                                        |                                        |              |

|               |                         | 1:64 (Interval 2 ms n                          | ,                                      |                                        |                                        |                                        |              |

|               |                         | 1:32 (Interval 1 ms ne                         |                                        |                                        |                                        |                                        |              |

| oit O         |                         | ware Enable/Disable fo                         | or Watchdog Tin                        | ner bit                                |                                        |                                        |              |

|               | If WDTE<                |                                                |                                        |                                        |                                        |                                        |              |

|               | This bit is             |                                                |                                        |                                        |                                        |                                        |              |

|               | If WDTE<                |                                                |                                        |                                        |                                        |                                        |              |

|               |                         | is turned on                                   |                                        |                                        |                                        |                                        |              |

|               |                         | is turned off                                  |                                        |                                        |                                        |                                        |              |

|               | If WDTE<<br>This bit is |                                                |                                        |                                        |                                        |                                        |              |

|               |                         | -                                              | hand a Oddi                            |                                        |                                        |                                        |              |

| Note 1:<br>2: |                         | vroximate. WDT time is<br>PS <4:0> in CONFIG3L |                                        |                                        | <4.0> is 01011                         | Otherwise the Po                       | set value of |

| 2:            |                         | ual to WDTCPS<4:0>                             |                                        | Cesel value of PS                      | <b>-4.0/ 15</b> UIUII.                 | ouierwise, lite Re                     | Set value of |

| 3:            | •                       | PS <4:0> in CONFIG3L                           |                                        | bits are read-on                       | lv                                     |                                        |              |

| 4:            |                         | DT is configured to rur                        |                                        |                                        | -                                      | o is allowed to upo                    | lorgo o Dooo |

4: When the WWDT is configured to run using the SOSC as a clock source and the device is allowed to undergo a Reset, as triggered by a WDT time-out, the SOSC would also undergo a Reset. That means the SOSC will execute its start-up sequence which requires 1024 SOSC clock counts before it is made available for peripherals to use. So for example, if the WDT is set for a 1 ms time-out and the device is allowed to undergo a WDT Reset, then the actual WDT Reset period will be: WDT\_PERIOD = (1/(SOSC\_FREQUENCY) \* 1024) + 1 ms.

# PIC18(L)F26/27/45/46/47/55/56/57K42

| U-0                               | U-0      | U-0                            | U-0        | R/W-0/0        | R/W-0/0          | R/W-0/0          | R/W-0/0      |

|-----------------------------------|----------|--------------------------------|------------|----------------|------------------|------------------|--------------|

| _                                 | _        | _                              | _          |                | TSEL             | <3:0>            |              |

| bit 7                             | •        | ŀ                              |            | ·              |                  |                  | bit (        |

| d.                                |          |                                |            |                |                  |                  |              |

| Legend:                           |          |                                |            |                |                  |                  |              |

| R = Readable bit W = Writable bit |          |                                |            | U = Unimpler   | mented bit, read | l as '0'         |              |

| u = Bit is un                     | ichanged | x = Bit is unkr                | nown       | -n/n = Value   | at POR and BO    | R/Value at all c | other Resets |

| '1' = Bit is s                    | et       | '0' = Bit is clea              | ared       |                |                  |                  |              |

|                                   |          |                                |            |                |                  |                  |              |

| bit 7-4                           | Unimple  | mented: Read as '              | ) <b>'</b> |                |                  |                  |              |

| bit 3-0                           | •        | :0>: Scanner Data T            |            | Selection bits |                  |                  |              |

|                                   |          | Reserved                       | nggoi mpar |                |                  |                  |              |

|                                   | •        |                                |            |                |                  |                  |              |

|                                   | •        |                                |            |                |                  |                  |              |

|                                   | •        |                                |            |                |                  |                  |              |

|                                   |          |                                |            |                |                  |                  |              |

|                                   |          | Reserved                       |            |                |                  |                  |              |

|                                   |          | SMT1_output                    |            |                |                  |                  |              |

|                                   |          | TMR6_postscaled<br>TMR5 output |            |                |                  |                  |              |

|                                   |          | TMR4 postscaled                |            |                |                  |                  |              |

|                                   |          | TMR3 output                    |            |                |                  |                  |              |

|                                   | 0100 =   | TMR2 postscaled                |            |                |                  |                  |              |

|                                   | 0011 =   | TMR1 output                    |            |                |                  |                  |              |

|                                   |          | TMR0_output                    |            |                |                  |                  |              |

|                                   | 0001 =   | CLKREF_output                  |            |                |                  |                  |              |

|                                   | 0000 =   | LFINTOSC                       |            |                |                  |                  |              |

#### **REGISTER 14-18: SCANTRIG: SCAN TRIGGER SELECTION REGISTER**

### 20.3 Programmable Prescaler

A software programmable prescaler is available for exclusive use with Timer0. There are 16 prescaler options for Timer0 ranging in powers of two from 1:1 to 1:32768. The prescaler values are selected using the CKPS<3:0> bits of the T0CON1 register.

The prescaler is not directly readable or writable. Clearing the prescaler register can be done by writing to the TMR0L register or to the T0CON0/T0CON1 register or by any Reset.

# 20.4 Programmable Postscaler

A software programmable postscaler (output divider) is available for exclusive use with Timer0. There are 16 postscaler options for Timer0 ranging from 1:1 to 1:16. The postscaler values are selected using the OUTPS bits of the T0CON0 register.

The postscaler is not directly readable or writable. Clearing the postscaler register can be done by writing to the TMR0L register or to the T0CON0/T0CON1 register or by any Reset.

# 20.5 Operation During Sleep

When operating synchronously, Timer0 will halt. When operating asynchronously, Timer0 will continue to increment and wake the device from Sleep (if Timer0 interrupts are enabled) provided that the input clock source is active.

# 20.6 Timer0 Interrupts

The Timer0 interrupt flag bit (TMR0IF) is set when either of the following conditions occur:

- 8-bit TMR0L matches the TMR0H value

- 16-bit TMR0 rolls over from 'FFFFh'

When the postscaler bits (OUTPS) are set to 1:1 operation (no division), the T0IF flag bit will be set with every TMR0 match or rollover. In general, the TMR0IF flag bit will be set every OUTPS +1 matches or rollovers.

If Timer0 interrupts are enabled (TMR0IE bit of the PIE3 register = '1'), the CPU will be interrupted and the device may wake from Sleep (see Section 20.2 "Clock Source Selection" for more details).

# 20.7 Timer0 Output

The Timer0 output can be routed to any I/O pin via the RxyPPS output selection register (see Section **17.0 "Peripheral Pin Select (PPS) Module**" for additional information). The Timer0 output can also be used by other peripherals, such as the auto-conversion trigger of the Analog-to-Digital Converter. Finally, the Timer0 output can be monitored through software via the Timer0 output bit (OUT) of the T0CON0 register (Register 20-1).

TMR0\_out will be a pulse of one postscaled clock period when a match occurs between TMR0L and PR0 (Period register for TMR0) in 8-bit mode, or when TMR0 rolls over in 16-bit mode. The Timer0 output is a 50% duty cycle that toggles on each TMR0\_out rising clock edge.

# 22.5 Operation Examples

Unless otherwise specified, the following notes apply to the following timing diagrams:

- Both the prescaler and postscaler are set to 1:1 (both the CKPS and OUTPS bits in the T2CON register are cleared).

- The diagrams illustrate any clock except FOSC/4 and show clock-sync delays of at least two full cycles for both ON and T2TMR\_ers. When using FOSC/4, the clocksync delay is at least one instruction period for T2TMR\_ers; ON applies in the next instruction period.

- ON and T2TMR\_ers are somewhat generalized, and clock-sync delays may produce results that are slightly different than illustrated.

- The PWM Duty Cycle and PWM output are illustrated assuming that the timer is used for the PWM function of the CCP module as described in Section 23.0 "Capture/ Compare/PWM Module" and Section 24.0 "Pulse-Width Modulation (PWM)". The signals are not a part of the T2TMR module.

| R/W-x/x |

|---------|---------|---------|---------|---------|---------|---------|---------|

|         |         |         | RH<     | :7:0>   |         |         |         |

| bit 7   |         |         |         |         |         |         | bit 0   |

|         |         |         |         |         |         |         |         |

| Lanandı |         |         |         |         |         |         |         |

# REGISTER 23-5: CCPRxH: CCPx REGISTER HIGH BYTE

| Legend:           |                  |                       |                    |

|-------------------|------------------|-----------------------|--------------------|

| R = Readable bit  | W = Writable bit | U = Unimplemented bit | , read as '0'      |

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared  | x = Bit is unknown |

| bit 7-0 | MODE = Capture Mode:                       |

|---------|--------------------------------------------|

|         | RH<7:0>: MSB of captured TMR1 value        |

|         | MODE = Compare Mode:                       |

|         | RH<7:0>: MSB compared to TMR1 value        |

|         | MODE = PWM Mode && FMT = 0:                |

|         | RH<7:2>: Not used                          |

|         | RH<1:0>: CCPW<9:8> - Pulse-Width MS 2 bits |

|         | MODE = PWM Mode && FMT = 1:                |

|         | RH<7:0>: CCPW<9:2> - Pulse-Width MS 8 bits |

#### TABLE 23-4: SUMMARY OF REGISTERS ASSOCIATED WITH CCPx

| Name     | Bit 7                   | Bit 6 | Bit 5 | Bit 4 | Bit 3 | Bit 2  | Bit 1 | Bit 0  | Register<br>on Page |

|----------|-------------------------|-------|-------|-------|-------|--------|-------|--------|---------------------|

| CCPxCON  | EN                      | —     | OUT   | FMT   |       | 350    |       |        |                     |

| CCPxCAP  |                         |       |       |       |       |        | CTS<  | :1:0>  | 352                 |

| CCPRxL   | CCPRx<7:0>              |       |       |       |       |        |       | 352    |                     |

| CCPRxH   | CCPRx<15:8>             |       |       |       |       |        |       | 353    |                     |

| CCPTMRS0 | C4TSEL<1:0> C3TSEL<1:0> |       |       |       | C2TSE | L<1:0> | C1TSE | L<1:0> | 351                 |

**Legend:** — = Unimplemented location, read as '0'. Shaded cells are not used by the CCP module.

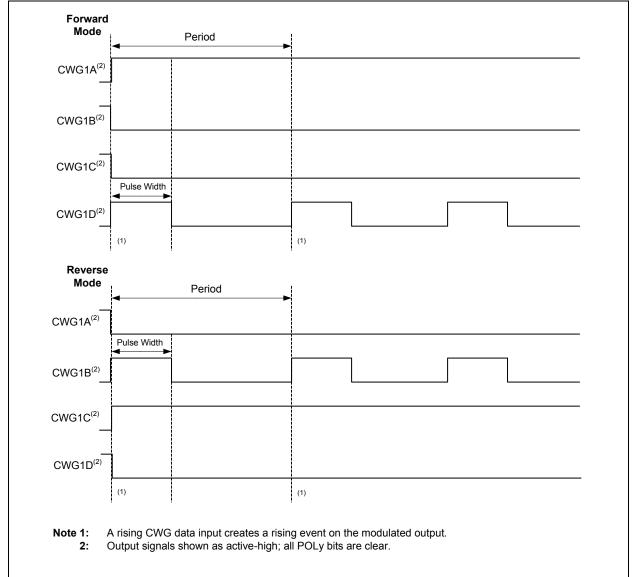

In Forward Full-Bridge mode (MODE<2:0> = 010), CWGxA is driven to its active state, CWGxB and CWGxC are driven to their inactive state, and CWGxD is modulated by the input signal, as shown in Figure 26-7.

In Reverse Full-Bridge mode (MODE<2:0> = 011), CWGxC is driven to its active state, CWGxA and CWGxD are driven to their inactive states, and CWGxB is modulated by the input signal, as shown in Figure 26-7. In Full-Bridge mode, the dead-band period is used when there is a switch from forward to reverse or viceversa. This dead-band control is described in Section 26.6 "Dead-Band Control", with additional details in Section 26.7 "Rising Edge and Reverse Dead Band" and Section 26.8 "Falling Edge and Forward Dead Band". Steering modes are not used with either of the Full-Bridge modes. The mode selection may be toggled between forward and reverse toggling the MODE<0> bit of the CWGxCON0 while keeping MODE<2:1> static, without disabling the CWG module.

# PIC18(L)F26/27/45/46/47/55/56/57K42

#### **REGISTER 26-3:** CWGxCLK: CWGx CLOCK INPUT SELECTION REGISTER

| CS<br>bit 7bit 0 | U-0   | U-0 | U-0 | U-0 | U-0 | U-0 | U-0 | R/W-0/0 |

|------------------|-------|-----|-----|-----|-----|-----|-----|---------|

| bit 7 bit 0      | —     | —   | _   | —   | —   | —   | _   | CS      |

|                  | bit 7 |     |     |     |     |     |     | bit 0   |

| Legend:              |                      |                                                       |

|----------------------|----------------------|-------------------------------------------------------|

| R = Readable bit     | W = Writable bit     | U = Unimplemented bit, read as '0'                    |

| u = Bit is unchanged | x = Bit is unknown   | -n/n = Value at POR and BOR/Value at all other Resets |

| '1' = Bit is set     | '0' = Bit is cleared | q = Value depends on condition                        |

#### bit 7-1 Unimplemented: Read as '0'

bit 0

CS: CWG Clock Source Selection bits

| CS | CWG1                    | CWG2                    | CWG3                    |

|----|-------------------------|-------------------------|-------------------------|

| 1  | HFINTOSC <sup>(1)</sup> | HFINTOSC <sup>(1)</sup> | HFINTOSC <sup>(1)</sup> |

| 0  | Fosc                    | Fosc                    | Fosc                    |

Note 1: HFINTOSC remains operating during Sleep.

# 29.0 ZERO-CROSS DETECTION (ZCD) MODULE

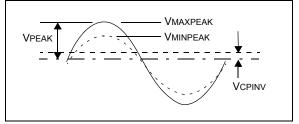

The ZCD module detects when an A/C signal crosses through the ground potential. The actual zero-crossing threshold is the zero-crossing reference voltage, VCPINV, which is typically 0.75V above ground.

The connection to the signal to be detected is through a series current-limiting resistor. The module applies a current source or sink to the ZCD pin to maintain a constant voltage on the pin, thereby preventing the pin voltage from forward biasing the ESD protection diodes. When the applied voltage is greater than the reference voltage, the module sinks current. When the applied voltage is less than the reference voltage, the module sources current. The current source and sink action keeps the pin voltage constant over the full range of the applied voltage. The ZCD module is shown in the simplified block diagram Figure 29-2.

The ZCD module is useful when monitoring an A/C waveform for, but not limited to, the following purposes:

- A/C period measurement

- Accurate long term time measurement

- Dimmer phase delayed drive

- Low EMI cycle switching

# 29.1 External Resistor Selection

The ZCD module requires a current-limiting resistor in series with the external voltage source. The impedance and rating of this resistor depends on the external source peak voltage. Select a resistor value that will drop all of the peak voltage when the current through the resistor is nominally 300  $\mu$ A. Refer to Equation 29-1 and Figure 29-1. Make sure that the ZCD I/O pin internal weak pull-up is disabled so it does not interfere with the current source and sink.

#### EQUATION 29-1: EXTERNAL RESISTOR

$$RSERIES = \frac{V_{PEAK}}{3 \times 10^{-4}}$$

FIGURE 29-1: EXTERNA

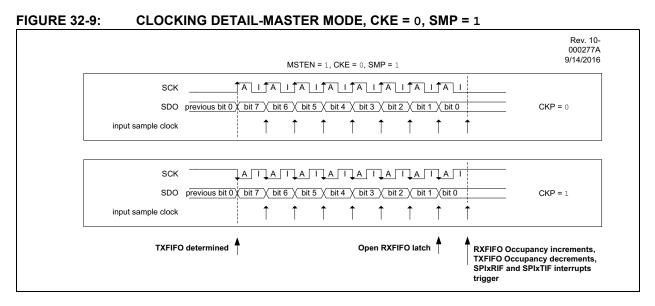

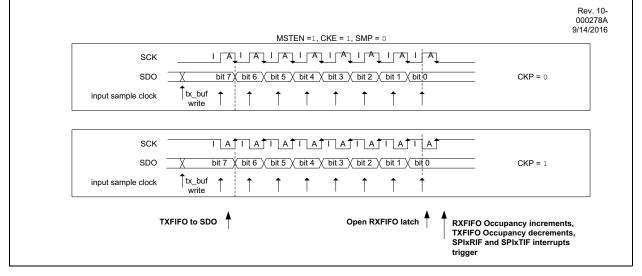

FIGURE 32-10: CLOCKING DETAIL-MASTER MODE, CKE = 1, SMP = 0

### 32.5.6.3 SCK Start-Up Delay

When starting an SPI data exchange, the master device sets the SS output (either through hardware or software) and then triggers the module to send data. These data triggers are synchronized to the clock selected by the SPIxCLK register before the first SCK pulse appears, usually requiring one or two clocks of the selected clock.

The SPI module includes synchronization delays on SCK generation specifically designed to ensure that the Slave Select output timing is correct, without requiring precision software timing loops.

When the value of the SPIxBAUD register is a small number (indicating higher SCK frequencies), the synchronization delay can be relatively long between setting SS and the first SCK. With larger values of SPIxBAUD (indicating lower SCK frequencies), this delay is much smaller and the first SCK can appear relatively quickly after SS is set.

By default, the SPI module inserts a ½ baud delay (half of the period of the clock selected by the SPIxCLK register) before the first SCK pulse. This allows for systems with a high SPIxBAUD value to have extra setup time before the first clock. Setting the FST bit in SPIxCON1 removes this additional delay, allowing systems with low SPIxBAUD values (and thus, long synchronization delays) to forego this unnecessary extra delay.

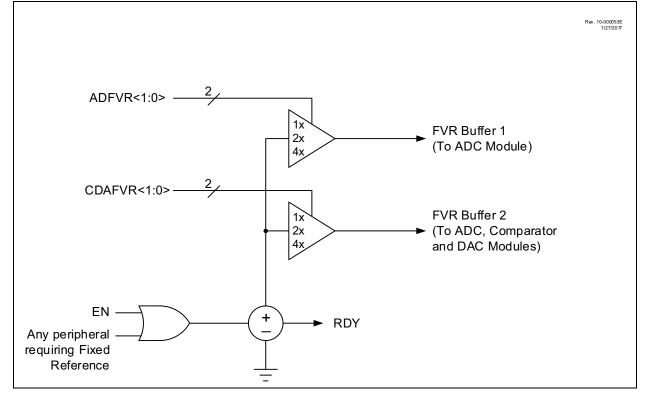

# 34.0 FIXED VOLTAGE REFERENCE (FVR)

The Fixed Voltage Reference, or FVR, is a stable voltage reference, independent of VDD, with 1.024V, 2.048V or 4.096V selectable output levels. The output of the FVR can be configured to supply a reference voltage to the following:

- ADC input channel

- ADC positive reference

- Comparator input

- Digital-to-Analog Converter (DAC)

The FVR can be enabled by setting the EN bit of the FVRCON register.

Note: Fixed Voltage Reference output cannot exceed VDD.

# 34.1 Independent Gain Amplifiers

The output of the FVR, which is connected to the ADC, Comparators, and DAC, is routed through two independent programmable gain amplifiers. Each amplifier can be programmed for a gain of 1x, 2x or 4x, to produce the three possible voltage levels. The ADFVR<1:0> bits of the FVRCON register are used to enable and configure the gain amplifier settings for the reference supplied to the ADC module. Reference Section 36.0 "Analog-to-Digital Converter with Computation (ADC2) Module" for additional information.

The CDAFVR<1:0> bits of the FVRCON register are used to enable and configure the gain amplifier settings for the reference supplied to the DAC and comparator module. Reference Section 37.0 "5-Bit Digital-to-Analog Converter (DAC) Module" and Section 38.0 "Comparator Module" for additional information.

# 34.2 FVR Stabilization Period

When the Fixed Voltage Reference module is enabled, it requires time for the reference and amplifier circuits to stabilize. Once the circuits stabilize and are ready for use, the RDY bit of the FVRCON register will be set.

# FIGURE 34-1: VOLTAGE REFERENCE BLOCK DIAGRAM

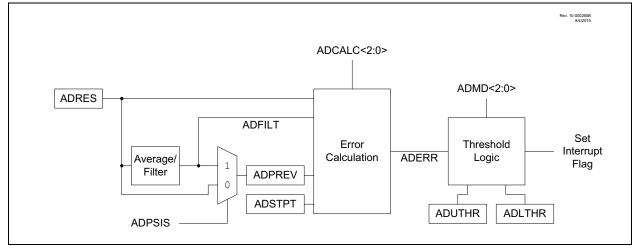

### 36.6 Computation Operation

The ADC module hardware is equipped with post conversion computation features. These features provide data post-processing functions that can be operated on the ADC conversion result, including digital filtering/averaging and threshold comparison functions.

FIGURE 36-10: COMPUTATIONAL FEATURES SIMPLIFIED BLOCK DIAGRAM

The operation of the ADC computational features is controlled by ADMD <2:0> bits in the ADCON2 register.

The module can be operated in one of five modes:

• **Basic**: In this mode, ADC conversion occurs on single (ADDSEN = 0) or double (ADDSEN = 1) samples. ADIF is set after all the conversion are complete.

• Accumulate: With each trigger, the ADC conversion result is added to accumulator and CNT increments. ADIF is set after each conversion. ADTIF is set according to the calculation mode.

• Average: With each trigger, the ADC conversion result is added to the accumulator. When the RPT number of samples have been accumulated, a threshold test is performed. Upon the next trigger, the accumulator is cleared. For the subsequent tests, additional RPT samples are required to be accumulated.

• **Burst Average**: At the trigger, the accumulator is cleared. The ADC conversion results are then collected repetitively until RPT samples are accumulated and finally the threshold is tested.

• Low-Pass Filter (LPF): With each trigger, the ADC conversion result is sent through a filter. When RPT samples have occurred, a threshold test is performed. Every trigger after that the ADC conversion result is sent through the filter and another threshold test is performed.

The five modes are summarized in Table 36-2 below.

# 38.7 Comparator Response Time

The comparator output is indeterminate for a period of time after the change of an input source or the selection of a new reference voltage. This period is referred to as the response time. The response time of the comparator differs from the settling time of the voltage reference. Therefore, both of these times must be considered when determining the total response time to a comparator input change. See the Comparator and Voltage Reference Specifications in Table 44-17 and Table 44-19 for more details.

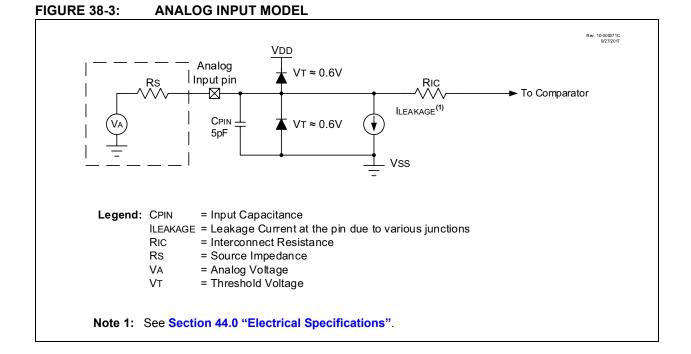

### 38.8 Analog Input Connection Considerations

A simplified circuit for an analog input is shown in Figure 38-3. Since the analog input pins share their connection with a digital input, they have reverse biased ESD protection diodes to VDD and VSS. The analog input, therefore, must be between VSS and VDD. If the input voltage deviates from this range by more than 0.6V in either direction, one of the diodes is forward biased and a latch-up may occur.

The maximum source impedance for analog sources is mentioned in Parameter AD08 in Table 44-15. Also, any external component connected to an analog input pin, such as a capacitor or a Zener diode, should have very little leakage current to minimize inaccuracies introduced.

- Note 1: When reading a PORT register, all pins configured as analog inputs will read as a '0'. Pins configured as digital inputs will convert as an analog input, according to the input specification.

- 2: Analog levels on any pin defined as a digital input, may cause the input buffer to consume more current than is specified.

© 2017 Microchip Technology Inc.

# **39.6 Operation During Sleep**

When enabled, the HLVD circuitry continues to operate during Sleep. If the device voltage crosses the trip point, the HLVDIF bit will be set and the device will wake up from Sleep. Device execution will continue from the interrupt vector address if interrupts have been globally enabled.

# 39.7 Operation During Idle and Doze Modes

In both Idle and Doze modes, the module is active and events are generated if peripheral is enabled.

# **39.8 Operation During Freeze**

When in Freeze mode, no new event or interrupt can be generated. The state of the LRDY bit is frozen.

Register reads and writes through the CPU interface are allowed.

# **39.9 Effects of a Reset**

A device Reset forces all registers to their Reset state. This forces the HLVD module to be turned off.

# PIC18(L)F26/27/45/46/47/55/56/57K42

| Address          | Name       | Bit 7 | Bit 6 | Bit 5 | Bit 4       | Bit 3          | Bit 2      | Bit 1 | Bit 0     | Register<br>on page |

|------------------|------------|-------|-------|-------|-------------|----------------|------------|-------|-----------|---------------------|

| 3BC8h -<br>3AEBh | —          |       |       |       | Unimple     | mented         |            |       |           |                     |

| 3AEAh            | U2CTSPPS   | —     | —     | —     |             | U2CTSPPS       |            |       |           |                     |

| 3AE8h            | U2RXPPS    | _     | —     | —     |             | U2RXPPS        |            |       |           |                     |

| 3AE7h            | U1CTSPPS   | _     | —     | —     |             | U1CTSPPS       |            |       |           |                     |

| 3AE5h            | U1RXPPS    | _     | —     | _     |             |                | U1RXPPS    |       |           | 277                 |

| 3AE4h            | I2C2SDAPPS | —     | —     | —     |             |                | I2C2SDAPPS | S     |           | 277                 |

| 3AE3h            | I2C2SCLPPS | _     | —     | _     |             |                | I2C2SCLPPS | 3     |           | 277                 |

| 3AE2h            | I2C1SDAPPS | _     | —     | _     |             |                | I2C1SDAPPS | S     |           | 277                 |

| 3AE1h            | I2C1SCLPPS | —     | —     | —     |             |                | I2C1SCLPPS | 3     |           | 277                 |

| 3AE0h            | SPI1SSPPS  | _     | —     | _     |             |                | SPI1SSPPS  | ;     |           | 277                 |

| 3ADFh            | SPI1SDIPPS | _     | —     | _     |             |                | SPI1SDIPPS | 6     |           | 277                 |

| 3ADEh            | SPI1SCKPPS | —     | —     | —     |             | SPI1SCKPPS     |            |       |           |                     |

| 3ADDh            | ADACTPPS   | —     | —     | —     |             | ADACTPPS       |            |       |           |                     |

| 3ADCh            | CLCIN3PPS  | —     | —     | —     |             | CLCIN3PPS      |            |       |           |                     |

| 3ADBh            | CLCIN2PPS  | —     | —     | —     |             | CLCIN2PPS      |            |       |           |                     |

| 3ADAh            | CLCIN1PPS  | —     | —     | —     |             | CLCIN1PPS      |            |       |           |                     |

| 3AD9h            | CLCIN0PPS  | —     | —     | —     |             |                | CLCIN0PPS  | ;     |           | 277<br>277          |

| 3AD8h            | MD1SRCPPS  | —     | —     | —     |             | MD1SRCPPS      |            |       |           |                     |

| 3AD7h            | MD1CARHPPS | —     | —     | —     |             | MD1CARHPPS     |            |       |           |                     |

| 3AD6h            | MD1CARLPPS | —     | —     | —     | MD1CARLPPS  |                |            |       |           | 277                 |

| 3AD5h            | CWG3INPPS  | —     | —     | —     | CWG3INPPS   |                |            |       |           | 277                 |

| 3AD4h            | CWG2INPPS  | —     | —     | —     | CWG2INPPS   |                |            |       |           | 277                 |

| 3AD3h            | CWG1INPPS  | _     | —     | —     | CWG1INPPS   |                |            |       |           | 277                 |

| 3AD2h            | SMT1SIGPPS | _     | —     | —     | SMT1SIGPPS  |                |            |       |           | 277                 |

| 3AD1h            | SMT1WINPPS |       | _     | —     | SMT1WINPPS  |                |            |       |           | 277                 |

| 3AD0h            | CCP4PPS    |       | _     | —     | CCP4PPS     |                |            |       |           | 277                 |

| 3ACFh            | CCP3PPS    |       | _     | —     | CCP3PPS     |                |            |       |           | 277                 |

| 3ACEh            | CCP2PPS    | —     | —     | —     | CCP2PPS     |                |            |       |           | 277                 |

| 3ACDh            | CCP1PPS    |       | _     | —     | CCP1PPS     |                |            |       |           | 277                 |

| 3ACCh            | T6INPPS    |       | _     | —     | T6INPPS     |                |            |       |           | 277                 |

| 3ACBh            | T4INPPS    | _     | _     | —     | T4INPPS     |                |            |       |           | 277                 |

| 3ACAh            | T2INPPS    |       | _     | —     | T2INPPS     |                |            |       |           | 277                 |

| 3AC9h            | T5GPPS     |       |       | —     | T5GPPS      |                |            |       |           | 277                 |

| 3AC8h            | T5CLKIPPS  |       |       | —     | T5CLKIPPS   |                |            |       |           | 277                 |

| 3AC7h            | T3GPPS     |       |       | —     | T3GPPS      |                |            |       |           | 277                 |

| 3AC6h            | T3CLKIPPS  | _     | _     | —     | T3CLKIPPS   |                |            |       |           | 277                 |

| 3AC5h            | T1GPPS     | _     | —     | —     | TIGPPS      |                |            |       |           | 277                 |

| 3AC4h            | T1CLKIPPS  | _     | —     | —     | T1CLKIPPS   |                |            |       |           | 277                 |

| 3AC3h            | TOCLKIPPS  | _     | —     | —     | TOCLKIPPS   |                |            |       |           | 277                 |

| 3AC2h            | INT2PPS    | _     | —     | —     | INT2PPS     |                |            |       |           | 277                 |

| 3AC1h            | INT1PPS    | _     | —     | —     | INTIPPS     |                |            |       |           | 277                 |

| 3AC0h            | INT0PPS    | _     | _     | —     |             |                | INT0PPS    |       |           | 277                 |

| 3ABFh            | PPSLOCK    | _     | —     | —     | —           | _              | —          | _     | PPSLOCKED | 283                 |

| 3ABEh            | —          |       |       |       | Reserved, m | aintain as '0' |            |       |           |                     |

| 3ABDh -<br>3A9Ah | —          |       |       |       | Unimple     | mented         |            |       |           |                     |

| 3A99h            | —          |       |       |       | Reserved, m | aintain as '0' |            |       |           |                     |

#### **TABLE 42-1**: REGISTER FILE SUMMARY FOR PIC18(L)F26/27/45/46/47/55/56/57K42 DEVICES

Note

Unimplemented in LF devices. 1:

Unimplemented in PIC18(L)F26/27K42. 2:

Unimplemented on PIC18(L)F26/27/45/46/47K42 devices. 3:

Unimplemented in PIC18(L)F45/55K42. 4:

### TABLE 44-5:POWER-DOWN CURRENT (IPD)

| PIC18LF27/47/57K42 |           |                                           |      |                                                                       | Standard Operating Conditions (unless otherwise stated) |                               |       |               |                        |  |  |

|--------------------|-----------|-------------------------------------------|------|-----------------------------------------------------------------------|---------------------------------------------------------|-------------------------------|-------|---------------|------------------------|--|--|

| PIC18F27/47/57K42  |           |                                           |      | Standard Operating Conditions (unless otherwise stated)<br>VREGPM = 1 |                                                         |                               |       |               |                        |  |  |

| Param.             | Symbol    | Device Characteristics                    | Min. | Typ.†                                                                 | Max.                                                    | Max.                          | Units |               | Conditions             |  |  |

| No.                | Cymbol    | Device onaracteristics                    |      | ויקעי                                                                 | +85°C                                                   | +125°C                        |       | VDD           | Note                   |  |  |

| D200               | IPD       | IPD Base                                  | —    | 0.07                                                                  | 2                                                       | 10.5                          | μΑ    | 3.0V          | $\langle \rangle$      |  |  |

| D200               | IPD       | IPD Base                                  | _    | 0.4                                                                   | 4                                                       | 12                            | μA    | 3.0V          |                        |  |  |

| D200A              |           |                                           | —    | 20                                                                    | 38                                                      | 42                            | μΑ    | 3.0V          | VREGPM = 0             |  |  |

| D201               | IPD_WDT   | Low-Frequency Internal Oscillator/<br>WDT | —    | 0.9                                                                   | 3.2                                                     | 11.2                          | μΑ    | 3.0V          | $\frown$               |  |  |

| D201               | IPD_WDT   | Low-Frequency Internal Oscillator/<br>WDT | —    | 1.1                                                                   | 3.2                                                     | 13                            | μΑ    | 3.0           | $\sum$                 |  |  |

| D202               | IPD_SOSC  | Secondary Oscillator (SOSC)               |      | 0.75                                                                  | 6                                                       | 14                            | μΑ    | 3.QV          | ⊻P mode                |  |  |

| D202               | IPD_SOSC  | Secondary Oscillator (SOSC)               |      | 1.0                                                                   | 7                                                       | 15                            | μΑ    | 3.0V          | LP mode                |  |  |

| D203               | IPD_FVR   | FVR                                       |      | 45                                                                    | 74                                                      | 75                            | /ttA_ | 3.0V          | FVRCON = 0x81 or 0x84  |  |  |

| D203               | IPD_FVR   | FVR                                       | _    | 40                                                                    | 70                                                      | 76                            | μA    | 3.0∀          | EVRCON = 0x81 or 0x84  |  |  |

| D204               | IPD_BOR   | Brown-out Reset (BOR)                     |      | 9.4                                                                   | 14                                                      | 18                            | \µA\  | 3.0V          | $\checkmark$           |  |  |

| D204               | IPD_BOR   | Brown-out Reset (BOR)                     | _    | 9.4                                                                   | 15                                                      | <del>18</del>                 | μA    | 3.0V          |                        |  |  |

| D205               | IPD_LPBOR | Low-Power Brown-out Reset (LPBOR)         | —    | 0.2                                                                   | 3 ·                                                     | $\langle \mathcal{M} \rangle$ | μΑ    | 3.0V          |                        |  |  |

| D206               | IPD_HLVD  | High/Low Voltage Detect (HLVD)            | —    | 9.5                                                                   | 14.8                                                    | 18                            | μΑ `  | <b>√</b> 3.0∨ |                        |  |  |

| D206               | IPD_HLVD  | High/Low Voltage Detect (HLVD)            | _    | 9.7                                                                   | 14.2                                                    | -17-                          | μA    | 3.0V          |                        |  |  |

| D207               | IPD_ADCA  | ADC - Converting                          |      | .01                                                                   | X                                                       | 10.5                          | μŔ    | 3.0V          |                        |  |  |

| D207               | IPD_ADCA  | ADC - Converting                          | —    | 0(1                                                                   | 4                                                       | 12                            | μΑ    | 3.0V          | ADC not converting (4) |  |  |

| D208               | IPD_CMP   | Comparator                                | —    | 33                                                                    | 49                                                      | 50                            | μΑ    | 3.0V          |                        |  |  |

| D208               | IPD_CMP   | Comparator                                |      | 30                                                                    | 49                                                      | 50                            | μΑ    | 3.0V          |                        |  |  |

† Data in "Typ." column is at 3.0V, 25°C unless otherwise stated. These parameters are for design guidance only and are not tested.

Note 1: The peripheral current is the sum of the base /DD and the additional current consumed when this peripheral is enabled. The peripheral ∆ current can be determined by subtracting the base lop or IPD current from this limit. Max. values should be used when calculating total current consumption.

2: The power-down current in Sleep mode does not depend on the oscillator type. Power-down current is measured with the part in Sleep mode with all I/O pins in high-impedance state and tied to Vss.

3: All peripheral currents listed are on a per-peripheral basis if more than one instance of a peripheral is available.

4: ADC clock source is FRC.

# TABLE 44-15: ANALOG-TO-DIGITAL CONVERTER (ADC) ACCURACY SPECIFICATIONS<sup>(1,2)</sup>:

| <mark>Operating Conditions (unless otherwise stated)</mark><br>VDD = 3.0V, TA = 25°C, TAD = 1μs |        |                                                   |        |      |        |       |                                   |

|-------------------------------------------------------------------------------------------------|--------|---------------------------------------------------|--------|------|--------|-------|-----------------------------------|

| Param<br>No.                                                                                    | Sym.   | Characteristic                                    | Min.   | Тур† | Max.   | Units | Conditions                        |

| AD01                                                                                            | NR     | Resolution                                        | —      | _    | 12     | bit   | $\wedge$                          |

| AD02                                                                                            | EIL    | Integral Error                                    | _      | ±0.1 | ±2.0   | LSb   | ADCREF+ = 3.0V, ADCREF- $\neq 0$  |

| AD03                                                                                            | Edl    | Differential Error                                | _      | ±0.1 | ±1.0   | LSb   | ADCREF+ = 3.0V, ADCREF-= $\rho V$ |

| AD04                                                                                            | EOFF   | Offset Error                                      | _      | 0.5  | 6.0    | LSb   | ADCREF+ = 3.0V, ADCREF-= 0V       |

| AD05                                                                                            | Egn    | Gain Error                                        | _      | ±0.2 | ±6.0   | LSb   | ADCREF+ = 3.0V, ADCREF-= 0V       |

| AD06                                                                                            | VADREF | ADC Reference Voltage<br>(ADREF+ - ADREF-)        | 1.8    |      | Vdd    | V     |                                   |

| AD07                                                                                            | VAIN   | Full-Scale Range                                  | ADREF- | _    | ADREF+ | V     |                                   |

| AD08                                                                                            | Zain   | Recommended Impedance of<br>Analog Voltage Source | —      | 1    | —      | kΩ    |                                   |

| AD09                                                                                            | Rvref  | ADC Voltage Reference Ladder<br>Impedance         | —      | 50   | —      | kΩ    | Note 3                            |

\* These parameters are characterized but not tested.

+ Data in "Typ" column is at 3.0V, 25°C unless otherwise stated. These parameters are for design guidance only and are not tested.

Note 1: Total Absolute Error is the sum of the offset, gain and integral non-linearity (INL) errors.

2: The ADC conversion result never decreases with an increase in the input and has no missing codes.

3: This is the impedance seen by the VREF pads when the external reference pads are selected.

# PIC18(L)F26/27/45/46/47/55/56/57K42

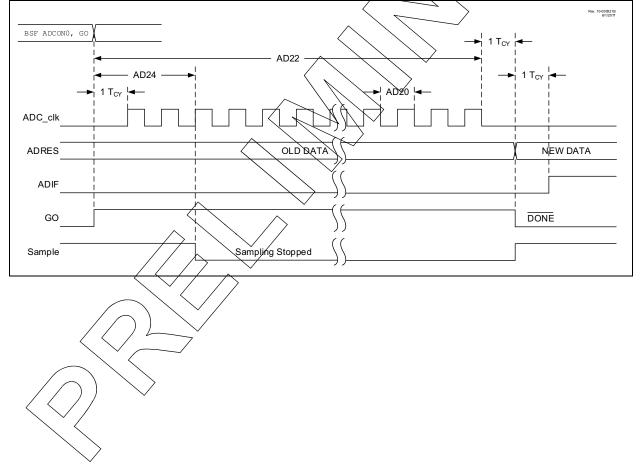

#### TABLE 44-16: ANALOG-TO-DIGITAL CONVERTER (ADC) CONVERSION TIMING SPECIFICATIONS

| Standard Operating Conditions (unless otherwise stated) |      |                                              |      |                |      |       |                                                            |  |

|---------------------------------------------------------|------|----------------------------------------------|------|----------------|------|-------|------------------------------------------------------------|--|

| Param<br>No.                                            | Sym. | Characteristic                               | Min. | Тур†           | Max. | Units | Conditions                                                 |  |

| AD20                                                    | Tip  | ADC Clock Period                             | 1    | _              | 9    | μS    | Using Fosc as the ADC clock<br>source ADCS = 1             |  |

| AD21                                                    | TAD  |                                              |      | 2              |      | μS    | Using FRC as the ADC clock<br>source ADCS = 0              |  |

| AD22                                                    | TCNV | Conversion Time <sup>(1)</sup>               |      | 14 Tad + 2 Tcy |      | _     | Using Fosc as the ADC clock source ADCS = 1                |  |

|                                                         |      |                                              |      | 16 Tad + 2 Tcy |      | _     | Using FRc as the ADC clock<br>source ADCS = &              |  |

| AD24                                                    | THCD | Sample and Hold Capacitor<br>Disconnect Time |      | 2 Tad + 1 Tcy  | I    | _     | Using Fose as the ADC clock<br>source ADCS = 1             |  |

|                                                         |      |                                              | _    | 3 Tad + 2 Tcy  |      |       | Using FRC as the AD <del>C clo</del> ck<br>source ADCS = 0 |  |

\* These parameters are characterized but not tested.

† Data in "Typ" column is at 3.0V, 25°C unless otherwise stated. These parameters are for design guidance only and are not tested.

**Note 1:** Does not apply for the ADCRC oscillator.

# FIGURE 44-10: ADC CONVERSION TIMING (ADC CLOCK Fose-BASED)

#### 40-Lead Ultra Thin Plastic Quad Flat, No Lead Package (MV) – 5x5x0.5 mm Body [UQFN]

**Note:** For the most current package drawings, please see the Microchip Packaging Specification located at http://www.microchip.com/packaging

|                        | Units |           |      | MILLIMETERS |  |  |  |  |

|------------------------|-------|-----------|------|-------------|--|--|--|--|

| Dimen                  | MIN   | NOM       | MAX  |             |  |  |  |  |

| Number of Pins         | N     | 40        |      |             |  |  |  |  |

| Pitch                  | е     | 0.40 BSC  |      |             |  |  |  |  |

| Overall Height         | A     | 0.45      | 0.50 | 0.55        |  |  |  |  |

| Standoff               | A1    | 0.00      | 0.02 | 0.05        |  |  |  |  |

| Contact Thickness      | A3    | 0.127 REF |      |             |  |  |  |  |

| Overall Width          | E     | 5.00 BSC  |      |             |  |  |  |  |

| Exposed Pad Width      | E2    | 3.60      | 3.70 | 3.80        |  |  |  |  |

| Overall Length         | D     | 5.00 BSC  |      |             |  |  |  |  |

| Exposed Pad Length     | D2    | 3.60      | 3.70 | 3.80        |  |  |  |  |

| Contact Width          | b     | 0.15      | 0.20 | 0.25        |  |  |  |  |

| Contact Length         | L     | 0.30      | 0.40 | 0.50        |  |  |  |  |

| Contact-to-Exposed Pad | K     | 0.20      | -    | -           |  |  |  |  |

Notes:

1. Pin 1 visual index feature may vary, but must be located within the hatched area.

2. Package is saw singulated.

3. Dimensioning and tolerancing per ASME Y14.5M.

BSC: Basic Dimension. Theoretically exact value shown without tolerances.

REF: Reference Dimension, usually without tolerance, for information purposes only.

Microchip Technology Drawing C04-156A Sheet 2 of 2