Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

#### Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Details                    |                                                                             |

|----------------------------|-----------------------------------------------------------------------------|

| Product Status             | Active                                                                      |

| Core Processor             | PIC                                                                         |

| Core Size                  | 8-Bit                                                                       |

| Speed                      | 64MHz                                                                       |

| Connectivity               | I <sup>2</sup> C, LINbus, SPI, UART/USART                                   |

| Peripherals                | Brown-out Detect/Reset, DMA, HLVD, POR, PWM, WDT                            |

| Number of I/O              | 25                                                                          |

| Program Memory Size        | 64KB (64K x 8)                                                              |

| Program Memory Type        | FLASH                                                                       |

| EEPROM Size                | 1K x 8                                                                      |

| RAM Size                   | 4K x 8                                                                      |

| Voltage - Supply (Vcc/Vdd) | 1.8V ~ 3.6V                                                                 |

| Data Converters            | A/D 24x12b; D/A 1x5b                                                        |

| Oscillator Type            | Internal                                                                    |

| Operating Temperature      | -40°C ~ 125°C (TA)                                                          |

| Mounting Type              | Surface Mount                                                               |

| Package / Case             | 28-UQFN Exposed Pad                                                         |

| Supplier Device Package    | 28-UQFN (6x6)                                                               |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/pic18lf26k42-e-mx |

|                            |                                                                             |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

#### 7.4 Fail-Safe Clock Monitor

The Fail-Safe Clock Monitor (FSCM) allows the device to continue operating should the external oscillator fail. The FSCM is enabled by setting the FCMEN bit in the Configuration Words. The FSCM is applicable to all external Oscillator modes (LP, XT, HS, ECL/M/H and Secondary Oscillator).

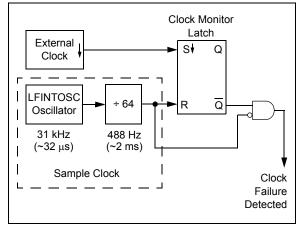

FIGURE 7-9: FSCM BLOCK DIAGRAM

#### 7.4.1 FAIL-SAFE DETECTION

The FSCM module detects a failed oscillator by comparing the external oscillator to the FSCM sample clock. The sample clock is generated by dividing the LFINTOSC by 64. See Figure 7-9. Inside the fail detector block is a latch. The external clock sets the latch on each falling edge of the external clock. The sample clock clears the latch on each rising edge of the sample clock. A failure is detected when an entire half-cycle of the sample clock elapses before the external clock goes low.

#### 7.4.2 FAIL-SAFE OPERATION

When the external clock fails, the FSCM overwrites the COSC bits to select HFINTOSC (3'b110). The frequency of HFINTOSC would be determined by the previous state of the FRQ bits and the NDIV/CDIV bits. The bit flag OSFIF of the respective PIR register is set. Setting this flag will generate an interrupt if the OSFIE bit of the respective PIR register is also set. The device firmware can then take steps to mitigate the problems that may arise from a failed clock. The system clock will continue to be sourced from the internal clock source until the device firmware successfully restarts the external oscillator and switches back to external operation, by writing to the NOSC and NDIV bits of the OSCCON1 register.

#### 7.4.3 FAIL-SAFE CONDITION CLEARING

The Fail-Safe condition is cleared after a Reset, executing a SLEEP instruction or changing the NOSC and NDIV bits of the OSCCON1 register. When switching to the external oscillator or PLL, the OST is restarted. While the OST is running, the device continues to operate from the INTOSC selected in OSCCON1. When the OST times out, the Fail-Safe condition is cleared after successfully switching to the external clock source. The OSCFIF bit should be cleared prior to switching to the external clock source. If the Fail-Safe condition still exists, the OSCFIF flag will again become set by hardware.

#### 9.6 Returning from Interrupt Service Routine (ISR)

The "Return from Interrupt" instruction (RETFIE) is used to mark the end of an ISR.

When RETFIE 1 instruction is executed, the PC is loaded with the saved PC value from the top of the PC stack. Saved context is also restored with the execution of this instruction. Thus, execution returns to the previous state of operation that existed before the interrupt occurred.

When RETFIE 0 instruction is executed, the saved context is not restored back to the registers.

#### 9.7 Interrupt Latency

By assigning each interrupt with a vector address/ number (MVECEN = 1), scanning of all interrupts is not necessary to determine the source of the interrupt.

When MVECEN = 1, Vectored interrupt controller requires three clock cycles to vector to the ISR from main routine, thereby removing dependency of interrupt timing on compiled code.

There is a fixed latency of three instruction cycles between the completion of the instruction active when the interrupt occurred and the first instruction of the Interrupt Service Routine. Figure 9-7, Figure 9-8 and Figure 9-9 illustrate the sequence of events when a peripheral interrupt is asserted when the last executed instruction is one-cycle, two-cycle and three-cycle respectively, when MVECEN = 1.

After the Interrupt Flag Status bit is set, the current instruction completes executing. In the first latency cycle, the contents of the PC, STATUS, WREG, BSR, FSR0/1/2, PRODL/H and PCLATH/U registers are context saved and the IVTBASE+ Vector number is calculated. In the second latency cycle, the PC is loaded with the calculated vector table address for the interrupt source and the starting address of the ISR is fetched. In the third latency cycle, the PC is loaded with the ISR address. All the latency cycles are executed as a FNOP instruction.

When MVECEN = 0, Vectored interrupt controller requires two clock cycles to vector to the ISR from main routine. There is a latency of two instruction cycles plus the software latency between the completion of the instruction active when the interrupt occurred and the first instruction of the Interrupt Service Routine.

| R-0/0            | R-0/0          | U-0 | U-0 | U-0 U-0 U-0 U-0 U-0 |                             |     |       |  |  |  |

|------------------|----------------|-----|-----|---------------------|-----------------------------|-----|-------|--|--|--|

| STAT             | <1:0>          | —   | _   | —                   | —                           | —   | —     |  |  |  |

| bit 7            |                |     |     |                     |                             |     | bit 0 |  |  |  |

|                  |                |     |     |                     |                             |     |       |  |  |  |

| Legend:          |                |     |     |                     |                             |     |       |  |  |  |

| HC = Bit is clea | ared by hardwa | are |     |                     |                             |     |       |  |  |  |

| D - Deedekle     | L 11           |     | L:4 |                     | an a material la it was a d | (0) |       |  |  |  |

#### REGISTER 9-2: INTCON1: INTERRUPT CONTROL REGISTER 1

# HC = Bit is cleared by hardwareR = Readable bitW = Writable bitu = Bit is unchangedx = Bit is unknown'1' = Bit is set'0' = Bit is clearedq = Value depends on condition

#### bit 7-6 STAT<1:0>: Interrupt State Status bits

11 = High priority ISR executing, high priority interrupt was received while a low priority ISR was executing

10 = High priority ISR executing, high priority interrupt was received in main routine

01 = Low priority ISR executing, low priority interrupt was received in main routine

00 = Main routine executing

bit 5-0 Unimplemented: Read as '0'

| U-0                        | U-0                             | U-0                  | U-0            | U-0                         | U-0              | R/W/HS-0/0       | R/W/HS-0/0   |  |

|----------------------------|---------------------------------|----------------------|----------------|-----------------------------|------------------|------------------|--------------|--|

| -                          | —                               | —                    | -              | —                           | —                | CLC4IF           | CCP4IF       |  |

| bit 7                      |                                 |                      |                |                             |                  |                  | bit 0        |  |

|                            |                                 |                      |                |                             |                  |                  |              |  |

| Legend:                    |                                 |                      |                |                             |                  |                  |              |  |

| R = Readable bit W = Writa |                                 |                      | bit            | U = Unimpler                | mented bit, read | as '0'           |              |  |

| u = Bit is und             | changed                         | x = Bit is unkr      | nown           | -n/n = Value                | at POR and BO    | R/Value at all c | other Resets |  |

| '1' = Bit is se            | et                              | '0' = Bit is cleared |                | HS = Bit is set in hardware |                  |                  |              |  |

|                            |                                 |                      |                |                             |                  |                  |              |  |

| bit 7-2                    | Unimplemen                      | ted: Read as '       | O'             |                             |                  |                  |              |  |

| bit 1                      | CLC4IF: CLC                     | 4 Interrupt Flag     | g bit          |                             |                  |                  |              |  |

|                            | 1 = Interrupt                   | has occurred (i      | must be cleare | ed by software              | )                |                  |              |  |

|                            | 0 = Interrupt                   | event has not o      | occurred       |                             |                  |                  |              |  |

| bit 0                      | CCP4IF: CCP4 Interrupt Flag bit |                      |                |                             |                  |                  |              |  |

|                            | 1 = Interrupt                   | has occurred (i      | must be cleare | ed by software              | )                |                  |              |  |

#### **REGISTER 9-13: PIR10: PERIPHERAL INTERRUPT REGISTER 10<sup>(1)</sup>**

- 0 = Interrupt event has not occurred

- **Note 1:** Interrupt flag bits get set when an interrupt condition occurs, regardless of the state of its corresponding enable bit, or the global enable bit. User software should ensure the appropriate interrupt flag bits are clear prior to enabling an interrupt.

# PIC18(L)F26/27/45/46/47/55/56/57K42

| R/W-1/1         | R/W-1/1                                                         | R/W-1/1             | R/W-1/1          | R/W-1/1        | R/W-1/1          | R/W-1/1          | R/W-1/1     |  |  |  |

|-----------------|-----------------------------------------------------------------|---------------------|------------------|----------------|------------------|------------------|-------------|--|--|--|

| IOCIP           | CRCIP                                                           | SCANIP              | NVMIP            | CSWIP          | OSFIP            | HLVDIP           | SWIP        |  |  |  |

| bit 7           |                                                                 |                     |                  |                |                  |                  | bit         |  |  |  |

|                 |                                                                 |                     |                  |                |                  |                  |             |  |  |  |

| Legend:         |                                                                 |                     |                  |                |                  | (0)              |             |  |  |  |

| R = Readable    |                                                                 | W = Writable        |                  | •              | mented bit, read |                  |             |  |  |  |

| u = Bit is unc  | •                                                               | x = Bit is unk      |                  | -n/n = value a | at POR and BO    | R/value at all c | iner Resets |  |  |  |

| '1' = Bit is se | t                                                               | '0' = Bit is cle    | ared             |                |                  |                  |             |  |  |  |

| bit 7           | IOCIP: Inter                                                    | rupt-on-Change      | Priority bit     |                |                  |                  |             |  |  |  |

|                 | 1 = High pri                                                    |                     | 2                |                |                  |                  |             |  |  |  |

|                 | 0 = Low price                                                   | ority               |                  |                |                  |                  |             |  |  |  |

| bit 6           | CRCIP: CR                                                       | C Interrupt Prior   | ity bit          |                |                  |                  |             |  |  |  |

|                 | 1 = High pri                                                    |                     |                  |                |                  |                  |             |  |  |  |

|                 | 0 = Low price                                                   | •                   |                  |                |                  |                  |             |  |  |  |

| bit 5           |                                                                 | emory Scanner       | Interrupt Prior  | ity bit        |                  |                  |             |  |  |  |

|                 | <ul> <li>1 = High priority</li> <li>0 = Low priority</li> </ul> |                     |                  |                |                  |                  |             |  |  |  |

| bit 4           | -                                                               | M Interrupt Prior   | ity hit          |                |                  |                  |             |  |  |  |

|                 | 1 = High pri                                                    | -                   |                  |                |                  |                  |             |  |  |  |

|                 | 0 = Low price                                                   | •                   |                  |                |                  |                  |             |  |  |  |

| bit 3           | CSWIP: Clo                                                      | ck Switch Interr    | upt Priority bit |                |                  |                  |             |  |  |  |

|                 | 1 = High pri                                                    | ,                   |                  |                |                  |                  |             |  |  |  |

|                 | 0 = Low price                                                   | ority               |                  |                |                  |                  |             |  |  |  |

| bit 2           |                                                                 | illator Fail Interr | upt Priority bit | :              |                  |                  |             |  |  |  |

|                 | 1 = High pri                                                    |                     |                  |                |                  |                  |             |  |  |  |

| L:1 4           | 0 = Low price                                                   | •                   | a with a latit   |                |                  |                  |             |  |  |  |

| bit 1           | 1 = High pri                                                    | VD Interrupt Pri    | ority dit        |                |                  |                  |             |  |  |  |

|                 | 1 = High phi0 = Low price                                       |                     |                  |                |                  |                  |             |  |  |  |

| bit 0           | -                                                               | vare Interrupt Pr   | iority bit       |                |                  |                  |             |  |  |  |

|                 | 1 = High pri                                                    |                     | <b>,</b> -       |                |                  |                  |             |  |  |  |

|                 | 0 = Low price                                                   | -                   |                  |                |                  |                  |             |  |  |  |

#### REGISTER 9-25: IPR0: PERIPHERAL INTERRUPT PRIORITY REGISTER 0

| Name     | Bit 7     | Bit 6     | Bit 5    | Bit 4    | Bit 3      | Bit 2       | Bit 1      | Bit 0      | Register<br>on Page |

|----------|-----------|-----------|----------|----------|------------|-------------|------------|------------|---------------------|

| INTCON0  | GIE/GIEH  | GIEL      | IPEN     | -        | -          | INT2EDG     | INT1EDG    | INT0EDG    | 135                 |

| INTCON1  | STAT      | <1:0>     | -        | -        | -          | -           | -          | —          | 136                 |

| PIE0     | IOCIE     | CRCIE     | SCANIE   | NVMIE    | CSWIE      | OSFIE       | HLVDIE     | SWIE       | 147                 |

| PIE1     | SMT1PWAIE | SMT1PRAIE | SMT1IE   | C1IE     | ADTIE      | ADIE        | ZCDIE      | INTOIE     | 148                 |

| PIE2     | I2C1RXIE  | SPI1IE    | SPI1TXIE | SPI1RXIE | DMA1AIE    | DMA10RIE    | DMA1DCNTIE | DMA1SCNTIE | 149                 |

| PIE3     | TMR0IE    | U1IE      | U1EIE    | U1TXIE   | U1RXIE     | I2C1EIE     | I2C1IE     | I2C1TXIE   | 150                 |

| PIE4     | CLC1IE    | CWG1IE    | NCO1IE   | -        | CCP1IE     | TMR2IE      | TMR1GIE    | TMR1IE     | 151                 |

| PIE5     | I2C2TXIE  | I2C2RXIE  | DMA2AIE  | DMA2ORIE | DMA2DCNTIE | DMA2SCNTIE  | C2IE       | INT1IE     | 152                 |

| PIE6     | TMR3GIE   | TMR3IE    | U2IE     | U2EIE    | U2TXIE     | U2RXIE      | I2C2EIE    | I2C2IE     | 153                 |

| PIE7     | -         | -         | INT2IE   | CLC2IE   | CWG2IE     | _           | CCP2IE     | TMR4IE     | 154                 |

| PIE8     | TMR5GIE   | TMR5IE    | -        | -        | _          | _           | _          | —          | 155                 |

| PIE9     | -         | -         | -        | -        | CLC3IE     | CWG3IE      | CCP3IE     | TMR6IE     | 155                 |

| PIE10    | -         | -         | -        | -        | -          | -           | CLC4IE     | CCP4IE     | 156                 |

| PIR0     | IOCIF     | CRCIF     | SCANIF   | NVMIF    | CSWIF      | OSFIF       | HLVDIF     | SWIF       | 137                 |

| PIR1     | SMT1PWAIF | SMT1PRAIF | SMT1IF   | C1IF     | ADTIF      | ADIF        | ZCDIF      | INT0IF     | 138                 |

| PIR2     | I2C1RXIF  | SPI1IF    | SPI1TXIF | SPI1RXIF | DMA1AIF    | DMA10RIF    | DMA1DCNTIF | DMA1SCNTIF | 139                 |

| PIR3     | TMR0IF    | U1IF      | U1EIF    | U1TXIF   | U1RXIF     | I2C1EIF     | I2C1IF     | I2C1TXIF   | 140                 |

| PIR4     | CLC1IF    | CWG1IF    | NCO1IF   | -        | CCP1IF     | TMR2IF      | TMR1GIF    | TMR1IF     | 141                 |

| PIR5     | I2C2TXF   | I2C2RXF   | DMA2AIF  | DMA2ORIF | DMA2DCNTIF | DMA2SCNTIF  | C2IF       | INT1IF     | 142                 |

| PIR6     | TMR3GIF   | TMR3IF    | U2IF     | U2EIF    | U2TXIF     | U2RXIF      | I2C2EIF    | I2C2IF     | 143                 |

| PIR7     | —         | -         | INT2IF   | CLC2IF   | CWG2IF     | —           | CCP2IF     | TMR4IF     | 144                 |

| PIR8     | TMR5GIF   | TMR5IF    | _        | —        | -          | -           | -          | -          | 145                 |

| PIR9     | -         | -         | -        | -        | CLC3IF     | CWG3IF      | CCP3IF     | TMR6IF     | 145                 |

| PIR10    | -         | -         | -        | -        | -          | -           | CLC4IF     | CCP4IF     | 146                 |

| IPR0     | IOCIP     | CRCIP     | SCANIP   | NVMIP    | CSWIP      | OSFIP       | HLVDIP     | SWIP       | 157                 |

| IPR1     | SMT1PWAIP | SMT1PRAIP | SMT1IP   | C1IP     | ADTIP      | ADIP        | ZCDIP      | INT0IP     | 158                 |

| IPR2     | I2C1RIP   | SPI1IP    | SPI1TIP  | SPI1RIP  | DMA1AIP    | DMA10RIP    | DMA1DCNTIP | DMA1SCNTIP | 159                 |

| IPR3     | TMR0IP    | U1IP      | U1EIP    | U1TXIP   | U1RXIP     | I2C1EIP     | I2C1IP     | I2C1TXIP   | 160                 |

| IPR4     | CLC1IP    | CWG1IP    | NCO1IP   | -        | CCP1IP     | TMR2IP      | TMR1GIP    | TMR1IP     | 161                 |

| IPR5     | I2C2TXP   | I2C2RXP   | DMA2AIP  | DMA2ORIP | DMA2DCNTIP | DMA2SCNTIP  | C2IP       | INT1IP     | 162                 |

| IPR6     | TMR3GIP   | TMR3IP    | U2IP     | U2EIP    | U2TXIP     | U2RXIP      | I2C2EIP    | I2C2IP     | 163                 |

| IPR7     | -         | -         | INT2IP   | CLC2IP   | CWG2IP     | -           | CCP2IP     | TMR4IP     | 164                 |

| IPR8     | TMR5GIP   | TMR5IP    | -        | -        | -          | -           | -          | -          | 164                 |

| IPR9     | -         | -         | -        | -        | CLC3IP     | CWG3IP      | CCP3IP     | TMR6IP     | 165                 |

| IPR10    | -         | -         | -        | -        | -          | -           | CLC4IP     | CCP4IP     | 165                 |

| IVTBASEU | _         | _         | -        |          | •          | BASE<20:16> | •          | I.         | 166                 |

| IVTBASEH |           |           |          | BAS      | E<15:8>    |             |            |            | 166                 |

| IVTBASEL |           |           |          | BAS      | SE<7:0>    |             |            |            | 166                 |

| IVTADU   |           |           |          |          |            | AD<20:16>   |            |            | 167                 |

| IVTADH   |           |           |          | AD       | <15:8>     |             |            |            | 167                 |

| IVTADL   |           |           |          | AD       | )<7:0>     |             |            |            | 167                 |

|          |           |           |          |          |            |             |            | IVTLOCKED  | 168                 |

| TABLE 9-3: | SUMMARY OF REGISTERS ASSOCIATED WITH INTERRUPTS |

|------------|-------------------------------------------------|

|------------|-------------------------------------------------|

Legend: — = unimplemented locations, read as '0'. Shaded bits are not used for interrupts.

#### 15.9.4 TRANSFER FROM SFR TO GPR

The following visual reference describes the sequence of events when copying ADC results to a GPR location. The ADC Interrupt Flag can be chosen as the Source Hardware trigger, the Source address can be set to point to the ADC Result registers at 3EEF, the Destination address can be set to point to any GPR location of our choice (Example 0x100).

#### FIGURE 15-8: SFR SPACE TO GPR SPACE TRANSFER

| Instruction<br>Clock       |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |  |

|----------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|

| EN                         |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |  |

| SIRQEN                     |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |  |

| Source Hardware<br>Trigger |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |  |

| DGO                        |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |  |

| DMAxSPTR                   | Ox3EEF         Ox3EF0         S         Ox3EEF         Ox3EEF         Ox3EEF         S         S         S         S         S         S         S         S         S         S         S         S         S         S         S         S         S         S         S         S         S         S         S         S         S         S         S         S         S         S         S         S         S         S         S         S         S         S         S         S         S         S         S         S         S         S         S         S         S         S         S         S         S         S         S         S         S         S         S         S         S         S         S         S         S         S         S         S         S         S         S         S         S         S         S         S         S         S         S         S         S         S         S         S         S         S         S         S         S         S         S         S         S         S         S         S         S         S         S         S </th <th></th>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |  |

| DMAxDPTR                   | 0x100         0x101         ( 0x102         0x103         ( 0x103)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |  |

| DMAxSCNT                   |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |  |

| DMAxDCNT                   |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |  |

| DMA STATE                  | $ \left( \begin{array}{c} \text{IDLE} \end{array} \right) \left( SR^{(1)} \right) DW^{(2)} \left( SR^$ |  |

| DMAxSCNTIF                 |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |  |

| DMAxDCNTIF -               | <u>}</u>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |  |

|                            | DMAxSSA 0x3EEF DMAxDSA 0x100                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |  |

|                            | DMAxSSZ 0x2 DMAxDSZ 0xA                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |  |

|                            | SMODE 0x1 DMODE 0x1                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |  |

| Note 1:                    | SR - Source Read                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |  |

| 2:                         | DW - Destination Write                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |  |

| R/W-1/1 |

|---------|---------|---------|---------|---------|---------|---------|---------|

| TRISx7  | TRISx6  | TRISx5  | TRISx4  | TRISx3  | TRISx2  | TRISx1  | TRISx0  |

| bit 7   |         |         |         |         |         |         | bit 0   |

|         |         |         |         |         |         |         |         |

|         |         |         |         |         |         |         |         |

#### REGISTER 16-2: TRISx: TRI-STATE CONTROL REGISTER

Legend:

W = Writable bit

U = Unimplemented bit, read as '0'

'1' = Bit is set

'0' = Bit is cleared

x = Bit is unknown

-n/n = Value at POR and BOR/Value at all other Resets

bit 7-0

- TRISx<7:0>: TRISx Port I/O Tri-state Control bits

- 1 = Port output driver is disabled

- 0 = Port output driver is enabled

#### TABLE 16-3: TRIS REGISTERS

| Name                 | Bit 7                 | Bit 6                 | Bit 5  | Bit 4  | Bit 3  | Bit 2  | Bit 1  | Bit 0  |

|----------------------|-----------------------|-----------------------|--------|--------|--------|--------|--------|--------|

| TRISA                | TRISA7                | TRISA6                | TRISA5 | TRISA4 | TRISA3 | TRISA2 | TRISA1 | TRISA0 |

| TRISB                | TRISB7 <sup>(1)</sup> | TRISB6 <sup>(1)</sup> | TRISB5 | TRISB4 | TRISB3 | TRISB2 | TRISB1 | TRISB0 |

| TRISC                | TRISC7                | TRISC6                | TRISC5 | TRISC4 | TRISC3 | TRISC2 | TRISC1 | TRISC0 |

| TRISD <sup>(2)</sup> | TRISD7                | TRISD6                | TRISD5 | TRISD4 | TRISD3 | TRISD2 | TRISD1 | TRISD0 |

| TRISE <sup>(2)</sup> | —                     | _                     | _      | —      | _      | TRISE2 | TRISE1 | TRISE0 |

| TRISF <sup>(3)</sup> | TRISF7                | TRISF6                | TRISF5 | TRISF4 | TRISF3 | TRISF2 | TRISF1 | TRISF0 |

Note 1: Bits RB6 and RB7 read '1' while in Debug mode.

2: Unimplemented in PIC18(L)F26/27K42.

**3:** Unimplemented in PIC18(L)F26/45/46/47K42.

| Name                   | Bit 7                 | Bit 6                 | Bit 5   | Bit 4   | Bit 3              | Bit 2                | Bit 1                | Bit 0                | Register on<br>Page |

|------------------------|-----------------------|-----------------------|---------|---------|--------------------|----------------------|----------------------|----------------------|---------------------|

| PORTA                  | RA7                   | RA6                   | RA5     | RA4     | RA3                | RA2                  | RA1                  | RA0                  | 263                 |

| PORTB                  | RB7 <sup>(1)</sup>    | RB6 <sup>(1)</sup>    | RB5     | RB4     | RB3                | RB2                  | RB1                  | RB0                  | 263                 |

| PORTC                  | RC7                   | RC6                   | RC5     | RC4     | RC3                | RC2                  | RC1                  | RC0                  | 263                 |

| PORTD <sup>(6)</sup>   | RD7                   | RD6                   | RD5     | RD4     | RD3                | RD2                  | RD1                  | RD0                  | 263                 |

| PORTE                  | _                     | _                     | _       | _       | RE3 <sup>(2)</sup> | RE2 <sup>(6)</sup>   | RE1 <sup>(6)</sup>   | RE0 <sup>(6)</sup>   | 263                 |

| PORTF <sup>(7)</sup>   | RF7                   | RF6                   | RF5     | RF4     | RF3                | RF2                  | RF1                  | RF0                  | 263                 |

| TRISA                  | TRISA7                | TRISA6                | TRISA5  | TRISA4  | TRISA3             | TRISA2               | TRISA1               | TRISA0               | 264                 |

| TRISB                  | TRISB7 <sup>(3)</sup> | TRISB6 <sup>(3)</sup> | TRISB5  | TRISB4  | TRISB3             | TRISB2               | TRISB1               | TRISB0               | 264                 |

| TRISC                  | TRISC7                | TRISC6                | TRISC5  | TRISC4  | TRISC3             | TRISC2               | TRISC1               | TRISC0               | 264                 |

| TRISD <sup>(6)</sup>   | TRISD7                | TRISD6                | TRISD5  | TRISD4  | TRISD3             | TRISD2               | TRISD1               | TRISD0               | 264                 |

| TRISE <sup>(6)</sup>   | -                     | —                     | _       | —       | —                  | TRISE2               | TRISE1               | TRISE0               | 264                 |

| TRISF <sup>(7)</sup>   | TRISF7                | TRISF6                | TRISF5  | TRISF4  | TRISF3             | TRISF2               | TRISF1               | TRISF0               | 264                 |

| LATA                   | LATA7                 | LATA6                 | LATA5   | LATA4   | LATA3              | LATA2                | LATA1                | LATA0                | 265                 |