Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

E·XFI

| Details                    |                                                                             |

|----------------------------|-----------------------------------------------------------------------------|

| Product Status             | Active                                                                      |

| Core Processor             | PIC                                                                         |

| Core Size                  | 8-Bit                                                                       |

| Speed                      | 64MHz                                                                       |

| Connectivity               | I <sup>2</sup> C, LINbus, SPI, UART/USART                                   |

| Peripherals                | Brown-out Detect/Reset, DMA, HLVD, POR, PWM, WDT                            |

| Number of I/O              | 25                                                                          |

| Program Memory Size        | 64KB (32K x 16)                                                             |

| Program Memory Type        | FLASH                                                                       |

| EEPROM Size                | 1K x 8                                                                      |

| RAM Size                   | 4K x 8                                                                      |

| Voltage - Supply (Vcc/Vdd) | 1.8V ~ 3.6V                                                                 |

| Data Converters            | A/D 24x12b; D/A 1x5b                                                        |

| Oscillator Type            | Internal                                                                    |

| Operating Temperature      | -40°C ~ 125°C (TA)                                                          |

| Mounting Type              | Surface Mount                                                               |

| Package / Case             | 28-SOIC (0.295", 7.50mm Width)                                              |

| Supplier Device Package    | 28-SOIC                                                                     |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/pic18lf26k42-e-so |

|                            |                                                                             |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

#### 6.13 Power Control (PCON0/PCON1) Register

The Power Control (PCON0/PCON1) register contains flag bits to differentiate between a:

- Brown-out Reset (BOR)

- Power-on Reset (POR)

- Reset Instruction Reset (RI)

- MCLR Reset (RMCLR)

- Watchdog Timer Reset (RWDT)

- Watchdog Window Violation (WDTWV)

- Stack Underflow Reset (STKUNF)

- Stack Overflow Reset (STKOVF)

- Memory Violation Reset (MEMV)

The PCON0/1 register bits are shown in Register 6-2 and Register 6-3. Hardware will change the corresponding register bit during the Reset process; if the Reset was not caused by the condition, the bit remains unchanged (Table 6-3).

Software should reset the bit to the inactive state after restart (hardware will not reset the bit). Software may also set any PCON0 bit to the active state, so that user code may be tested, but no Reset action will be generated.

### EXAMPLE 10-1: DOZE SOFTWARE EXAMPLE

```

//Mainline operation

bool somethingToDo = FALSE:

void main()

{

initializeSystem();

// DOZE = 64:1 (for example)

// ROI = 1;

GIE = 1; // enable interrupts

while (1)

{

// If ADC completed, process data

if (somethingToDo)

{

doSomething();

DOZEN = 1; // resume low-power

}

}

// Data interrupt handler

void interrupt()

// DOZEN = 0 because ROI = 1

if (ADIF)

{

somethingToDo = TRUE;

DOE = 0; // make main() go fast

ADIF = 0;

}

// else check other interrupts...

if (TMROIF)

{

timerTick++;

DOE = 1; // make main() go slow

TMROIF = 0;

}

```

#### FIGURE 10-2: WAKE-UP FROM SLEEP THROUGH INTERRUPT

| Q1 Q2 Q3 Q4 Q1 Q2 Q3 Q4 Q1                         | 01/02/03/04         |                    | Q3 Q4 Q1 Q2 Q3 Q4   |

|----------------------------------------------------|---------------------|--------------------|---------------------|

|                                                    |                     |                    |                     |

|                                                    | Tost <sup>(3)</sup> | ·/                 |                     |

| Interrupt flag                                     | / Interrupt Late    | ncy <sup>(4)</sup> |                     |

| GIE bit<br>(INTCON reg.)<br>Sleet                  |                     | <u>.</u>           |                     |

| Instruction Flow<br>PC X PC X PC + 1 X             | PC + 2 X PC + 2     | PC+2 00            | 004h X 0005h        |

| Instruction { Inst(PC) = Sleep Inst(PC + 1)        | Inst(PC + 2)        | Inst               | (0004h) Inst(0005h) |

| Instruction { Inst(PC - 1) Sleep                   | Inst(PC + 1)        | Forced NOP Force   | ed NOP Inst(0004h)  |

| Note 1: External clock. High, Medium, Low mode ass | umed.               |                    |                     |

2: CLKOUT is shown here for timing reference.

3: TOST = 1024 TOSC. This delay does not apply to EC and INTOSC Oscillator modes.

4: GIE = 1 assumed. In this case after wake-up, the processor calls the ISR at 0004h. If GIE = 0, execution will continue in-line.

#### 10.2.3 LOW-POWER SLEEP MODE

The PIC18F26/27/45/46/47/55/56/57K42 device family contains an internal Low Dropout (LDO) voltage regulator, which allows the device I/O pins to operate at voltages up to 5.5V while the internal device logic operates at a lower voltage. The LDO and its associated reference circuitry must remain active when the device is in Sleep mode.

The PIC18F26/27/45/46/47/55/56/57K42 devices allow the user to optimize the operating current in Sleep, depending on the application requirements.

Low-Power Sleep mode can be selected by setting the VREGPM bit of the VREGCON register.

#### 10.2.3.1 Sleep Current vs. Wake-up Time

In the default operating mode, the LDO and reference circuitry remain in the normal configuration while in Sleep. The device is able to exit Sleep mode quickly since all circuits remain active. In Low-Power Sleep mode, when waking-up from Sleep, an extra delay time is required for these circuits to return to the normal configuration and stabilize.

The Low-Power Sleep mode is beneficial for applications that stay in Sleep mode for long periods of time. The Normal mode is beneficial for applications that need to wake from Sleep quickly and frequently.

| U-0                                     | U-0                               | U-0                            | U-0          | R/W-0/0        | R/W-0/0          | R/W-0/0      | R/W-0/0 |

|-----------------------------------------|-----------------------------------|--------------------------------|--------------|----------------|------------------|--------------|---------|

| _                                       | _                                 | _                              | _            |                | TSEL             | <3:0>        |         |

| bit 7                                   | •                                 | ŀ                              |              | ·              |                  |              | bit (   |

| d.                                      |                                   |                                |              |                |                  |              |         |

| Legend:                                 |                                   |                                |              |                |                  |              |         |

| R = Readab                              | R = Readable bit W = Writable bit |                                |              |                | mented bit, read | l as '0'     |         |

| u = Bit is unchanged x = Bit is unknown |                                   |                                | -n/n = Value | at POR and BO  | R/Value at all c | other Resets |         |

| '1' = Bit is s                          | et                                | '0' = Bit is clea              | ared         |                |                  |              |         |

|                                         |                                   |                                |              |                |                  |              |         |

| bit 7-4                                 | Unimple                           | mented: Read as '              | ) <b>'</b>   |                |                  |              |         |

| bit 3-0                                 | •                                 | :0>: Scanner Data T            |              | Selection bits |                  |              |         |

|                                         |                                   | Reserved                       | nggoi mpar   |                |                  |              |         |

|                                         | •                                 |                                |              |                |                  |              |         |

|                                         | •                                 |                                |              |                |                  |              |         |

|                                         | •                                 |                                |              |                |                  |              |         |

|                                         |                                   |                                |              |                |                  |              |         |

|                                         |                                   | Reserved                       |              |                |                  |              |         |

|                                         |                                   | SMT1_output                    |              |                |                  |              |         |

|                                         |                                   | TMR6_postscaled<br>TMR5 output |              |                |                  |              |         |

|                                         |                                   | TMR4 postscaled                |              |                |                  |              |         |

|                                         |                                   | TMR3 output                    |              |                |                  |              |         |

|                                         | 0100 =                            | TMR2 postscaled                |              |                |                  |              |         |

|                                         | 0011 =                            | TMR1 output                    |              |                |                  |              |         |

|                                         |                                   | TMR0_output                    |              |                |                  |              |         |

|                                         | 0001 =                            | CLKREF_output                  |              |                |                  |              |         |

|                                         | 0000 =                            | LFINTOSC                       |              |                |                  |              |         |

#### **REGISTER 14-18: SCANTRIG: SCAN TRIGGER SELECTION REGISTER**

|                  |       | •                 |                                                                          |             |                 |           |         |  |  |  |

|------------------|-------|-------------------|--------------------------------------------------------------------------|-------------|-----------------|-----------|---------|--|--|--|

| U-0              | U-0   | R/W-0/u           | R/W-0/u                                                                  | R/W-0/u     | R/W-0/u         | R/W-0/u   | R/W-0/u |  |  |  |

| —                | _     |                   | RxyPPS<5:0>                                                              |             |                 |           |         |  |  |  |

| bit 7            |       | bit 0             |                                                                          |             |                 |           |         |  |  |  |

|                  |       |                   |                                                                          |             |                 |           |         |  |  |  |

| Legend:          |       |                   |                                                                          |             |                 |           |         |  |  |  |

| R = Readable I   | oit   | W = Writable b    | bit                                                                      | U = Unimple | mented bit, rea | id as '0' |         |  |  |  |

| u = Bit is uncha | anged | x = Bit is unkn   | x = Bit is unknown -n/n = Value at POR and BOR/Value at all other Resets |             |                 |           |         |  |  |  |

| '1' = Bit is set |       | '0' = Bit is clea | 0' = Bit is cleared                                                      |             |                 |           |         |  |  |  |

|                  |       |                   |                                                                          |             |                 |           |         |  |  |  |

#### REGISTER 17-2: RxyPPS: PIN Rxy OUTPUT SOURCE SELECTION REGISTER

bit 7-6 Unimplemented: Read as '0'

bit 5-0 **RxyPPS<5:0>:** Pin Rxy Output Source Selection bits See Table 17-2 for the list of available ports.

| R/W-0/0         | R/W-1/1                      | R/W-0/0                                               | R/W-1/1                          | R/W-0/0                                                      | R/W-1/1          | R/W-0/0         | R/W-1/1 |

|-----------------|------------------------------|-------------------------------------------------------|----------------------------------|--------------------------------------------------------------|------------------|-----------------|---------|

| C4TSE           | :L<1:0>                      | C3TSEL<1:0>                                           |                                  | C2TSEL<1:0>                                                  |                  | C1TSE           | EL<1:0> |

| bit 7           |                              |                                                       |                                  |                                                              |                  |                 | bit 0   |

|                 |                              |                                                       |                                  |                                                              |                  |                 |         |

| Legend:         |                              |                                                       |                                  |                                                              |                  |                 |         |

| R = Readable    | bit                          | W = Writable                                          | bit                              | U = Unimplen                                                 | nented bit, read | l as '0'        |         |

| -n = Value at F | POR                          | '1' = Bit is set                                      |                                  | '0' = Bit is clea                                            | ared             | x = Bit is unkr | nown    |

| bit 7-6         | 10 = CCP4 is                 | s based off Tin<br>s based off Tin<br>s based off Tin | ner5 in Captur<br>ner3 in Captur | s<br>e/Compare mo<br>e/Compare mo<br>e/Compare mo            | de and Timer4    | in PWM mode     |         |

| bit 5-4         | 11 = CCP3 is<br>10 = CCP3 is | s based off Tim<br>s based off Tim                    | ner5 in Captur<br>ner3 in Captur | e/Compare mo<br>e/Compare mo<br>e/Compare mo<br>e/Compare mo | de and Timer4    | in PWM mode     |         |

| bit 3-2         | 11 = CCP2 is<br>10 = CCP2 is | based off Tim<br>based off Tim                        | er5 in Capture<br>er3 in Capture | s<br>e/Compare mod<br>e/Compare mod<br>e/Compare mod         | le and Timer4 i  | n PWM mode      |         |

| bit 1-0         | 10 = CCP1 is                 | based off Tim<br>based off Tim<br>based off Tim       | er5 in Capture<br>er3 in Capture | s<br>e/Compare mod<br>e/Compare mod<br>e/Compare mod         | le and Timer4 i  | n PWM mode      |         |

#### REGISTER 23-2: CCPTMRS0: CCP TIMERS CONTROL REGISTER 0

| R/W-0/0       | R/W-1/1                                                | R/W-0/0                                                         | R/W-1/1 | R/W-0/0           | R/W-1/1          | R/W-0/0         | R/W-1/1 |

|---------------|--------------------------------------------------------|-----------------------------------------------------------------|---------|-------------------|------------------|-----------------|---------|

| P8TS          | EL<1:0>                                                | P7TSE                                                           | L<1:0>  | P6TSE             | EL<1:0>          | P5TSEL<1:0>     |         |

| bit 7         |                                                        |                                                                 |         |                   |                  | ·               | bit 0   |

|               |                                                        |                                                                 |         |                   |                  |                 |         |

| Legend:       |                                                        |                                                                 |         |                   |                  |                 |         |

| R = Readable  | e bit                                                  | W = Writable                                                    | bit     | U = Unimplen      | nented bit, read | d as '0'        |         |

| -n = Value at | POR                                                    | '1' = Bit is set                                                |         | '0' = Bit is clea | ared             | x = Bit is unkr | nown    |

| bit 7-6       | 11 = PWM8<br>10 = PWM8                                 | PWM8 Time<br>based on TMR<br>based on TMR<br>based on TMR<br>ed | 6<br>4  | S                 |                  |                 |         |

| bit 5-4       |                                                        |                                                                 |         |                   |                  |                 |         |

| bit 3-2       | 11 = PWM6 b<br>10 = PWM6 b                             | PWM6 Time<br>ased on TMR6<br>ased on TMR4<br>ased on TMR2<br>d  | 5<br>4  | S                 |                  |                 |         |

| bit 1-0       | <b>P5TSEL&lt;1:0&gt;</b><br>11 = PWM5 b<br>10 = PWM5 b | PWM5 Time<br>based on TMR6<br>based on TMR4<br>based on TMR2    | 5<br>4  | s                 |                  |                 |         |

#### REGISTER 24-2: CCPTMRS1: CCP TIMERS CONTROL REGISTER 1

#### 25.6.3 PERIOD AND DUTY CYCLE MODE

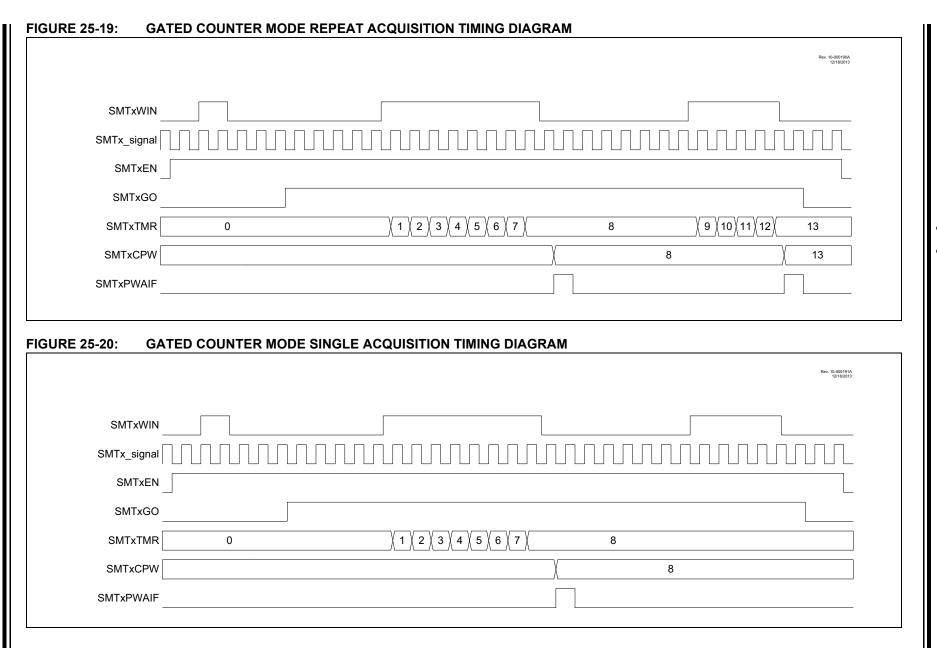

In Duty Cycle mode, either the duty cycle or period (depending on polarity) of the SMT1\_signal can be acquired relative to the SMT clock. The CPW register is updated on a falling edge of the signal, and the CPR register is updated on a rising edge of the signal, along with the SMT1TMR resetting to 0x0001. In addition, the GO bit is reset on a rising edge when the SMT is in Single Acquisition mode. See Figure 25-6 and Figure 25-7.

© 2016-2017 Microchip Technology Inc

Preliminary

| REGISTER :       | R/W-0/0                                                                                                        | N2: UART CONTE<br>R/W-0/0 R/                                                                                       | W-0/0     | R/W-0/0           | R/W-0/0            | R/W-0/0           | R/W-0/0      |  |

|------------------|----------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------|-----------|-------------------|--------------------|-------------------|--------------|--|

| RUNOVF           | RXPOL                                                                                                          | STP<1:0>                                                                                                           | •• 0/0    | C0EN              | TXPOL              |                   | <1:0>        |  |

| bit 7            | 101 02                                                                                                         |                                                                                                                    |           | OULIN             | 174 02             | 120               | bit (        |  |

|                  |                                                                                                                |                                                                                                                    |           |                   |                    |                   |              |  |

| Legend:          |                                                                                                                |                                                                                                                    |           |                   |                    |                   |              |  |

| R = Readable     |                                                                                                                | W = Writable bit                                                                                                   |           |                   | nented bit, read   |                   |              |  |

| u = Bit is uncl  | •                                                                                                              | x = Bit is unknown                                                                                                 |           | -n/n = Value a    | at POR and BO      | R/Value at all c  | other Resets |  |

| '1' = Bit is set |                                                                                                                | '0' = Bit is cleared                                                                                               |           |                   |                    |                   |              |  |

| bit 7            |                                                                                                                | In During Overflow C                                                                                               | `ontrol h | it                |                    |                   |              |  |

|                  |                                                                                                                | shifter continues to                                                                                               |           |                   | hits after overflo | w condition       |              |  |

|                  |                                                                                                                | shifter stops all activ                                                                                            |           |                   |                    |                   |              |  |

| bit 6            | RXPOL: Rec                                                                                                     | eive Polarity Control                                                                                              | bit       |                   |                    |                   |              |  |

|                  |                                                                                                                | K polarity, Idle state is                                                                                          |           |                   |                    |                   |              |  |

|                  | -                                                                                                              | ity is not inverted, Id                                                                                            |           | s high            |                    |                   |              |  |

| bit 5-4          |                                                                                                                | top Bit Mode Control                                                                                               |           | a first Otan hit  |                    |                   |              |  |

|                  |                                                                                                                | nit 2 Stop bits, receiver verifies first Stop bit<br>nit 2 Stop bits, receiver verifies first and second Stop bits |           |                   |                    |                   |              |  |

|                  |                                                                                                                | nit 1.5 Stop bits, rece                                                                                            |           |                   |                    |                   |              |  |

|                  |                                                                                                                | nit 1 Stop bit, receive                                                                                            |           | s first Stop bit  |                    |                   |              |  |

| bit 3            | COEN: Check                                                                                                    | sum Mode Select bi                                                                                                 | t(2)      |                   |                    |                   |              |  |

|                  | LIN mode:                                                                                                      |                                                                                                                    |           |                   |                    |                   |              |  |

|                  |                                                                                                                | m Mode 1, enhanced                                                                                                 |           |                   |                    | um                |              |  |

|                  | <ul> <li>0 = Checksum Mode 0, legacy LIN checksum does not include PID in sum</li> <li>Other modes:</li> </ul> |                                                                                                                    |           |                   |                    |                   |              |  |

|                  |                                                                                                                | X and RX characters                                                                                                | 5         |                   |                    |                   |              |  |

|                  | 0 = Checksu                                                                                                    | ms disabled                                                                                                        |           |                   |                    |                   |              |  |

| bit 2            | TXPOL: Tran                                                                                                    | smit Polarity Control                                                                                              | bit       |                   |                    |                   |              |  |

|                  |                                                                                                                | ata is inverted, TX ou                                                                                             | •         |                   |                    |                   |              |  |

|                  | -                                                                                                              | ata is not inverted, T                                                                                             | -         | t is high in Idle | state              |                   |              |  |

| bit 1-0          |                                                                                                                | landshake Flow Cont                                                                                                | trol bits |                   |                    |                   |              |  |

|                  | $11 = \frac{\text{Reserv}}{\text{RTS/C}}$                                                                      | ved<br>CTS and TXDE Hardv                                                                                          | ware flow | v control         |                    |                   |              |  |

|                  |                                                                                                                | OFF Software flow                                                                                                  |           | Veontion          |                    |                   |              |  |

|                  | 00 = Flow c                                                                                                    | ontrol is off                                                                                                      |           |                   |                    |                   |              |  |

| Note 1: All      | modes transmit                                                                                                 | t selected number of                                                                                               | Stop bit  | s. Only DMX a     | nd DALI receive    | ers verify select | ted number o |  |

|                  |                                                                                                                | thers verify only the f                                                                                            |           |                   |                    | -                 |              |  |

|                  |                                                                                                                |                                                                                                                    |           |                   |                    |                   |              |  |

### REGISTER 31-3: UxCON2: UART CONTROL REGISTER 2

2: UART1 only.

#### REGISTER 31-8: UxBRGL: UART BAUD RATE GENERATOR LOW REGISTER

| R/W-0/0          | R/W-0/0 | R/W-0/0           | R/W-0/0 | R/W-0/0        | R/W-0/0          | R/W-0/0          | R/W-0/0     |

|------------------|---------|-------------------|---------|----------------|------------------|------------------|-------------|

|                  |         |                   | BRG     | <7:0>          |                  |                  |             |

| bit 7            |         |                   |         |                |                  |                  | bit 0       |

|                  |         |                   |         |                |                  |                  |             |

| Legend:          |         |                   |         |                |                  |                  |             |

| R = Readable     | bit     | W = Writable      | bit     | U = Unimpler   | nented bit, read | as '0'           |             |

| u = Bit is uncha | anged   | x = Bit is unkr   | iown    | -n/n = Value a | at POR and BO    | R/Value at all c | ther Resets |

| '1' = Bit is set |         | '0' = Bit is clea | ared    |                |                  |                  |             |

bit 7-0 BRG<7:0>: Least Significant Byte of Baud Rate Generator

#### REGISTER 31-9: UxBRGH: UART BAUD RATE GENERATOR HIGH REGISTER

| R/W-0/0   | R/W-0/0 | R/W-0/0 | R/W-0/0 | R/W-0/0 | R/W-0/0 | R/W-0/0 | R/W-0/0 |

|-----------|---------|---------|---------|---------|---------|---------|---------|

| BRG<15:8> |         |         |         |         |         |         |         |

| bit 7     |         |         |         |         |         |         | bit 0   |

| Legend:              |                      |                                                       |

|----------------------|----------------------|-------------------------------------------------------|

| R = Readable bit     | W = Writable bit     | U = Unimplemented bit, read as '0'                    |

| u = Bit is unchanged | x = Bit is unknown   | -n/n = Value at POR and BOR/Value at all other Resets |

| '1' = Bit is set     | '0' = Bit is cleared |                                                       |

bit 7-0 BRG<15:8>: Most Significant Byte of Baud Rate Generator

**Note 1:** The UxBRG registers should only be written when ON = 0.

**2:** Maximum BRG value when MODE = 100x and BRGS = 1 is 0x7FFE.

3: Maximum BRG value when MODE = '100x' and BRGS = 0 is 0x1FFE.

#### 32.5.5 MASTER MODE SLAVE SELECT CONTROL

#### 32.5.5.1 Hardware Slave Select Control

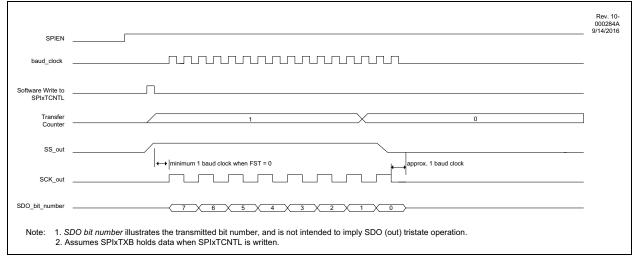

This SPI module allows for direct hardware control of a Slave Select output. The Slave Select output SS(out) is controlled both directly, through the SSET bit of SPIxCON2, as well indirectly by the hardware while the transfer counter is non-zero (see Section 32.4 "Transfer Counter"). SS(out) is steered by the PPS registers to pins (see Section 17.2 "PPS Outputs") and its polarity is controlled by the SSP bit of SPIxCON1. Setting the SSET bit will also assert SS(out). Clearing the SSET bit will leave SS(out) to be controlled by the Transfer Counter. When the Transfer Counter is loaded, the SPI module will automatically assert the SS. When the Transfer Counter decrements to zero, the SPI module will deassert SS either one baud period after the final SCK pulse of the final transfer (if CKE/SMP = 0/1) or one half baud period otherwise (see Figure 32-6).

#### FIGURE 32-6: SPI MASTER SS OPERATION- CKE = 0, BMODE = 1, TCWIDTH = 0, SSP = 0

#### 32.5.5.2 Software Slave Select Control

Slave Select can also be controlled through software via a general purpose I/O pin. In this case, ensure that the pin in question is configured as a GPIO through PPS (see Section 17.2 "PPS Outputs"), and ensure that the pin is set as an output (clear the appropriate bit in the appropriate TRIS register). In this case, SSET will not affect the slave select, the Transfer Counter will not automatically control the slave select output, and all setting and clearing of the slave select output line must be directly controlled by software.

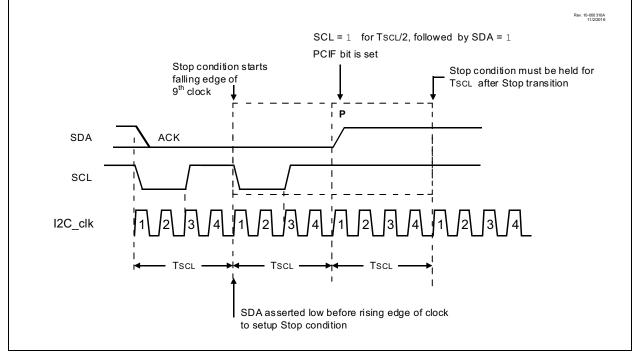

#### FIGURE 33-18: STOP CONDITION DURING RECEIVE OR TRANSMIT

#### 33.5.9 MASTER TRANSMISSION IN 7-BIT ADDRESSING MODE

This section describes the sequence of events for the  $I^2C$  module configured as an  $I^2C$  master in 7-bit Addressing mode and is transmitting data. Figure 33-19 is used as a visual reference for this description.

#### 1. If ABD = 0; i.e., Address buffers are enabled

Master software loads number of bytes to be transmitted in one sequence in I2CxCNT, slave address in I2CxADB1 with R/W = 0 and the first byte of data in I2CxTXB. Master software has to set the Start (S) bit to initiate communication.

If ABD = 1; i.e., Address buffers are disabled

Master software loads the number of bytes to be transmitted in one sequence in I2CxCNT and the slave address with R/W = 0 into the I2CxTXB register. Writing to the I2CxTXB will assert the start condition on the bus and sets the S bit. Software writes to the S bit are ignored in this case.

- 2. Master hardware waits for BFRE bit to be set; then shifts out start and address.

- If the transmit buffer is empty (i.e., TXBE = 1) and I2CxCNT!= 0, the I2CxTXIF and MDR bits are set and the clock is stretched on the 8th falling SCL edge. Clock can be started by loading the next data byte in I2CxTXB register.

- 4. Master sends out the 9th SCL pulse for ACK.

- If the Master hardware receives ACK from Slave device, it loads the next byte from the transmit buffer (I2CxTXB) into the shift register and the

value of I2CxCNT register is decremented.

- 6. If a NACK was received, Master hardware asserts Stop or Restart

- 7. If ABD = 0; i.e., Address buffers are enabled

If I2CxCNT = 0, Master hardware sends Stop or sets MDR if RSEN = 1 and waits for the software to set the Start bit again to issue a restart condition.

If ABD = 1; i.e., Address buffers are disabled

If I2CxCNT = 0, Master hardware sends Stop or sets MDR if RSEN = 1 and waits for the software to write the new address to the I2CxTXB register. Software writes to the S bit are ignored in this case.

- 8. Master hardware outputs data on SDA.

- 9. If TXBE = 1 and I2CxCNT! = 0, I2CxTXIF and MDR bits are set and the clock is stretched on 8th falling SCL edge. The user can release the clock by writing the next data byte to I2CxTXB register.

- 10. Master hardware clocks in ACK from Slave, and loads the next data byte from I2CTXB to the shift register. The value of I2CxCNT is decremented.

- 11. Go to step 7.

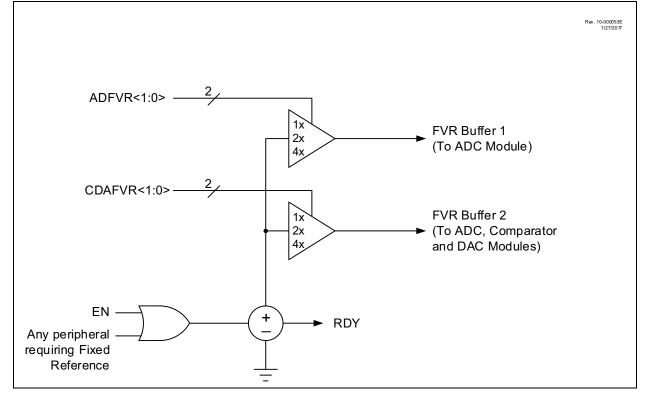

## 34.0 FIXED VOLTAGE REFERENCE (FVR)

The Fixed Voltage Reference, or FVR, is a stable voltage reference, independent of VDD, with 1.024V, 2.048V or 4.096V selectable output levels. The output of the FVR can be configured to supply a reference voltage to the following:

- ADC input channel

- ADC positive reference

- Comparator input

- Digital-to-Analog Converter (DAC)

The FVR can be enabled by setting the EN bit of the FVRCON register.

Note: Fixed Voltage Reference output cannot exceed VDD.

#### 34.1 Independent Gain Amplifiers

The output of the FVR, which is connected to the ADC, Comparators, and DAC, is routed through two independent programmable gain amplifiers. Each amplifier can be programmed for a gain of 1x, 2x or 4x, to produce the three possible voltage levels. The ADFVR<1:0> bits of the FVRCON register are used to enable and configure the gain amplifier settings for the reference supplied to the ADC module. Reference Section 36.0 "Analog-to-Digital Converter with Computation (ADC2) Module" for additional information.

The CDAFVR<1:0> bits of the FVRCON register are used to enable and configure the gain amplifier settings for the reference supplied to the DAC and comparator module. Reference Section 37.0 "5-Bit Digital-to-Analog Converter (DAC) Module" and Section 38.0 "Comparator Module" for additional information.

### 34.2 FVR Stabilization Period

When the Fixed Voltage Reference module is enabled, it requires time for the reference and amplifier circuits to stabilize. Once the circuits stabilize and are ready for use, the RDY bit of the FVRCON register will be set.

#### FIGURE 34-1: VOLTAGE REFERENCE BLOCK DIAGRAM

#### TABLE 41-1: OPCODE FIELD DESCRIPTIONS

| Field           | Description                                                                                                                                                      |

|-----------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| a               | RAM access bit<br>a = 0: RAM location in Access RAM (BSR register is ignored)                                                                                    |

|                 | a = 1: RAM bank is specified by BSR register                                                                                                                     |

| ACCESS          | ACCESS = 0: RAM access bit symbol                                                                                                                                |

| BANKED          | BANKED = 1: RAM access bit symbol                                                                                                                                |

| bbb             | Bit address within an 8-bit file register (0 to 7)                                                                                                               |

| BSR             | Bank Select Register. Used to select the current RAM bank.                                                                                                       |

| d               | Destination select bit;<br>d = 0: store result in WREG,<br>d = 1: store result in file register f.                                                               |

| dest            | Destination either the WREG register or the specified register file location                                                                                     |

| f               | 8-bit Register file address (00h to FFh)                                                                                                                         |

| f <sub>n</sub>  | FSR Number (0 to 2)                                                                                                                                              |

| fs              | 12-bit Register file address (000h to FFFh). This is the source address.                                                                                         |

| f <sub>d</sub>  | 12-bit Register file address (000h to FFFh). This is the destination address.                                                                                    |

| zs              | 7-bit literal offset for FSR2 to used as register file address (000h to FFFh). This is the source address.                                                       |

| zd              | 7-bit literal offset for FSR2 to used as register file address (000h to FFFh). This is the destination address.                                                  |

| k               | Literal field, constant data or label (may be a 6-bit, 8-bit, 12-bit or a 20-bit value)                                                                          |

| label           | Label name                                                                                                                                                       |

| mm              | The mode of the TBLPTR register for the Table Read and Table Write instructions<br>Only used with Table Read and Table Write instructions:                       |

| *               | No Change to register (such as TBLPTR with Table reads and writes)                                                                                               |

| *+              | Post-Increment register (such as TBLPTR with Table reads and writes)                                                                                             |

| *_              | Post-Decrement register (such as TBLPTR with Table reads and writes)                                                                                             |

| +*              | Pre-Increment register (such as TBLPTR with Table reads and writes)                                                                                              |

| n               | The relative address (2's complement number) for relative branch instructions, or the direct address for Call/Branch and Return instructions                     |

| PRODH           | Product of Multiply high byte                                                                                                                                    |

| PRODL           | Product of Multiply low byte                                                                                                                                     |

| S               | Fast Call / Return mode select bit.<br>s = 0: do not update into/from shadow registers<br>s = 1: certain registers loaded into/from shadow registers (Fast mode) |

| u               | Unused or Unchanged                                                                                                                                              |

| W               | W = 0: Destination select bit symbol                                                                                                                             |

| WREG            | Working register (accumulator)                                                                                                                                   |

| х               | Don't care (0 or 1)<br>The assembler will generate code with x = 0. It is the recommended form of use for compatibility with all Microchip software tools.       |

| TBLPTR          | 21-bit Table Pointer (points to a Program Memory location)                                                                                                       |

| TABLAT          | 8-bit Table Latch                                                                                                                                                |

| TOS             | Top of Stack                                                                                                                                                     |

| PC              | Program Counter                                                                                                                                                  |

| PCL             | Program Counter Low Byte                                                                                                                                         |

| PCH             | Program Counter High Byte                                                                                                                                        |

| PCLATH          | Program Counter High Byte Latch                                                                                                                                  |

| PCLATU          | Program Counter Upper Byte Latch                                                                                                                                 |

| GIE             | Global Interrupt Enable bit                                                                                                                                      |

| WDT             | Watchdog Timer                                                                                                                                                   |

| ТО              | Time-out bit                                                                                                                                                     |

| PD              | Power-down bit                                                                                                                                                   |

| C, DC, Z, OV, N | ALU status bits Carry, Digit Carry, Zero, Overflow, Negative                                                                                                     |

| [ ]             | Optional                                                                                                                                                         |

| ( )             | Contents                                                                                                                                                         |

| $\rightarrow$   | Assigned to                                                                                                                                                      |

| Address          | Name                   | Bit 7   | Bit 6   | Bit 5 | Bit 4   | Bit 3   | Bit 2   | Bit 1   | Bit 0    | Registe<br>on page |

|------------------|------------------------|---------|---------|-------|---------|---------|---------|---------|----------|--------------------|

| 3A16h            | RC6PPS                 | —       | —       | —     | RC6PPS4 | RC6PPS3 | RC6PPS2 | RC6PPS1 | RC6PPS0  | 280                |

| 3A15h            | RC5PPS                 | _       | —       | —     | RC5PPS4 | RC5PPS3 | RC5PPS2 | RC5PPS1 | RC5PPS0  | 280                |

| 3A14h            | RC4PPS                 | _       | —       | —     | RC4PPS4 | RC4PPS3 | RC4PPS2 | RC4PPS1 | RC4PPS0  | 280                |

| 3A13h            | RC3PPS                 | _       | —       | _     | RC3PPS4 | RC3PPS3 | RC3PPS2 | RC3PPS1 | RC3PPS0  | 280                |

| 3A12h            | RC2PPS                 | _       | —       | —     | RC2PPS4 | RC2PPS3 | RC2PPS2 | RC2PPS1 | RC2PPS0  | 280                |

| 3A11h            | RC1PPS                 | _       | —       | —     | RC1PPS4 | RC1PPS3 | RC1PPS2 | RC1PPS1 | RC1PPS0  | 280                |

| 3A10h            | RC0PPS                 | _       | —       | —     | RC0PPS4 | RC0PPS3 | RC0PPS2 | RC0PPS1 | RC0PPS0  | 280                |

| 3A0Fh            | RB7PPS                 | _       | —       | —     | RB7PPS4 | RB7PPS3 | RB7PPS2 | RB7PPS1 | RB7PPS0  | 280                |

| 3A0Eh            | RB6PPS                 | _       | —       | _     | RB6PPS4 | RB6PPS3 | RB6PPS2 | RB6PPS1 | RB6PPS0  | 280                |

| 3A0Dh            | RB5PPS                 | _       | —       | —     | RB5PPS4 | RB5PPS3 | RB5PPS2 | RB5PPS1 | RB5PPS0  | 280                |

| 3A0Ch            | RB4PPS                 | _       | —       | _     | RB4PPS4 | RB4PPS3 | RB4PPS2 | RB4PPS1 | RB4PPS0  | 280                |

| 3A0Bh            | RB3PPS                 | _       | —       | _     | RB3PPS4 | RB3PPS3 | RB3PPS2 | RB3PPS1 | RB3PPS0  | 280                |

| 3A0Ah            | RB2PPS                 | _       | —       | _     | RB2PPS4 | RB2PPS3 | RB2PPS2 | RB2PPS1 | RB2PPS0  | 280                |

| 3A09h            | RB1PPS                 | _       | —       | _     | RB1PPS4 | RB1PPS3 | RB1PPS2 | RB1PPS1 | RB1PPS0  | 280                |

| 3A08h            | RB0PPS                 | _       | _       | _     | RB0PPS4 | RB0PPS3 | RB0PPS2 | RB0PPS1 | RB0PPS0  | 280                |

| 3A07h            | RA7PPS                 | _       | _       | —     | RA7PPS4 | RA7PPS3 | RA7PPS2 | RA7PPS1 | RA7PPS0  | 280                |

| 3A06h            | RA6PPS                 | _       | _       | _     | RA6PPS4 | RA6PPS3 | RA6PPS2 | RA6PPS1 | RA6PPS0  | 280                |

| 3A05h            | RA5PPS                 | _       | _       | _     | RA5PPS4 | RA5PPS3 | RA5PPS2 | RA5PPS1 | RA5PPS0  | 280                |

| 3A04h            | RA4PPS                 | _       | _       | _     | RA4PPS4 | RA4PPS3 | RA4PPS2 | RA4PPS1 | RA4PPS0  | 280                |

| 3A03h            | RA3PPS                 | _       | _       | _     | RA3PPS4 | RA3PPS3 | RA3PPS2 | RA3PPS1 | RA3PPS0  | 280                |

| 3A02h            | RA2PPS                 | _       | _       | _     | RA2PPS4 | RA2PPS3 | RA2PPS2 | RA2PPS1 | RA2PPS0  | 280                |

| 3A01h            | RA1PPS                 | _       | _       | _     | RA1PPS4 | RA1PPS3 | RA1PPS2 | RA1PPS1 | RA1PPS0  | 280                |

| 3A00h            | RA0PPS                 | _       | _       | _     | RA0PPS4 | RA0PPS3 | RA0PPS2 | RA0PPS1 | RA0PPS0  | 280                |

| 39FFh -<br>39F8h | —                      |         |         | L     | Unimple | emented |         | •       |          |                    |

| 39F7h            | SCANPR                 | _       | —       | _     | _       | _       |         | PR      |          | 31                 |

| 39F6h -<br>39F5h | —                      |         |         |       | Unimple | emented |         |         |          |                    |

| 39F4h            | DMA2PR                 | —       | —       | —     | —       | —       |         | PR      |          | 31                 |

| 39F3h            | DMA1PR                 | —       | —       | —     | —       | —       |         | PR      |          | 30                 |

| 39F2h            | MAINPR                 | —       | —       | —     | —       | —       |         | PR      |          | 30                 |

| 39F1h            | ISRPR                  | —       | —       | —     | —       | —       |         | PR      |          | 30                 |

| 39F0h            | —                      |         |         |       | Unimple | emented |         |         |          |                    |

| 39EFh            | PRLOCK                 | —       | —       | —     | —       | —       | —       | —       | PRLOCKED | 31                 |

| 39EEh -<br>39E7h | —                      |         |         |       | Unimple | emented |         |         |          |                    |

| 39E6h            | NVMCON2                |         |         | -     | NVM     | CON2    |         |         |          | 211                |

| 39E5h            | NVMCON1                | RI      | EG      | —     | FREE    | WRERR   | WREN    | WR      | RD       | 210                |

| 39E4h            |                        |         |         |       | Unimple | emented |         |         |          |                    |

| 39E3h            | NVMDAT                 |         |         |       | D       | AT      |         |         |          | 212                |

| 39E2h            | —                      |         |         |       | Unimple | emented |         |         |          |                    |

| 39E1h            | NVMADRH <sup>(4)</sup> | —       | —       | _     | —       | _       | —       | A       | DR       | 211                |

| 39E0h            | NVMADRL                |         |         |       | A       | DR      |         |         |          | 211                |

| 39DFh            | OSCFRQ                 | _       | _       | _     | _       |         | F       | RQ      |          | 107                |

| 39DEh            | OSCTUNE                | _       | _       |       |         |         | TUN     |         |          | 108                |

| 39DDh            | OSCEN                  | EXTOEN  | HFOEN   | MFOEN | LFOEN   | SOSCEN  | ADOEN   | _       | —        | 109                |

| 39DCh            | OSCSTAT                | EXTOR   | HFOR    | MFOR  | LFOR    | SOR     | ADOR    | _       | PLLR     | 106                |

| 39DBh            | OSCCON3                | CSWHOLD | SOSCPWR | _     | ORDY    | NOSCR   | _       | _       | _        | 105                |

#### TABLE 42-1:REGISTER FILE SUMMARY FOR PIC18(L)F26/27/45/46/47/55/56/57K42 DEVICES

Legend: x = unknown, u = unchanged, — = unimplemented, q = value depends on condition

**Note 1:** Unimplemented in LF devices.

2: Unimplemented in PIC18(L)F26/27K42.

3: Unimplemented on PIC18(L)F26/27/45/46/47K42 devices.

4: Unimplemented in PIC18(L)F45/55K42.

| Address          | Name       | Bit 7            | Bit 6     | Bit 5    | Bit 4    | Bit 3           | Bit 2           | Bit 1           | Bit 0      | Regis<br>on pa |

|------------------|------------|------------------|-----------|----------|----------|-----------------|-----------------|-----------------|------------|----------------|

| 3989h            | IPR9       | —                | —         | —        | _        | CLC3IP          | CWG3IP          | CCP3IP          | TMR6IP     | 165            |

| 3988h            | IPR8       | TMR5GIP          | TMR5IP    | _        | _        | —               | _               | —               | _          | 164            |

| 3987h            | IPR7       |                  | _         | INT2IP   | CLC2IP   | CWG2IP          | -               | CCP2IP          | TMR4IP     | 164            |

| 3986h            | IPR6       | TMR3GIP          | TMR3IP    | U2IP     | U2EIP    | U2TXIP          | U2RXIP          | I2C2EIP         | I2C2IP     | 163            |

| 3985h            | IPR5       | I2C2TXIP         | I2C2RXIP  | DMA2AIP  | DMA2ORIP | DMA2DCN-<br>TIP | DMA2SCN-<br>TIP | C2IP            | INT1IP     | 162            |

| 3984h            | IPR4       | CLC1IP           | CWG1IP    | NCO1IP   | _        | CCP1IP          | TMR2IP          | TMR1GIP         | TMR1IP     | 161            |

| 3983h            | IPR3       | TMR0IP           | U1IP      | U1EIP    | U1TXIP   | U1RXIP          | I2C1EIP         | I2C1IP          | I2C1TXIP   | 160            |

| 3982h            | IPR2       | I2C1RXIP         | SPI1IP    | SPI1TXIP | SPI1RXIP | DMA1AIP         | DMA10RIP        | DMA1DCN-<br>TIP | DMA1SCNTIP | 15             |

| 3981h            | IPR1       | SMT1PWAIP        | SMT1PRAIP | SMT1IP   | C1IP     | ADTIP           | ADIP            | ZCDIP           | INT0IP     | 158            |

| 3980h            | IPR0       | IOCIP            | CRCIP     | SCANIP   | NVMIP    | CSWIP           | OSFIP           | HLVDIP          | SWIP       | 15             |

| 397Fh -<br>397Eh | —          | Unimplemented    |           |          |          |                 |                 |                 |            |                |

| 397Dh            | SCANTRIG   |                  | _         | _        | _        |                 | T               | SEL             |            | 22             |

| 397Ch            | SCANCON0   | EN               | TRIGEN    | SGO      | _        | —               | MREG            | BURSTMD         | BUSY       | 22             |

| 397Bh            | SCANHADRU  | —                | —         |          | •        | F               | IADR            | •               |            | 22             |

| 397Ah            | SCANHADRH  |                  |           |          | HA       | DR              |                 |                 |            | 22             |

| 3979h            | SCANHADRL  | HADR             |           |          |          |                 |                 |                 |            | 22             |

| 3978h            | SCANLADRU  |                  |           |          |          |                 |                 |                 |            | 22             |

| 3977h            | SCANLADRH  | LADR             |           |          |          |                 |                 |                 |            | 22             |

| 3976h            | SCANLADRL  | LADR             |           |          |          |                 |                 |                 |            | 22             |

| 3975h -<br>396Ah | -          | Unimplemented    |           |          |          |                 |                 |                 |            |                |

| 3969h            | CRCCON1    |                  | DLEI      | N        |          |                 | P               | LEN             |            | 21             |

| 3968h            | CRCCON0    | EN               | CRCGO     | BUSY     | ACCM     | _               | _               | SHIFTM          | FULL       | 21             |

| 3967h            | CRCXORH    | X15              | X14       | X13      | X12      | X11             | X10             | X9              | X8         | 22             |

| 3966h            | CRCXORL    | X7               | X6        | X5       | X4       | X3              | X2              | X1              | _          | 22             |

| 3965h            | CRCSHIFTH  | SHFT15           | SHFT14    | SHFT13   | SHFT12   | SHFT11          | SHFT10          | SHFT9           | SHFT8      | 22             |

| 3964h            | CRCSHIFTL  | SHFT7            | SHFT6     | SHFT5    | SHFT4    | SHFT3           | SHFT2           | SHFT1           | SHFT0      | 22             |

| 3963h            | CRCACCH    | ACC15            | ACC14     | ACC13    | ACC12    | ACC11           | ACC10           | ACC9            | ACC8       | 21             |

| 3962h            | CRCACCL    | ACC7             | ACC6      | ACC5     | ACC4     | ACC3            | ACC2            | ACC1            | ACC0       | 22             |

| 3961h            | CRCDATH    | DATA15           | DATA14    | DATA13   | DATA12   | DATA11          | DATA10          | DATA9           | DATA8      | 21             |

| 3960h            | CRCDATL    | DATA7            | DATA6     | DATA5    | DATA4    | DATA3           | DATA2           | DATA1           | DATA0      | 21             |

| 395Fh            | WDTTMR     |                  |           | WDTTMR   | 1        |                 | STATE           |                 | SCNT       | 18             |

| 395Eh            | WDTPSH     | PSCNT            |           |          |          |                 |                 |                 | 18         |                |

| 395Dh            | WDTPSL     | PSCNT            |           |          |          |                 |                 |                 | 18         |                |

| 395Ch            | WDTCON1    | _                |           | CS       |          |                 |                 | WINDOW          |            | 18             |

| 395Bh            | WDTCON0    |                  |           |          |          | PS              |                 |                 | SEN        | 18             |

| 395Ah -<br>38A0h | _          | Unimplemented    |           |          |          |                 |                 |                 |            | .0             |

| 389Fh            | IVTADU     | AD               |           |          |          |                 |                 |                 |            | 16             |

| 389Eh            | IVTADH     | AD               |           |          |          |                 |                 |                 |            | 16             |

| 389Dh            | IVTADL     |                  |           |          |          |                 |                 |                 |            | 16             |

| 389Ch -<br>3891h | _          | AD Unimplemented |           |          |          |                 |                 |                 |            | 10             |

|                  | PRODH SHAD | PRODH            |           |          |          |                 |                 |                 | 12         |                |

| 3890h            |            | PRODE            |           |          |          |                 |                 |                 |            |                |

| 3890h<br>388Fh   | PRODL_SHAD |                  |           |          | PR       | וחכ             |                 |                 |            | 125            |

#### **TABLE 42-1**: REGISTER FILE SUMMARY FOR PIC18(L)F26/27/45/46/47/55/56/57K42 DEVICES

Note 1: Unimplemented in LF devices.

Unimplemented in PIC18(L)F26/27K42. 2:

Unimplemented on PIC18(L)F26/27/45/46/47K42 devices. 3:

4: Unimplemented in PIC18(L)F45/55K42.

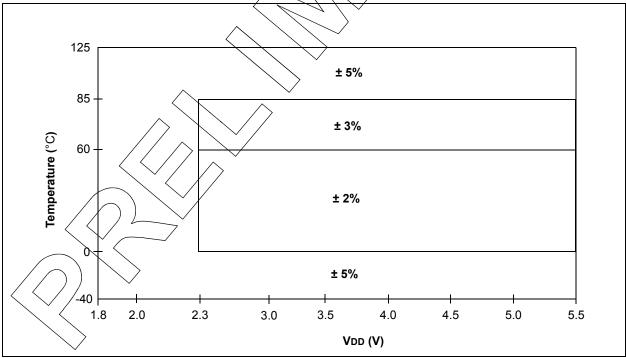

#### TABLE 44-10: INTERNAL OSCILLATOR PARAMETERS<sup>(1)</sup>

| Standard Operating Conditions (unless otherwise stated) |          |                                                 |              |                                |              |            |                          |  |

|---------------------------------------------------------|----------|-------------------------------------------------|--------------|--------------------------------|--------------|------------|--------------------------|--|

| Param<br>No.                                            | Sym.     | Characteristic                                  | Min.         | Тур†                           | Max.         | Units      | Conditions               |  |

| OS50                                                    | FHFOSC   | Precision Calibrated HFINTOSC<br>Frequency      | _            | 4<br>8<br>12<br>16<br>48<br>64 |              | MHz        | (Note 2)                 |  |

| OS51                                                    | FHFOSCLP | Low-Power Optimized HFINTOSC<br>Frequency       | 0.93<br>1.86 | 1<br>2                         | 1.07<br>2.14 | MHz<br>MHz |                          |  |

| OS53*                                                   | FLFOSC   | Internal LFINTOSC Frequency                     | —            | 31                             | _            | kHz        |                          |  |

| OS54*                                                   | THFOSCST | HFINTOSC<br>Wake-up from Sleep Start-up<br>Time | _            | 11<br>50                       | 20<br>—      | μs<br>μs   | VREGPM = 0<br>VREGPM = 1 |  |

| OS56                                                    | TLFOSCST | LFINTOSC<br>Wake-up from Sleep Start-up Time    |              | 0.2                            |              | ms         |                          |  |

These parameters are characterized but not tested. \*

Data in "Typ" column is at 3.0V, 25°C unless otherwise stated. These parameters are for design guidance † only and are not tested.

Note 1: To ensure these oscillator frequency tolerances, VDD and Vss must be capacitively decoupled as close to the device as possible. 0.1  $\mu$ F and 0.01  $\mu$ F values in parallel are recommended.

2: See Figure 44-6: Precision Calibrated HFINTOSC Frequency Accuracy Over Device VDD and Temperature.

PRECISION CALIBRATED HEINTOSC FREQUENCY ACCURACY OVER DEVICE **FIGURE 44-6:** VDD AND TEMPERATURE

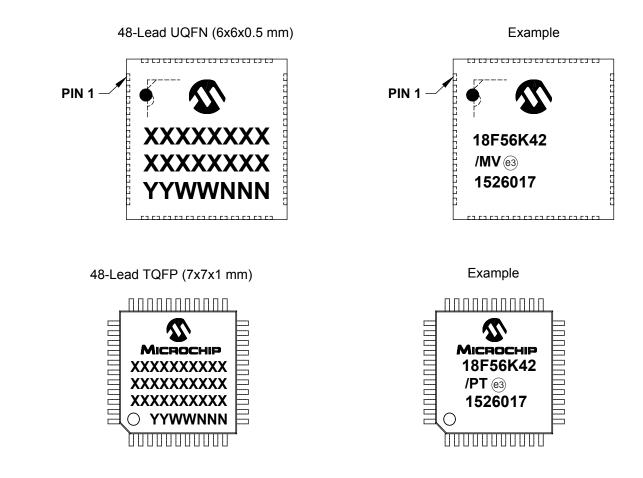

### Package Marking Information (Continued)

| Legend | d: XXX<br>Y<br>YY<br>WW<br>NNN<br>@3<br>* | Customer-specific information or Microchip part number<br>Year code (last digit of calendar year)<br>Year code (last 2 digits of calendar year)<br>Week code (week of January 1 is week '01')<br>Alphanumeric traceability code<br>Pb-free JEDEC <sup>®</sup> designator for Matte Tin (Sn)<br>This package is Pb-free. The Pb-free JEDEC designator ((e3))<br>can be found on the outer packaging for this package. |

|--------|-------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Note:  | be carrie                                 | nt the full Microchip part number cannot be marked on one line, it will d over to the next line, thus limiting the number of available s for customer-specific information.                                                                                                                                                                                                                                          |

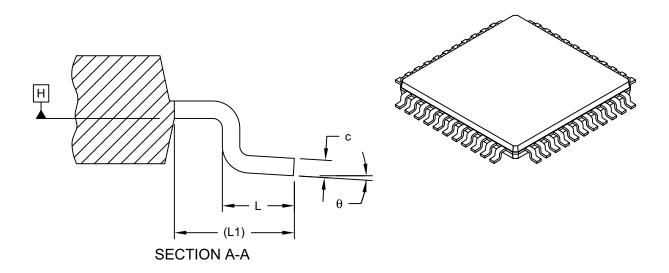

### 44-Lead Plastic Thin Quad Flatpack (PT) - 10x10x1.0 mm Body [TQFP]

**Note:** For the most current package drawings, please see the Microchip Packaging Specification located at http://www.microchip.com/packaging

|                          | MILLIMETERS  |           |        |      |  |  |

|--------------------------|--------------|-----------|--------|------|--|--|

| Dimension                | MIN          | NOM       | MAX    |      |  |  |

| Number of Leads          | N            | 44        |        |      |  |  |

| Lead Pitch               | е            | 0.80 BSC  |        |      |  |  |

| Overall Height           | Α            |           |        | 1.20 |  |  |

| Standoff                 | A1           | 0.05      | 0.05 - |      |  |  |

| Molded Package Thickness | A2           | 0.95      | 1.00   | 1.05 |  |  |

| Overall Width            | E            | 12.00 BSC |        |      |  |  |

| Molded Package Width     | E1           | 10.00 BSC |        |      |  |  |

| Overall Length           | D            | 12.00 BSC |        |      |  |  |

| Molded Package Length    | D1 10.00 BSC |           |        |      |  |  |

| Lead Width               | b            | 0.30      | 0.37   | 0.45 |  |  |

| Lead Thickness           | С            | 0.09      | -      | 0.20 |  |  |

| Lead Length              | L            | 0.45      | 0.60   | 0.75 |  |  |

| Footprint                | L1           | 1.00 REF  |        |      |  |  |

| Foot Angle               | θ            | 0°        | 3.5°   | 7°   |  |  |

Notes:

1. Pin 1 visual index feature may vary, but must be located within the hatched area.

2. Exact shape of each corner is optional.

3. Dimensioning and tolerancing per ASME Y14.5M

BSC: Basic Dimension. Theoretically exact value shown without tolerances.

REF: Reference Dimension, usually without tolerance, for information purposes only.

Microchip Technology Drawing C04-076C Sheet 2 of 2