Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

-XF

| Product Status             | Active                                                                      |

|----------------------------|-----------------------------------------------------------------------------|

| Core Processor             | PIC                                                                         |

| Core Size                  | 8-Bit                                                                       |

| Speed                      | 64MHz                                                                       |

| Connectivity               | I <sup>2</sup> C, LINbus, SPI, UART/USART                                   |

| Peripherals                | Brown-out Detect/Reset, DMA, HLVD, POR, PWM, WDT                            |

| Number of I/O              | 25                                                                          |

| Program Memory Size        | 64KB (32K x 16)                                                             |

| Program Memory Type        | FLASH                                                                       |

| EEPROM Size                | 1K x 8                                                                      |

| RAM Size                   | 4K x 8                                                                      |

| Voltage - Supply (Vcc/Vdd) | 1.8V ~ 3.6V                                                                 |

| Data Converters            | A/D 24x12b; D/A 1x5b                                                        |

| Oscillator Type            | Internal                                                                    |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                           |

| Mounting Type              | Surface Mount                                                               |

| Package / Case             | 28-VQFN Exposed Pad                                                         |

| Supplier Device Package    | 28-QFN (6x6)                                                                |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/pic18lf26k42-i-ml |

|                            |                                                                             |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

#### TABLE 4-11: SPECIAL FUNCTION REGISTER MAP FOR PIC18(L)F26/27/45/46/47/55/56/57K42 DEVICES BANK 56

| 38FFh | — | 38DFh | — | 38BFh | — | 389Fh | IVTADU       | 387Fh | — | 385Fh | — | 383Fh | — | 381Fh | — |

|-------|---|-------|---|-------|---|-------|--------------|-------|---|-------|---|-------|---|-------|---|

| 38FEh | — | 38DEh | — | 38BEh | — | 389Eh | IVTADH       | 387Eh | — | 385Eh | — | 383Eh | — | 381Eh | — |

| 38FDh | — | 38DDh | — | 38BDh | — | 389Dh | IVTADL       | 387Dh | — | 385Dh | — | 383Dh | — | 381Dh | — |

| 38FCh | — | 38DCh | — | 38BCh | — | 389Ch | —            | 387Ch | — | 385Ch | — | 383Ch | — | 381Ch | — |

| 38FBh | — | 38DBh | — | 38BBh | — | 389Bh | —            | 387Bh | — | 385Bh | — | 383Bh | — | 381Bh | — |

| 38FAh | — | 38DAh | — | 38BAh | — | 389Ah | —            | 387Ah | — | 385Ah | — | 383Ah | — | 381Ah | — |

| 38F9h | — | 38D9h | — | 38B9h | — | 3899h | —            | 3879h | — | 3859h | — | 3839h | — | 3819h | — |

| 38F8h | — | 38D8h | — | 38B8h | — | 3898h | —            | 3878h | — | 3858h | — | 3838h | — | 3818h | — |

| 38F7h | — | 38D7h | — | 38B7h | — | 3897h | —            | 3877h | — | 3857h | — | 3837h | — | 3817h | — |

| 38F6h | — | 38D6h | — | 38B6h | — | 3896h | —            | 3876h | — | 3856h | — | 3836h | — | 3816h | — |

| 38F5h | — | 38D5h | — | 38B5h | — | 3895h | —            | 3875h | — | 3855h | — | 3835h | — | 3815h | — |

| 38F4h | — | 38D4h | — | 38B4h | — | 3894h | —            | 3874h | — | 3854h | — | 3834h | — | 3814h | — |

| 38F3h | — | 38D3h | — | 38B3h | — | 3893h | —            | 3873h | — | 3853h | — | 3833h | — | 3813h | — |

| 38F2h | — | 38D2h | — | 38B2h | _ | 3892h | —            | 3872h | — | 3852h | — | 3832h |   | 3812h | — |

| 38F1h | — | 38D1h | — | 38B1h | _ | 3891h | —            | 3871h | — | 3851h | — | 3831h |   | 3811h | — |

| 38F0h | — | 38D0h | — | 38B0h | _ | 3890h | PRODH_SHAD   | 3870h | — | 3850h | — | 3830h |   | 3810h | — |

| 38EFh | — | 38CFh | — | 38AFh | _ | 388Fh | PRODL_SHAD   | 386Fh | — | 384Fh | — | 382Fh |   | 380Fh | — |

| 38EEh | — | 38CEh | — | 38AEh | _ | 388Eh | FSR2H_SHAD   | 386Eh | — | 384Eh | — | 382Eh |   | 380Eh | — |

| 38EDh | — | 38CDh | — | 38ADh | _ | 388Dh | FSR2L_SHAD   | 386Dh | — | 384Dh | — | 382Dh |   | 380Dh | — |

| 38ECh | — | 38CCh | — | 38ACh | _ | 388Ch | FSR1H_SHAD   | 386Ch | — | 384Ch | — | 382Ch |   | 380Ch | — |

| 38EBh | — | 38CBh | — | 38ABh | _ | 388Bh | FSR1L_SHAD   | 386Bh | — | 384Bh | — | 382Bh |   | 380Bh | — |

| 38EAh | — | 38CAh | — | 38AAh | _ | 388Ah | FSR0H_SHAD   | 386Ah | — | 384Ah | — | 382Ah |   | 380Ah | — |

| 38E9h | — | 38C9h | — | 38A9h | _ | 3889h | FSR0L_SHAD   | 3869h | — | 3849h | — | 3829h |   | 3809h | — |

| 38E8h | — | 38C8h | — | 38A8h | _ | 3888h | PCLATU_SHAD  | 3868h | — | 3848h | — | 3828h |   | 3808h | — |

| 38E7h | — | 38C7h | — | 38A7h | _ | 3887h | PCLATH_SHAD  | 3867h | — | 3847h | — | 3827h |   | 3807h | — |

| 38E6h | — | 38C6h | — | 38A6h | — | 3886h | BSR_SHAD     | 3866h | — | 3846h | — | 3826h | — | 3806h | — |

| 38E5h | — | 38C5h | — | 38A5h | — | 3885h | WREG_SHAD    | 3865h | — | 3845h | — | 3825h | — | 3805h | — |

| 38E4h | _ | 38C4h | — | 38A4h |   | 3884h | STATUS_SHAD  | 3864h | — | 3844h | — | 3824h | _ | 3804h | — |

| 38E3h | _ | 38C3h | — | 38A3h |   | 3883h | SHADCON      | 3863h | — | 3843h | — | 3823h | _ | 3803h | — |

| 38E2h | _ | 38C2h | — | 38A2h |   | 3882h | BSR_CSHAD    | 3862h | — | 3842h | — | 3822h | _ | 3802h | — |

| 38E1h | _ | 38C1h | _ | 38A1h |   | 3881h | WREG_CSHAD   | 3861h | — | 3841h | _ | 3821h | _ | 3801h |   |

| 38E0h | _ | 38C0h | — | 38A0h |   | 3880h | STATUS_CSHAD | 3860h | — | 3840h | — | 3820h | _ | 3800h | — |

Legend: Unimplemented data memory locations and registers, read as '0'.

Note 1: Unimplemented in LF devices.

2: Unimplemented in PIC18(L)F26/27K42.

**3:** Unimplemented in PIC18(L)F26/27/45/46/47K42.

#### 6.1 **Power-on Reset (POR)**

The POR circuit holds the device in Reset until VDD has reached an acceptable level for minimum operation. Slow rising VDD, fast operating speeds or analog performance may require greater than minimum VDD. The PWRT, BOR or MCLR features can be used to extend the start-up period until all device operation conditions have been met.

#### 6.2 Brown-out Reset (BOR)

The BOR circuit holds the device in Reset when VDD reaches a selectable minimum level. Between the POR and BOR, complete voltage range coverage for execution protection can be implemented.

The Brown-out Reset module has four operating modes controlled by the BOREN<1:0> bits in Configuration Words. The four operating modes are:

- · BOR is always on

- BOR is off when in Sleep

- BOR is controlled by software

- BOR is always off

Refer to Table 6-1 for more information.

The Brown-out Reset voltage level is selectable by configuring the BORV<1:0> bits in Configuration Words.

A VDD noise rejection filter prevents the BOR from triggering on small events. If VDD falls below VBOR for a duration greater than parameter TBORDC, the device will reset. See Table 44-13 for more information.

#### 6.2.1 BOR IS ALWAYS ON

When the BOREN bits of Configuration Words are programmed to '11', the BOR is always on. The device start-up will be delayed until the BOR is ready and VDD is higher than the BOR threshold.

BOR protection is active during Sleep. The BOR does not delay wake-up from Sleep.

#### 6.2.2 BOR IS OFF IN SLEEP

When the BOREN bits of Configuration Words are programmed to '10', the BOR is on, except in Sleep. The device start-up will be delayed until the BOR is ready and VDD is higher than the BOR threshold.

BOR protection is not active during Sleep. The device wake-up will be delayed until the BOR is ready.

#### 6.2.3 BOR CONTROLLED BY SOFTWARE

When the BOREN bits of Configuration Words are programmed to '01', the BOR is controlled by the SBOREN bit of the BORCON register. The device startup is not delayed by the BOR ready condition or the VDD level.

BOR protection begins as soon as the BOR circuit is ready. The status of the BOR circuit is reflected in the BORRDY bit of the BORCON register.

BOR protection is unchanged by Sleep.

#### 6.2.4 BOR AND BULK ERASE

BOR is forced ON during PFM Bulk Erase operations to make sure that a safe erase voltage is maintained for a successful erase cycle.

During Bulk Erase, the BOR is enabled at 2.45V for F and LF devices, even if it is configured to some other value. If VDD falls, the erase cycle will be aborted, but the device will not be reset.

| R-0/0            | R-0/0                           | U-0 | U-0 | U-0 | U-0                         | U-0 | U-0   |  |  |  |  |  |  |

|------------------|---------------------------------|-----|-----|-----|-----------------------------|-----|-------|--|--|--|--|--|--|

| STAT             | <1:0>                           | —   | _   | —   | —                           | —   | —     |  |  |  |  |  |  |

| bit 7            |                                 |     |     |     |                             |     | bit 0 |  |  |  |  |  |  |

|                  |                                 |     |     |     |                             |     |       |  |  |  |  |  |  |

| Legend:          |                                 |     |     |     |                             |     |       |  |  |  |  |  |  |

| HC = Bit is clea | HC = Bit is cleared by hardware |     |     |     |                             |     |       |  |  |  |  |  |  |

| D - Deedekle     | L 11                            |     | L:4 |     | an a material la it was a d | (0) |       |  |  |  |  |  |  |

#### REGISTER 9-2: INTCON1: INTERRUPT CONTROL REGISTER 1

# HC = Bit is cleared by hardwareR = Readable bitW = Writable bitu = Bit is unchangedx = Bit is unknown'1' = Bit is set'0' = Bit is clearedq = Value depends on condition

#### bit 7-6 STAT<1:0>: Interrupt State Status bits

11 = High priority ISR executing, high priority interrupt was received while a low priority ISR was executing

10 = High priority ISR executing, high priority interrupt was received in main routine

01 = Low priority ISR executing, low priority interrupt was received in main routine

00 = Main routine executing

bit 5-0 Unimplemented: Read as '0'

| R/W-0/0          | R/W-0/0                     | R/W-0/0          | R/W-0/0         | R/W-0/0      | R/W-0/0          | R/W-0/0 | R/W-0/0     |

|------------------|-----------------------------|------------------|-----------------|--------------|------------------|---------|-------------|

| TMR3GIE          | TMR3IE                      | U2IE             | U2EIE           | U2TXIE       | U2RXIE           | I2C2EIE | I2C2IE      |

| bit 7            |                             |                  |                 |              |                  |         | bit         |

| Legend:          |                             |                  |                 |              |                  |         |             |

| R = Readable     | e bit                       | W = Writable     | bit             | U = Unimpler | nented bit, read | as '0'  |             |

| u = Bit is uncł  | nanged                      | x = Bit is unkr  | nown            | •            | at POR and BO    |         | ther Resets |

| '1' = Bit is set | -                           | '0' = Bit is cle | ared            |              |                  |         |             |

| bit 7            |                             | MD2 Cata Inter   | wt. Enchla.h    | :1           |                  |         |             |

| Dit 7            | 1 = Enabled<br>0 = Disabled | VR3 Gate Inter   | rupt Enable b   | 11           |                  |         |             |

| bit 6            | TMR3IE: TM                  | R3 Interrupt En  | able bit        |              |                  |         |             |

|                  | 1 = Enabled<br>0 = Disabled |                  |                 |              |                  |         |             |

| bit 5            | U2IE: UART2                 | 2 Interrupt Enat | ole bit         |              |                  |         |             |

|                  | 1 = Enabled                 |                  |                 |              |                  |         |             |

|                  | 0 = Disabled                |                  |                 |              |                  |         |             |

| bit 4            |                             | F2 Framing Erro  | or Interrupt Er | nable bit    |                  |         |             |

|                  | 1 = Enabled<br>0 = Disabled |                  |                 |              |                  |         |             |

| bit 3            |                             | RT2 Transmit Ir  | terrunt Enabl   | e hit        |                  |         |             |

| DIU              | 1 = Enabled                 |                  |                 | ebit         |                  |         |             |

|                  | 0 = Disabled                |                  |                 |              |                  |         |             |

| bit 2            | U2RXIE: UA                  | RT2 Receive In   | terrupt Enable  | e bit        |                  |         |             |

|                  | 1 = Enabled                 |                  |                 |              |                  |         |             |

|                  | 0 = Disabled                |                  |                 |              |                  |         |             |

| bit 1            |                             | 2 Error Interrup | t Enable bit    |              |                  |         |             |

|                  | 1 = Enabled                 |                  |                 |              |                  |         |             |

| <b>h</b> # 0     | 0 = Disabled                |                  | a hit           |              |                  |         |             |

| bit 0            | 1 = Enabled                 | Interrupt Enabl  |                 |              |                  |         |             |

|                  |                             |                  |                 |              |                  |         |             |

#### REGISTER 9-20: PIE6: PERIPHERAL INTERRUPT ENABLE REGISTER 6

#### 11.7 Register Definitions: Windowed Watchdog Timer Control

#### REGISTER 11-1: WDTCON0: WATCHDOG TIMER CONTROL REGISTER 0

| U-0           | U-0                     | R/W <sup>(3)</sup> -q/q <sup>(2)</sup>         | R/W <sup>(3)</sup> -q/q <sup>(2)</sup> | R/W <sup>(3)</sup> -q/q <sup>(2)</sup> | R/W <sup>(3)</sup> -q/q <sup>(2)</sup> | R/W <sup>(3)</sup> -q/q <sup>(2)</sup> | R/W-0/0      |

|---------------|-------------------------|------------------------------------------------|----------------------------------------|----------------------------------------|----------------------------------------|----------------------------------------|--------------|

| _             | -                       |                                                |                                        | PS<4:0>                                |                                        |                                        | SEN          |

| oit 7         |                         |                                                |                                        |                                        |                                        |                                        | bit          |

|               |                         |                                                |                                        |                                        |                                        |                                        |              |

| _egend:       |                         |                                                |                                        |                                        |                                        |                                        |              |

| R = Reada     | ble bit                 | W = Writable bit                               |                                        | U = Unimpleme                          | nted bit, read as                      | '0'                                    |              |

| u = Bit is ur | nchanged                | x = Bit is unknow                              | vn                                     | -n/n = Value at                        | POR and BOR/V                          | alue at all other Re                   | esets        |

| 1' = Bit is s | et                      | '0' = Bit is cleare                            | d                                      | q = Value deper                        | nds on condition                       |                                        |              |

| oit 7-6       | Unimplem                | nented: Read as '0'                            |                                        |                                        |                                        |                                        |              |

| bit 5-1       | •                       | Watchdog Timer Preso                           | ala Salaat hita(                       | )                                      |                                        |                                        |              |

| JIL J- I      |                         | = Prescale Rate                                |                                        |                                        |                                        |                                        |              |

|               |                         | Reserved. Results in                           | minimum inten                          | al (1·32)                              |                                        |                                        |              |

|               | •                       |                                                |                                        | ar(1.52)                               |                                        |                                        |              |

|               | •                       |                                                |                                        |                                        |                                        |                                        |              |

|               | •                       |                                                |                                        |                                        |                                        |                                        |              |

|               | 10011 =                 | Reserved. Results in                           | minimum interv                         | al (1:32)                              |                                        |                                        |              |

|               | 10010 =                 | 1:8388608 (2 <sup>23</sup> ) (Inte             | erval 256s nomir                       | nal)                                   |                                        |                                        |              |

|               |                         | 1:4194304 (2 <sup>22</sup> ) (Inte             |                                        |                                        |                                        |                                        |              |

|               |                         | 1:2097152 (2 <sup>21</sup> ) (Inte             |                                        |                                        |                                        |                                        |              |

|               | 01111 =                 | 1:1048576 (2 <sup>20</sup> ) (Inte             | erval 32s nomina                       | al)                                    |                                        |                                        |              |

|               | 01110 =                 | 1:524288 (219) (Inter                          | val 16s nominal                        | )                                      |                                        |                                        |              |

|               | 01101 =                 | 1:262144 (2 <sup>18</sup> ) (Inter             | val 8s nominal)                        |                                        |                                        |                                        |              |

|               | 01100 =                 | 1:131072 (2 <sup>17</sup> ) (Inter             | val 4s nominal)                        |                                        |                                        |                                        |              |

|               |                         | 1:65536 (Interval 2s                           | , ,                                    | value)                                 |                                        |                                        |              |

|               |                         | 1:32768 (Interval 1s                           | ,                                      |                                        |                                        |                                        |              |

|               |                         | 1:16384 (Interval 512                          |                                        |                                        |                                        |                                        |              |

|               |                         | 1:8192 (Interval 256                           | ,                                      |                                        |                                        |                                        |              |

|               |                         | 1:4096 (Interval 128                           |                                        |                                        |                                        |                                        |              |

|               |                         | 1:2048 (Interval 64 m<br>1:1024 (Interval 32 m |                                        |                                        |                                        |                                        |              |

|               |                         | 1:512 (Interval 16 ms                          | ,                                      |                                        |                                        |                                        |              |

|               |                         | 1:256 (Interval 8 ms                           | ,                                      |                                        |                                        |                                        |              |

|               |                         | 1:128 (Interval 4 ms                           | ,                                      |                                        |                                        |                                        |              |

|               |                         | 1:64 (Interval 2 ms n                          | ,                                      |                                        |                                        |                                        |              |

|               |                         | 1:32 (Interval 1 ms ne                         |                                        |                                        |                                        |                                        |              |

| oit O         |                         | ware Enable/Disable fo                         | or Watchdog Tin                        | ner bit                                |                                        |                                        |              |

|               | If WDTE<                |                                                |                                        |                                        |                                        |                                        |              |

|               | This bit is             |                                                |                                        |                                        |                                        |                                        |              |

|               | If WDTE<                |                                                |                                        |                                        |                                        |                                        |              |

|               |                         | is turned on                                   |                                        |                                        |                                        |                                        |              |

|               |                         | is turned off                                  |                                        |                                        |                                        |                                        |              |

|               | If WDTE<<br>This bit is |                                                |                                        |                                        |                                        |                                        |              |

|               |                         | -                                              | hand a Oddin                           |                                        |                                        |                                        |              |

| Note 1:<br>2: |                         | vroximate. WDT time is<br>PS <4:0> in CONFIG3L |                                        |                                        | <4.0> is 01011                         | Otherwise the Po                       | set value of |

| 2:            |                         | ual to WDTCPS<4:0>                             |                                        | Cesel value of PS                      | <b>-4.0/ 15</b> UIUII.                 | ouierwise, lite Re                     | Set value of |

| 3:            | •                       | PS <4:0> in CONFIG3L                           |                                        | bits are read-on                       | lv                                     |                                        |              |

| 4:            |                         | DT is configured to rur                        |                                        |                                        | -                                      | o is allowed to upo                    | lorgo o Dooo |

4: When the WWDT is configured to run using the SOSC as a clock source and the device is allowed to undergo a Reset, as triggered by a WDT time-out, the SOSC would also undergo a Reset. That means the SOSC will execute its start-up sequence which requires 1024 SOSC clock counts before it is made available for peripherals to use. So for example, if the WDT is set for a 1 ms time-out and the device is allowed to undergo a WDT Reset, then the actual WDT Reset period will be: WDT\_PERIOD = (1/(SOSC\_FREQUENCY) \* 1024) + 1 ms.

| Name    | Bit 7 | Bit 6       | Bit 5      | Bit 4       | Bit 3 | Bit 2 | Bit 1       | Bit 0 | Register<br>on Page |  |

|---------|-------|-------------|------------|-------------|-------|-------|-------------|-------|---------------------|--|

| WDTCON0 |       | _           |            | PS<4:0> SEN |       |       |             |       |                     |  |

| WDTCON1 | _     |             | CS<2:0>    |             | _     | 1177  | WINDOW<2:0> |       |                     |  |

| WDTPSL  |       |             | PSCNT<7:0> |             |       |       |             |       |                     |  |

| WDTPSH  |       | PSCNT<15:8> |            |             |       |       |             |       |                     |  |

| WDTTMR  |       | W           | DTTMR<4:   | 0>          | STATE | PSCNT | <17:16>     | 185   |                     |  |

**Legend:** x = unknown, u = unchanged, – = unimplemented locations read as '0'. Shaded cells are not used by Windowed Watchdog Timer.

#### 16.2.6 INPUT THRESHOLD CONTROL

The INLVLx register (Register 16-8) controls the input voltage threshold for each of the available PORTx input pins. A selection between the Schmitt Trigger CMOS or the TTL compatible thresholds is available. The input threshold is important in determining the value of a read of the PORTx register and also the level at which an interrupt-on-change occurs, if that feature is enabled. See Table 44-6 for more information on threshold levels.

**Note:** Changing the input threshold selection should be performed while all peripheral modules are disabled. Changing the threshold level during the time a module is active may inadvertently generate a transition associated with an input pin, regardless of the actual voltage level on that pin.

#### 16.2.7 WEAK PULL-UP CONTROL

The WPUx register (Register 16-5) controls the individual weak pull-ups for each port pin.

#### 16.2.8 EDGE SELECTABLE INTERRUPT-ON-CHANGE

An interrupt can be generated by detecting a signal at the port pin that has either a rising edge or a falling edge. Any individual pin can be configured to generate an interrupt. The interrupt-on-change module is present on all the pins. For further details about the IOC module refer to Section 18.0 "Interrupt-on-Change".

#### 16.2.9 I<sup>2</sup>C PAD CONTROL

For the PIC18(L)F26/27/45/46/47/55/56/57K42 devices, the  $I^2C$  specific pads are available on RB1, RB2, RC3, RC4, RD0<sup>(1)</sup> and RD1<sup>(1)</sup> pins. The  $I^2C$  characteristics of each of these pins is controlled by the RxyI2C registers (see Register 16-9). These characteristics include enabling  $I^2C$  specific slew rate (over standard GPIO slew rate), selecting internal pullups for  $I^2C$  pins, and selecting appropriate input threshold as per SMBus specifications.

### **Note 1:** RD0 and RD1 I<sup>2</sup>C pads are not available in PIC18(L)F26K42 parts.

Any peripheral using the I<sup>2</sup>C pins read the I<sup>2</sup>C ST inputs when enabled via RxyI2C.

#### 16.3 PORTE Registers

Depending on the device, PORTE is implemented in two different ways.

#### 16.3.1 PORTE ON 40/44/48-PIN DEVICES

For PIC18(L)F45/46/47/55/56/57K42 devices, PORTE is a 4-bit wide port. Three pins (RE0, RE1 and RE2) are individually configurable as inputs or outputs. These pins have Schmitt Trigger input buffers. When selected as an analog input, these pins will read as '0's. The corresponding data direction register is TRISE. Setting a TRISE bit (= 1) will make the corresponding PORTE pin an input (i.e., disable the output driver).

Clearing a TRISE bit (= 0) will make the corresponding PORTE pin an output (i.e., enable the output driver and put the contents of the output latch on the selected pin). TRISE controls the direction of the REx pins, even when they are being used as analog pins. The user must make sure to keep the pins configured as inputs when using them as analog inputs. RE<2:0> bits have other registers associated with them (i.e., ANSELE, WPUE, INLVLE, SLRCONE and ODCONE). The functionality is similar to the other ports. The Data Latch register (LATE) is also memory-mapped. Readmodify-write operations on the LATE register read and write the latched output value for PORTE.

Note: On a Power-on Reset, RE<2:0> are configured as analog inputs.

The fourth pin of PORTE (MCLR/VPP/RE3) is an input-only pin. Its operation is controlled by the MCLRE Configuration bit. When selected as a port pin, (MCLRE = 0), it functions as a digital input-only pin; as such, it does not have TRIS or LAT bits associated with its operation. Otherwise, it functions as the device's Master Clear input. In either configuration, RE3 also functions as the programming voltage input during programming. RE3 in PORTE register is a read-only bit and will read '1' when MCLRE = 1 (i.e., Master Clear enabled).

Note: On a Power-on Reset, RE3 is enabled as a digital input only if Master Clear functionality is disabled.

| R/W-1/1 |

|---------|---------|---------|---------|---------|---------|---------|---------|

| SLRx7   | SLRx6   | SLRx5   | SLRx4   | SLRx3   | SLRx2   | SLRx1   | SLRx0   |

| bit 7   |         |         |         |         |         |         | bit 0   |

|         |         |         |         |         |         |         |         |

| Legend: |         |         |         |         |         |         |         |

#### REGISTER 16-7: SLRCONX: SLEW RATE CONTROL REGISTER

R = Readable bitW = Writable bitU = Unimplemented bit, read as '0''1' = Bit is set'0' = Bit is clearedx = Bit is unknown-n/n = Value at POR and BOR/Value at all other Resets

bit 7-0

- SLRx<7:0>: Slew Rate Control on Pins Rx<7:0>, respectively

- 1 = Port pin slew rate is limited

- 0 = Port pin slews at maximum rate

#### TABLE 16-8: SLEW RATE CONTROL REGISTERS

| Name                   | Bit 7 | Bit 6 | Bit 5 | Bit 4 | Bit 3 | Bit 2 | Bit 1 | Bit 0 |

|------------------------|-------|-------|-------|-------|-------|-------|-------|-------|

| SLRCONA                | SLRA7 | SLRA6 | SLRA5 | SLRA4 | SLRA3 | SLRA2 | SLRA1 | SLRA0 |

| SLRCONB                | SLRB7 | SLRB6 | SLRB5 | SLRB4 | SLRB3 | SLRB2 | SLRB1 | SLRB0 |

| SLRCONC                | SLRC7 | SLRC6 | SLRC5 | SLRC4 | SLRC3 | SLRC2 | SLRC1 | SLRC0 |

| SLRCOND <sup>(1)</sup> | SLRD7 | SLRD6 | SLRD5 | SLRD4 | SLRD3 | SLRD2 | SLRD1 | SLRD0 |

| SLRCONE <sup>(1)</sup> | _     | _     | _     | _     | _     | SLRE2 | SLRE1 | SLRE0 |

| SLRCONF <sup>(2)</sup> | SLRF7 | SLRF6 | SLRF5 | SLRF4 | SLRF3 | SLRF2 | SLRF1 | SLRF0 |

Note 1: Unimplemented in PIC18(L)F26/27K42.

2: Unimplemented in PIC18(L)F26/27/45/46/47K42.

| U-0            | U-0            | R/W-0/0                         | R/W-0/0 | U-0            | R/W-0/0          | R/W-0/0          | R/W-0/0      |

|----------------|----------------|---------------------------------|---------|----------------|------------------|------------------|--------------|

| —              | —              | U2MD                            | U1MD    | —              | SPI1MD           | I2C2MD           | I2C1MD       |

| bit 7          |                |                                 |         |                |                  |                  | bit 0        |

|                |                |                                 |         |                |                  |                  |              |

| Legend:        |                |                                 |         |                |                  |                  |              |

| R = Reada      | ble bit        | W = Writable                    | bit     | U = Unimplen   | nented bit, read | as '0'           |              |

| u = Bit is u   | nchanged       | x = Bit is unkn                 | iown    | -n/n = Value a | t POR and BOF    | R/Value at all o | other Resets |

| '1' = Bit is : | set            | '0' = Bit is clea               | ared    | q = Value dep  | ends on conditi  | on               |              |

|                |                |                                 |         |                |                  |                  |              |

| bit 7-6        | Unimpleme      | nted: Read as '0                | )'      |                |                  |                  |              |

| bit 5          | U2MD: Disa     | ble UART2 bit                   |         |                |                  |                  |              |

|                |                | module disabled                 |         |                |                  |                  |              |

|                | 0 = UART2      | module enabled                  |         |                |                  |                  |              |

| bit 4          |                | ble UART1 bit                   |         |                |                  |                  |              |

|                | -              | module disabled                 |         |                |                  |                  |              |

| L:1 0          |                | module enabled                  |         |                |                  |                  |              |

| bit 3          | -              | nted: Read as '0                |         |                |                  |                  |              |

| bit 2          |                | sable SPI1 Modu                 | ile bit |                |                  |                  |              |

|                | -              | odule disabled                  |         |                |                  |                  |              |

|                |                | odule enabled                   |         |                |                  |                  |              |

| bit 1          |                | sable I <sup>2</sup> C2 Modu    | le bit  |                |                  |                  |              |

|                | -              | odule disabled<br>odule enabled |         |                |                  |                  |              |

|                |                |                                 |         |                |                  |                  |              |

| bit 0          | -              | sable I <sup>2</sup> C1 Modu    | le bit  |                |                  |                  |              |

|                |                | odule disabled                  |         |                |                  |                  |              |

|                | 0 = 1 - 0.1  m | odule enabled                   |         |                |                  |                  |              |

#### REGISTER 19-6: PMD5: PMD CONTROL REGISTER 5

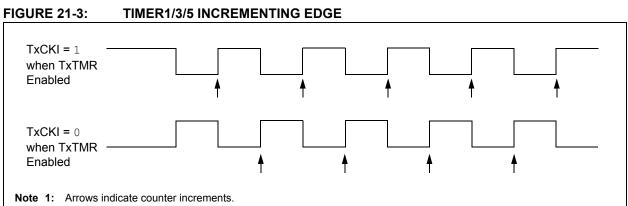

#### 21.3 Timer1/3/5 Prescaler

Timer1/3/5 has four prescaler options allowing 1, 2, 4 or 8 divisions of the clock input. The CKPS bits of the TxCON register control the prescale counter. The prescale counter is not directly readable or writable; however, the prescaler counter is cleared upon a write to TMRxH or TMRxL.

#### 21.4 Timer1/3/5 Operation in Asynchronous Counter Mode

If control bit SYNC of the TxCON register is set, the external clock input is not synchronized. The timer increments asynchronously to the internal phase clocks. If external clock source is selected then the timer will continue to run during Sleep and can generate an interrupt on overflow, which will wake up the processor. However, special precautions in software are needed to read/write the timer (see Section 21.4.1 "Reading and Writing Timer1/3/5 in Asynchronous Counter Mode").

Note: When switching from synchronous to asynchronous operation, it is possible to skip an increment. When switching from asynchronous to synchronous operation, it is possible to produce an additional increment.

#### 21.4.1 READING AND WRITING TIMER1/3/ 5 IN ASYNCHRONOUS COUNTER MODE

Reading TMRxH or TMRxL while the timer is running from an external asynchronous clock will ensure a valid read (taken care of in hardware). However, the user should keep in mind that reading the 16-bit timer in two 8-bit values itself, poses certain problems, since the timer may overflow between the reads. For writes, it is recommended that the user simply stop the timer and write the desired values. A write contention may occur by writing to the timer registers, while the register is incrementing. This may produce an unpredictable value in the TMRxH:TMRxL register pair.

#### 21.5 Timer1/3/5 16-Bit Read/Write Mode

Timer1/3/5 can be configured to read and write all 16 bits of data, to and from, the 8-bit TMRxL and TMRxH registers, simultaneously. The 16-bit read and write operations are enabled by setting the RD16 bit of the TxCON register.

To accomplish this function, the TMRxH register value is mapped to a buffer register called the TMRxH buffer register. While in 16-Bit mode, the TMRxH register is not directly readable or writable and all read and write operations take place through the use of this TMRxH buffer register.

When a read from the TMRxL register is requested, the value of the TMRxH register is simultaneously loaded into the TMRxH buffer register. When a read from the TMRxH register is requested, the value is provided from the TMRxH buffer register instead. This provides the user with the ability to accurately read all 16 bits of the Timer1/3/5 value from a single instance in time. Reference the block diagram in Figure 21-2 for more details.

In contrast, when not in 16-Bit mode, the user must read each register separately and determine if the values have become invalid due to a rollover that may have occurred between the read operations.

When a write request of the TMRxL register is requested, the TMRxH buffer register is simultaneously updated with the contents of the TMRxH register. The value of TMRxH must be preloaded into the TMRxH buffer register prior to the write request for the TMRxL register. This provides the user with the ability to write all 16 bits to the TMRxL:TMRxH register pair at the same time.

Any requests to write to the TMRxH directly does not clear the Timer1/3/5 prescaler value. The prescaler value is only cleared through write requests to the TMRxL register.

2: In Counter mode, a falling edge must be registered by the counter prior to the first incrementing rising edge of the clock.

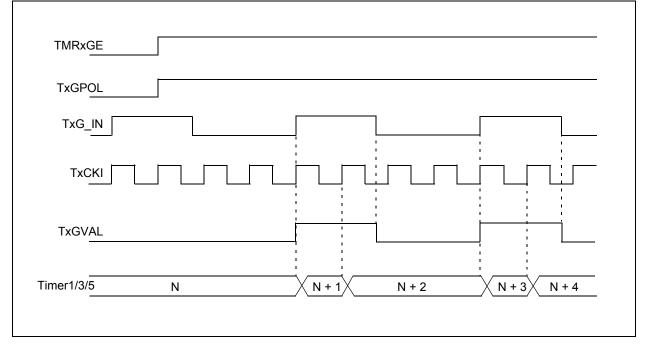

#### FIGURE 21-4: TIMER1/3/5 GATE ENABLE MODE

#### REGISTER 24-3: PWMxDCH: PWM DUTY CYCLE HIGH BITS

| R/W-x/u                                                                              | R/W-x/u | R/W-x/u           | R/W-x/u | R/W-x/u      | R/W-x/u          | R/W-x/u  | R/W-x/u |

|--------------------------------------------------------------------------------------|---------|-------------------|---------|--------------|------------------|----------|---------|

|                                                                                      |         |                   | DC      | <9:2>        |                  |          |         |

| bit 7                                                                                |         |                   |         |              |                  |          | bit 0   |

|                                                                                      |         |                   |         |              |                  |          |         |

| Legend:                                                                              |         |                   |         |              |                  |          |         |

| R = Readable                                                                         | bit     | W = Writable b    | oit     | U = Unimplen | nented bit, read | l as '0' |         |

| u = Bit is unchanged x = Bit is unknown -n/n = Value at POR and BOR/Value at all oth |         |                   |         |              |                  |          |         |

| '1' = Bit is set                                                                     |         | '0' = Bit is clea | ared    |              |                  |          |         |

bit 7-0 **DC<9:2>:** PWM Duty Cycle Most Significant bits These bits are the MSbs of the PWM duty cycle. The two LSbs are found in PWMxDCL Register.

#### REGISTER 24-4: PWMxDCL: PWM DUTY CYCLE LOW BITS

| R/W-x/u | R/W-x/u | U-0 | U-0 | U-0 | U-0 | U-0 | U-0   |

|---------|---------|-----|-----|-----|-----|-----|-------|

| DC<1:0> |         | —   | —   | —   | _   | —   | —     |

| bit 7   |         |     |     |     |     |     | bit 0 |

| Legend:              |                      |                                                       |

|----------------------|----------------------|-------------------------------------------------------|

| R = Readable bit     | W = Writable bit     | U = Unimplemented bit, read as '0'                    |

| u = Bit is unchanged | x = Bit is unknown   | -n/n = Value at POR and BOR/Value at all other Resets |

| '1' = Bit is set     | '0' = Bit is cleared |                                                       |

bit 7-6 **DC<1:0>:** PWM Duty Cycle Least Significant bits These bits are the LSbs of the PWM duty cycle. The MSbs are found in PWMxDCH Register. bit 5-0 **Unimplemented:** Read as '0'

#### TABLE 24-3: SUMMARY OF REGISTERS ASSOCIATED WITH PWM

| Name     | Bit 7     | Bit 6                   | Bit 5 | Bit 4 | Bit 3 | Bit 2  | Bit 1 | Bit 0  | Register<br>on Page |

|----------|-----------|-------------------------|-------|-------|-------|--------|-------|--------|---------------------|

| PWMxCON  | EN        | _                       | OUT   | POL   | —     | —      |       |        | 358                 |

| PWMxDCH  | H DC<9:2> |                         |       |       |       |        |       |        |                     |

| PWMxDCL  | DC<       | DC<1:0> — —             |       |       |       | _      | _     | _      | 360                 |

| CCPTMRS1 | P8TSE     | P8TSEL<1:0> P7TSEL<1:0> |       |       |       | L<1:0> | P5TSE | L<1:0> | 359                 |

Legend: - = Unimplemented locations, read as '0', u = unchanged, x = unknown. Shaded cells are not used by the PWM.

#### 26.14 Register Definitions: CWG Control

Long bit name prefixes for the CWG peripheral is shown below. Refer to **Section 1.3.2.2 "Long Bit Names**" for more information.

| Peripheral | Bit Name Prefix |

|------------|-----------------|

| CWG1       | CWG1            |

| CWG2       | CWG2            |

| CWG3       | CWG3            |

#### REGISTER 26-1: CWGxCON0: CWG CONTROL REGISTER 0

| R/W-0/0 | R/W/HC-0/0        | U-0 | U-0 | U-0 | R/W-0/0 | R/W-0/0   | R/W-0/0 |

|---------|-------------------|-----|-----|-----|---------|-----------|---------|

| EN      | LD <sup>(1)</sup> | —   | _   | —   |         | MODE<2:0> |         |

| bit 7   |                   |     |     |     |         |           | bit 0   |

I

| Legend:              |                      |                                                       |

|----------------------|----------------------|-------------------------------------------------------|

| R = Readable bit     | W = Writable bit     | U = Unimplemented bit, read as '0'                    |

| u = Bit is unchanged | x = Bit is unknown   | -n/n = Value at POR and BOR/Value at all other Resets |

| '1' = Bit is set     | '0' = Bit is cleared | HC = Bit is cleared by hardware                       |

| bit 7 | EN: CWGx Enable bit |

|-------|---------------------|

|       |                     |

- 1 = Module is enabled

- 0 = Module is disabled

bit 6 LD: CWGx Load Buffers bit<sup>(1)</sup>

- 1 = Dead-band count buffers to be loaded on CWG data rising edge, following first falling edge after this bit is set

- 0 = Buffers remain unchanged

- bit 5-3 Unimplemented: Read as '0'

- bit 2-0 **MODE<2:0>**: CWGx Mode bits

- 111 = Reserved

- 110 = Reserved

- 101 = CWG outputs operate in Push-Pull mode

- 100 = CWG outputs operate in Half-Bridge mode

- 011 = CWG outputs operate in Reverse Full-Bridge mode

- 010 = CWG outputs operate in Forward Full-Bridge mode

- 001 = CWG outputs operate in Synchronous Steering mode

- 000 = CWG outputs operate in Asynchronous Steering mode

**Note 1:** This bit can only be set after EN = 1; it cannot be set in the same cycle when EN is set.

| Name    | Bit 7    | Bit 6                          | Bit 5  | Bit 4 | Bit 3  | Bit 2  | Bit 1  | Bit 0 | Register<br>on page |

|---------|----------|--------------------------------|--------|-------|--------|--------|--------|-------|---------------------|

| UxCON0  | BRGS     | BRGS ABDEN TXEN RXEN MODE<3:0> |        |       |        |        |        |       | 498                 |

| UxCON1  | ON       | ON – – WUE RXBIMD – BRKOVR     |        |       |        |        |        | SENDB | 499                 |

| UxCON2  | RUNOVF   | F RXPOL STP<1:0>               |        |       | C0EN   | TXPOL  | FLO<   | <1:0> | 500                 |

| UxERRIR | TXMTIF   | PERIF                          | ABDOVF | CERIF | FERIF  | RXBKIF | RXFOIF | TXCIF | 501                 |

| UxERRIE | TXMTIE   | PERIE                          | ABDOVE | CERIE | FERIE; | RXBKIE | RXFOIE | TXCIE | 502                 |

| UxUIR   | WUIF     | ABDIF                          | _      | _     | _      | ABDIE  | _      | _     | 503                 |

| UxFIFO  | TXWRE    | STPMD                          | TXBE   | TXBF  | RXIDL  | XON    | RXBE   | RXBF  | 504                 |

| UxBRGL  | BRG<7:0> |                                |        |       |        |        |        |       |                     |

| UxBRGH  |          | BRG<15:8>                      |        |       |        |        |        |       |                     |

| UxRXB   |          |                                |        | RXB   | <7:0>  |        |        |       | 506                 |

| UxTXB   |          |                                |        | TXB   | <7:0>  |        |        |       | 506                 |

| UxP1H   | _        | _                              | _      | _     | —      | _      | _      | P1<8> | 507                 |

| UxP1L   |          |                                | •      | P1<   | 7:0>   |        |        |       | 507                 |

| UxP2H   | _        | _                              | _      | _     | —      | _      | _      | P2<8> | 508                 |

| UxP2L   |          |                                | •      | P2<   | 7:0>   |        |        |       | 508                 |

| UxP3H   | —        | —                              | —      | —     | —      | —      | —      | P3<8> | 509                 |

| UxP3L   |          |                                | •      | P3<   | 7:0>   | •      | •      |       | 509                 |

| UxTXCHK |          |                                |        | TXCH  | K<7:0> |        |        |       | 510                 |

| UxRXCHK |          |                                |        | RXCH  | K<7:0> |        |        |       | 510                 |

#### TABLE 31-3: SUMMARY OF REGISTERS ASSOCIATED WITH THE UART

Legend: — = unimplemented, read as '0'. Shaded cells are unused by the UART module.

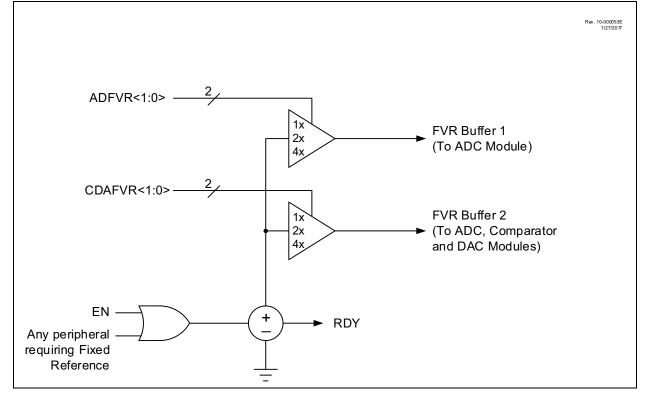

## 34.0 FIXED VOLTAGE REFERENCE (FVR)

The Fixed Voltage Reference, or FVR, is a stable voltage reference, independent of VDD, with 1.024V, 2.048V or 4.096V selectable output levels. The output of the FVR can be configured to supply a reference voltage to the following:

- ADC input channel

- ADC positive reference

- Comparator input

- Digital-to-Analog Converter (DAC)

The FVR can be enabled by setting the EN bit of the FVRCON register.

Note: Fixed Voltage Reference output cannot exceed VDD.

#### 34.1 Independent Gain Amplifiers

The output of the FVR, which is connected to the ADC, Comparators, and DAC, is routed through two independent programmable gain amplifiers. Each amplifier can be programmed for a gain of 1x, 2x or 4x, to produce the three possible voltage levels. The ADFVR<1:0> bits of the FVRCON register are used to enable and configure the gain amplifier settings for the reference supplied to the ADC module. Reference Section 36.0 "Analog-to-Digital Converter with Computation (ADC2) Module" for additional information.

The CDAFVR<1:0> bits of the FVRCON register are used to enable and configure the gain amplifier settings for the reference supplied to the DAC and comparator module. Reference Section 37.0 "5-Bit Digital-to-Analog Converter (DAC) Module" and Section 38.0 "Comparator Module" for additional information.

#### 34.2 FVR Stabilization Period

When the Fixed Voltage Reference module is enabled, it requires time for the reference and amplifier circuits to stabilize. Once the circuits stabilize and are ready for use, the RDY bit of the FVRCON register will be set.

#### FIGURE 34-1: VOLTAGE REFERENCE BLOCK DIAGRAM

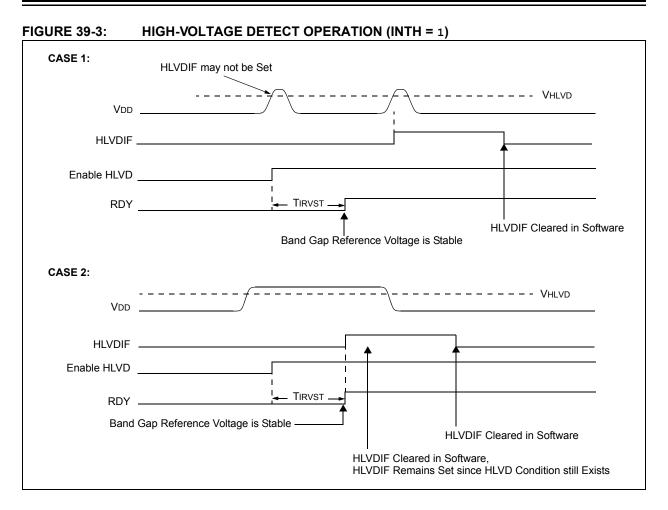

#### 39.5 Applications

In many applications, it is desirable to detect a drop below, or rise above, a particular voltage threshold. For example, the HLVD module could be periodically enabled to detect Universal Serial Bus (USB) attach or detach. This assumes the device is powered by a lower voltage source than the USB when detached. An attach would indicate a High-Voltage Detect from, for example, 3.3V to 5V (the voltage on USB) and vice versa for a detach. This feature could save a design a few extra components and an attach signal (input pin).

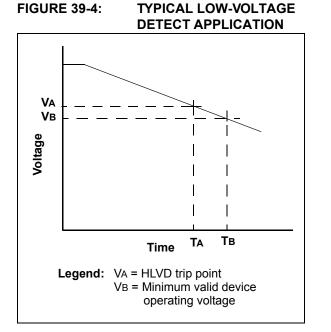

For general battery applications, Figure 39-4 shows a possible voltage curve. Over time, the device voltage decreases. When the device voltage reaches voltage, VA, the HLVD logic generates an interrupt at time, TA. The interrupt could cause the execution of an Interrupt Service Routine (ISR), which would allow the application to perform "housekeeping tasks" and a controlled shutdown before the device voltage exits the valid operating range at TB. This would give the application a time window, represented by the difference between TA and TB, to safely exit.

| 1     |     |     |     |         |         |         |         |

|-------|-----|-----|-----|---------|---------|---------|---------|

| bit 7 |     |     |     |         |         |         | bit 0   |

| _     | _   | _   | _   |         | SEL     | <3:0>   |         |

| U-0   | U-0 | U-0 | U-0 | R/W-0/0 | R/W-0/0 | R/W-0/0 | R/W-0/0 |

|       |     |     |     |         |         |         |         |

#### REGISTER 39-2: HLVDCON1: LOW-VOLTAGE DETECT CONTROL REGISTER 1

| Legend:           |                  |                             |                      |

|-------------------|------------------|-----------------------------|----------------------|

| R = Readable bit  | W = Writable bit | U = Unimplemented bit, read | l as '0'             |

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared        | u = Bit is unchanged |

bit 7-4 Unimplemented: Read as '0'

bit 3-0 SEL<3:0>: High/Low Voltage Detection Limit Selection bits Refer to Table 44-14 for voltage detection limits.

### TABLE 39-2: SUMMARY OF REGISTERS ASSOCIATED WITH HIGH/LOW-VOLTAGE DETECT MODULE

| Name     | Bit 7 | Bit 6 | Bit 5 | Bit 4 | Bit 3 | Bit 2 | Bit 1 | Bit 0 | Register<br>on Page |

|----------|-------|-------|-------|-------|-------|-------|-------|-------|---------------------|

| HLVDCON0 | EN    | -     | OUT   | RDY   | -     | -     | INTH  | INTL  | 657                 |

| HLVDCON1 | -     | -     | -     | -     |       | SEL<  | :3:0> |       | 658                 |

**Legend:** — = unimplemented, read as '0'. Shaded cells are unused by the HLVD module.

| MO\              | /SF                                       | Move Ind                                                                                                                                                                                          | Move Indexed to f                                                                                                                         |                                                                                                                                                                              |  |  |  |  |

|------------------|-------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|

| Synta            | ax:                                       | MOVSF [2                                                                                                                                                                                          | z <sub>s</sub> ], f <sub>d</sub>                                                                                                          |                                                                                                                                                                              |  |  |  |  |

| Oper             | ands:                                     | $\begin{array}{l} 0 \leq z_s \leq 12 \\ 0 \leq f_d \leq 408 \end{array}$                                                                                                                          |                                                                                                                                           |                                                                                                                                                                              |  |  |  |  |

| Oper             | ation:                                    | ((FSR2) + 2                                                                                                                                                                                       | $(z_s) \rightarrow f_d$                                                                                                                   |                                                                                                                                                                              |  |  |  |  |

| Status Affected: |                                           | None                                                                                                                                                                                              |                                                                                                                                           |                                                                                                                                                                              |  |  |  |  |

| 1st w            | oding:<br>vord (source)<br>word (destin.) | 1110<br>1111                                                                                                                                                                                      |                                                                                                                                           | zz zzzz <sub>s</sub><br>ff fff <sub>d</sub>                                                                                                                                  |  |  |  |  |

| Desc             | ription:                                  | moved to d<br>actual addr<br>determined<br>offset ' $z_s$ ' in<br>FSR2. The<br>register is s<br>'f <sub>d</sub> ' in the se<br>can be any<br>space (000<br>MOVSF has<br>range to the<br>memory (B | estination reg<br>ess of the sou<br>by adding the<br>the first word<br>address of th<br>specified by the<br>econd word. E<br>where in the | arce register is<br>e 7-bit literal<br>to the value of<br>e destination<br>to 12-bit literal<br>soth addresses<br>4096-byte data<br>destination<br>te space in<br>h 15). For |  |  |  |  |

| Word             | ls:                                       | 2                                                                                                                                                                                                 |                                                                                                                                           |                                                                                                                                                                              |  |  |  |  |

| Cycle            | es:                                       | 2                                                                                                                                                                                                 |                                                                                                                                           |                                                                                                                                                                              |  |  |  |  |

| QC               | ycle Activity:                            |                                                                                                                                                                                                   |                                                                                                                                           |                                                                                                                                                                              |  |  |  |  |

|                  | Q1                                        | Q2                                                                                                                                                                                                | Q3                                                                                                                                        | Q4                                                                                                                                                                           |  |  |  |  |

|                  | Decode                                    | Determine source addr                                                                                                                                                                             | Determine source addr                                                                                                                     | Read<br>source reg                                                                                                                                                           |  |  |  |  |

|                  | Decode                                    | No<br>operation<br>No dummy<br>read                                                                                                                                                               | No<br>operation                                                                                                                           | Write<br>register 'f'<br>(dest)                                                                                                                                              |  |  |  |  |

| <u>Exan</u>      | nple:                                     | MOVSF                                                                                                                                                                                             | [05h], REG                                                                                                                                | 2                                                                                                                                                                            |  |  |  |  |

|                  | Before Instruc                            | tion                                                                                                                                                                                              |                                                                                                                                           |                                                                                                                                                                              |  |  |  |  |

|                  | FSR2<br>Contents                          |                                                                                                                                                                                                   |                                                                                                                                           |                                                                                                                                                                              |  |  |  |  |

|                  | of 85h<br>REG2<br>After Instructio        | = 33<br>= 11                                                                                                                                                                                      |                                                                                                                                           |                                                                                                                                                                              |  |  |  |  |

|                  | FSR2                                      | = 80                                                                                                                                                                                              | h                                                                                                                                         |                                                                                                                                                                              |  |  |  |  |

|                  | Contents<br>of 85h<br>REG2                | = 33<br>= 33                                                                                                                                                                                      |                                                                                                                                           |                                                                                                                                                                              |  |  |  |  |

|                  |                                           |                                                                                                                                                                                                   |                                                                                                                                           |                                                                                                                                                                              |  |  |  |  |

|                                                                                               | MOVSFL                                                                                                                                                                                         | [z <sub>s</sub> ], f <sub>d</sub>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |                      |                                                 |  |  |  |  |

|-----------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------|-------------------------------------------------|--|--|--|--|

| Operands:                                                                                     |                                                                                                                                                                                                | $0 \le z_s \le 127$<br>$0 \le f_d \le 16383$                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |                      |                                                 |  |  |  |  |

| Operation:                                                                                    | ((FSR2) +                                                                                                                                                                                      |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |                      |                                                 |  |  |  |  |

| Status Affected:                                                                              | None                                                                                                                                                                                           | u u                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |                      |                                                 |  |  |  |  |

| Encoding:<br>1st word (opcode)<br>2nd word (source)<br>3rd word (full destin.<br>Description: | 0000<br>1111<br>1111<br>The conte                                                                                                                                                              | 0000<br>xxxz<br>ffff                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | 0110<br>zzzz<br>ffff | 0010<br>zz <sub>s</sub> ff<br>ffff <sub>d</sub> |  |  |  |  |

|                                                                                               | actual add<br>determine<br>offset 'z <sub>s</sub> ' i<br>FSR2 (14<br>destination<br>14-bit liter<br>Both addr<br>16 Kbyte of<br>The MOVS<br>PCL, TOS<br>destination<br>source ad<br>addressing | moved to destination register ' $f_d$ '. The<br>actual address of the source register is<br>determined by adding the 7-bit literal<br>offset ' $z_s$ ' in the first word to the value of<br>FSR2 (14 bits). The address of the<br>destination register is specified by the<br>14-bit literal ' $f_d$ ' in the second word.<br>Both addresses can be anywhere in the<br>16 Kbyte data space (0000h to 3FFFh).<br>The MOVSFL instruction cannot use the<br>PCL, TOSU, TOSH or TOSL as the<br>destination register. If the resultant<br>source address points to an indirect<br>addressing register, the value returned |                      |                                                 |  |  |  |  |

|                                                                                               | will be 00h                                                                                                                                                                                    | ۱.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |                      |                                                 |  |  |  |  |