Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

E·XFI

| Details                    |                                                                             |

|----------------------------|-----------------------------------------------------------------------------|

| Product Status             | Active                                                                      |

| Core Processor             | PIC                                                                         |

| Core Size                  | 8-Bit                                                                       |

| Speed                      | 64MHz                                                                       |

| Connectivity               | I <sup>2</sup> C, LINbus, SPI, UART/USART                                   |

| Peripherals                | Brown-out Detect/Reset, DMA, HLVD, POR, PWM, WDT                            |

| Number of I/O              | 25                                                                          |

| Program Memory Size        | 64KB (32K x 16)                                                             |

| Program Memory Type        | FLASH                                                                       |

| EEPROM Size                | 1K x 8                                                                      |

| RAM Size                   | 4K x 8                                                                      |

| Voltage - Supply (Vcc/Vdd) | 1.8V ~ 3.6V                                                                 |

| Data Converters            | A/D 24x12b; D/A 1x5b                                                        |

| Oscillator Type            | Internal                                                                    |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                           |

| Mounting Type              | Surface Mount                                                               |

| Package / Case             | 28-SOIC (0.295", 7.50mm Width)                                              |

| Supplier Device Package    | 28-SOIC                                                                     |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/pic18lf26k42-i-so |

|                            |                                                                             |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

| Ο                       |

|-------------------------|

| $\sim$                  |

| Ξ                       |

| 3                       |

|                         |

| .)                      |

|                         |

| N                       |

| 6                       |

| $\overline{\mathbf{N}}$ |

|                         |

|                         |

| 4                       |

| S                       |

| 4                       |

| 9                       |

| Ň                       |

| 4                       |

|                         |

| 5                       |

| 5                       |

| N N                     |

| 5                       |

| 6                       |

|                         |

| N                       |

| F                       |

|                         |

| 4                       |

| N                       |

\_

| 0/I  | 40-Pin PDIP | 44-Pin TQFP | 40-Pin UQFN | 44-Pin QFN | ADC                           | Voltage Reference | DAC              | Comparators      | Zero Cross Detect | I <sup>2</sup> C      | SPI                | UART                | WSQ                   | Timers/SMT                                                                                   | CCP and PWM         | CWG                   | СГС                   | NCO | Clock Reference (CLKR) | Interrupt-on-Change          | Basic          |

|------|-------------|-------------|-------------|------------|-------------------------------|-------------------|------------------|------------------|-------------------|-----------------------|--------------------|---------------------|-----------------------|----------------------------------------------------------------------------------------------|---------------------|-----------------------|-----------------------|-----|------------------------|------------------------------|----------------|

| RA0  | 2           | 19          | 17          | 19         | ANA0                          |                   | —                | C1IN0-<br>C2IN0- |                   | _                     | _                  | _                   | —                     | —                                                                                            |                     | -                     | CLCIN0 <sup>(1)</sup> | -   | _                      | IOCA0                        | _              |

| RA1  | 3           | 20          | 18          | 20         | ANA1                          | —                 | —                | C1IN1-<br>C2IN1- | —                 | —                     | —                  | —                   | _                     | —                                                                                            | -                   | —                     | CLCIN1 <sup>(1)</sup> | -   | —                      | IOCA1                        | —              |

| RA2  | 4           | 21          | 19          | 21         | ANA2                          | VREF-             | DAC1OUT1         | C1IN0+<br>C2IN0+ |                   | -                     | -                  | -                   | —                     | —                                                                                            | -                   | -                     | -                     | -   | -                      | IOCA2                        | —              |

| RA3  | 5           | 22          | 20          | 22         | ANA3                          | VREF+             | _                | C1IN1+           | _                 | _                     | _                  | _                   | MDCARL <sup>(1)</sup> | _                                                                                            |                     | _                     | _                     |     | _                      | IOCA3                        | _              |

| RA4  | 6           | 23          | 21          | 23         | ANA4                          | _                 | _                | _                | _                 | _                     | _                  | _                   | MDCARH <sup>(1)</sup> | T0CKI <sup>(1)</sup>                                                                         | -                   | _                     | _                     | _   | _                      | IOCA4                        | _              |

| RA5  | 7           | 24          | 22          | 24         | ANA5                          | -                 | _                | _                | _                 | _                     | SS1 <sup>(1)</sup> | _                   | MDSRC <sup>(1)</sup>  | _                                                                                            | _                   | _                     | _                     | _   | _                      | IOCA5                        | —              |

| RA6  | 14          | 31          | 29          | 33         | ANA6                          | _                 | —                | —                | _                 | —                     | —                  | —                   | —                     | —                                                                                            | -                   | —                     | —                     | —   | —                      | IOCA6                        | OSC2<br>CLKOUT |

| RA7  | 13          | 30          | 28          | 32         | ANA7                          | _                 | —                | —                | _                 | —                     | —                  | —                   | —                     | —                                                                                            | -                   | —                     | —                     | —   | —                      | IOCA7                        | OSC1<br>CLKIN  |

| RB0  | 33          | 8           | 8           | 9          | ANB0                          | -                 | —                | C2IN1+           | ZCD               | —                     | —                  | —                   | —                     | —                                                                                            | CCP4 <sup>(1)</sup> | CWG1IN <sup>(1)</sup> | -                     | -   | —                      | INT0 <sup>(1)</sup><br>IOCB0 | —              |

| RB1  | 34          | 9           | 9           | 10         | ANB1                          |                   | —                | C1IN3-<br>C2IN3- | —                 | SCL2 <sup>(3,4)</sup> | —                  | —                   | —                     | —                                                                                            | _                   | CWG2IN <sup>(1)</sup> | -                     | —   | —                      | INT1 <sup>(1)</sup><br>IOCB1 | —              |

| RB2  | 35          | 10          | 10          | 11         | ANB2                          | -                 | —                | —                | —                 | SDA2 <sup>(3,4)</sup> | —                  | —                   | -                     | —                                                                                            | -                   | CWG3IN <sup>(1)</sup> | -                     | -   | —                      | INT2 <sup>(1)</sup><br>IOCB2 | —              |

| RB3  | 36          | 11          | 11          | 12         | ANB3                          | _                 | —                | C1IN2-<br>C2IN2- | —                 | -                     | -                  | -                   | -                     | —                                                                                            | _                   | -                     | -                     | _   | -                      | IOCB3                        | —              |

| RB4  | 37          | 14          | 12          | 14         | ANB4<br>ADCACT <sup>(1)</sup> | _                 | —                | —                | —                 | -                     | -                  | -                   | —                     | T5G <sup>(1)</sup>                                                                           | _                   | -                     | -                     | -   | -                      | IOCB4                        | -              |

| RB5  | 38          | 15          | 13          | 15         | ANB5                          | -                 | _                | _                | _                 | -                     | _                  | _                   | _                     | T1G <sup>(1)</sup>                                                                           | CCP3 <sup>(1)</sup> | _                     | -                     | _   | _                      | IOCB5                        | _              |

| RB6  | 39          | 16          | 14          | 16         | ANB6                          | _                 | _                | —                | _                 | _                     | _                  | CTS2 <sup>(1)</sup> | _                     | -                                                                                            | _                   | _                     | CLCIN2 <sup>(1)</sup> | _   | —                      | IOCB6                        | ICSPCLK        |

| RB7  | 40          | 17          | 15          | 17         | ANB7                          | _                 | DAC1OUT2         | _                | _                 | _                     | _                  | RX2 <sup>(1)</sup>  | _                     | T6IN <sup>(1)</sup>                                                                          | _                   | _                     | CLCIN3 <sup>(1)</sup> |     | _                      | IOCB7                        | ICSPDAT        |

| RC0  | 15          | 32          | 30          | 34         | ANC0                          |                   | _                | —                | —                 | -                     | —                  | —                   | —                     | T1CKI <sup>(1)</sup><br>T3CKI <sup>(1)</sup><br>T3G <sup>(1)</sup><br>SMTWIN1 <sup>(1)</sup> | _                   | —                     | _                     | _   | —                      | IOCC0                        | SOSCO          |

| RC1  | 16          | 35          | 31          | 35         | ANC1                          |                   | —                | _                | _                 | —                     | _                  | _                   | —                     | SMTSIG1 <sup>(1)</sup>                                                                       | CCP2 <sup>(1)</sup> | _                     | _                     | _   | _                      | IOCC1                        | SOSCI          |

| RC2  | 17          | 36          | 32          | 36         | ANC2                          | —                 | _                | —                | _                 | _                     | _                  | —                   | _                     | T5CKI <sup>(1)</sup>                                                                         | CCP1 <sup>(1)</sup> | _                     | —                     |     | —                      | IOCC2                        | —              |

| Note | 1:          | This        | is a F      | PS re      | mappable inpu                 | t signal. Th      | e input function | may be me        | oved fro          | om the default        | location sh        | own to one          | of several othe       | er PORTx pins.                                                                               |                     |                       |                       |     |                        |                              |                |

2:

40/44-PIN ALLOCATION TABLE FOR PIC18(L)F4XK42

All output signals shown in this row are PPS remappable. This is a bidirectional signal. For normal module operation, the firmware should map this signal to the same pin in both the PPS input and PPS output registers. 3:

These pins can be configured for I<sup>2</sup>C and SMB<sup>TM</sup> 3.0/2.0 logic levels; The SCLx/SDAx signals may be assigned to any of the RB1/RB2/RC3/RC4/RD0/RD1 pins. PPS assignments to the other pins (e.g., RA5) will operate, but input logic levels will be standard TTL/ST as selected by the INLVL register, instead of the I<sup>2</sup>C specific or SMBus input buffer thresholds. 4:

TABLE 2:

#### TABLE 4-3: SPECIAL FUNCTION REGISTER MAP FOR PIC18(L)F26/27/45/46/47/55/56/57K42 DEVICES BANK 64

|         |            |       |            | _     |            | _     |            |       |          |       |   |       |   |       |   |

|---------|------------|-------|------------|-------|------------|-------|------------|-------|----------|-------|---|-------|---|-------|---|

| 40FFh   | —          | 40DFh |            | 40BFh | —          | 409Fh | —          | 407Fh | _        | 405Fh | — | 403Fh |   | 401Fh | _ |

| 40FEh   | —          | 40DEh |            | 40BEh | _          | 409Eh | _          | 407Eh | _        | 405Eh | — | 403Eh |   | 401Eh | _ |

| 40FDh   | _          | 40DDh | T6PR_M2    | 40BDh | ADRESH_M2  | 409Dh | _          | 407Dh | _        | 405Dh | — | 403Dh | - | 401Dh | _ |

| 40FCh   | _          | 40DCh | PWM5DCH_M2 | 40BCh | ADRESL_M2  | 409Ch | _          | 407Ch | _        | 405Ch | — | 403Ch | - | 401Ch | _ |

| 40FBh   | TMR5H_M1   | 40DBh | PWM5DCL_M2 | 40BBh | ADPCH_M2   | 409Bh | _          | 407Bh | _        | 405Bh | — | 403Bh | - | 401Bh | _ |

| 40FAh   | TMR5L_M1   | 40DAh | T6PR_M1    | 40BAh | ADCLK_M1   | 409Ah | —          | 407Ah | _        | 405Ah | — | 403Ah |   | 401Ah | _ |

| 40F9h   | TMR3H_M1   | 40D9h | CCPR1H_M2  | 40B9h | ADACT_M1   | 4099h | —          | 4079h | _        | 4059h | — | 4039h |   | 4019h | _ |

| 40F8h   | TMR3L_M1   | 40D8h | CCPR1L_M2  | 40B8h | ADREF_M1   | 4098h | —          | 4078h | _        | 4058h | — | 4038h |   | 4018h | _ |

| 40F7h   | TMR1H_M1   | 40D7h | T4PR_M4    | 40B7h | ADCON3_M1  | 4097h | —          | 4077h | _        | 4057h | — | 4037h |   | 4017h | _ |

| 40F6h   | TMR1L_M1   | 40D6h | PWM8DCH_M1 | 40B6h | ADCON2_M1  | 4096h | ADRESH_M1  | 4076h | _        | 4056h | — | 4036h |   | 4016h | _ |

| 40F5h   | —          | 40D5h | PWM8DCL_M1 | 40B5h | ADCON1_M1  | 4095h | ADRESL_M1  | 4075h | _        | 4055h | — | 4035h |   | 4015h | _ |

| 40F4h   | —          | 40D4h | T4PR_M3    | 40B4h | ADCON0_M1  | 4094h | ADPCH_M1   | 4074h | _        | 4054h | — | 4034h |   | 4014h | _ |

| 40F3h   | —          | 40D3h | PWM7DCH_M1 | 40B3h | ADCAP_M2   | 4093h | ADCAP_M1   | 4073h | _        | 4053h | — | 4033h | _ | 4013h | — |

| 40F2h   | —          | 40D2h | PWM7DCL_M1 | 40B2h | ADACQH_M2  | 4092h | ADACQH_M1  | 4072h | —        | 4052h | — | 4032h | — | 4012h | — |

| 40F1h   | —          | 40D1h | T4PR_M2    | 40B1h | ADACQL_M2  | 4091h | ADACQL_M1  | 4071h | —        | 4051h | — | 4031h | — | 4011h | — |

| 40F0h   | —          | 40D0h | CCPR4H_M1  | 40B0h | ADPREVH_M2 | 4090h | ADPREVH_M1 | 4070h | —        | 4050h | — | 4030h | — | 4010h | — |

| 40EFh P | WM8DCH_M2  | 40CFh | CCPR4L_M1  | 40AFh | ADPREVL_M2 | 408Fh | ADPREVL_M1 | 406Fh | —        | 404Fh | — | 402Fh | — | 400Fh | — |

| 40EEh P | WM8DCL_M2  | 40CEh | T4PR_M1    | 40AEh | ADRPT_M2   | 408Eh | ADRPT_M1   | 406Eh | —        | 404Eh | — | 402Eh | — | 400Eh | — |

| 40EDh P | WM7DCH_M2  | 40CDh | CCPR3H_M1  | 40ADh | ADCNT_M2   | 408Dh | ADCNT_M1   | 406Dh | —        | 404Dh | — | 402Dh | — | 400Dh | — |

| 40ECh P | WM7DCL_M2  | 40CCh | CCPR3L_M1  | 40ACh | ADACCU_M2  | 408Ch | ADACCU_M1  | 406Ch | —        | 404Ch | — | 402Ch | — | 400Ch | — |

| 40EBh P | WM6DCH_M2  | 40CBh | T2PR_M3    | 40ABh | ADACCH_M2  | 408Bh | ADACCH_M1  | 406Bh | —        | 404Bh | — | 402Bh | — | 400Bh | — |

|         | WM6DCL_M2  | 40CAh | PWM6DCH_M1 | 40AAh | ADACCL_M2  | 408Ah | ADACCL_M1  | 406Ah | _        | 404Ah | — | 402Ah |   | 400Ah | _ |

| 40E9h P | WM5DCH_M3  | 40C9h | PWM6DCL_M1 | 40A9h | ADFLTRH_M2 | 4089h | ADFLTRH_M1 | 4069h | _        | 4049h | — | 4029h |   | 4009h | _ |

| 40E8h P | PWM5DCL_M3 | 40C8h | T2PR_M2    | 40A8h | ADFLTRL_M2 | 4088h | ADFLTRL_M1 | 4068h | _        | 4048h | — | 4028h |   | 4008h | _ |

| 40E7h ( | CCPR4H_M2  | 40C7h | PWM5DCH_M1 | 40A7h | ADSTPTH_M2 | 4087h | ADSTPTH_M1 | 4067h | _        | 4047h | — | 4027h | — | 4007h | — |

| 40E6h   | CCPR4L_M2  | 40C6h | PWM5DCL_M1 | 40A6h | ADSTPTL_M2 | 4086h | ADSTPTL_M1 | 4066h | _        | 4046h | — | 4026h | — | 4006h | — |

| 40E5h ( | CCPR3H_M2  | 40C5h | T2PR_M2    | 40A5h | ADERRH_M2  | 4085h | ADERRH_M1  | 4065h | _        | 4045h | — | 4025h | — | 4005h | — |

| 40E4h   | CCPR3L_M2  | 40C4h | CCPR2H_M1  | 40A4h | ADERRL_M2  | 4084h | ADERRL_M1  | 4064h | _        | 4044h | — | 4024h | _ | 4004h |   |

| 40E3h   | CCPR2H_M2  | 40C3h | CCPR2L_M1  | 40A3h | ADUTHH_M2  | 4083h | ADUTHH_M1  | 4063h | IOCEF_M1 | 4043h | _ | 4023h | _ | 4003h | — |

| 40E2h   | CCPR2L_M2  | 40C2h | T2PR_M1    | 40A2h | ADUTHL_M2  | 4082h | ADUTHL_M1  | 4062h | IOCCF_M1 | 4042h | — | 4022h | — | 4002h |   |

| 40E1h   | CCPR1H_M3  | 40C1h | CCPR1H_M1  | 40A1h | ADLTHH_M2  | 4081h | ADLTHH_M1  | 4061h | IOCBF_M1 | 4041h | — | 4021h | — | 4001h |   |

| 40E0h   | CCPR1L_M3  | 40C0h | CCPR1L_M1  | 40A0h | ADLTHL_M2  | 4080h | ADLTHL_M1  | 4060h | IOCAF_M1 | 4040h | _ | 4020h | _ | 4000h | _ |

Note 1: Addresses in Bank 64 are accessible ONLY through DMA Source and Destination Address Registers. CPU does not have access to registers in Bank 64.

| REGISIER   | 5-12:         | REVISIC                            | IN ID: REVI      |                       | GIÐIER             |                |                   |                |

|------------|---------------|------------------------------------|------------------|-----------------------|--------------------|----------------|-------------------|----------------|

| R          |               | R                                  | R                | R                     | R                  | R              | R                 | R              |

| 1          |               | 0                                  | 1                | 0                     |                    | MJR            | REV<5:2>          |                |

| bit 15     |               |                                    |                  |                       |                    |                |                   | bit 8          |

|            |               |                                    |                  |                       |                    |                |                   |                |

| R          |               | R                                  | R                | R                     | R                  | R              | R                 | R              |

| MJR        | REV<1:        | 0>                                 |                  |                       | MNRR               | EV<5:0>        |                   |                |

| bit 7      |               |                                    |                  |                       |                    |                |                   | bit 0          |

|            |               |                                    |                  |                       |                    |                |                   |                |

| Legend:    |               |                                    |                  |                       |                    |                |                   |                |

| R = Readab | le bit        |                                    | '1' = Bit is set |                       | 0' = Bit is clea   | ared           | x = Bit is unki   | nown           |

| bit 15-12  |               | <b>d as</b> '1010<br>se bits are f |                  | <b>e</b> '1010' for a | Ill devices in thi | s family.      |                   |                |

| bit 11-6   | The:<br>etc.) | se bits are ι                      |                  |                       | sion. A major re   | evision is ind | cated by revisior | n (A0, B0, C0, |

| bit 5-0    | MNF           | RREV<5:0>                          | : Minor Revis    | ion ID bits           |                    |                |                   |                |

#### REGISTER 5-12: REVISION ID: REVISION ID REGISTER

These bits are used to identify a minor revision.

**Revision A0 =** 0b00 0000

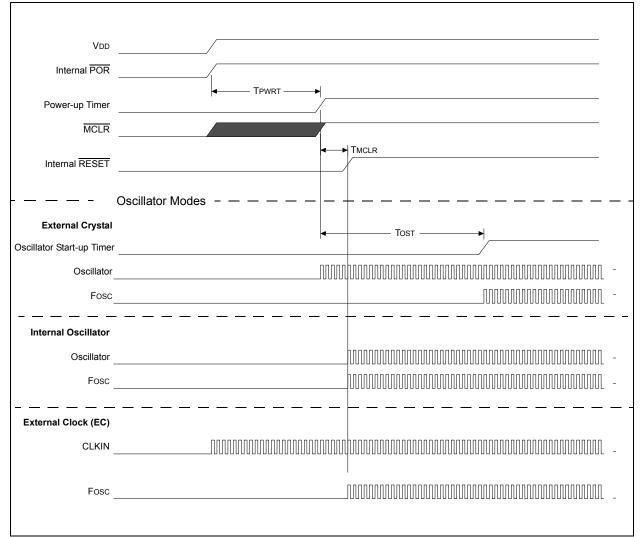

#### 6.11 Start-up Sequence

Upon the release of a POR or BOR, the following must occur before the device will begin executing:

- 1. Power-up Timer runs to completion (if enabled).

- 2. Oscillator start-up timer runs to completion (if required for selected oscillator source).

- 3. MCLR must be released (if enabled).

The total time-out will vary based on oscillator configuration and Power-up Timer configuration. See Section 7.0 "Oscillator Module (with Fail-Safe Clock Monitor)" for more information.

The Power-up Timer and oscillator start-up timer run independently of MCLR Reset. If MCLR is kept low long enough, the Power-up Timer and oscillator Start-up Timer will expire. Upon bringing MCLR high, the device will begin execution after 10 Fosc cycles (see Figure 6-4). This is useful for testing purposes or to synchronize more than one device operating in parallel.

#### FIGURE 6-4: RESET START-UP SEQUENCE

#### 8.5 **Register Definitions: Reference Clock**

Long bit name prefixes for the Reference Clock peripherals are shown below. Refer to **Section 1.3.2.2 "Long Bit Names**" for more information.

| Peripheral | Bit Name Prefix |

|------------|-----------------|

| CLKR       | CLKR            |

#### REGISTER 8-1: CLKRCON: REFERENCE CLOCK CONTROL REGISTER

| R/W-0/0 | U-0 | U-0 | R/W-1/1 | R/W-0/0 | R/W-0/0 | R/W-0/0  | R/W-0/0 |

|---------|-----|-----|---------|---------|---------|----------|---------|

| EN      | —   | _   | DC<1:0> |         |         | DIV<2:0> |         |

| bit 7   |     |     |         |         |         |          | bit 0   |

| Legend:              |                      |                                                       |

|----------------------|----------------------|-------------------------------------------------------|

| R = Readable bit     | W = Writable bit     | U = Unimplemented bit, read as '0'                    |

| u = Bit is unchanged | x = Bit is unknown   | -n/n = Value at POR and BOR/Value at all other Resets |

| '1' = Bit is set     | '0' = Bit is cleared |                                                       |

| bit 7   | EN: Reference Clock Module Enable bit<br>1 = Reference clock module enabled |

|---------|-----------------------------------------------------------------------------|

|         | 0 = Reference clock module is disabled                                      |

| bit 6-5 | Unimplemented: Read as '0'                                                  |

| bit 4-3 | DC<1:0>: Reference Clock Duty Cycle bits <sup>(1)</sup>                     |

|         | 11 = Clock outputs duty cycle of 75%                                        |

|         | 10 = Clock outputs duty cycle of 50%                                        |

|         | 01 = Clock outputs duty cycle of 25%                                        |

|         | 00 = Clock outputs duty cycle of 0%                                         |

| bit 2-0 | DIV<2:0>: Reference Clock Divider bits                                      |

|         | 111 = Base clock value divided by 128                                       |

|         | 110 = Base clock value divided by 64                                        |

|         | 101 = Base clock value divided by 32                                        |

|         | 100 = Base clock value divided by 16                                        |

|         | 011 = Base clock value divided by 8                                         |

|         | 010 = Base clock value divided by 4                                         |

|         | 001 = Base clock value divided by 2                                         |

|         | 000 = Base clock value                                                      |

|         |                                                                             |

**Note 1:** Bits are valid for reference clock divider values of two or larger, the base clock cannot be further divided.

| R-0/0            | R-0/0                           | U-0 | U-0 | U-0 | U-0                         | U-0 | U-0   |  |  |

|------------------|---------------------------------|-----|-----|-----|-----------------------------|-----|-------|--|--|

| STAT             | STAT<1:0>                       |     |     |     |                             |     |       |  |  |

| bit 7            |                                 |     |     |     |                             |     | bit 0 |  |  |

|                  |                                 |     |     |     |                             |     |       |  |  |

| Legend:          |                                 |     |     |     |                             |     |       |  |  |

| HC = Bit is clea | HC = Bit is cleared by hardware |     |     |     |                             |     |       |  |  |

| D - Deedekle     | L 11                            |     | L:4 |     | an a material la it was a d | (0) |       |  |  |

#### REGISTER 9-2: INTCON1: INTERRUPT CONTROL REGISTER 1

# HC = Bit is cleared by hardwareR = Readable bitW = Writable bitu = Bit is unchangedx = Bit is unknown'1' = Bit is set'0' = Bit is clearedq = Value depends on condition

#### bit 7-6 STAT<1:0>: Interrupt State Status bits

11 = High priority ISR executing, high priority interrupt was received while a low priority ISR was executing

10 = High priority ISR executing, high priority interrupt was received in main routine

01 = Low priority ISR executing, low priority interrupt was received in main routine

00 = Main routine executing

bit 5-0 Unimplemented: Read as '0'

| IABLE 15-2:          | DMAXSIRQ AND DMAXA |                    |  |  |  |  |

|----------------------|--------------------|--------------------|--|--|--|--|

| DMAxSIRQ<br>DMAxAIRQ | Trigger<br>Source  | Level<br>Triggered |  |  |  |  |

| 0                    | Reserved           |                    |  |  |  |  |

| 1                    | LVD                | No                 |  |  |  |  |

| 2                    | OSF                | No                 |  |  |  |  |

| 3                    | CSW                | No                 |  |  |  |  |

| 4                    | NVM                | No                 |  |  |  |  |

| 5                    | SCAN               | No                 |  |  |  |  |

| 6                    | CRC                | No                 |  |  |  |  |

| 7                    | IOC                | Yes                |  |  |  |  |

| 8                    | INT0               | No                 |  |  |  |  |

| 9                    | ZCD                | No                 |  |  |  |  |

| 10                   | AD                 | No                 |  |  |  |  |

| 11                   | ADT                | No                 |  |  |  |  |

| 12                   | CMP1               | No                 |  |  |  |  |

| 13                   | SMT1               | No                 |  |  |  |  |

| 14                   | SMT1PRA            | No                 |  |  |  |  |

| 15                   | SMT1PWA            | No                 |  |  |  |  |

| 16                   | DMA1SCNT           | No                 |  |  |  |  |

| 17                   | DMA1DCNT           | No                 |  |  |  |  |

| 18                   | DMA10R             | No                 |  |  |  |  |

| 19                   | DMA1A              | No                 |  |  |  |  |

| 20                   | SPI1RX             | Yes                |  |  |  |  |

| 21                   | SPI1TX             | Yes                |  |  |  |  |

| 22                   | SPI1               | Yes                |  |  |  |  |

| 23                   | I2C1RX             | Yes                |  |  |  |  |

| 24                   | I2C1TX             | Yes                |  |  |  |  |

| 25                   | I2C1               | Yes                |  |  |  |  |

| 26                   | I2C1E              | Yes                |  |  |  |  |

| 27                   | U1RX               | Yes                |  |  |  |  |

| 28                   | U1TX               | Yes                |  |  |  |  |

| 29                   | U1E                | Yes                |  |  |  |  |

| 30                   | U1                 | No                 |  |  |  |  |

| 31                   | TMR0               | No                 |  |  |  |  |

| 32                   | TMR1               | No                 |  |  |  |  |

| 33                   | TMR1G              | No                 |  |  |  |  |

| 34                   | TMR2               | No                 |  |  |  |  |

| 35                   | CCP1               | No                 |  |  |  |  |

| 36                   | Reserved           |                    |  |  |  |  |

| 37                   | NCO                | No                 |  |  |  |  |

| 38                   | CWG1               | No                 |  |  |  |  |

| 39                   | CLC1               | No                 |  |  |  |  |

| 40                   | INT1               | No                 |  |  |  |  |

| 41                   | CMP2               | No                 |  |  |  |  |

| L                    |                    | 1]                 |  |  |  |  |

| SOURCES              |                   | 1                  |

|----------------------|-------------------|--------------------|

| DMAxSIRQ<br>DMAxAIRQ | Trigger<br>Source | Level<br>Triggered |

| 42                   | DMA2SCNT          | No                 |

| 43                   | DMA2DCNT          | No                 |

| 44                   | DMA2OR            | No                 |

| 45                   | DMA2A             | No                 |

| 46                   | I2C2RX            | Yes                |

| 47                   | I2C2TX            | Yes                |

| 48                   | I2C2              | Yes                |

| 49                   | I2C2E             | Yes                |

| 50                   | U2RX              | Yes                |

| 51                   | U2TX              | Yes                |

| 52                   | U2E               | Yes                |

| 53                   | U2                | No                 |

| 54                   | TMR3              | No                 |

| 55                   | TMR3G             | No                 |

| 56                   | TMR4              | No                 |

| 57                   | CCP2              | No                 |

| 58                   | Reserved          |                    |

| 59                   | CWG2              | No                 |

| 60                   | CLC2              | No                 |

| 61                   | INT2              | No                 |

| 62                   | Reserved          |                    |

| 63                   | Reserved          |                    |

| 64                   | Reserved          |                    |

| 65                   | Reserved          |                    |

| 66                   | Reserved          |                    |

| 67                   | Reserved          |                    |

| 68                   | Reserved          |                    |

| 69                   | Reserved          |                    |

| 70                   | TMR5              | No                 |

| 71                   | TMR5G             | No                 |

| 72                   | TMR6              | No                 |

| 73                   | CCP3              | No                 |

| 74                   | CWG3              | No                 |

| 75                   | CLC3              | No                 |

| 76                   | Reserved          |                    |

| 77                   | Reserved          |                    |

| 78                   | Reserved          |                    |

| 79                   | Reserved          |                    |

| 80                   | CCP4              | No                 |

| 81                   | CLC4              | No                 |

| 82                   | Reserved          |                    |

| _<br>127             |                   |                    |

| 121                  |                   |                    |

Note 1: All trigger sources that are not Level-triggered are Edge-triggered.

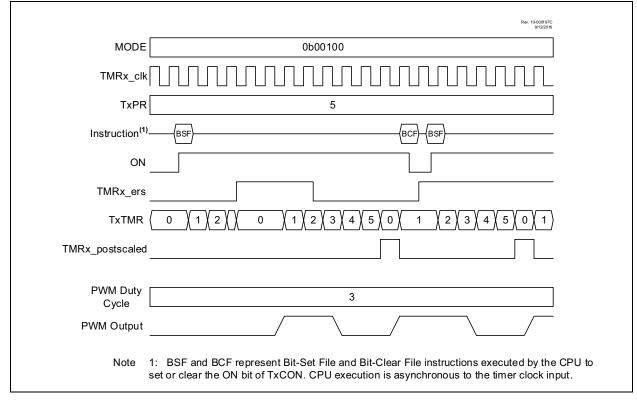

### 22.5.3 EDGE-TRIGGERED HARDWARE LIMIT MODE

In Hardware Limit mode the timer can be reset by the TMRx\_ers external signal before the timer reaches the period count. Three types of Resets are possible:

- Reset on rising or falling edge (MODE<4:0> = 00011)

- Reset on rising edge (MODE<4:0> = 0010)

- Reset on falling edge (MODE<4:0> = 00101)

When the timer is used in conjunction with the CCP in PWM mode then an early Reset shortens the period and restarts the PWM pulse after a two clock delay. Refer to Figure 22-6.

#### FIGURE 22-6: EDGE TRIGGERED HARDWARE LIMIT MODE TIMING DIAGRAM (MODE=00100)

#### **REGISTER 26-3:** CWGxCLK: CWGx CLOCK INPUT SELECTION REGISTER

| CS<br>bit 7 bit 0 | U-0   | U-0 | U-0 | U-0 | U-0 | U-0 | U-0 | R/W-0/0 |

|-------------------|-------|-----|-----|-----|-----|-----|-----|---------|

| bit 7 bit 0       | —     | _   | _   | _   | _   | —   | _   | CS      |

|                   | bit 7 |     |     |     |     |     |     | bit 0   |

| Legend:              |                      |                                                       |

|----------------------|----------------------|-------------------------------------------------------|

| R = Readable bit     | W = Writable bit     | U = Unimplemented bit, read as '0'                    |

| u = Bit is unchanged | x = Bit is unknown   | -n/n = Value at POR and BOR/Value at all other Resets |

| '1' = Bit is set     | '0' = Bit is cleared | q = Value depends on condition                        |

#### bit 7-1 Unimplemented: Read as '0'

bit 0

CS: CWG Clock Source Selection bits

| CS | CWG1                    | CWG2                    | CWG3                    |

|----|-------------------------|-------------------------|-------------------------|

| 1  | HFINTOSC <sup>(1)</sup> | HFINTOSC <sup>(1)</sup> | HFINTOSC <sup>(1)</sup> |

| 0  | Fosc                    | Fosc                    | Fosc                    |

Note 1: HFINTOSC remains operating during Sleep.

#### 30.0 DATA SIGNAL MODULATOR (DSM) MODULE

The Data Signal Modulator (DSM) is a peripheral which allows the user to mix a data stream, also known as a modulator signal, with a carrier signal to produce a modulated output.

Both the carrier and the modulator signals are supplied to the DSM module either internally, from the output of a peripheral, or externally through an input pin.

The modulated output signal is generated by performing a logical "AND" operation of both the carrier and modulator signals and then provided to the MDOUT pin.

The carrier signal is comprised of two distinct and separate signals. A carrier high (CARH) signal and a carrier low (CARL) signal. During the time in which the modulator (MOD) signal is in a logic high state, the DSM mixes the carrier high signal with the modulator signal. When the modulator signal is in a logic low state, the DSM mixes the carrier low signal with the modulator signal.

Using this method, the DSM can generate the following types of Key Modulation schemes:

- Frequency-Shift Keying (FSK)

- Phase-Shift Keying (PSK)

- On-Off Keying (OOK)

Additionally, the following features are provided within the DSM module:

- Carrier Synchronization

- Carrier Source Polarity Select

- Programmable Modulator Data

- · Modulated Output Polarity Select

- Peripheral Module Disable, which provides the ability to place the DSM module in the lowest power consumption mode

Figure 30-1 shows a Simplified Block Diagram of the Data Signal Modulator peripheral.

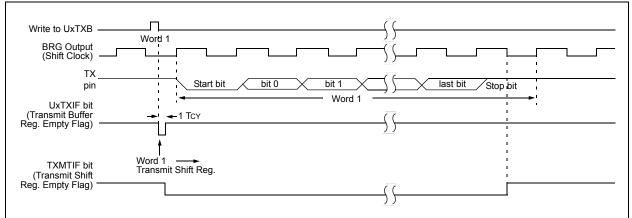

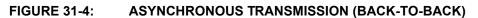

#### 31.2.1.8 Asynchronous Transmission Setup

- Initialize the UxBRGH, UxBRGL register pair and the BRGS bit to achieve the desired baud rate (see Section 31.17 "UART Baud Rate Generator (BRG)").

- 2. Set the MODE<3:0> bits to the desired asynchronous mode.

- 3. Set TXPOL bit if inverted TX output is desired.

- 4. Enable the asynchronous serial port by setting the ON bit.

- 5. Enable the transmitter by setting the TXEN control bit. This will cause the UxTXIF interrupt flag to be set.

- 6. If the device has PPS, configure the desired I/O pin RxyPPS register with the code for TX output.

- 7. If interrupts are desired, set the UxTXIE interrupt enable bit in the respective PIE register. An interrupt will occur immediately provided that the GIE bits in the INTCON0 register are also set.

- 8. Write one byte of data into the UxTXB register. This will start the transmission.

- 9. Subsequent bytes may be written when the UxTXIF bit is '1'.

#### FIGURE 31-3: ASYNCHRONOUS TRANSMISSION

#### 33.7 Register Definitions: I<sup>2</sup>C Control

This section defines all the registers associated with the control and status of the  $I^2C$  bus.

#### REGISTER 33-1: I2CxCON0: I<sup>2</sup>C CONTROL REGISTER 0

| R/W-0               | R/W-0                                                                                                             | R/W/HC/HS-0                                                                                                                                                                                      | R/C/HS/HC-0                                                                                                 | R-0                                                   | R/W-0           | R/W-0            | R/W-0       |

|---------------------|-------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------|-------------------------------------------------------|-----------------|------------------|-------------|

| EN <sup>(1,2)</sup> | RSEN                                                                                                              | S                                                                                                                                                                                                | CSTR <sup>(3)</sup>                                                                                         | MDR                                                   |                 | MODE <2:0>       |             |

| bit 7               |                                                                                                                   |                                                                                                                                                                                                  |                                                                                                             |                                                       |                 |                  | bit (       |

| Legend:             |                                                                                                                   |                                                                                                                                                                                                  |                                                                                                             |                                                       |                 |                  |             |

| R = Readable        | e bit                                                                                                             | W = Writable bi                                                                                                                                                                                  | t                                                                                                           | U = Unimple                                           | mented bit, rea | <b>d as</b> '0'  |             |

| u = Bit is unc      | hanged                                                                                                            | x = Bit is unkno                                                                                                                                                                                 | wn                                                                                                          | -n/n = Value                                          | at POR and BC   | R/Value at all o | ther Resets |

| ʻ1' = Bit is se     | t                                                                                                                 | '0' = Bit is clear                                                                                                                                                                               | ed                                                                                                          | HS = Hardwa                                           | are set HC =    | Hardware clea    | r           |

| bit 7               | 1 = Enables                                                                                                       | ule Enable bit<br>the I <sup>2</sup> C module <sup>(1,2</sup><br>s the I <sup>2</sup> C module.                                                                                                  | )                                                                                                           |                                                       |                 |                  |             |

| bit 6               | 1 = When (I                                                                                                       | art Enable bit (Only<br>2CCNT = 0 or ACK<br>2CCNT = 0 or ACK                                                                                                                                     | STAT = 1), on 9th                                                                                           | falling SCL se                                        |                 | Stop condition   |             |

| bit 5               | When MMA =       1 =     Set b       0 =     Clea       When (MMA)     1 =       1 =     Set b       0 =     Clea | art/Restart bit (Only<br>= 0<br>by user set of STAF<br>red by hardware af<br>= 1 & MDR = 1 & p<br>by user set of STAF<br>red by hardware af<br>to I2CTXB or set h                                | RT bit or write to 12<br>ter sending Start<br>ause_for_Restart<br>T bit or write to 12<br>ter sending Resta | 2CTXB, waits fo<br>( <u>)</u><br>2CTXB, resume<br>Irt |                 | •                |             |

| bit 4               | 1 = Clock is                                                                                                      | Clock Stretching b<br>held low (clock stre<br>clocking, SCL contr                                                                                                                                | etching)                                                                                                    |                                                       |                 |                  |             |

|                     | - User<br><u>SMA = 1 and</u><br>- Set b<br>- User<br><u>when ADRIE</u><br>- Set b                                 | y hardware on 7th t<br>must read byte I2C<br>TXBE = <u>1</u> and I2C<br>y hardware on 8th t<br>must write byte to I<br><u>is set</u> <sup>(4)</sup><br>y hardware on 8th t<br>must clear CSTR to | RXB to release S<br>CNT!= 0<br>alling SCL edge<br>2CTXB to release<br>alling SCL edge o                     | SCL                                                   | eived address   |                  |             |

|                     | - Set b<br>- User<br>SMA = 1 & A<br>- Set b                                                                       | y hardware on 8th t<br>must clear CSTR to                                                                                                                                                        | o release SCL<br>alling SCL edge                                                                            | of received data                                      | i byte          |                  |             |

| R/W-1 | U-0   |

|-------|-------|-------|-------|-------|-------|-------|-------|

| ADR14 | ADR13 | ADR12 | ADR11 | ADR10 | ADR9  | ADR8  |       |

| bit 7 |       |       |       |       |       |       | bit 0 |

| R/W-1 | U-0   |

| ADR7  | ADR6  | ADR5  | ADR4  | ADR3  | ADR2  | ADR1  | _     |

| bit 7 |       |       |       |       |       |       | bit 0 |

#### REGISTER 33-13: I2CxADR1: I<sup>2</sup>C ADDRESS 1 REGISTER

| Legend:              |                      |                                                       |

|----------------------|----------------------|-------------------------------------------------------|

| R = Readable bit     | W = Writable bit     | U = Unimplemented bit, read as '0'                    |

| u = Bit is unchanged | x = Bit is unknown   | -n/n = Value at POR and BOR/Value at all other Resets |

| '1' = Bit is set     | '0' = Bit is cleared | HS = Hardware set HC = Hardware clear                 |

bit 7-1 **ADR[7-1]:** Address or Divider bits

MODE<2:0> = 000 | 110 - 7-bit Slave/Multi-Master Modes ADR<7:1>:7-bit Slave Address

ADR<0>: Unused in this mode; bit state is a don't care

MODE<2:0> = 001 | 111 - 7-bit Slave/Multi-Master modes w/Masking

MSK0<7:1>:7-bit Slave Address

MSK0<0>: Unused in this mode; bit state is a don't care

MODE<2:0> = 01x - 10-bit Slave Modes

ADR<14-10>:Bit pattern sent by master is fixed by I<sup>2</sup>C specification and must be equal to '11110'. However, these bit values are compared by hardware to the received data to determine a match. It is up to the user to set these bits as '11110'.

ADR<9-8>:Two Most Significant bits of 10-bit address

bit 0 Unimplemented: Read as '0'.

© 2017 Microchip Technology Inc.

#### 36.2.5 AUTO-CONVERSION TRIGGER

The auto-conversion trigger allows periodic ADC measurements without software intervention. When a rising edge of the selected source occurs, the GO bit is set by hardware.

The auto-conversion trigger source is selected by the ADACT register.

Using the auto-conversion trigger does not assure proper ADC timing. It is the user's responsibility to ensure that the ADC timing requirements are met. See Register 36-33 for auto-conversion sources.

#### 36.2.6 ADC CONVERSION PROCEDURE (BASIC MODE)

This is an example procedure for using the ADC to perform an analog-to-digital conversion:

- 1. Configure Port:

- Disable pin output driver (Refer to the TRISx register)

- Configure pin as analog (Refer to the ANSELx register)

- 2. Configure the ADC module:

- Select ADC conversion clock

- Select voltage reference

- Select ADC input channel

### **EXAMPLE 36-1: ADC CONVERSION** /\*This code block configures the ADC

- Precharge and acquisition

- Turn on ADC module

- 3. Configure ADC interrupt (optional):

- Clear ADC interrupt flag

- Enable ADC interrupt

- Enable global interrupt<sup>(1)</sup>

- If ADACQ = 0, software must wait the required acquisition time<sup>(2)</sup>.

- 5. Start conversion by setting the GO bit.

- 6. Wait for ADC conversion to complete by one of the following:

- Polling the GO bit

- Polling the ADIF bit

- Waiting for the ADC interrupt (interrupts enabled)

- 7. Read ADC Result.

- 8. Clear the ADC interrupt flag (required if interrupt is enabled).

- **Note 1:** The global interrupt can be disabled if the user is attempting to wake-up from Sleep and resume in-line code execution.

- 2: Refer to Section 36.3 "ADC Acquisition Requirements".

for polling, VDD and VSS references, FRC oscillator and ANO input. Conversion start & polling for completion are included. \*/ void main() { //System Initialize initializeSystem(); //Setup ADC ADCONObits.FM = 1; //right justify ADCONObits.CS = 1; //FRC Clock  $ADPCH = 0 \times 00; //RA0$  is Analog channel TRISAbits.TRISA0 = 1; //Set RA0 to input ANSELAbits.ANSELA0 = 1; //Set RA0 to analog ADCONObits.ON = 1; //Turn ADC On while (1) { ADCONObits.GO = 1; //Start conversion while (ADCONObits.GO); //Wait for conversion done resultHigh = ADRESH; //Read result resultLow = ADRESL; //Read result }

#### **39.6 Operation During Sleep**

When enabled, the HLVD circuitry continues to operate during Sleep. If the device voltage crosses the trip point, the HLVDIF bit will be set and the device will wake up from Sleep. Device execution will continue from the interrupt vector address if interrupts have been globally enabled.

#### 39.7 Operation During Idle and Doze Modes

In both Idle and Doze modes, the module is active and events are generated if peripheral is enabled.

#### **39.8 Operation During Freeze**

When in Freeze mode, no new event or interrupt can be generated. The state of the LRDY bit is frozen.

Register reads and writes through the CPU interface are allowed.

#### **39.9 Effects of a Reset**

A device Reset forces all registers to their Reset state. This forces the HLVD module to be turned off.

| Mnemonic, |                                 | Description                               | Cycles     | 16-Bit Instruction Word |              |      |      | Status          | Notes |

|-----------|---------------------------------|-------------------------------------------|------------|-------------------------|--------------|------|------|-----------------|-------|

| Opera     | nds                             | Description                               | Cycles     | MSb                     |              |      | LSb  | Affected        | Notes |

| BYTE-ORIE | INTED FI                        | LE REGISTER INSTRUCTIONS                  |            |                         |              |      |      |                 |       |

| ADDWF     | f, d ,a                         | Add WREG and f                            | 1          | 0010                    | 01da         | ffff | ffff | C, DC, Z, OV, N |       |

| ADDWFC    | f, d, a                         | Add WREG and Carry bit to f               | 1          | 0010                    | 00da         | ffff | ffff | C, DC, Z, OV, N |       |

| ANDWF     | f, d, a                         | AND WREG with f                           | 1          | 0001                    | 01da         | ffff | ffff | Z, N            |       |

| CLRF      | f, a                            | Clear f                                   | 1          | 0110                    | 101a         | ffff | ffff | Z               |       |

| COMF      | f, d, a                         | Complement f                              | 1          | 0001                    | 11da         | ffff | ffff | Z, N            |       |

| DECF      | f, d, a                         | Decrement f                               | 1          | 0000                    | 01da         | ffff | ffff | C, DC, Z, OV, N |       |

| INCF      | f, d, a                         | Increment f                               | 1          | 0010                    | 10da         | ffff | ffff | C, DC, Z, OV, N |       |

| IORWF     | f, d, a                         | Inclusive OR WREG with f                  | 1          | 0001                    | 00da         | ffff | ffff | Z, N            |       |

| MOVF      | f, d, a                         | Move f to WREG or f                       | 1          | 0101                    | 00da         | ffff | ffff | Z, N            |       |

| MOVFF     | f <sub>s</sub> , f <sub>d</sub> | Move f <sub>s</sub> (source) to 1st word  | 2          | 1100                    | ffff         | ffff | ffff | None            | 2, 3  |

|           | ° u                             | f <sub>d</sub> (destination) 2nd word     |            | 1111                    | ffff         | ffff | ffff |                 |       |

| MOVFFL    | f <sub>s</sub> , f <sub>d</sub> | Move f <sub>s</sub> (source) to           | 3          | 0000                    | 0000         | 0110 | ffff | None            | 2     |

|           | 3. u                            | g (full destination)                      |            | 1111                    | ffff         | ffff | ffgg |                 |       |

|           |                                 | f <sub>d</sub> (full destination)3rd word |            | 1111                    | dddd         | gggg | aaaa |                 |       |

| MOVWF     | f, a                            | Move WREG to f                            | 1          | 0110                    | 111a         | ffff | ffff | None            |       |

| MULWF     | f, a                            | Multiply WREG with f                      | 1          | 0000                    | 001a         | ffff | ffff | None            |       |

| NEGF      | f, a                            | Negate f                                  | 1          | 0110                    | 110a         | ffff | ffff | C, DC, Z, OV, N |       |

| RLCF      | f, d, a                         | Rotate Left f through Carry               | 1          | 0011                    | 01da         | ffff | ffff | C, Z, N         |       |

| RLNCF     | f, d, a                         | Rotate Left f (No Carry)                  | 1          | 0100                    | 01da         | ffff | ffff | Z, N            |       |

| RRCF      | f, d, a                         | Rotate Right f through Carry              | 1          | 0011                    | 01da<br>00da | ffff | ffff | C, Z, N         |       |

| RRNCF     |                                 | Rotate Right f (No Carry)                 | 1          |                         |              |      | ffff | Z, N            |       |

|           | f, d, a                         | Set f                                     |            | 0100                    | 00da         | ffff |      |                 |       |

| SETF      | f, a                            |                                           | 1          | 0110                    | 100a         | ffff | ffff | None            |       |

| SUBFWB    | f, d, a                         | Subtract f from WREG with<br>borrow       | 1          | 0101                    | 01da         | ffff | ffff | C, DC, Z, OV, N |       |

| SUBWF     | f, d, a                         | Subtract WREG from f                      | 1          | 0101                    | 11da         | ffff | ffff | C, DC, Z, OV, N |       |

| SUBWFB    | f, d, a                         | Subtract WREG from f with                 | 1          | 0101                    | 10da         | ffff | ffff | C, DC, Z, OV, N |       |

|           |                                 | borrow                                    |            |                         |              |      |      |                 |       |

| SWAPF     | f, d, a                         | Swap nibbles in f                         | 1          | 0011                    | 10da         | ffff | ffff | None            |       |

| XORWF     | f, d, a                         | Exclusive OR WREG with f                  | 1          | 0001                    |              | ffff | ffff | Z, N            |       |

| BYTE-ORIE |                                 |                                           |            |                         |              |      |      |                 |       |

| CPFSEQ    | f, a                            | Compare f with WREG, skip =               | 1 (2 or 3) | 0110                    | 001a         | ffff | ffff | None            | 1     |

| CPFSGT    | f, a                            | Compare f with WREG, skip >               | 1 (2 or 3) | 0110                    | 010a         | ffff | ffff | None            | 1     |

| CPFSLT    | f, a                            | Compare f with WREG, skip <               | 1 (2 or 3) | 0110                    | 000a         | ffff | ffff | None            | 1     |

| DECFSZ    | f, d, a                         | Decrement f, Skip if 0                    | 1 (2 or 3) | 0010                    | 11da         | ffff | ffff | None            | 1     |

| DCFSNZ    | f, d, a                         | Decrement f, Skip if Not 0                | 1 (2 or 3) |                         | 11da         | ffff | ffff | None            | 1     |

| INCFSZ    | f, d, a                         | Increment f, Skip if 0                    | 1 (2 or 3) |                         | 11da         | ffff | ffff | None            | 1     |

| INFSNZ    | f, d, a                         | Increment f, Skip if Not 0                | 1 (2 or 3) |                         | 10da         | ffff | ffff | None            | 1     |

| TSTFSZ    | f, a                            | Test f, skip if 0                         | 1 (2 or 3) |                         | 011a         | ffff | ffff | None            | 1     |

|           |                                 |                                           | . (2 0. 0) | 0110                    | 0110         |      |      |                 |       |

| BCF       | f, b, a                         | Bit Clear f                               | 1          | 1001                    | bbba         | ffff | ffff | None            |       |

| BSF       | f, b, a                         | Bit Set f                                 | 1          |                         | bbba         | ffff | ffff | None            |       |

| BTG       | f, d, a                         | Bit Toggle f                              | 1          | 0111                    |              | ffff | ffff | None            |       |

|           |                                 | PINSTRUCTIONS                             | ·          |                         |              |      |      |                 | 1     |

| BTFSC     | f, b, a                         | Bit Test f, Skip if Clear                 | 1 (2 or 3) | 1011                    | bbba         | ffff | ffff | None            | 1     |

| BTFSS     | f, b, a                         | Bit Test f, Skip if Set                   | 1 (2 or 3) |                         |              | ffff | ffff | None            | 1     |

#### TABLE 41-2: INSTRUCTION SET

Note 1: If Program Counter (PC) is modified or a conditional test is true, the instruction requires an additional cycle. The extra cycle is executed as a NOP.

2: Some instructions are multi word instructions. The second/third words of these instructions will be decoded as a NOP, unless the first word of the instruction retrieves the information embedded in these 16-bits. This ensures that all program memory locations have a valid instruction.

3: f<sub>s</sub> and f<sub>d</sub> do not cover the full memory range. 2 MSBs of bank selection are forced to 'b00 to limit the range of these instructions to lower 4k addressing space.

#### 45.0 DC AND AC CHARACTERISTICS GRAPHS AND TABLES

The graphs and tables provided in this section are for **design guidance** and are **not tested**.

In some graphs or tables, the data presented are **outside specified operating range** (i.e., outside specified VDD range). This is for **information only** and devices are ensured to operate properly only within the specified range.

Unless otherwise noted, all graphs apply to both the L and LF devices.

**Note:** The graphs and tables provided following this note are a statistical summary based on a limited number of samples and are provided for informational purposes only. The performance characteristics listed herein are not tested or guaranteed. In some graphs or tables, the data presented may be outside the specified operating range (e.g., outside specified power supply range) and therefore, outside the warranted range.

"Typical" represents the mean of the distribution at 25°C. "Maximum", "Max.", "Minimum" or "Min." represents (mean +  $3\sigma$ ) or (mean -  $3\sigma$ ) respectively, where  $\sigma$  is a standard deviation, over each temperature range.

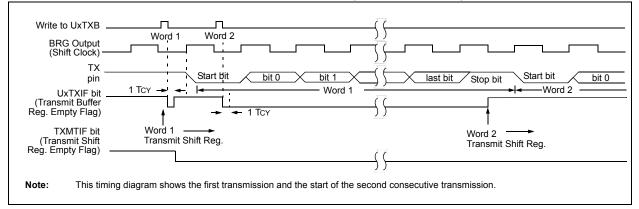

#### Package Marking Information (Continued)

| 2090114 | Y<br>YY<br>WW<br>NNN<br>(e3)                                                                                                                                                                         | Year code (last digit of calendar year)<br>Year code (last 2 digits of calendar year)<br>Week code (week of January 1 is week '01')<br>Alphanumeric traceability code<br>Pb-free JEDEC <sup>®</sup> designator for Matte Tin (Sn) |  |  |  |  |  |

|---------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|--|

|         | *                                                                                                                                                                                                    | This package is Pb-free. The Pb-free JEDEC designator ((e3)) can be found on the outer packaging for this package.                                                                                                                |  |  |  |  |  |

|         | : In the event the full Microchip part number cannot be marked on one line, it w be carried over to the next line, thus limiting the number of availab characters for customer-specific information. |                                                                                                                                                                                                                                   |  |  |  |  |  |

© 2017 Microchip Technology Inc.

#### 48-Lead Plastic Ultra Thin Quad Flat, No Lead Package (MV) – 6x6x0.5 mm Body [UQFN]

**Note:** For the most current package drawings, please see the Microchip Packaging Specification located at http://www.microchip.com/packaging

|                        | Units            |           |          | S    |  |

|------------------------|------------------|-----------|----------|------|--|

| Dimension              | Dimension Limits |           |          | MAX  |  |

| Number of Pins         | N                |           | 48       |      |  |

| Pitch                  | е                |           | 0.40 BSC |      |  |

| Overall Height         | A                | 0.45      | 0.50     | 0.55 |  |

| Standoff               | A1               | 0.00      | 0.02     | 0.05 |  |

| Contact Thickness      | A3               | 0.127 REF |          |      |  |

| Overall Width          | E                | 6.00 BSC  |          |      |  |

| Exposed Pad Width      | E2               | 4.45      | 4.60     | 4.75 |  |

| Overall Length         | D                |           | 6.00 BSC |      |  |

| Exposed Pad Length     | D2               | 4.45      | 4.60     | 4.75 |  |

| Contact Width          | b 0.15 0.        |           |          | 0.25 |  |

| Contact Length         | L                | 0.30      | 0.40     | 0.50 |  |

| Contact-to-Exposed Pad | K                | 0.20      | -        | -    |  |

#### Notes:

1. Pin 1 visual index feature may vary, but must be located within the hatched area.

2. Package is saw singulated.

3. Dimensioning and tolerancing per ASME Y14.5M.

BSC: Basic Dimension. Theoretically exact value shown without tolerances.

REF: Reference Dimension, usually without tolerance, for information purposes only.

Microchip Technology Drawing C04-153A Sheet 2 of 2