Welcome to E-XFL.COM

### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

### Details

E·XFI

| Details                    |                                                                              |

|----------------------------|------------------------------------------------------------------------------|

| Product Status             | Active                                                                       |

| Core Processor             | PIC                                                                          |

| Core Size                  | 8-Bit                                                                        |

| Speed                      | 64MHz                                                                        |

| Connectivity               | I <sup>2</sup> C, LINbus, SPI, UART/USART                                    |

| Peripherals                | Brown-out Detect/Reset, DMA, HLVD, POR, PWM, WDT                             |

| Number of I/O              | 25                                                                           |

| Program Memory Size        | 64KB (32K x 16)                                                              |

| Program Memory Type        | FLASH                                                                        |

| EEPROM Size                | 1K x 8                                                                       |

| RAM Size                   | 4K x 8                                                                       |

| Voltage - Supply (Vcc/Vdd) | 1.8V ~ 3.6V                                                                  |

| Data Converters            | A/D 24x12b; D/A 1x5b                                                         |

| Oscillator Type            | Internal                                                                     |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                            |

| Mounting Type              | Surface Mount                                                                |

| Package / Case             | 28-SOIC (0.295", 7.50mm Width)                                               |

| Supplier Device Package    | 28-SOIC                                                                      |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/pic18lf26k42t-i-so |

|                            |                                                                              |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

| Pin Allocation Tables |

|-----------------------|

|-----------------------|

| bit         bit <th>TABLE 1</th> <th>:</th> <th></th> <th>28-PIN ALI</th> <th colspan="10">28-PIN ALLOCATION TABLE (PIC18(L)F2XK42)</th>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | TABLE 1 | :                      |               | 28-PIN ALI                    | 28-PIN ALLOCATION TABLE (PIC18(L)F2XK42) |          |                  |                   |                       |                    |                     |                       |                      |                     |                       |                       |     |                        |                     |         |

|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------|------------------------|---------------|-------------------------------|------------------------------------------|----------|------------------|-------------------|-----------------------|--------------------|---------------------|-----------------------|----------------------|---------------------|-----------------------|-----------------------|-----|------------------------|---------------------|---------|

| Image: Problem in the system in theresystem in the system in there and the system in the s | 0/1     | 28-Pin SPDIP/SOIC/SSOP | 28-Pin (U)QFN | ADC                           | Voltage Reference                        | DAC      | Comparators      | Zero Cross Detect | I²C                   | SPI                | UART                | WSD                   | Timers/SMT           | CCP and PWM         | CWG                   | CLC                   | NCO | Clock Reference (CLKR) | Interrupt-on-Change | Basic   |

| Image: Probability of the p | RA0     | 2                      | 27            | ANA0                          | —                                        | —        | C1IN0-<br>C2IN0- | -                 | _                     | _                  |                     | _                     | _                    | -                   | -                     | CLCIN0 <sup>(1)</sup> | _   | -                      | IOCA0               | —       |

| Image         Image <t< td=""><td>RA1</td><td>3</td><td>28</td><td>ANA1</td><td>-</td><td>—</td><td></td><td>-</td><td>-</td><td>-</td><td>-</td><td>—</td><td>_</td><td>—</td><td>—</td><td>CLCIN1<sup>(1)</sup></td><td>-</td><td>-</td><td>IOCA1</td><td>-</td></t<>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | RA1     | 3                      | 28            | ANA1                          | -                                        | —        |                  | -                 | -                     | -                  | -                   | —                     | _                    | —                   | —                     | CLCIN1 <sup>(1)</sup> | -   | -                      | IOCA1               | -       |

| R4         6         3         ANA4             MDCARH <sup>0</sup> TOCKI <sup>0</sup> MDCARH <sup>0</sup> TOCKI <sup>0</sup> MDCARH <sup>0</sup> TOCKI <sup>0</sup> </td <td>RA2</td> <td>4</td> <td>1</td> <td>ANA2</td> <td>VREF-</td> <td>DAC1OUT1</td> <td></td> <td>I</td> <td>-</td> <td>—</td> <td>-</td> <td>-</td> <td>—</td> <td>—</td> <td>—</td> <td>-</td> <td>—</td> <td>-</td> <td>IOCA2</td> <td>—</td>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | RA2     | 4                      | 1             | ANA2                          | VREF-                                    | DAC1OUT1 |                  | I                 | -                     | —                  | -                   | -                     | —                    | —                   | —                     | -                     | —   | -                      | IOCA2               | —       |

| RAS       7       4       ANAS           NDSRC <sup>10</sup> ICCAS          RA6       10       7       ANAG        ICCAS       ICCAS <td>RA3</td> <td>5</td> <td>2</td> <td>ANA3</td> <td>VREF+</td> <td>_</td> <td>C1IN1+</td> <td> </td> <td>_</td> <td>_</td> <td> </td> <td>MDCARL<sup>(1)</sup></td> <td>_</td> <td>_</td> <td>_</td> <td>_</td> <td>_</td> <td>_</td> <td>IOCA3</td> <td>_</td>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | RA3     | 5                      | 2             | ANA3                          | VREF+                                    | _        | C1IN1+           |                   | _                     | _                  |                     | MDCARL <sup>(1)</sup> | _                    | _                   | _                     | _                     | _   | _                      | IOCA3               | _       |

| RA6       10       7       ANA6                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | RA4     | 6                      | 3             | ANA4                          | _                                        | _        |                  | _                 | _                     | _                  | -                   | MDCARH <sup>(1)</sup> | T0CKI <sup>(1)</sup> | _                   | _                     | _                     | _   | _                      | IOCA4               | _       |

| Image: Normal Section  | RA5     | 7                      | 4             | ANA5                          | _                                        | _        | _                | -                 | _                     | SS1 <sup>(1)</sup> | _                   | MDSRC <sup>(1)</sup>  | _                    | _                   | _                     | _                     | _   | -                      | IOCA5               | —       |

| Image: Constraint of the state of | RA6     | 10                     | 7             | ANA6                          | -                                        | -        | -                | -                 | -                     | -                  | -                   | -                     | -                    | -                   | -                     | —                     |     |                        | IOCA6               |         |

| Image: Constraint of the state of | RA7     | 9                      | 6             | ANA7                          | _                                        | —        | _                | -                 | —                     | _                  | _                   | —                     | _                    | —                   | —                     | —                     | _   | -                      | IOCA7               |         |

| Image: Normal Section Sectin Section Section Section Section Section Section S | RB0     | 21                     | 18            | ANB0                          | —                                        | -        | C2IN1+           | ZCD               | -                     | —                  | -                   | -                     | —                    | CCP4 <sup>(1)</sup> | CWG1IN <sup>(1)</sup> | -                     | —   | -                      |                     | —       |

| Image: Normal system         Image: N                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | RB1     | 22                     | 19            | ANB1                          | —                                        | —        |                  | 1                 | SCL2 <sup>(3,4)</sup> | _                  | -                   | —                     | —                    | —                   | CWG2IN <sup>(1)</sup> | —                     | _   | _                      |                     | —       |

| RB4         25         24         ANB4<br>ADCACT <sup>(1)</sup> TGG <sup>(1)</sup> TGG <sup>(1)</sup>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | RB2     | 23                     | 20            | ANB2                          | —                                        | -        | -                | I                 | SDA2 <sup>(3,4)</sup> | —                  | -                   | -                     | —                    | —                   | CWG3IN <sup>(1)</sup> | -                     | —   | -                      |                     | —       |

| ADCACT <sup>(1)</sup>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | RB3     | 24                     | 21            | ANB3                          | —                                        | -        |                  | —                 | —                     | _                  | —                   | —                     | _                    | -                   | -                     | -                     | —   | —                      | IOCB3               | —       |

| RB6 27 24 ANB6 CLCIN2 <sup>(1)</sup> IOCB6 ICSPCLK                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | RB4     | 25                     | 22            | ANB4<br>ADCACT <sup>(1)</sup> | —                                        | —        | —                | —                 | —                     | —                  | —                   | -                     | T5G <sup>(1)</sup>   | —                   | —                     | —                     | —   | —                      | IOCB4               | —       |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | RB5     | 26                     | 23            | ANB5                          | _                                        | —        | _                | -                 | _                     | _                  | _                   | _                     | T1G <sup>(1)</sup>   | CCP3 <sup>(1)</sup> | —                     | —                     | _   | _                      | IOCB5               | —       |

| RB7 28 25 ANB7 - DAC10UT2 RX2 <sup>(1)</sup> - T6IN(1) CLCIN3 <sup>(1)</sup> IOCB7 ICSPDAT                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | RB6     | 27                     | 24            | ANB6                          | —                                        |          | _                | —                 | _                     | _                  | CTS2 <sup>(1)</sup> | _                     | _                    | _                   | _                     |                       | _   | _                      | IOCB6               | ICSPCLK |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | RB7     | 28                     | 25            | ANB7                          | —                                        | DAC10UT2 | _                | _                 | _                     |                    | RX2 <sup>(1)</sup>  | _                     | T6IN(1)              | —                   | —                     | CLCIN3 <sup>(1)</sup> | -   | -                      | IOCB7               | ICSPDAT |

Note 1: This is a PPS remappable input signal. The input function may be moved from the default location shown to one of several other PORTx pins.

2: All output signals shown in this row are PPS remappable.

3: This is a bidirectional signal. For normal module operation, the firmware should map this signal to the same pin in both the PPS input and PPS output registers.

4: These pins can be configured for I<sup>2</sup>C and SMB<sup>™</sup> 3.0/2.0 logic levels; The SCLx/SDAx signals may be assigned to any of the RB1/RB2/RC3/RC4 pins. PPS assignments to the other pins (e.g., RA5) will operate, but input logic levels will be standard TTL/ST as selected by the INLVL register, instead of the I<sup>2</sup>C specific or SMBUs input buffer thresholds.

### TO OUR VALUED CUSTOMERS

It is our intention to provide our valued customers with the best documentation possible to ensure successful use of your Microchip products. To this end, we will continue to improve our publications to better suit your needs. Our publications will be refined and enhanced as new volumes and updates are introduced.

If you have any questions or comments regarding this publication, please contact the Marketing Communications Department via E-mail at docerrors@microchip.com. We welcome your feedback.

### Most Current Data Sheet

To obtain the most up-to-date version of this data sheet, please register at our Worldwide Website at:

### http://www.microchip.com

You can determine the version of a data sheet by examining its literature number found on the bottom outside corner of any page. The last character of the literature number is the version number, (e.g., DS3000000A is version A of document DS30000000).

### Errata

An errata sheet, describing minor operational differences from the data sheet and recommended workarounds, may exist for current devices. As device/documentation issues become known to us, we will publish an errata sheet. The errata will specify the revision of silicon and revision of document to which it applies.

To determine if an errata sheet exists for a particular device, please check with one of the following:

- Microchip's Worldwide Website; http://www.microchip.com

- Your local Microchip sales office (see last page)

When contacting a sales office, please specify which device, revision of silicon and data sheet (include literature number) you are using.

### **Customer Notification System**

Register on our website at www.microchip.com to receive the most current information on all of our products.

|                      | PC<21:0>                                                                                               | PC<21:0>                                                                                                                                                         | PC<21:0>                                       | 7                    |  |  |

|----------------------|--------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------|----------------------|--|--|

|                      | <b>†</b> 1                                                                                             | <b>\$</b>                                                                                                                                                        | ¢ I                                            | _                    |  |  |

| Note 1               | Stack (31 levels)                                                                                      | Stack (31 levels)                                                                                                                                                | Stack (31 levels)                              | Note 1               |  |  |

|                      | •                                                                                                      |                                                                                                                                                                  | ★                                              | _                    |  |  |

| 00 0000h             | Reset Vector                                                                                           | Reset Vector                                                                                                                                                     | Reset Vector                                   | 00 0000h             |  |  |

| •••                  | •••                                                                                                    | •••                                                                                                                                                              | •••                                            | •••                  |  |  |

| 00 0008h             | Interrupt Vector High <sup>(2)</sup>                                                                   | Interrupt Vector High <sup>(2)</sup>                                                                                                                             | Interrupt Vector High <sup>(2)</sup>           | 00 0008h             |  |  |

| •••                  | • • •                                                                                                  | • • •                                                                                                                                                            | • • •                                          | •••                  |  |  |

| 00 0018h             | Interrupt Vector Low <sup>(2)</sup>                                                                    | Interrupt Vector Low <sup>(2)</sup>                                                                                                                              | Interrupt Vector Low <sup>(2)</sup>            | 00 0018h             |  |  |

| 00 001Ah<br>•        | Program Flash Memory (16<br>KW) <sup>(3)</sup>                                                         |                                                                                                                                                                  |                                                | 00 001Ah<br>•        |  |  |

| 00 7FFFh             | (WV) <sup></sup>                                                                                       | Program Flash Memory (32<br>KW) <sup>(3)</sup>                                                                                                                   |                                                | 00 7FFF              |  |  |

| 00 8000h             |                                                                                                        | KVV). /                                                                                                                                                          | Program Flash Memory (64<br>KW) <sup>(3)</sup> | 00 8000h<br>•        |  |  |

| 00 FFFFh             |                                                                                                        |                                                                                                                                                                  |                                                | 00 FFFF              |  |  |

| 01 0000h             | Reserved <sup>(4)</sup>                                                                                |                                                                                                                                                                  |                                                | 01 0000h             |  |  |

| 01 FFFFh             |                                                                                                        | Reserved <sup>(4)</sup>                                                                                                                                          |                                                | 01 FFFF              |  |  |

| 02 0000h<br>1F FFFFh |                                                                                                        |                                                                                                                                                                  | Reserved <sup>(4)</sup>                        | 02 0000h<br>1F FFFFh |  |  |

| 20 0000              |                                                                                                        | User IDs (8 Words) <sup>(5)</sup>                                                                                                                                |                                                | 20 0000h             |  |  |

| 20 000Fh             |                                                                                                        |                                                                                                                                                                  |                                                | 20 000Fh             |  |  |

| 20 0010h             | Personal                                                                                               |                                                                                                                                                                  |                                                |                      |  |  |

| 2F FFFFh             | Reserved                                                                                               |                                                                                                                                                                  |                                                |                      |  |  |

| 30 0000h             | Configuration Words (5 Words) <sup>(5)</sup>                                                           |                                                                                                                                                                  |                                                |                      |  |  |

| 30 0009h             | Configuration Words (5 Words)(**                                                                       |                                                                                                                                                                  |                                                |                      |  |  |

| 30 000Ah             | Descend                                                                                                |                                                                                                                                                                  |                                                |                      |  |  |

| 30 FFFFh             |                                                                                                        | Reserved                                                                                                                                                         |                                                |                      |  |  |

| 31 0000h             |                                                                                                        |                                                                                                                                                                  |                                                | 31 0000h             |  |  |

| 31 00FFh             | Data EEPROM (256 Bytes)                                                                                |                                                                                                                                                                  |                                                | •••<br>31 00FFh      |  |  |

| 31 0100h             |                                                                                                        | Data EEPRO                                                                                                                                                       | M (1024Bytes)                                  | 31 0100h             |  |  |

| •••                  |                                                                                                        |                                                                                                                                                                  |                                                | •••                  |  |  |

| 31 03FFh             | Reserved                                                                                               |                                                                                                                                                                  |                                                | 31 03FFh             |  |  |

| 31 0400h             |                                                                                                        | Rese                                                                                                                                                             | erved                                          | 31 0400h             |  |  |

| 3E FFFFh             |                                                                                                        |                                                                                                                                                                  |                                                | 3E FFFF              |  |  |

| 3F 0000h             |                                                                                                        | Device Information Area <sup>(5),(7)</sup>                                                                                                                       |                                                | 3F 0000h             |  |  |

| 3F 003Fh             |                                                                                                        |                                                                                                                                                                  |                                                | 3F 003Fh             |  |  |

| 3F0040h              |                                                                                                        | Reserved                                                                                                                                                         |                                                | 3F0040h              |  |  |

| 3F FEFFh             |                                                                                                        |                                                                                                                                                                  |                                                | 3F FEFFI             |  |  |

| 3F FF00h             | Device C                                                                                               | onfiguration Information (5 Word                                                                                                                                 | (5),(6),(7)                                    | 3F FF00h             |  |  |

| 3F FF09h             |                                                                                                        | <b>.</b> .                                                                                                                                                       |                                                | 3F FF09h             |  |  |

| 3F FF0Ah             |                                                                                                        | Reserved                                                                                                                                                         |                                                | 3F FF0Ah             |  |  |

| 3F FFFBh             |                                                                                                        | Reserved                                                                                                                                                         |                                                | 3F FFFB              |  |  |

| 3F FFFCh             |                                                                                                        | Revision ID (1 Word) <sup>(5),(6),(7)</sup>                                                                                                                      |                                                | 3F FFFCI             |  |  |

| 3F FFFDh             |                                                                                                        | Revision ID (1 word)                                                                                                                                             |                                                | 3F FFFD              |  |  |

| 3F FFFEh             |                                                                                                        |                                                                                                                                                                  |                                                | 3F FFFEI             |  |  |

| 3F FFFFh             |                                                                                                        | Device ID (1 Word) <sup>(5),(6),(7)</sup>                                                                                                                        |                                                | 3F FFFF              |  |  |

| Note 1:<br>2:<br>3:  | 00 0008h location is used as the<br>memory by programming the IVT<br>Storage area Flash is implemented | anel, apart from all user memory pa<br>reset default for the IVTBASE regis<br>BASE register.<br>ed as the last 128 Words of user FI<br>he region is read as '0'. | ster, the vector table can be reloca           | ated in the          |  |  |

### TABLE 4-1: PROGRAM AND DATA EEPROM MEMORY MAP

| U-0              | U-0   | R/W-0/0           | R/W-0/0       | R/W-0/0        | R/W-0/0          | R/W-0/0          | R/W-0/0      |

|------------------|-------|-------------------|---------------|----------------|------------------|------------------|--------------|

| _                | _     |                   |               | TUN            | <5:0>            |                  |              |

| bit 7            |       |                   |               |                |                  |                  | bit (        |

| <del></del>      |       |                   |               |                |                  |                  |              |

| Legend:          |       |                   |               |                |                  |                  |              |

| R = Readable     | bit   | W = Writable      | bit           | U = Unimplen   | nented bit, read | d as '0'         |              |

| u = Bit is unch  | anged | x = Bit is unkr   | iown          | -n/n = Value a | t POR and BO     | R/Value at all o | other Resets |

| '1' = Bit is set |       | '0' = Bit is clea | ared          |                |                  |                  |              |

|                  |       | Maximum freque    | quency Tuning | DITS           |                  |                  |              |

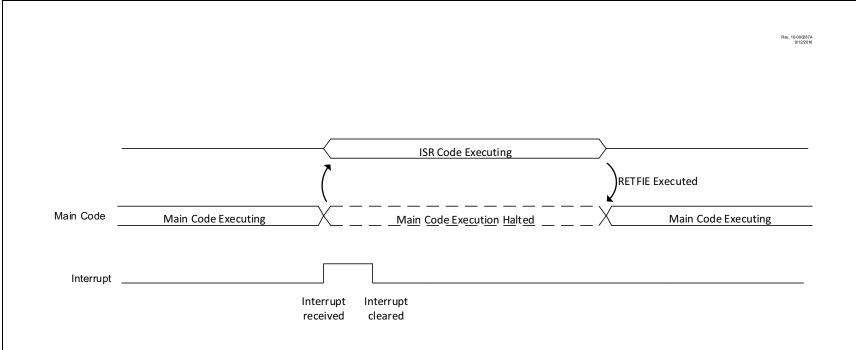

### 9.4.1 SERVING A HIGH OR LOW PRIORITY INTERRUPT WHEN MAIN ROUTINE CODE IS EXECUTING

When a high or low priority interrupt is requested when the main routine code is executing, the main routine execution is halted and the ISR is addressed, see Figure 9-2. Upon a return from the ISR (by executing the RETFIE instruction), the main routine resumes execution.

### FIGURE 9-2: INTERRUPT EXECUTION: HIGH/LOW PRIORITY INTERRUPT WHEN EXECUTING MAIN ROUTINE

| R-0/0                  | R-0/0                                  | R-0/0                              | R-0/0                                                           | R/W/HS-0/0        | R/W/HS-0/0        | R/W/HS-0/0                                  | R/W/HS-0/0     |  |  |

|------------------------|----------------------------------------|------------------------------------|-----------------------------------------------------------------|-------------------|-------------------|---------------------------------------------|----------------|--|--|

| I2C1RXIF <sup>(2</sup> | <sup>2)</sup> SPI1IF <sup>(3)</sup>    | SPI1TXIF <sup>(4)</sup>            | SPI1RXIF <sup>(4)</sup>                                         | DMA1AIF           | DMA10RIF          | DMA1DCNTIF                                  | DMA1SCNTIF     |  |  |

| bit 7                  |                                        |                                    |                                                                 |                   |                   |                                             | bit (          |  |  |

|                        |                                        |                                    |                                                                 |                   |                   |                                             |                |  |  |

| Legend:                |                                        |                                    |                                                                 |                   |                   |                                             |                |  |  |

| R = Reada              |                                        | W = Writable                       |                                                                 | •                 | ented bit, read   |                                             |                |  |  |

| u = Bit is u           | -                                      |                                    | Bit is unknown -n/n = Value at POR and BOR/Value at all other F |                   |                   |                                             |                |  |  |

| '1' = Bit is s         | set                                    | '0' = Bit is cle                   | ared                                                            | HS = Hardwar      | e set             |                                             |                |  |  |

| bit 7                  | I2C1RXIF:                              | <sup>2</sup> C1 Receive Ir         | nterrupt Flag b                                                 | it(2)             |                   |                                             |                |  |  |

|                        |                                        | ot has occurred                    |                                                                 |                   |                   |                                             |                |  |  |

|                        | 0 = Interrup                           | ot event has no                    | t occurred                                                      |                   |                   |                                             |                |  |  |

| bit 6                  |                                        | 1 Interrupt Flag                   | -                                                               |                   |                   |                                             |                |  |  |

|                        |                                        | ot has occurred                    |                                                                 |                   |                   |                                             |                |  |  |

|                        | -                                      | ot event has no                    |                                                                 | (4)               |                   |                                             |                |  |  |

| bit 5                  |                                        | SPI1 Transmit I                    |                                                                 | DIL               |                   |                                             |                |  |  |

|                        |                                        | ot has occurred<br>ot event has no |                                                                 |                   |                   |                                             |                |  |  |

| bit 4                  | •                                      | SPI1 Receive I                     |                                                                 | oit(4)            |                   |                                             |                |  |  |

|                        |                                        | ot has occurred                    | 1 0                                                             |                   |                   |                                             |                |  |  |

|                        |                                        | ot event has no                    |                                                                 |                   |                   |                                             |                |  |  |

| bit 3                  | DMA1AIF: DMA1 Abort Interrupt Flag bit |                                    |                                                                 |                   |                   |                                             |                |  |  |

|                        | 1 = Interrup                           | ot has occurred                    | (must be clea                                                   | red by software   | e)                |                                             |                |  |  |

|                        | •                                      | ot event has no                    |                                                                 |                   |                   |                                             |                |  |  |

| bit 2                  |                                        | : DMA1 Overru                      | •                                                               | •                 |                   |                                             |                |  |  |

|                        | -                                      |                                    | -                                                               | red by software   | e)                |                                             |                |  |  |

| bit 1                  |                                        | ot event has no                    |                                                                 | t Interrupt Flag  | hit               |                                             |                |  |  |

|                        |                                        |                                    |                                                                 | red by software   |                   |                                             |                |  |  |

|                        |                                        | ot event has no                    |                                                                 | incu by softward  | -)                |                                             |                |  |  |

| bit 0                  | •                                      | <b>FIF:</b> DMA1 Sou               |                                                                 | errupt Flag bit   |                   |                                             |                |  |  |

|                        |                                        |                                    |                                                                 | red by software   | e)                |                                             |                |  |  |

|                        | 0 = Interrup                           | ot event has no                    | toccurred                                                       | -                 |                   |                                             |                |  |  |

|                        |                                        | e global enable                    |                                                                 |                   |                   | the state of its co<br>priate interrupt fla |                |  |  |

| 2:                     | -                                      | 2CxRXIF are r                      | ead-only bits.                                                  | To clear the inte | errupt condition  | , the CLRBF bit i                           | n I2CxSTAT1    |  |  |

| 3:                     | SPIxIF is a rea                        | d-only bit. To c                   | lear the interru                                                | pt condition, al  | l bits in the SPI | kINTF register m                            | ust be cleared |  |  |

|                        |                                        |                                    |                                                                 |                   |                   |                                             |                |  |  |

### REGISTER 9-5: PIR2: PERIPHERAL INTERRUPT REGISTER 2<sup>(1)</sup>

4: SPIxTXIF and SPIxRXIF are read-only bits and cannot be set/cleared by the software.

| R/W-1/1         | R/W-1/1                                                                         | R/W-1/1          | R/W-1/1                                                           | R/W-1/1            | R/W-1/1           | R/W-1/1    | R/W-1/1    |  |  |  |  |

|-----------------|---------------------------------------------------------------------------------|------------------|-------------------------------------------------------------------|--------------------|-------------------|------------|------------|--|--|--|--|

| I2C1RXIP        | SPI1IP                                                                          | SPI1TXIP         | SPI1RXIP                                                          | DMA1AIP            | DMA10RIP          | DMA1DCNTIP | DMA1SCNTIP |  |  |  |  |

| bit 7           |                                                                                 |                  |                                                                   | •                  |                   |            | bit 0      |  |  |  |  |

|                 |                                                                                 |                  |                                                                   |                    |                   |            |            |  |  |  |  |

| Legend:         |                                                                                 |                  |                                                                   |                    |                   |            |            |  |  |  |  |

| R = Readab      |                                                                                 | W = Writable     |                                                                   | -                  | ented bit, read a |            |            |  |  |  |  |

| u = Bit is und  | •                                                                               |                  | x = Bit is unknown -n/n = Value at POR and BOR/Value at all other |                    |                   |            |            |  |  |  |  |

| '1' = Bit is se | et                                                                              | '0' = Bit is cle | ared                                                              |                    |                   |            |            |  |  |  |  |

|                 |                                                                                 | 201 0            |                                                                   |                    |                   |            |            |  |  |  |  |

| bit 7           | <b>I2C1RXIP:</b> I <sup>2</sup> C1 Receive Interrupt Priority bit               |                  |                                                                   |                    |                   |            |            |  |  |  |  |

|                 | 1 = High priority<br>0 = Low priority                                           |                  |                                                                   |                    |                   |            |            |  |  |  |  |

| bit 6           | 0 = Low priority<br>SPI1IP: SPI1 Transmit Interrupt Priority bit                |                  |                                                                   |                    |                   |            |            |  |  |  |  |

|                 | 1 = High priority                                                               |                  |                                                                   |                    |                   |            |            |  |  |  |  |

|                 | 0 = Low priority                                                                |                  |                                                                   |                    |                   |            |            |  |  |  |  |

| bit 5           | SPI1TXIP: I <sup>2</sup> C1 Transmit Interrupt Priority bit                     |                  |                                                                   |                    |                   |            |            |  |  |  |  |

|                 | 1 = High priority                                                               |                  |                                                                   |                    |                   |            |            |  |  |  |  |

|                 | 0 = Low priority                                                                |                  |                                                                   |                    |                   |            |            |  |  |  |  |

| bit 4           | SPI1RXIP: SPI1 Receive Interrupt Priority bit                                   |                  |                                                                   |                    |                   |            |            |  |  |  |  |

|                 | 1 = High priority<br>0 = Low priority                                           |                  |                                                                   |                    |                   |            |            |  |  |  |  |

| bit 3           |                                                                                 |                  | ansmit Interru                                                    | int Priority bit   |                   |            |            |  |  |  |  |

|                 | <b>DMA1AIP:</b> DMA1 Abort Transmit Interrupt Priority bit<br>1 = High priority |                  |                                                                   |                    |                   |            |            |  |  |  |  |

|                 | 0 = Low priority                                                                |                  |                                                                   |                    |                   |            |            |  |  |  |  |

| bit 2           | DMA10RIP                                                                        | : DMA1 Overru    | un Interrupt P                                                    | riority bit        |                   |            |            |  |  |  |  |

|                 | 1 = High pr                                                                     |                  |                                                                   |                    |                   |            |            |  |  |  |  |

|                 | 0 = Low pri                                                                     | -                |                                                                   |                    |                   |            |            |  |  |  |  |

| bit 1           |                                                                                 |                  | tination Coun                                                     | t Interrupt Prior  | ity bit           |            |            |  |  |  |  |

|                 | <ul> <li>1 = High priority</li> <li>0 = Low priority</li> </ul>                 |                  |                                                                   |                    |                   |            |            |  |  |  |  |

| bit 0           | -                                                                               | -                | irce Count Int                                                    | terrupt Priority b | it                |            |            |  |  |  |  |

|                 | 1 = High pr                                                                     |                  |                                                                   |                    |                   |            |            |  |  |  |  |

|                 | 1 = High phoney<br>0 = Low priority                                             |                  |                                                                   |                    |                   |            |            |  |  |  |  |

### REGISTER 9-27: IPR2: PERIPHERAL INTERRUPT PRIORITY REGISTER 2

### **REGISTER 15-15: DMAxDSAH: DMAx DESTINATION START ADDRESS HIGH REGISTER**

|           |         | -       | -       |         |         |         |         |  |  |  |

|-----------|---------|---------|---------|---------|---------|---------|---------|--|--|--|

| R/W-0/0   | R/W-0/0 | R/W-0/0 | R/W-0/0 | R/W-0/0 | R/W-0/0 | R/W-0/0 | R/W-0/0 |  |  |  |

| DSA<15:8> |         |         |         |         |         |         |         |  |  |  |

| bit 7     |         |         |         |         |         |         | bit 0   |  |  |  |

|           |         |         |         |         |         |         |         |  |  |  |

|           |         |         |         |         |         |         |         |  |  |  |

| Legend:                                                     |                  |                        |                                            |

|-------------------------------------------------------------|------------------|------------------------|--------------------------------------------|

| R = Readable bit                                            | W = Writable bit | U = Unimplemented bit, | read as '0'                                |

| -n/n = Value at POR and<br>BOR/Value at all other<br>Resets | 1 = bit is set   | 0 = bit is cleared     | x = bit is unknown<br>u = bit is unchanged |

bit 7-0 DSA<15:8>: Destination Start Address bits

### **REGISTER 15-16: DMAxDPTRL: DMAx DESTINATION POINTER LOW REGISTER**

| R-0       | R-0 | R-0 | R-0 | R-0 | R-0 | R-0 | R-0   |  |  |  |  |

|-----------|-----|-----|-----|-----|-----|-----|-------|--|--|--|--|

| DPTR<7:0> |     |     |     |     |     |     |       |  |  |  |  |

| bit 7     |     |     |     |     |     |     | bit 0 |  |  |  |  |

|           |     |     |     |     |     |     |       |  |  |  |  |

|           |     |     |     |     |     |     |       |  |  |  |  |

| Legend:                                                     |                  |                             |                                            |

|-------------------------------------------------------------|------------------|-----------------------------|--------------------------------------------|

| R = Readable bit                                            | W = Writable bit | U = Unimplemented bit, read | as '0'                                     |

| -n/n = Value at POR and<br>BOR/Value at all other<br>Resets | 1 = bit is set   | 0 = bit is cleared          | x = bit is unknown<br>u = bit is unchanged |

bit 7-0 DPTR<7:0>: Current Destination Address Pointer

### **REGISTER 15-17: DMAxDPTRH: DMAx DESTINATION POINTER HIGH REGISTER**

| R-0        | R-0 | R-0 | R-0 | R-0 | R-0 | R-0 | R-0   |  |  |  |

|------------|-----|-----|-----|-----|-----|-----|-------|--|--|--|

| DPTR<15:8> |     |     |     |     |     |     |       |  |  |  |

| bit 7      |     |     |     |     |     |     | bit 0 |  |  |  |

| Legend:                                                     |                  |                           |                                            |

|-------------------------------------------------------------|------------------|---------------------------|--------------------------------------------|

| R = Readable bit                                            | W = Writable bit | U = Unimplemented bit, re | ead as '0'                                 |

| -n/n = Value at POR and<br>BOR/Value at all other<br>Resets | 1 = bit is set   | 0 = bit is cleared        | x = bit is unknown<br>u = bit is unchanged |

bit 7-0 **DPTR<15:8>:** Current Destination Address Pointer

© 2017 Microchip Technology Inc.

### 22.5.1 SOFTWARE GATE MODE

The timer increments with each clock input when ON = 1and does not increment when ON = 0. When the T2TMR count equals the T2PR period count the timer resets on the next clock and continues counting from 0. Operation with the ON bit software controlled is illustrated in Figure 22-4. With T2PR = 5, the counter advances until T2TMR = 5, and goes to zero with the next clock.