Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

-XF

| Product Status             | Active                                                                      |

|----------------------------|-----------------------------------------------------------------------------|

| Core Processor             | PIC                                                                         |

| Core Size                  | 8-Bit                                                                       |

| Speed                      | 64MHz                                                                       |

| Connectivity               | I <sup>2</sup> C, LINbus, SPI, UART/USART                                   |

| Peripherals                | Brown-out Detect/Reset, DMA, HLVD, POR, PWM, WDT                            |

| Number of I/O              | 25                                                                          |

| Program Memory Size        | 128KB (64K x 16)                                                            |

| Program Memory Type        | FLASH                                                                       |

| EEPROM Size                | 1K x 8                                                                      |

| RAM Size                   | 8K x 8                                                                      |

| Voltage - Supply (Vcc/Vdd) | 1.8V ~ 3.6V                                                                 |

| Data Converters            | A/D 24x12b; D/A 1x5b                                                        |

| Oscillator Type            | Internal                                                                    |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                           |

| Mounting Type              | Surface Mount                                                               |

| Package / Case             | 28-VQFN Exposed Pad                                                         |

| Supplier Device Package    | 28-QFN (6x6)                                                                |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/pic18lf27k42-i-ml |

|                            |                                                                             |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

## 1.0 DEVICE OVERVIEW

This document contains device specific information for the following devices:

- PIC18F26K42 PIC18LF26K42

- PIC18F27K42

- PIC18LF27K42

PIC18LF45K42

- PIC18F45K42

- PIC18F46K42 PIC18LF46K42

- PIC18F47K42

- PIC18F55K42

- PIC18LF47K42

PIC18LF55K42

- PIC18F56K42

- PIC18LF56K42

- PIC18F57K42 PIC18LF57K42

- This family offers the advantages of all PIC18 microcontrollers – namely, high computational performance at an economical price – with the addition of high-endurance Program Flash Memory, Universal Asynchronous Receiver Transmitter (UART), Serial Peripheral Interface (SPI), Inter-integrated Circuit (I<sup>2</sup>C), Direct Memory Access (DMA), Configurable Logic Cells (CLC), Signal Measurement Timer (SMT), Numerically Controlled Oscillator (NCO), and Analog-to-Digital Converter with Computation (ADC<sup>2</sup>).

## 1.1 New Features

- Direct Memory Access Controller: The Direct Memory Access (DMA) Controller is designed to service data transfers between different memory regions directly without intervention from the CPU. By eliminating the need for CPU-intensive management of handling interrupts intended for data transfers, the CPU now can spend more time on other tasks.

- Vectored Interrupt Controller: The Vectored Interrupt Controller module reduces the numerous peripheral interrupt request signals to a single interrupt request signal to the CPU. It assembles all of the interrupt request signals and resolves the interrupts based on both a fixed natural order priority and a user-assigned priority, thereby eliminating scanning of interrupt sources.

- Universal Asynchronous Receiver Transmitter: The Universal Asynchronous Receiver Transmitter (UART) module is a serial I/O communications peripheral. It contains all the clock generators, shift registers and data buffers necessary to perform an input or output serial data transfer, independent of device program execution. The UART can be configured as a fullduplex asynchronous system or one of several automated protocols. Full-Duplex mode is useful for communications with peripheral systems, with DMX/DALI/LIN support.

- Serial Peripheral Interface: The Serial Peripheral Interface (SPI) module is a synchronous serial data communication bus that operates in Full-Duplex mode. Devices communicate in a master/slave environment where the master device initiates the communication. A slave device is controlled through a Chip Select known as Slave Select. Example slave devices include serial EEPROMs, shift registers, display drivers, A/D converters, or another PIC.

- I<sup>2</sup>C Module: The I<sup>2</sup>C module provides a synchronous interface between the microcontroller and other I<sup>2</sup>C-compatible devices using the two-wire I<sup>2</sup>C serial bus. Devices communicate in a master/slave environment. The I<sup>2</sup>C bus specifies two signal connections - Serial Clock (SCL) and Serial Data (SDA). Both the SCL and SDA connections are bidirectional open-drain lines, each requiring pull-up resistors to the supply voltage.

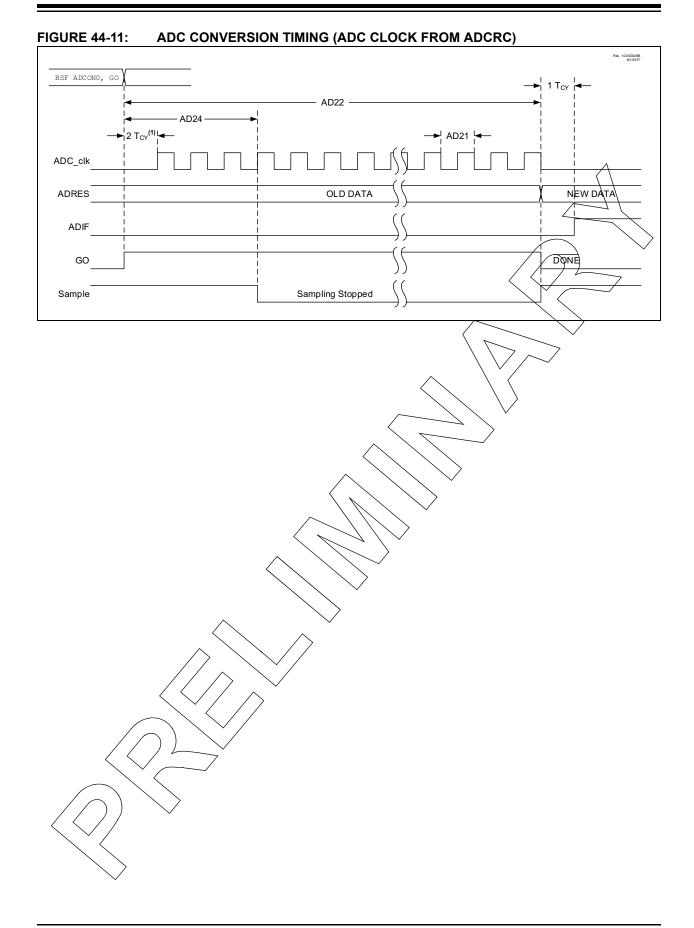

- **12-bit A/D Converter with Computation:** This module incorporates programmable acquisition time, allowing for a channel to be selected and a conversion to be initiated without waiting for a sampling period and thus, reduces code overhead. It has a new module called ADC<sup>2</sup> with computation features, which provides a digital filter and threshold interrupt functions.

## 1.2 Details on Individual Family Members

Devices in the PIC18(L)F26/27/45/46/47/55/56/57K42 family are available in 28-pin and 40/44/48-pin packages. The block diagram for this device is shown in Figure 3-1.

The similarities and differences among the devices are listed in the PIC18(L)F2X/4X/5XK42 Family Types Table (page 4). The pinouts for all devices are listed in Table 1.

## 5.0 DEVICE CONFIGURATION

Device configuration consists of the Configuration Words, User ID, Device ID, Rev ID, Device Information Area (DIA), (see Section 5.7 "Device Information Area"), and the Device Configuration Information (DCI) regions, (see Section 5.8 "Device Configuration Information").

## 5.1 Configuration Words

There are six Configuration Word bits that allow the user to setup the device with several choices of oscillators, Resets and memory protection options. These are implemented as Configuration Word 1 through Configuration Word 6 at 300000h through 30000Bh.

## 5.5 Device ID and Revision ID

The 16-bit device ID word is located at 3F FFFEh and the 16-bit revision ID is located at 3F FFFCh. These locations are read-only and cannot be erased or modified.

Development tools, such as device programmers and debuggers, may be used to read the Device ID, Revision ID and Configuration Words. Refer to **13.0 "Nonvolatile Memory (NVM) Control"** for more information on accessing these locations.

## 5.6 Register Definitions: Device ID and Revision ID

| R       | R | R | R     | R    | R | R | R     |

|---------|---|---|-------|------|---|---|-------|

|         |   |   | DEV<1 | 5:8> |   |   |       |

| bit 15  |   |   |       |      |   |   | bit 8 |

|         |   |   |       |      |   |   |       |

| R       | R | R | R     | R    | R | R | R     |

|         |   |   | DEV<  | 7:0> |   |   |       |

| bit 7   |   |   |       |      |   |   | bit 0 |

|         |   |   |       |      |   |   |       |

| Legend: |   |   |       |      |   |   |       |

| Legena.          |                  |                     |                    |  |

|------------------|------------------|---------------------|--------------------|--|

| R = Readable bit | '1' = Bit is set | 0' = Bit is cleared | x = Bit is unknown |  |

bit 15-0 **DEV<15:0>:** Device ID bits

| Device       | Device ID |

|--------------|-----------|

| PIC18F26K42  | 6C60h     |

| PIC18F27K42  | 6C40h     |

| PIC18F45K42  | 6C20h     |

| PIC18F46K42  | 6C00h     |

| PIC18F47K42  | 6BE0h     |

| PIC18F55K42  | 6BC0h     |

| PIC18F56K42  | 6BA0h     |

| PIC18F57K42  | 6B80h     |

| PIC18LF26K42 | 6DA0h     |

| PIC18LF27K42 | 6D80h     |

| PIC18LF45K42 | 6D60h     |

| PIC18LF46K42 | 6D40h     |

| PIC18LF47K42 | 6D20h     |

| PIC18LF55K42 | 6D00h     |

| PIC18LF56K42 | 6CE0h     |

| PIC18LF57K42 | 6CC0h     |

© 2017 Microchip Technology Inc.

## 9.0 INTERRUPT CONTROLLER

The Vectored Interrupt Controller module reduces the numerous peripheral interrupt request signals to a single interrupt request signal to the CPU. This module includes the following major features:

- Interrupt Vector Table (IVT) with a unique vector for each interrupt source

- · Fixed and ensured interrupt latency

- Programmable base address for Interrupt Vector Table (IVT) with lock

- Two user-selectable priority levels High priority and Low priority

- Two levels of context saving

- Interrupt state status bits to indicate the current execution status of the CPU

The Interrupt Controller module assembles all of the interrupt request signals and resolves the interrupts based on both a fixed natural order priority (i.e., determined by the Interrupt Vector Table), and a user-assigned priority (i.e., determined by the IPRx registers), thereby eliminating scanning of interrupt sources.

## 9.1 Interrupt Control and Status Registers

The devices in this family implement the following registers for the interrupt controller:

- INTCON0, INTCON1 Control Registers

- PIRx Peripheral Interrupt Status Registers

- PIEx Peripheral Interrupt Enable Registers

- IPRx Peripheral Interrupt Priority Registers

- IVTBASE<20:0> Address Registers

- IVTLOCK Register

Global interrupt control functions and external interrupts are controlled from the INTCON0 register. The INTCON1 register contains the status flags for the Interrupt controller.

The PIRx registers contain all of the interrupt request flags. Each source of interrupt has a status bit, which is set by the respective peripherals or an external signal and is cleared via software.

The PIEx registers contain all of the interrupt enable bits. These control bits are used to individually enable interrupts from the peripherals or external signals.

The IPRx registers are used to set the Interrupt Priority Level for each source of interrupt. Each user interrupt source can be assigned to either a high or low priority.

The IVTBASE register is user programmable and is used to determine the start address of the Interrupt Vector Table and the IVTLOCK register is used to prevent any unintended writes to the IVTBASE register. There are two other configuration bits that control the way the interrupt controller can be configured.

- · CONFIG2L<3>, MVECEN bit

- CONFIG2L<4>, IVT1WAY bit

The MVECEN bit in CONFIG2L determines whether the Vector table is used to determine the interrupt priorities.

When the IVT1WAY determines the number of times the IVTLOCKED bit can be cleared and set after a device Reset. See Section

9.2.3 "Interrupt Vector Table (IVT) address calculation" for details.

## FIGURE 10-2: WAKE-UP FROM SLEEP THROUGH INTERRUPT

| Q1 Q2 Q3 Q4 Q1 Q2 Q3 Q4 Q1                         | 01/02/03/04         |                    | Q3 Q4 Q1 Q2 Q3 Q4   |

|----------------------------------------------------|---------------------|--------------------|---------------------|

|                                                    |                     |                    |                     |

|                                                    | Tost <sup>(3)</sup> | ·/                 |                     |

| Interrupt flag                                     | / Interrupt Late    | ncy <sup>(4)</sup> |                     |

| GIE bit<br>(INTCON reg.)<br>Sleet                  |                     | <u>.</u>           |                     |

| Instruction Flow<br>PC X PC X PC + 1 X             | PC + 2 X PC + 2     | PC+2 00            | 004h X 0005h        |

| Instruction { Inst(PC) = Sleep Inst(PC + 1)        | Inst(PC + 2)        | Inst               | (0004h) Inst(0005h) |

| Instruction { Inst(PC - 1) Sleep                   | Inst(PC + 1)        | Forced NOP Force   | ed NOP Inst(0004h)  |

| Note 1: External clock. High, Medium, Low mode ass | umed.               |                    |                     |

2: CLKOUT is shown here for timing reference.

3: TOST = 1024 TOSC. This delay does not apply to EC and INTOSC Oscillator modes.

4: GIE = 1 assumed. In this case after wake-up, the processor calls the ISR at 0004h. If GIE = 0, execution will continue in-line.

#### 10.2.3 LOW-POWER SLEEP MODE

The PIC18F26/27/45/46/47/55/56/57K42 device family contains an internal Low Dropout (LDO) voltage regulator, which allows the device I/O pins to operate at voltages up to 5.5V while the internal device logic operates at a lower voltage. The LDO and its associated reference circuitry must remain active when the device is in Sleep mode.

The PIC18F26/27/45/46/47/55/56/57K42 devices allow the user to optimize the operating current in Sleep, depending on the application requirements.

Low-Power Sleep mode can be selected by setting the VREGPM bit of the VREGCON register.

## 10.2.3.1 Sleep Current vs. Wake-up Time

In the default operating mode, the LDO and reference circuitry remain in the normal configuration while in Sleep. The device is able to exit Sleep mode quickly since all circuits remain active. In Low-Power Sleep mode, when waking-up from Sleep, an extra delay time is required for these circuits to return to the normal configuration and stabilize.

The Low-Power Sleep mode is beneficial for applications that stay in Sleep mode for long periods of time. The Normal mode is beneficial for applications that need to wake from Sleep quickly and frequently.

## 13.1 Program Flash Memory

The Program Flash Memory is readable, writable and erasable during normal operation over the entire VDD range.

A read from program memory is executed one byte at a time. A write to program memory or program memory erase is executed on blocks of n bytes at a time. Refer to Table 5-4 for write and erase block sizes. A Bulk Erase operation cannot be issued from user code.

Writing or erasing program memory will cease instruction fetches until the operation is complete. The program memory cannot be accessed during the write or erase, therefore, code cannot execute. An internal programming timer terminates program memory writes and erases.

A value written to program memory does not need to be a valid instruction. Executing a program memory location that forms an invalid instruction results in a NOP.

It is important to understand the PFM memory structure for erase and programming operations. Program memory word size is 16 bits wide. PFM is arranged in rows. A row is the minimum size that can be erased by user software. Refer to Table 5-4 for the row sizes for these devices.

After a row has been erased, all or a portion of this row can be programmed. Data to be written into the program memory row is written to 8-bit wide data write latches by means of 6 address lines. These latches are not directly accessible, but may be loaded via sequential writes to the TABLAT register.

**Note:** To modify only a portion of a previously programmed row, then the contents of the entire row must be read and saved in RAM prior to the erase. Then, the new data and retained data can be written into the write latches to reprogram the row of PFM. However, any unprogrammed locations can be written without first erasing the row. In this case, it is not necessary to save and rewrite the other previously programmed locations.

## REGISTER 14-9: CRCXORH: CRC XOR HIGH BYTE REGISTER

| R/W-x/x         | R/W-x/x | R/W-x/x         | R/W-x/x | R/W-x/x        | R/W-x/x          | R/W-x/x          | R/W-x/x     |

|-----------------|---------|-----------------|---------|----------------|------------------|------------------|-------------|

|                 |         |                 | X<1     | 5:8>           |                  |                  |             |

| bit 7           |         |                 |         |                |                  |                  | bit 0       |

|                 |         |                 |         |                |                  |                  |             |

| Legend:         |         |                 |         |                |                  |                  |             |

| R = Readable    | bit     | W = Writable    | bit     | U = Unimplen   | nented bit, read | l as '0'         |             |

| u = Bit is unch | anged   | x = Bit is unkr | nown    | -n/n = Value a | at POR and BO    | R/Value at all o | ther Resets |

bit 7-0 X<15:8>: XOR of Polynomial Term X<sup>n</sup> Enable bits

#### REGISTER 14-10: CRCXORL: CRC XOR LOW BYTE REGISTER

'0' = Bit is cleared

| R/W-x/x | U-1   |

|---------|---------|---------|---------|---------|---------|---------|-------|

|         |         |         | X<7:1>  |         |         |         | —     |

| bit 7   |         |         |         |         |         |         | bit 0 |

| Legend:              |                      |                                                       |

|----------------------|----------------------|-------------------------------------------------------|

| R = Readable bit     | W = Writable bit     | U = Unimplemented bit                                 |

| u = Bit is unchanged | x = Bit is unknown   | -n/n = Value at POR and BOR/Value at all other Resets |

| '1' = Bit is set     | '0' = Bit is cleared |                                                       |

bit 7-1 X<7:1>: XOR of Polynomial Term X<sup>n</sup> Enable bits

bit 0 Unimplemented: Read as '1'

'1' = Bit is set

## 15.0 DIRECT MEMORY ACCESS (DMA)

## 15.1 Introduction

The Direct Memory Access (DMA) module is designed to service data transfers between different memory regions directly without intervention from the CPU. By eliminating the need for CPU-intensive management of handling interrupts intended for data transfers, the CPU now can spend more time on other tasks.

PIC18(L)F26/27/45/46/47/55/56/57K42 family has two DMA modules which can be independently programmed to transfer data between different memory locations, move different data sizes, and use a wide range of hardware triggers to initiate transfers. The two DMA registers can even be programmed to work together, in order to carry out more complex data transfers without CPU overhead.

Key features of the DMA module include:

- Support access to the following memory regions:

- GPR and SFR space (R/W)

- Program Flash Memory (R only)

- Data EEPROM Memory (R only)

- Programmable priority between the DMA and CPU Operations. Refer to Section 3.1 "System Arbitration" for details.

- Programmable Source and Destination address

modes

- Fixed address

- Post-increment address

- Post-decrement address

- Programmable Source and Destination sizes

- Source and destination pointer register, dynamically updated and reloadable

- Source and destination count register, dynamically updated and reloadable

- Programmable auto-stop based on Source or Destination counter

- · Software triggered transfers

- Multiple user selectable sources for hardware triggered transfers

- Multiple user selectable sources for aborting DMA transfers

## 15.2 DMA Registers

The operation of the DMA module has the following registers:

- Control registers (DMAxCON0, DMAxCON1)

- Data buffer register (DMAxBUF)

- Source Start Address Register (DMAxSSAU:H:L)

- Source Pointer Register (DMAxSPTRU:H:L)

- · Source Message Size Register (DMAxSSZH:L)

- Source Count Register (DMAxSCNTH:L)

- Destination Start Address Register (DMAxDSAH:L)

- Destination Pointer Register (DMAxDPTRH:L)

- Destination Message Size Register (DMAxDSZH:L)

- Destination Count Register (DMAxDCNTH:L)

- Start Interrupt Request Source Register (DMAxSIRQ)

- Abort Interrupt Request Source Register (DMAxAIRQ)

These registers are detailed in Section 15.13 "Register definitions: DMA".

## TABLE 15-6: EXAMPLE DMA USE CASE TABLE

| Source Module                         | Source Register(s)   | Destination Module   | Destination Register(s)                | DCHxSIRQ  | Comment                                                                      |

|---------------------------------------|----------------------|----------------------|----------------------------------------|-----------|------------------------------------------------------------------------------|

| Signal Measurement<br>Timer           | SMTxCPW[U:H:L]       | GPR                  | GPR[x,y,z]                             | SMTxPWAIF | Store Captured Pulse-width values                                            |

| (SMT)                                 | SMTxCPR[U:H:L]       |                      |                                        | SMTxPRAIF | Store Captured Period values                                                 |

| GPR/SFR/Program<br>Flash/Data EEPROM  | MEMORY[x,y]          | TMR0                 | TMR0[H:L]                              | TMR0IF    | Use as a Timer0 reload for<br>custom 16-bit value                            |

| GPR/SFR/ Program<br>Flash/Data EEPROM | MEMORY[x]            | TMR0                 | PR0                                    | ANY       | Update TMR0 frequency<br>based on a specific trigger                         |

| GPR/SFR/ Program<br>Flash/Data EEPROM | MEMORY[x,y]          | TMR1                 | TMR1[H:L]                              | TMR1IF    | Use as a Timer1 reload for<br>custom 16-bit value                            |

| TMR1                                  | TMR1[H:L]            | GPR                  | GPR[x,y]                               | TMR1GIF   | Use TMR1 Gate interrupt flag<br>to read data out of TMR1<br>register         |

| GPR/SFR/ Program<br>Flash/Data EEPROM | MEMORY[x]            | TMR2                 | PR2                                    | TMR2IF    |                                                                              |

| GPR/SFR/ Program<br>Flash/Data EEPROM | MEMORY[x,y,z]        | TMR2<br>CCP or PWM   | PR2<br>CCPR[H:L] or<br>PWMDC[H:L]      | ANY       | Frequency generator with 50% duty cycle look up table                        |

| ССР                                   | CCPR[H:L]            | GPR                  | GPR[x,y]                               | CCPxIF    | Move data from CCP 16b<br>Capture                                            |

| GPR/SFR/ Program<br>Flash/Data EEPROM | MEMORY[x,y]          | CCP                  | CCPR[H:L]                              | ANY       | Load Compare value or PWM values into the CCP                                |

| GPR/SFR/ Program<br>Flash/Data EEPROM | MEMORY [x,y,z,u,v,w] | CCPx<br>CCPy<br>CCPz | CCPxR[H:L]<br>CCPyR[H:L]<br>CCPzR[H:L] | ANY       | Update multiple PWM values<br>at the same time<br>e.g. 3-phase motor control |

| GPR/SFR/ Program<br>Flash/Data EEPROM | MEMORY[x,y,z]        | NCO                  | NCOxINC[U:H:L]                         | ANY       | Frequency Generator look-up table                                            |

| GPR/SFR/ Program<br>Flash/Data EEPROM | MEMORY[x]            | DAC                  | DACxCON0                               | ANY       | Update DAC values                                                            |

| GPR/SFR/ Program<br>Flash/Data EEPROM | MEMORY[x]            | OSCTUNE              | OSCTUNE                                | ANY       | Automated Frequency dithering                                                |

# PIC18(L)F26/27/45/46/47/55/56/57K42

x = bit is unknown u = bit is unchanged

| REGISTE   | R 15-1: DM | AXCON0: DMA      | CONTROL | . REGISTER  | <b>K O</b>       |          |             |

|-----------|------------|------------------|---------|-------------|------------------|----------|-------------|

| R/W-0/0   | R/W/HC-0/0 | R/W/HS/HC-0/0    | U-0     | U-0         | R/W/HC-0/0       | U-0      | R/HS/HC-0/0 |

| EN        | SIRQEN     | DGO              | _       | _           | AIRQEN           | _        | XIP         |

| bit 7     |            |                  |         |             |                  |          | bit 0       |

|           |            |                  |         |             |                  |          |             |

| Legend:   |            |                  |         |             |                  |          |             |

| R = Reada | able bit   | W = Writable bit |         | U = Unimple | mented bit, read | d as '0' |             |

| -n/n = Value at POR  | 0 = bit is cleared | 1 |

|----------------------|--------------------|---|

| and BOR/Value at all |                    | I |

| other Resets         |                    |   |

|                      |                    |   |

| bit 7 EN: DMA Module Enable b | oit |

|-------------------------------|-----|

|-------------------------------|-----|

- 1 = Enables module

- 0 = Disables module

- SIRQEN: Start of Transfer Interrupt Request Enable bits

- 1 = Hardware triggers are allowed to start DMA transfers

- 0 = Hardware triggers are not allowed to start DMA transfers

## bit 5 DGO: DMA transaction bit

bit 6

- 1 = DMA transaction is in progress

- 0 = DMA transaction is not in progress

- bit 4-3 Unimplemented: Read as '0'

## bit 2 AIRQEN: Abort of Transfer Interrupt Request Enable bits

- 1 = Hardware triggers are allowed to abort DMA transfers

- 0 = Hardware triggers are not allowed to abort DMA transfers

## bit 1 Unimplemented: Read as '0'

- bit 0 XIP: Transfer in Progress Status bit

- 1 = The DMAxBUF register currently holds contents from a read operation and has not transferred data to the destination.

- 0 = The DMAxBUF register is empty or has successfully transferred data to the destination address

## TABLE 16-11: SUMMARY OF REGISTERS ASSOCIATED WITH I/O (CONTINUED)

| Name                  | Bit 7   | Bit 6   | Bit 5   | Bit 4                  | Bit 3                  | Bit 2   | Bit 1                  | Bit 0                  | Register on<br>Page |

|-----------------------|---------|---------|---------|------------------------|------------------------|---------|------------------------|------------------------|---------------------|

| INLVLC                | INLVLC7 | INLVLC6 | INLVLC5 | INLVLC4 <sup>(5)</sup> | INLVLC3 <sup>(5)</sup> | INLVLC2 | INLVLC1                | INLVLC0                | 270                 |

| INLVLD <sup>(6)</sup> | INLVLD7 | INLVLD6 | INLVLD5 | INLVLD4                | INLVLD3                | INLVLD2 | INLVLD1 <sup>(5)</sup> | INLVLD0 <sup>(5)</sup> | 270                 |

| INLVLF <sup>(7)</sup> | INLVLF7 | INLVLF6 | INLVLF5 | INLVLF4                | INLVLF3                | INLVLF2 | INLVLF1                | INLVLF0                | 270                 |

| INLVLE                | _       | _       | _       | _                      | INLVLE3                | _       | —                      | _                      | 270                 |

| RB1I2C                | _       | SLEW    | PU<     | 1:0>                   | _                      | _       | TH<                    | 1:0>                   | 271                 |

| RB2I2C                | _       | SLEW    | PU<     | 1:0>                   | _                      | _       | TH<                    | 1:0>                   | 271                 |

| RC3I2C                | _       | SLEW    | PU<     | PU<1:0>                |                        | _       | TH<1:0>                |                        | 271                 |

| RC4I2C                | _       | SLEW    | PU<1:0> |                        | _                      | _       | TH<1:0>                |                        | 271                 |

| RD0I2C <sup>(6)</sup> | _       | SLEW    | PU<1:0> |                        | _                      | _       | TH<1:0>                |                        | 271                 |

| RD1I2C <sup>(6)</sup> | —       | SLEW    | PU<     | 1:0>                   | —                      | _       | TH<                    | 1:0>                   | 271                 |

Legend: - = unimplemented location, read as '0'. Shaded cells are not used by I/O Ports.

Note 1:

Bits RB6 and RB7 read '1' while in Debug mode. Bit PORTE3 is read-only, and will read '1' when MCLRE = 1 (Master Clear enabled). Bits RB6 and RB7 read '1' while in Debug mode. 2:

3:

4: If MCLRE = 1, the weak pull-up in RE3 is always enabled; bit WPUE3 is not affected.

5: Any peripheral using the I<sup>2</sup>C pins read the I<sup>2</sup>C ST inputs when enabled via RxyI2C.

Unimplemented in PIC18(L)F26/27K42. 6:

7: Unimplemented in PIC18(L)F26/27/45/46/47K42 parts.

|       |     |     |     |     |         |          | •       |

|-------|-----|-----|-----|-----|---------|----------|---------|

| U-0   | U-0 | U-0 | U-0 | U-0 | R/W-0/x | R/W-0/x  | R/W-0/x |

| —     | —   | —   | _   | —   |         | CTS<2:0> |         |

| bit 7 |     |     |     |     |         |          | bit 0   |

## REGISTER 23-3: CCPxCAP: CAPTURE INPUT SELECTION MULTIPLEXER REGISTER

| Legend:           |                  |                             |                    |  |

|-------------------|------------------|-----------------------------|--------------------|--|

| R = Readable bit  | W = Writable bit | U = Unimplemented bit, read | l as '0'           |  |

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared        | x = Bit is unknown |  |

#### bit 7-3 Unimplemented: Read as '0'

bit 2-0 CTS<2:0>: Capture Trigger Input Selection bits

| CTS<1:0> |                            | Connection                 |                            |                            |  |  |  |

|----------|----------------------------|----------------------------|----------------------------|----------------------------|--|--|--|

| 019<1.02 | CCP1                       | CCP2                       | CCP3                       | CCP4                       |  |  |  |

| 111      |                            | CLC                        | 4_out                      |                            |  |  |  |

| 110      |                            | CLC                        | 3_out                      |                            |  |  |  |

| 101      |                            | CLC2_out                   |                            |                            |  |  |  |

| 100      |                            | CLC                        | 1_out                      |                            |  |  |  |

| 011      |                            | IOC_Ir                     | nterrupt                   |                            |  |  |  |

| 010      |                            | CMP2_output                |                            |                            |  |  |  |

| 001      | CMP1_output                |                            |                            |                            |  |  |  |

| 000      | Pin selected by<br>CCP1PPS | Pin selected by<br>CCP2PPS | Pin selected by<br>CCP3PPS | Pin selected by<br>CCP4PPS |  |  |  |

#### REGISTER 23-4: CCPRxL: CCPx REGISTER LOW BYTE

| R/W-x/x |

|---------|---------|---------|---------|---------|---------|---------|---------|

| RL<7:0> |         |         |         |         |         |         |         |

| bit 7   |         |         |         |         |         |         | bit 0   |

| Legend:           |                  |                       |                    |

|-------------------|------------------|-----------------------|--------------------|

| R = Readable bit  | W = Writable bit | U = Unimplemented bit | , read as '0'      |

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared  | x = Bit is unknown |

bit 7-0

MODE = Capture Mode:

RL<7:0>: LSB of captured TMR1 value

MODE = Compare Mode:

RL<7:0>: LSB compared to TMR1 value

MODE = PWM Mode && FMT = 0:

RL<7:0>: CCPW<7:0> - Pulse-Width LS 8 bits

MODE = PWM Mode && FMT = 1:

RL<7:6>: CCPW<1:0> - Pulse-Width LS 2 bits

RL<5:0>: Not used

| SELECTION          |                   |  |  |  |  |  |

|--------------------|-------------------|--|--|--|--|--|

| DyS<5:0><br>Value  | CLCx Input Source |  |  |  |  |  |

| 111111 <b>[63]</b> | Reserved          |  |  |  |  |  |

|                    |                   |  |  |  |  |  |

| •                  |                   |  |  |  |  |  |

| •                  |                   |  |  |  |  |  |

| 110100 <b>[52]</b> | Reserved          |  |  |  |  |  |

| 110011 <b>[51]</b> | CWG3B_out         |  |  |  |  |  |

| 110010 <b>[50]</b> | CWG3A_out         |  |  |  |  |  |

| 110001 <b>[49]</b> | CWG2B_out         |  |  |  |  |  |

| 110000 <b>[48]</b> | CWG2A_out         |  |  |  |  |  |

| 101111 <b>[47]</b> | CWG1B_out         |  |  |  |  |  |

| 101110 <b>[46]</b> | CWG1A_out         |  |  |  |  |  |

| 101101 <b>[45]</b> | SS1               |  |  |  |  |  |

| 101100 [44]        | SCK1              |  |  |  |  |  |

| 101011 <b>[43]</b> | SDO1              |  |  |  |  |  |

| 101010 <b>[42]</b> | Reserved          |  |  |  |  |  |

| 101001 <b>[41]</b> | UART2_tx_out      |  |  |  |  |  |

| 101000 <b>[40]</b> | UART1_tx_out      |  |  |  |  |  |

| 100111 <b>[39]</b> | CLC4_out          |  |  |  |  |  |

| 100110 <b>[38]</b> | CLC3_out          |  |  |  |  |  |

| 100101 [37]        | CLC2_out          |  |  |  |  |  |

| 100100 <b>[36]</b> | CLC1_out          |  |  |  |  |  |

| 100011 <b>[35]</b> | DSM1_out          |  |  |  |  |  |

| 100010 [34]        | IOC_flag          |  |  |  |  |  |

| 100001 [33]        | ZCD_out           |  |  |  |  |  |

| 100000 [32]        | CMP2_out          |  |  |  |  |  |

| 011111 [31]        | CMP1_out          |  |  |  |  |  |

| 011110 [30]        | NCO1_out          |  |  |  |  |  |

| 011101 [29]        | Reserved          |  |  |  |  |  |

| 011100 [28]        | Reserved          |  |  |  |  |  |

| 011011 [27]        | PWM8_out          |  |  |  |  |  |

| 011010 [26]        | PWM7_out          |  |  |  |  |  |

| 011001 [25]        | PWM6_out          |  |  |  |  |  |

| 011000 [24]        | PWM5_out          |  |  |  |  |  |

| 010111 [23]        | CCP4_out          |  |  |  |  |  |

| 010110 [22]        | CCP3_out          |  |  |  |  |  |

| 010101 [21]        | CCP2_out          |  |  |  |  |  |

| 010100 [20]        | CCP1_out          |  |  |  |  |  |

| 010011 [19]        | SMT1_out          |  |  |  |  |  |

| 010010 [18]        | TMR6_out          |  |  |  |  |  |

| 010001 [17]        | TMR5_overflow     |  |  |  |  |  |

| 010000 [16]        | TMR4 _out         |  |  |  |  |  |

| 001111 [15]        | TMR3 _overflow    |  |  |  |  |  |

## TABLE 27-1: CLCx DATA INPUT SELECTION

## TABLE 27-1:CLCx DATA INPUT SELECTION<br/>(CONTINUED)

| DyS<5:0><br>Value  | CLCx Input Source  |

|--------------------|--------------------|

| 001110 <b>[14]</b> | TMR2 _out          |

| 001101 <b>[13]</b> | TMR1 _overflow     |

| 001100 <b>[12]</b> | TMR0 _overflow     |

| 001011 <b>[11]</b> | CLKR _out          |

| 001010 <b>[10]</b> | ADCRC              |

| 001001 [9]         | SOSC               |

| 001000 <b>[8]</b>  | MFINTOSC (32 kHz)  |

| 000111 [7]         | MFINTOSC (500 kHz) |

| 000110 [6]         | LFINTOSC           |

| 000101 <b>[5]</b>  | HFINTOSC           |

| 000100 <b>[4]</b>  | Fosc               |

| 000011 <b>[3]</b>  | CLCIN3PPS          |

| 000010 [2]         | CLCIN2PPS          |

| 000001 [1]         | CLCIN1PPS          |

| 000000 <b>[0]</b>  | CLCINOPPS          |

## 27.1.2 DATA GATING

Outputs from the input multiplexers are directed to the desired logic function input through the data gating stage. Each data gate can direct any combination of the four selected inputs.

#### Note: Data gating is undefined at power-up.

The gate stage is more than just signal direction. The gate can be configured to direct each input signal as inverted or non-inverted data. Directed signals are ANDed together in each gate. The output of each gate can be inverted before going on to the logic function stage.

The gating is in essence a 1-to-4 input AND/NAND/OR/ NOR gate. When every input is inverted and the output is inverted, the gate is an OR of all enabled data inputs. When the inputs and output are not inverted, the gate is an AND or all enabled inputs.

Table 27-2 summarizes the basic logic that can be obtained in gate 1 by using the gate logic select bits. The table shows the logic of four input variables, but each gate can be configured to use less than four. If no inputs are selected, the output will be zero or one, depending on the gate output polarity bit.

#### TABLE 27-2: DATA GATING LOGIC

| CLCxGLSy | GyPOL | Gate Logic |

|----------|-------|------------|

| 0x55     | 1     | AND        |

| 0x55     | 0     | NAND       |

| 0xAA     | 1     | NOR        |

| 0xAA     | 0     | OR         |

| 0x00     | 0     | Logic 0    |

| 0x00     | 1     | Logic 1    |

It is possible (but not recommended) to select both the true and negated values of an input. When this is done, the gate output is zero, regardless of the other inputs, but may emit logic glitches (transient-induced pulses). If the output of the channel must be zero or one, the recommended method is to set all gate bits to zero and use the gate polarity bit to set the desired level.

Data gating is configured with the logic gate select registers as follows:

- Gate 1: CLCxGLS0 (Register 29-18)

- Gate 2: CLCxGLS1 (Register 29-19)

- Gate 3: CLCxGLS2 (Register 29-20)

- Gate 4: CLCxGLS3 (Register 29-21)

Register number suffixes are different than the gate numbers because other variations of this module have multiple gate selections in the same register. Data gating is indicated in the right side of Figure 27-2. Only one gate is shown in detail. The remaining three gates are configured identically with the exception that the data enables correspond to the enables for that gate.

#### 27.1.3 LOGIC FUNCTION

There are eight available logic functions including:

- AND-OR

- OR-XOR

- AND

- S-R Latch

- D Flip-Flop with Set and Reset

- D Flip-Flop with Reset

- J-K Flip-Flop with Reset

- · Transparent Latch with Set and Reset

Logic functions are shown in Figure 27-2. Each logic function has four inputs and one output. The four inputs are the four data gate outputs of the previous stage. The output is fed to the inversion stage and from there to other peripherals, an output pin, and back to the CLCx itself.

## 27.1.4 OUTPUT POLARITY

The last stage in the Configurable Logic Cell is the output polarity. Setting the POL bit of the CLCxPOL register inverts the output signal from the logic stage. Changing the polarity while the interrupts are enabled will cause an interrupt for the resulting output transition.

## 32.5.3 RECEIVE ONLY MODE

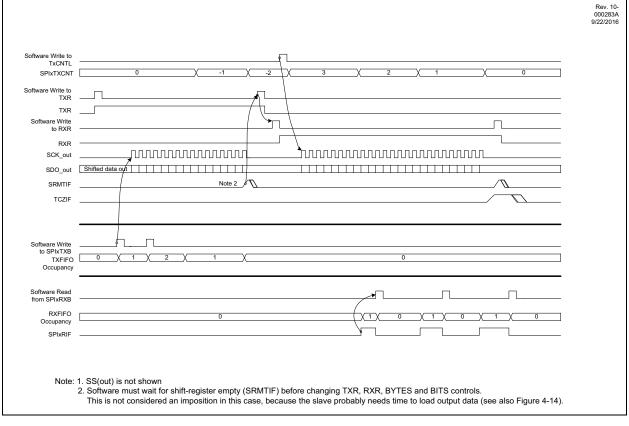

When RXR is set and TXR is clear, the SPI master is in Receive Only mode. In this mode, data transfers when the RXFIFO is not full and the Transfer Counter is nonzero. In this mode, writing a value to SPIxTCNTL will start the clocks for transfer. The clocks will suspend while the RXFIFO is full and cease when the SPIxTCNT reaches zero (see Section 32.4 "Transfer Counter"). If there is any data in the TXFIFO, the first data written to the TXFIFO will be transmitted on each data exchange, although the TXFIFO occupancy will not change, meaning that the same message will be sent on each transmission. If there is no data in the TXFIFO, the most recently received data will instead be transmitted. Figure 32-5 shows an example of sending a command using Section 32.5.2 "Transmit Only Mode" and then receiving a byte of data using this mode.

## 32.5.4 TRANSFER OFF MODE

When both TXR and RXR are cleared, the SPI master is in Transfer Off mode. In this mode, SCK will not toggle and no data is exchanged. However, writes to SPIxTXB will be transferred to the TXFIFO which will be transmitted if the TXR bit is set.

## 33.5 I<sup>2</sup>C Master Mode

Master mode is enabled by setting and clearing the appropriate Mode<2:0> bits in I2CxCON and then by setting the I2CEN bit. Master mode of operation is supported by interrupt generation on buffer full (RXIF), buffer empty (TXIF), and the detection of the Start, Restart, and Stop conditions. The Stop (P), Restart (RS) and Start (S) bits are cleared from a Reset or when the I<sup>2</sup>C module is disabled. Control of the I<sup>2</sup>C bus is asserted when the BFRE bit of I2CSTAT0 is set.

## 33.5.1 I<sup>2</sup>C MASTER MODE OPERATION

The master device generates all of the serial clock pulses and the Start, Restart, and Stop conditions. A transfer is ended with a Stop condition or with a Restart condition. Since the Repeated Start condition is also the beginning of the next serial transfer, the I<sup>2</sup>C bus will not be released, and MMA bit will stay set signifying that the Master module is still active.

The steps to initiate a transaction depends on the setting of the address buffer disable bit (ABD) of the I2CxCON2 register.

• ABD = 0 (Address buffers are enabled)

In this case, the master module will use the address stored in the address buffer registers (I2CxADB0/1) to initiate communication with a slave device. User software needs to set the Start bit (S) in the I2CxCON0 register to start communication. This is valid for both 7-bit and 10-bit Addressing modes.

• ABD = 1 (Address buffers are disabled)

In this case, the slave address is transmitted through the transmit buffer and the contents of the address buffers are ignored. User software needs to write the slave address to the transmit buffer (I2CxTXB) to initiate communication. Writing to the Start bit is ignored in this mode. This is valid for both 7-bit and 10bit Addressing modes.

## 33.5.1.1 Master Transmitter

In Master Transmitter mode, the first byte transmitted contains the slave address of the receiving device (7 bits) and the Read/Write (R/W) bit. In the case of master transmitter, the R/W bit will be logic '0'. Serial data is transmitted eight bits at a time. After each byte is transmitted, an Acknowledge bit is received. Start and Stop conditions are output to indicate the beginning and the end of a serial transfer.

## 33.5.1.2 Master Receiver

In Master Receive mode, the first byte transmitted contains the slave address of the transmitting device (7 bits) and the R/W bit. In this case, the R/W bit will be logic '1'. Thus, the first byte transmitted is a 7-bit slave address followed by a '1' to indicate the receive bit. Serial data is received via SDA, while SCL outputs the serial clock. Serial data is received eight bits at a time.

After each byte is received, an Acknowledge bit is transmitted. Start and Stop conditions indicate the beginning and end of the transmission.

## 33.5.2 MASTER CLOCK SOURCE AND ARBITRATION

The  $I^2C$  module clock source is selected by the I2CxCLK register. The  $I^2C$  Clock provides the SCL output clock for Master mode and is used by the Bus Free timer. The  $I^2C$  clock can be sourced from several peripherals.

## 33.5.3 BUS FREE TIME

In Master modes, the BFRE bit of the I2CxSTAT0 register gives an indication of the bus idle status. The master hardware cannot assert a Start condition until this bit is set by the hardware. This prevents the master from colliding with other masters that may already be talking on the bus. The BFRET<1:0> bits of I2CxCON1 allow selection of 8 to 64 pulses of the I<sup>2</sup>C clock input before asserting the BFRE bit. The BFRET bits are used to ensure that the I<sup>2</sup>C module always follows the minimum Stop Hold Time. The I<sup>2</sup>C timing requirements are listed in the electrical specifications chapter.

| Note: | I <sup>2</sup> C clock is not required to have a 50% |

|-------|------------------------------------------------------|

|       | duty cycle.                                          |

## 33.5.4 MASTER CLOCK TIMING

The clock generation in the  $l^2C$  module can be configured using the Fast Mode Enable (FME) bit of the l2CxCON2 register. This bit controls the number of times the SCL pin is sampled before the master hardware drives it.

## 33.5.4.1 Clock Timing with FME = 0

One Tscl, consists of five clocks of the  $I^2C$  clock input. The first clock is used to drive SCL low, the third releases SCL high. The fourth and fifth clocks are used to detect if the SCL pin is, in fact, high or being stretched by a slave.

If a slave is clock stretching, the hardware waits; checking SCL on each successive  $I^2C$  clock, proceeding only after detecting SCL high. Figure 33-13 shows the clock synthesis timing when FME = 0.

# PIC18(L)F26/27/45/46/47/55/56/57K42

| REGISTER 33-7: I2CxSTAT1: I <sup>2</sup> C STATUS REGISTER 1 |     |                        |     |                     |         |     |                       |

|--------------------------------------------------------------|-----|------------------------|-----|---------------------|---------|-----|-----------------------|

| R/W/HS-0                                                     | U-0 | R-1                    | U-0 | R/W/HS-0            | R/S-0/0 | U-0 | R-0                   |

| TXWE <sup>(2)</sup>                                          | _   | TXBE <sup>(1, 3)</sup> | —   | RXRE <sup>(2)</sup> | CLRBF   | _   | RXBF <sup>(1,3)</sup> |

| bit 7                                                        |     |                        |     |                     |         |     | bit 0                 |

|                                                              |     |                        |     |                     |         |     |                       |

| Legend:              |                      |                                                       |  |

|----------------------|----------------------|-------------------------------------------------------|--|

| R = Readable bit     | W = Writable bit     | U = Unimplemented bit, read as '0'                    |  |

| u = Bit is unchanged | x = Bit is unknown   | -n/n = Value at POR and BOR/Value at all other Resets |  |

| '1' = Bit is set     | '0' = Bit is cleared | HS = Hardware set HC = Hardware clear                 |  |

| bit 7 |          | <b>TXWE:</b> Transmit Write Error Status bit <sup>(2)</sup><br>1 = A new byte of data was written to I2CTXB when it was full (Must be cleared by software)<br>0 = No transmit write error                                                                        |  |

|-------|----------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|

| bit 6 |          | Unimplemented: Read as '0'                                                                                                                                                                                                                                       |  |

| bit 5 |          | <ul> <li>TXBE: Transmit Buffer Empty Status bit</li> <li>1 = I2CTXB is empty (Cleared by writing the I2CTXB register)</li> <li>0 = I2CTXB is full</li> </ul>                                                                                                     |  |

| bit 4 |          | Unimplemented: Read as '0'                                                                                                                                                                                                                                       |  |

| bit 3 |          | <b>RXRE:</b> Receive Read Error Status bit<br>1 = A byte of data was read from I2CxRXB when it was empty. (Must be cleared by software)<br>0 = No receive overflow                                                                                               |  |

| bit 2 |          | <b>CLRBF:</b> Clear Buffer bit<br>Setting this bit clears/empties the receive and transmit buffers, causing reset of RXBF and TXBE.<br>Setting this bit clears the RXIF and TXIF interrupt flags.<br>This bit is set-only special function, and always reads '0' |  |

| bit 1 |          | Unimplemented: Read as '0'                                                                                                                                                                                                                                       |  |

| bit 0 |          | <b>RXBF:</b> Receive Buffer Full Status bit<br>1 = I2CRXB has received new data (Cleared by reading the I2CRXB register)<br>0 = I2CRXB is empty                                                                                                                  |  |

| Note  | 1:<br>2: | The bits are held in Reset when I2CEN = 0.<br>Will cause NACK to be sent for slave address and master/slave data read bytes.                                                                                                                                     |  |

**3:** Used as triggers for DMA operation.

## PIC18(L)F26/27/45/46/47/55/56/57K42

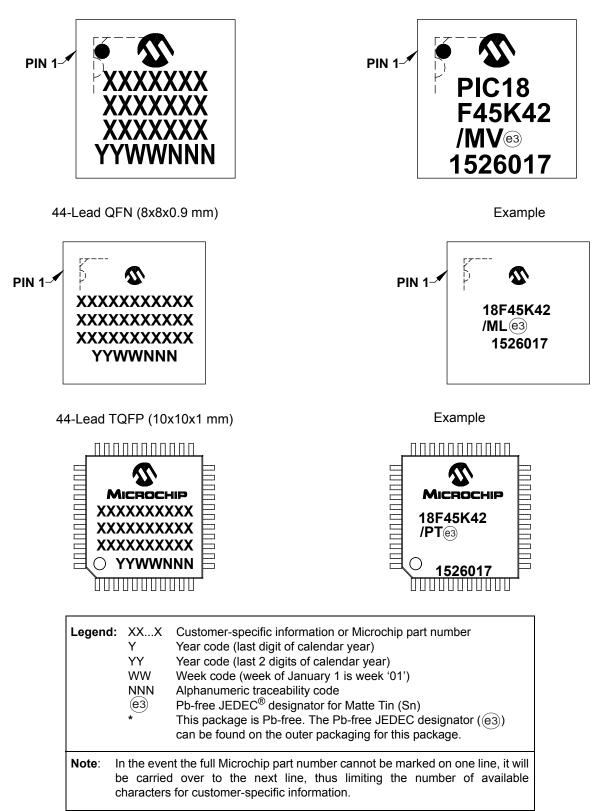

Example

## Package Marking Information (Continued)

40-Lead UQFN (5x5x0.5 mm)

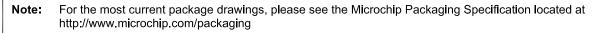

## 28-Lead Plastic Quad Flat, No Lead Package (ML) - 6x6 mm Body [QFN] With 0.55 mm Terminal Length

Microchip Technology Drawing C04-105C Sheet 1 of 2