Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

E·XFI

| Details                    |                                                                              |

|----------------------------|------------------------------------------------------------------------------|

| Product Status             | Active                                                                       |

| Core Processor             | PIC                                                                          |

| Core Size                  | 8-Bit                                                                        |

| Speed                      | 64MHz                                                                        |

| Connectivity               | I <sup>2</sup> C, LINbus, SPI, UART/USART                                    |

| Peripherals                | Brown-out Detect/Reset, DMA, HLVD, POR, PWM, WDT                             |

| Number of I/O              | 25                                                                           |

| Program Memory Size        | 128KB (64K x 16)                                                             |

| Program Memory Type        | FLASH                                                                        |

| EEPROM Size                | 1K x 8                                                                       |

| RAM Size                   | 8K x 8                                                                       |

| Voltage - Supply (Vcc/Vdd) | 1.8V ~ 3.6V                                                                  |

| Data Converters            | A/D 24x12b; D/A 1x5b                                                         |

| Oscillator Type            | Internal                                                                     |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                            |

| Mounting Type              | Surface Mount                                                                |

| Package / Case             | 28-SOIC (0.295", 7.50mm Width)                                               |

| Supplier Device Package    | 28-SOIC                                                                      |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/pic18lf27k42t-i-so |

|                            |                                                                              |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

### 4.0 MEMORY ORGANIZATION

There are three types of memory in PIC18 microcontroller devices:

- Program Flash Memory

- Data RAM

- Data EEPROM

As Harvard architecture devices, the data and program memories use separate buses; this allows for concurrent access of the two memory spaces. The data EEPROM, for practical purposes, can be regarded as a peripheral device, since it is addressed and accessed through a set of control registers.

Additional detailed information on the operation of the Program Flash Memory and Data EEPROM Memory is provided in Section 13.0 "Nonvolatile Memory (NVM) Control".

### 4.1 Program Flash Memory Organization

PIC18 microcontrollers implement a 21-bit program counter, which is capable of addressing a 2 Mbyte program memory space. Accessing any unimplemented memory will return all '0's (a NOP instruction).

These devices contain the following:

- PIC18(L)F45/55K42: 32 Kbytes of Flash memory, up to 16,384 single-word instructions

- PIC18(L)F26/46/56K42: 64 Kbytes of Flash memory, up to 32,768 single-word instructions

- PIC18(L)F27/47/57K42: 128 Kbytes of Flash memory, up to 65,536 single-word instructions

The Reset vector for the device is at address 00000h. PIC18(L)F26/27/45/46/47/55/56/57K42 devices feature a vectored interrupt controller with a dedicated interrupt vector table in the program memory, see Section 9.0 "Interrupt Controller".

**Note:** For memory information on this family of devices, see Table 4-1 and Table 4-3.

### 4.2 Memory Access Partition (MAP)

Program Flash memory is partitioned into:

- Application Block

- Boot Block, and

- Storage Area Flash (SAF) Block

#### 4.2.1 APPLICATION BLOCK

Application block is where the user's program resides by default. Default settings of the configuration bits (BBEN = 1 and  $\overline{SAFEN} = 1$ ) assign all memory in the program Flash memory area to the application block. The WRTAPP configuration bit is used to protect the application block.

#### 4.2.2 BOOT BLOCK

Boot block is an area in program memory that is ideal for storing bootloader code. Code placed in this area can be executed by the CPU. The boot block can be write-protected, independent of the main application block. The Boot Block is enabled by the BBEN bit and size is based on the value of the BBSIZE bits of Configuration word (Register 5-7), see Table 5-1 for boot block sizes. The WRTB Configuration bit is used to write-protect the Boot Block.

#### 4.2.3 STORAGE AREA FLASH

Storage Area Flash (SAF) is the area in program memory that can be used as data storage. SAF is enabled by the SAFEN bit of the Configuration word in Register 5-7. If enabled, the code placed in this area cannot be executed by the CPU. The SAF block is placed at the end of memory and spans 128 Words. The WRTSAF Configuration bit is used to write-protect the Storage Area Flash.

**Note:** If write-protected locations are written to, memory is not changed and the WRERR bit defined in Register 13-1 is set.

| U-1              | U-1         | R/W-1            | U-1 | R/W-1            | U-1              | R/W-1          | R/W-1    |  |

|------------------|-------------|------------------|-----|------------------|------------------|----------------|----------|--|

| _                | _           | FCMEN            | —   | CSWEN            | _                | PR1WAY         | CLKOUTEN |  |

| bit 7 bit 0      |             |                  |     |                  |                  |                |          |  |

|                  |             |                  |     |                  |                  |                |          |  |

| Legend:          |             |                  |     |                  |                  |                |          |  |

| R = Readable b   | bit         | W = Writable     | bit | U = Unimple      | mented bit, read | d as '1'       |          |  |

| -n = Value for b | lank device | '1' = Bit is set |     | '0' = Bit is cle | eared            | x = Bit is unk | nown     |  |

|                  |             |                  |     |                  |                  |                |          |  |

# REGISTER 5-2: CONFIGURATION WORD 1H (30 0001h)

| bit 7-6 | Unimplemented: Read as '1'                                                                                                                                                                                                                                                                      |

|---------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| bit 5   | FCMEN: Fail-Safe Clock Monitor Enable bit<br>1 = FSCM timer is enabled<br>0 = FSCM timer is disabled                                                                                                                                                                                            |

| bit 4   | Unimplemented: Read as '1'                                                                                                                                                                                                                                                                      |

| bit 3   | CSWEN: Clock Switch Enable bit<br>1 = Writing to NOSC and NDIV is allowed<br>0 = The NOSC and NDIV bits cannot be changed by user software                                                                                                                                                      |

| bit 2   | Unimplemented: Read as '1'                                                                                                                                                                                                                                                                      |

| bit 1   | <ul> <li>PR1WAY: PRLOCKED One-Way Set Enable bit</li> <li>1 = PRLOCKED bit can be cleared and set only once; Priority registers remain locked after one clear/set cycle</li> <li>0 = PRLOCKED bit can be set and cleared multiple times (subject to the unlock sequence)</li> </ul>             |

| bit 0   | CLKOUTEN: Clock Out Enable bit         If FEXTOSC<2:0> = EC (high, mid or low) or Not Enabled:         1 = CLKOUT function is disabled; I/O or oscillator function on OSC2         0 = CLKOUT function is enabled; Fosc/4 clock appears at OSC2         Otherwise:         This bit is ignored. |

# 7.2 Clock Source Types

Clock sources can be classified as external or internal.

External clock sources rely on external circuitry for the clock source to function. Examples are: oscillator modules (ECH, ECM, ECL mode), quartz crystal resonators or ceramic resonators (LP, XT and HS modes).

Internal clock sources are contained within the oscillator module. The internal oscillator block has two internal oscillators that are used to generate internal system clock sources. The High-Frequency Internal Oscillator (HFINTOSC) can produce 1, 2, 4, 8, 12, 16, 32, 48 and 64 MHz clock. The frequency can be controlled through the OSCFRQ register (Register 7-5). The Low-Frequency Internal Oscillator (LFINTOSC) generates a fixed 31 kHz frequency.

A 4x PLL is provided that can be used with an external clock. When used with the HFINTOSC the 4x PLL has input frequency limitations.See **Section 7.2.1.4 "4x PLL"** for more details.

The system clock can be selected between external or internal clock sources via the NOSC bits in the OSCCON1 register. See **Section 7.3 "Clock Switching"** for additional information. The system clock can be made available on the OSC2/CLKOUT pin for any of the modes that do not use the OSC2 pin. The clock out functionality is governed by the CLKOUTEN bit in the CONFIG1H register (Register 5-2). If enabled, the clock out signal is always at a frequency of Fosc/4.

#### 7.2.1 EXTERNAL CLOCK SOURCES

An external clock source can be used as the device system clock by performing one of the following actions:

- Program the RSTOSC<2:0> and FEXTOSC<2:0> bits in the Configuration Words to select an external clock source that will be used as the default system clock upon a device Reset.

- Write the NOSC<2:0> and NDIV<3:0> bits in the OSCCON1 register to switch the system clock source.

See **Section 7.3 "Clock Switching"** for more information.

#### 7.2.1.1 EC Mode

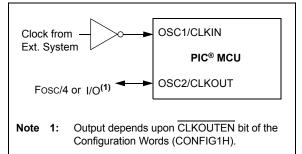

The External Clock (EC) mode allows an externally generated logic level signal to be the system clock source. When operating in this mode, an external clock source is connected to the OSC1 input. OSC2/ CLKOUT is available for general purpose I/O or CLKOUT. Figure 7-2 shows the pin connections for EC mode. EC mode has three power modes to select from through Configuration Words:

- ECH High power

- ECM Medium power

- ECL Low power

Refer to Table 44-9 for External Clock/Oscillator Timing Requirements. The Oscillator Start-up Timer (OST) is disabled when EC mode is selected. Therefore, there is no delay in operation after a Power-on Reset (POR) or wake-up from Sleep. Because the PIC<sup>®</sup> MCU design is fully static, stopping the external clock input will have the effect of halting the device while leaving all data intact. Upon restarting the external clock, the device will resume operation as if no time had elapsed.

#### FIGURE 7-2: EXTERNAL CLOCK (EC) MODE OPERATION

#### 7.2.1.2 LP, XT, HS Modes

The LP, XT and HS modes support the use of quartz crystal resonators or ceramic resonators connected to OSC1 and OSC2 (Figure 7-3). The three modes select a low, medium or high gain setting of the internal inverter-amplifier to support various resonator types and speed.

**LP** Oscillator mode selects the lowest gain setting of the internal inverter-amplifier. LP mode current consumption is the least of the three modes. This mode is designed to drive only 32.768 kHz tuning-fork type crystals (watch crystals).

**XT** Oscillator mode selects the intermediate gain setting of the internal inverter-amplifier. XT mode current consumption is the medium of the three modes. This mode is best suited to drive resonators with a medium drive level specification (above 100 kHz - 8 MHz).

**HS** Oscillator mode selects the highest gain setting of the internal inverter-amplifier. HS mode current consumption is the highest of the three modes. This mode is best suited for resonators that require a high drive setting (above 8 MHz).

Figure 7-3 and Figure 7-4 show typical circuits for quartz crystal and ceramic resonators, respectively.

| Name     | Bit 7     | Bit 6     | Bit 5    | Bit 4    | Bit 3      | Bit 2       | Bit 1      | Bit 0      | Register<br>on Page |

|----------|-----------|-----------|----------|----------|------------|-------------|------------|------------|---------------------|

| INTCON0  | GIE/GIEH  | GIEL      | IPEN     | -        | -          | INT2EDG     | INT1EDG    | INT0EDG    | 135                 |

| INTCON1  | STAT      | <1:0>     | -        | -        | -          | -           | -          | —          | 136                 |

| PIE0     | IOCIE     | CRCIE     | SCANIE   | NVMIE    | CSWIE      | OSFIE       | HLVDIE     | SWIE       | 147                 |

| PIE1     | SMT1PWAIE | SMT1PRAIE | SMT1IE   | C1IE     | ADTIE      | ADIE        | ZCDIE      | INTOIE     | 148                 |

| PIE2     | I2C1RXIE  | SPI1IE    | SPI1TXIE | SPI1RXIE | DMA1AIE    | DMA10RIE    | DMA1DCNTIE | DMA1SCNTIE | 149                 |

| PIE3     | TMR0IE    | U1IE      | U1EIE    | U1TXIE   | U1RXIE     | I2C1EIE     | I2C1IE     | I2C1TXIE   | 150                 |

| PIE4     | CLC1IE    | CWG1IE    | NCO1IE   | -        | CCP1IE     | TMR2IE      | TMR1GIE    | TMR1IE     | 151                 |

| PIE5     | I2C2TXIE  | I2C2RXIE  | DMA2AIE  | DMA2ORIE | DMA2DCNTIE | DMA2SCNTIE  | C2IE       | INT1IE     | 152                 |

| PIE6     | TMR3GIE   | TMR3IE    | U2IE     | U2EIE    | U2TXIE     | U2RXIE      | I2C2EIE    | I2C2IE     | 153                 |

| PIE7     | -         | -         | INT2IE   | CLC2IE   | CWG2IE     | _           | CCP2IE     | TMR4IE     | 154                 |

| PIE8     | TMR5GIE   | TMR5IE    | -        | -        | _          | _           | _          | —          | 155                 |

| PIE9     | -         | -         | -        | -        | CLC3IE     | CWG3IE      | CCP3IE     | TMR6IE     | 155                 |

| PIE10    | -         | -         | -        | -        | -          | -           | CLC4IE     | CCP4IE     | 156                 |

| PIR0     | IOCIF     | CRCIF     | SCANIF   | NVMIF    | CSWIF      | OSFIF       | HLVDIF     | SWIF       | 137                 |

| PIR1     | SMT1PWAIF | SMT1PRAIF | SMT1IF   | C1IF     | ADTIF      | ADIF        | ZCDIF      | INT0IF     | 138                 |

| PIR2     | I2C1RXIF  | SPI1IF    | SPI1TXIF | SPI1RXIF | DMA1AIF    | DMA10RIF    | DMA1DCNTIF | DMA1SCNTIF | 139                 |

| PIR3     | TMR0IF    | U1IF      | U1EIF    | U1TXIF   | U1RXIF     | I2C1EIF     | I2C1IF     | I2C1TXIF   | 140                 |

| PIR4     | CLC1IF    | CWG1IF    | NCO1IF   | -        | CCP1IF     | TMR2IF      | TMR1GIF    | TMR1IF     | 141                 |

| PIR5     | I2C2TXF   | I2C2RXF   | DMA2AIF  | DMA2ORIF | DMA2DCNTIF | DMA2SCNTIF  | C2IF       | INT1IF     | 142                 |

| PIR6     | TMR3GIF   | TMR3IF    | U2IF     | U2EIF    | U2TXIF     | U2RXIF      | I2C2EIF    | I2C2IF     | 143                 |

| PIR7     | —         | -         | INT2IF   | CLC2IF   | CWG2IF     | —           | CCP2IF     | TMR4IF     | 144                 |

| PIR8     | TMR5GIF   | TMR5IF    | _        | —        | -          | -           | -          | -          | 145                 |

| PIR9     | -         | -         | -        | -        | CLC3IF     | CWG3IF      | CCP3IF     | TMR6IF     | 145                 |

| PIR10    | -         | -         | -        | -        | -          | -           | CLC4IF     | CCP4IF     | 146                 |

| IPR0     | IOCIP     | CRCIP     | SCANIP   | NVMIP    | CSWIP      | OSFIP       | HLVDIP     | SWIP       | 157                 |

| IPR1     | SMT1PWAIP | SMT1PRAIP | SMT1IP   | C1IP     | ADTIP      | ADIP        | ZCDIP      | INT0IP     | 158                 |

| IPR2     | I2C1RIP   | SPI1IP    | SPI1TIP  | SPI1RIP  | DMA1AIP    | DMA10RIP    | DMA1DCNTIP | DMA1SCNTIP | 159                 |

| IPR3     | TMR0IP    | U1IP      | U1EIP    | U1TXIP   | U1RXIP     | I2C1EIP     | I2C1IP     | I2C1TXIP   | 160                 |

| IPR4     | CLC1IP    | CWG1IP    | NCO1IP   | -        | CCP1IP     | TMR2IP      | TMR1GIP    | TMR1IP     | 161                 |

| IPR5     | I2C2TXP   | I2C2RXP   | DMA2AIP  | DMA2ORIP | DMA2DCNTIP | DMA2SCNTIP  | C2IP       | INT1IP     | 162                 |

| IPR6     | TMR3GIP   | TMR3IP    | U2IP     | U2EIP    | U2TXIP     | U2RXIP      | I2C2EIP    | I2C2IP     | 163                 |

| IPR7     | -         | -         | INT2IP   | CLC2IP   | CWG2IP     | -           | CCP2IP     | TMR4IP     | 164                 |

| IPR8     | TMR5GIP   | TMR5IP    | -        | -        | -          | -           | -          | -          | 164                 |

| IPR9     | -         | -         | -        | -        | CLC3IP     | CWG3IP      | CCP3IP     | TMR6IP     | 165                 |

| IPR10    | -         | -         | -        | -        | -          | -           | CLC4IP     | CCP4IP     | 165                 |

| IVTBASEU | _         | _         | -        |          | •          | BASE<20:16> | •          | I.         | 166                 |

| IVTBASEH |           |           |          | BAS      | E<15:8>    |             |            |            | 166                 |

| IVTBASEL |           |           |          | BAS      | SE<7:0>    |             |            |            | 166                 |

| IVTADU   |           |           |          |          |            | AD<20:16>   |            |            | 167                 |

| IVTADH   |           |           |          | AD       | <15:8>     |             |            |            | 167                 |

| IVTADL   |           |           |          | AD       | )<7:0>     |             |            |            | 167                 |

|          |           |           |          |          |            |             |            | IVTLOCKED  | 168                 |

| TABLE 9-3: | SUMMARY OF REGISTERS ASSOCIATED WITH INTERRUPTS |

|------------|-------------------------------------------------|

|------------|-------------------------------------------------|

Legend: — = unimplemented locations, read as '0'. Shaded bits are not used for interrupts.

#### 10.2.3.2 Peripheral Usage in Sleep

Some peripherals that can operate in Sleep mode will not operate properly with the Low-Power Sleep mode selected. The Low-Power Sleep mode is intended for use with these peripherals:

- Brown-out Reset (BOR)

- Windowed Watchdog Timer (WWDT)

- External interrupt pin/Interrupt-On-Change pins

- Peripherals that run off external secondary clock source

It is the responsibility of the end user to determine what is acceptable for their application when setting the VREGPM settings in order to ensure operation in Sleep.

| Note: | The PIC18F26/27/45/46/47/55/56/57K42     |

|-------|------------------------------------------|

|       | devices do not have a configurable Low-  |

|       | Power Sleep mode. PIC18F26/27/45/46/     |

|       | 47/55/56/57K42 devices are unregulated   |

|       | and are always in the lowest power state |

|       | when in Sleep, with no wake-up time      |

|       | penalty. These devices have a lower      |

|       | maximum VDD and I/O voltage than the     |

|       | PIC18(L)F26/27/45/46/47/55/56/57K42.     |

|       |                                          |

|       | See Section 44.0 "Electrical             |

|       | Specifications" for more information.    |

#### 10.2.4 IDLE MODE

When IDLEN is set (IDLEN = 1), the SLEEP instruction will put the device into Idle mode. In Idle mode, the CPU and memory operations are halted, but the peripheral clocks continue to run. This mode is similar to Doze mode, except that in IDLE both the CPU and PFM are shut off.

Note: If CLKOUTEN is enabled (CLKOUTEN = 0, Configuration Word 1H), the output will continue operating while in idle.

#### 10.2.4.1 Idle and Interrupts

IDLE mode ends when an interrupt occurs (even if GIE = 0), but IDLEN is not changed. The device can reenter IDLE by executing the SLEEP instruction.

If Recover-On-Interrupt is enabled (ROI = 1), the interrupt that brings the device out of idle also restores full-speed CPU execution when doze is also enabled.

#### 10.2.4.2 Idle and WWDT

When in idle, the WWDT Reset is blocked and will instead wake the device. The WWDT wake-up is not an interrupt, therefore ROI does not apply.

Note: The WDT can bring the device out of idle, in the same way it brings the device out of Sleep. The DOZEN bit is not affected.

### 10.3 Peripheral Operation in Power Saving Modes

All selected clock sources and the peripherals running off them are active in both IDLE and DOZE mode. Only in Sleep mode, both the Fosc and Fosc/4 clocks are unavailable. All the other clock sources are active, if enabled manually or through peripheral clock selection before the part enters Sleep.

### TABLE 17-2: PPS OUTPUT REGISTER DETAILS

| D DD0 (5.0)              |                       |     | Device Configuration |     |   |      |              |       |   |                      |   |   |   |   |   |

|--------------------------|-----------------------|-----|----------------------|-----|---|------|--------------|-------|---|----------------------|---|---|---|---|---|

| RxyPPS<5:0>              | Pin Rxy Output Source | PIC | 18(L)F26/27          | K42 |   | PIC1 | 8(L)F45/46/4 | 17K42 |   | PIC18(L)F55/56/57K42 |   |   |   |   |   |

| 0b01 0010 -<br>0b01 0001 | Reserved              |     |                      |     |   |      |              |       |   |                      |   |   |   |   |   |

| 0b01 0000                | PWM8                  | А   | —                    | С   | А | _    | _            | D     | _ | Α                    | — | — | D | — | — |

| 0b00 1111                | PWM7                  | А   | —                    | С   | А | _    | С            | _     | _ | _                    | — | С | — | — | F |

| 0b00 1110                | PWM6                  | А   | —                    | С   | А | —    | _            | D     | _ | А                    | — | — | D | — | — |

| 0b00 1101                | PWM5                  | А   | —                    | С   | А | _    | С            | _     | _ | Α                    | — | — | — | — | F |

| 0b00 1100                | CCP4                  | _   | В                    | С   | — | В    | _            | D     | _ | —                    | В | — | D | — | — |

| 0b00 1011                | CCP3                  | -   | В                    | С   | _ | В    | _            | D     | - |                      | В | — | D | — | — |

| 0b00 1010                | CCP2                  | _   | В                    | С   | — | В    | С            | _     | _ | _                    | — | С | — | — | F |

| 0b00 1001                | CCP1                  | _   | В                    | С   | — | В    | С            | _     | _ | _                    | — | С | — | — | F |

| 0b00 1000                | CWG1D                 | _   | В                    | С   | — | В    | _            | D     | _ | —                    | В | — | D | — | — |

| 0b00 0111                | CWG1C                 | _   | В                    | С   | — | В    | _            | D     | _ | —                    | В | — | D | — | — |

| 0b00 0110                | CWG1B                 | _   | В                    | С   | — | В    | _            | D     | _ | —                    | В | — | D | — | — |

| 0b00 0101                | CWG1A                 | _   | В                    | С   | — | В    | С            | _     | _ | _                    | В | С | — | — | — |

| 0b00 0100                | CLC4OUT               | _   | В                    | С   | — | В    | _            | D     | _ | —                    | В | — | D | — | — |

| 0b00 0011                | CLC3OUT               | _   | В                    | С   | — | В    | _            | D     | _ | —                    | В | — | D | — | — |

| 0b00 0010                | CLC2OUT               | А   | _                    | С   | А | _    | С            | _     |   | Α                    | — | — | — | — | F |

| 0600 0001                | CLC1OUT               | А   | _                    | С   | Α | _    | С            | _     | - | Α                    | — | — | — | — | F |

| 0000 0000                | LATxy                 | А   | В                    | С   | Α | В    | С            | D     | E | Α                    | В | С | D | E | F |

# **19.5** Register Definitions: Peripheral Module Disable

| REGISTER        | 19-1: PMD                          | 0: PMD CON                                               | ROL REGIS                       | STER 0                                         |                  |                  |              |

|-----------------|------------------------------------|----------------------------------------------------------|---------------------------------|------------------------------------------------|------------------|------------------|--------------|

| R/W-0/0         | R/W-0/0                            | R/W-0/0                                                  | R/W-0/0                         | R/W-0/0                                        | R/W-0/0          | R/W-0/0          | R/W-0/0      |

| SYSCMD          | FVRMD                              | HLVDMD                                                   | CRCMD                           | SCANMD                                         | NVMMD            | CLKRMD           | IOCMD        |

| 7               |                                    |                                                          |                                 |                                                |                  |                  |              |

| Legend:         |                                    |                                                          |                                 |                                                |                  |                  |              |

| R = Readabl     | e bit                              | W = Writable                                             | bit                             | U = Unimplem                                   | nented bit, read | d as '0'         |              |

| u = Bit is und  | hanged                             | x = Bit is unkr                                          | nown                            | -n/n = Value a                                 | t POR and BO     | R/Value at all o | ther Resets  |

| '1' = Bit is se | t                                  | '0' = Bit is clea                                        | ared                            | q = Value dep                                  | ends on condi    | tion             |              |

| bit 7           | See descripti<br>1 = System o      |                                                          | 9.4 "System (<br>isabled (Fosc) | k Network bit <sup>(1)</sup><br>Clock Disable" |                  |                  |              |

| bit 6           | FVRMD: Disa                        | able Fixed Volta<br>dule disabled                        |                                 | bit                                            |                  |                  |              |

| bit 5           | 1 = HLVD m                         | sable High/Low<br>odule disabled<br>odule enabled        | -Voltage Deteo                  | et bit                                         |                  |                  |              |

| bit 4           | 1 = CRC mo                         | able CRC Engined<br>Indule disabled<br>Indule enabled    | ne bit                          |                                                |                  |                  |              |

| bit 3           | 1 = NVM Me                         | isable NVM Me<br>emory Scan mo<br>emory Scan mo          | dule disabled                   | bit <sup>(2)</sup>                             |                  |                  |              |

| bit 2           | 1 = All Memo                       | M Module Disa<br>ory reading and<br>odule enabled        |                                 | bled; NVMCON                                   | registers canr   | not be written   |              |

| bit 1           | 1 = CLKR m                         | isable Clock Re<br>odule disabled<br>odule enabled       | ference bit                     |                                                |                  |                  |              |

| bit 0           | 1 = IOC mod                        | able Interrupt-or<br>dule(s) disabled<br>dule(s) enabled | n-Change bit, A                 | All Ports                                      |                  |                  |              |

|                 | learing the SYS<br>y Fosc/4 are no |                                                          | es the system                   | clock (Fosc) to                                | peripherals, h   | owever periphe   | rals clocked |

# REGISTER 19-1: PMD0: PMD CONTROL REGISTER 0

- 2: Subject to SCANE bit in CONFIG4H.

- **3:** When enabling NVM, a delay of up to 1 µs may be required before accessing data.

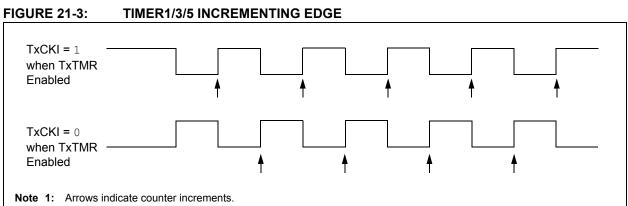

2: In Counter mode, a falling edge must be registered by the counter prior to the first incrementing rising edge of the clock.

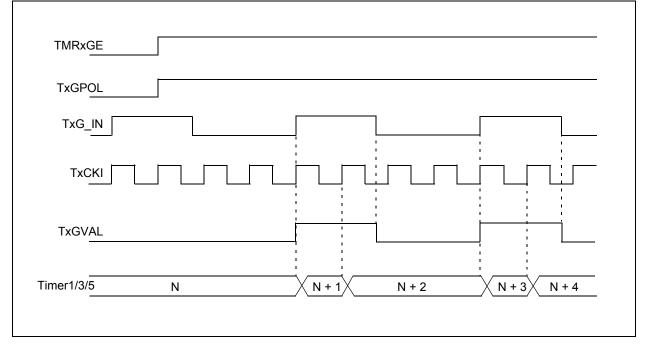

# FIGURE 21-4: TIMER1/3/5 GATE ENABLE MODE

# 22.5 Operation Examples

Unless otherwise specified, the following notes apply to the following timing diagrams:

- Both the prescaler and postscaler are set to 1:1 (both the CKPS and OUTPS bits in the T2CON register are cleared).

- The diagrams illustrate any clock except FOSC/4 and show clock-sync delays of at least two full cycles for both ON and T2TMR\_ers. When using FOSC/4, the clocksync delay is at least one instruction period for T2TMR\_ers; ON applies in the next instruction period.

- ON and T2TMR\_ers are somewhat generalized, and clock-sync delays may produce results that are slightly different than illustrated.

- The PWM Duty Cycle and PWM output are illustrated assuming that the timer is used for the PWM function of the CCP module as described in Section 23.0 "Capture/ Compare/PWM Module" and Section 24.0 "Pulse-Width Modulation (PWM)". The signals are not a part of the T2TMR module.

### 23.4.2 SETUP FOR PWM OPERATION

The following steps should be taken when configuring the CCP module for standard PWM operation:

- Use the desired output pin RxyPPS control to select CCPx as the source and disable the CCPx pin output driver by setting the associated TRIS bit.

- 2. Load the T2PR register with the PWM period value.

- Configure the CCP module for the PWM mode by loading the CCPxCON register with the appropriate values.

- 4. Load the CCPRxL register, and the CCPRxH register with the PWM duty cycle value and configure the FMT bit of the CCPxCON register to set the proper register alignment.

- 5. Configure and start Timer2:

- Clear the TMR2IF interrupt flag bit of the respective PIR register. See Note below.

- Select the timer clock source to be as Fosc/4 using the T2CLK register. This is required for correct operation of the PWM module.

- Configure the CKPS bits of the T2CON register with the Timer prescale value.

- Enable the Timer by setting the ON bit of the T2CON register.

- 6. Enable PWM output pin:

- Wait until the Timer overflows and the TMR2IF bit of the PIR4 register is set. See Note below.

- Enable the CCPx pin output driver by clearing the associated TRIS bit.

**Note:** In order to send a complete duty cycle and period on the first PWM output, the above steps must be included in the setup sequence. If it is not critical to start with a complete PWM signal on the first output, then step 6 may be ignored.

### 23.4.3 TIMER2 TIMER RESOURCE

The PWM standard mode makes use of the 8-bit Timer2 timer resources to specify the PWM period.

### 23.4.4 PWM PERIOD

The PWM period is specified by the T2PR register of Timer2. The PWM period can be calculated using the formula of Equation 23-1.

#### EQUATION 23-1: PWM PERIOD

$PWM Period = [(T2PR) + 1] \bullet 4 \bullet TOSC \bullet$ (TMR2 Prescale Value)

**Note 1:** Tosc = 1/Fosc

When T2TMR is equal to T2PR, the following three events occur on the next increment cycle:

- T2TMR is cleared

- The CCPx pin is set. (Exception: If the PWM duty cycle = 0%, the pin will not be set.)

- The PWM duty cycle is transferred from the CCPRxL/H register pair into a 10-bit buffer.

Note: The Timer postscaler (see Section 22.3 "External Reset Sources") is not used in the determination of the PWM frequency.

|                           |          |          |           | (         | - /       |           |

|---------------------------|----------|----------|-----------|-----------|-----------|-----------|

| PWM Frequency             | 1.22 kHz | 4.88 kHz | 19.53 kHz | 78.12 kHz | 156.3 kHz | 208.3 kHz |

| Timer Prescale            | 16       | 4        | 1         | 1         | 1         | 1         |

| T2PR Value                | 0xFF     | 0xFF     | 0xFF      | 0x3F      | 0x1F      | 0x17      |

| Maximum Resolution (bits) | 10       | 10       | 10        | 8         | 7         | 6.6       |

#### TABLE 23-2:EXAMPLE PWM FREQUENCIES AND RESOLUTIONS (Fosc = 20 MHz)

#### TABLE 23-3:EXAMPLE PWM FREQUENCIES AND RESOLUTIONS (Fosc = 8 MHz)

| PWM Frequency             | 1.22 kHz | 4.90 kHz | 19.61 kHz | 76.92 kHz | 153.85 kHz | 200.0 kHz |

|---------------------------|----------|----------|-----------|-----------|------------|-----------|

| Timer Prescale            | 16       | 4        | 1         | 1         | 1          | 1         |

| T2PR Value                | 0x65     | 0x65     | 0x65      | 0x19      | 0x0C       | 0x09      |

| Maximum Resolution (bits) | 8        | 8        | 8         | 6         | 5          | 5         |

### 23.4.7 OPERATION IN SLEEP MODE

In Sleep mode, the T2TMR register will not increment and the state of the module will not change. If the CCPx pin is driving a value, it will continue to drive that value. When the device wakes up, T2TMR will continue from its previous state.

#### 23.4.8 CHANGES IN SYSTEM CLOCK FREQUENCY

The PWM frequency is derived from the system clock frequency. Any changes in the system clock frequency will result in changes to the PWM frequency. See Section 7.0 "Oscillator Module (with Fail-Safe Clock Monitor)" for additional details.

#### 23.4.9 EFFECTS OF RESET

Any Reset will force all ports to Input mode and the CCP registers to their Reset states.

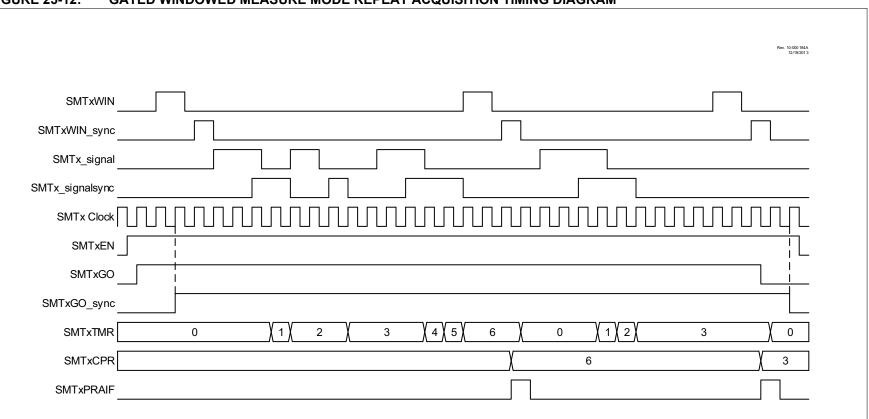

#### 25.6.5 WINDOWED MEASURE MODE

This mode measures the window duration of the SMTWINx input of the SMT. It begins incrementing the timer on a rising edge of the SMTWINx input and updates the SMT1CPR register with the value of the timer and resets the timer on a second rising edge. See Figure 25-10 and Figure 25-11.

#### FIGURE 25-12: GATED WINDOWED MEASURE MODE REPEAT ACQUISITION TIMING DIAGRAM

PIC18(L)F26/27/45/46/47/55/56/57K42

# 31.5 LIN Modes (UART1 only)

LIN is a protocol used primarily in automotive applications. The LIN network consists of two kinds of software processes: a Master process and a Slave process. Each network has only one Master process and one or more Slave processes.

From a physical layer point of view, the UART on one processor may be driven by both a Master and a Slave process, as long as only one Master process exists on the network.

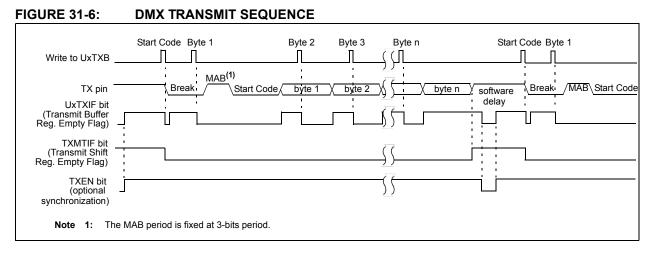

A LIN transaction consists of a Master process followed by a Slave process. The Slave process may involve more than one Slave where one is transmitting and the other(s) are receiving. The transaction begins by the following Master process transmission sequence:

- 1. Break

- 2. Delimiter bit

- 3. Sync Field

- 4. PID byte

The PID determines which Slave processes are expected to respond to the Master. When the PID byte is complete, the TX output remains in the Idle state. One or more of the Slave processes may respond to the Master process. If no one responds within the interbyte period, the Master is free to start another transmission. The inter-byte period is timed by software using a means other than the UART.

The Slave process follows the Master process. When the Slave software recognizes the PID then that Slave process responds by either transmitting the required response or by receiving the transmitted data. Only Slave processes send data. Therefore, Slave processes receiving data are receiving that of another Slave process.

When a Slave sends data, the Slave UART automatically calculates the checksum for the transmitted bytes as they are sent and appends the inverted checksum byte to the slave response.

When a Slave receives data, the checksum is accumulated on each byte as it is received using the same algorithm as the sending process. The last byte, which is the inverted checksum value calculated by the sending process, is added to the locally calculated checksum by the UART. The check passes when the result is all '1's, otherwise the check fails and the CERIF bit is set.

Two methods for computing the checksum are available: legacy and enhanced. The legacy checksum includes only the data bytes. The enhanced checksum includes the PID and the data. The C0EN control bit in the UxCON2 register determines the checksum method. Setting C0EN to '1' selects the enhanced method. Software must select the appropriate method before the Start bit of the checksum byte is received.

#### 31.5.1 LIN MASTER/SLAVE MODE

The LIN Master mode includes capabilities to generate Slave processes. The Master process stops at the PID transmission. Any data that is transmitted in Master/ Slave mode is done as a Slave process. LIN Master/ Slave mode is configured by the following settings:

- MODE<3:0> = 1100

- **TXEN =** 1

- RXEN = 1

- UxBRGH:L = Value to achieve desired baud rate

- TXPOL = 0 (for high Idle state)

- STP = desired Stop bits selection

- C0EN = desired checksum mode

- RxyPPS = TX pin selection code

- TX pin TRIS control = 0

- ON = 1

Note: The TXEN bit must be set before the Master process is received and remain set while in LIN mode whether or not the slave process is a transmitter.

#### 36.1.5 INTERRUPTS

The ADC module allows for the ability to generate an interrupt upon completion of an Analog-to-Digital conversion. The ADC Interrupt Flag is the ADIF bit in the PIRx register. The ADC Interrupt Enable is the ADIE bit in the PIEx register. The ADIF bit must be cleared in software.

- **Note 1:** The ADIF bit is set at the completion of every conversion, regardless of whether or not the ADC interrupt is enabled.

- **2:** The ADC operates during Sleep only when the FRC oscillator is selected.

This interrupt can be generated while the device is operating or while in Sleep. If the device is in Sleep, the interrupt will wake up the device. Upon waking from Sleep, the next instruction following the SLEEP instruction is always executed. If the user is attempting to wake up from Sleep and resume in-line code execution, the ADIE bit of the PIEx register and the GIE bits of the INTCON0 register must both be set. If all these bits are set, the execution will switch to the Interrupt Service Routine.

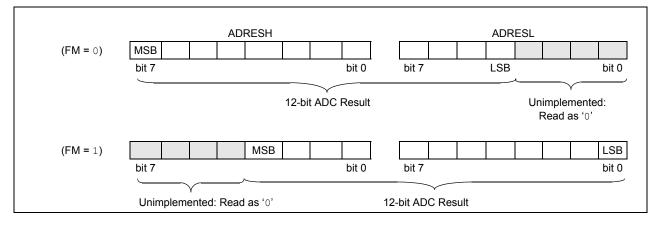

#### 36.1.6 RESULT FORMATTING

The 12-bit ADC conversion result can be supplied in two formats, left justified or right justified. The FM bits of the ADCON0 register controls the output format.

Figure 36-3 shows the two output formats.

Writes to the ADRES register pair are always right justified regardless of the selected format mode. Therefore, data read after writing to ADRES when ADFRM0 = 0 will be shifted left four places.

| RRNCF                                                                                          | Rotate Ri                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | ght f (No Ca                                   | ırry)       |  |  |  |

|------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------|-------------|--|--|--|

| Syntax:                                                                                        | RRNCF f                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | {,d {,a}}                                      |             |  |  |  |

| Operands:                                                                                      | $\begin{array}{l} 0 \leq f \leq 255 \\ d  \in  [0,1] \\ a  \in  [0,1] \end{array}$                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |                                                |             |  |  |  |

| Operation:                                                                                     | $(f \le n >) \rightarrow de$<br>$(f \le 0 >) \rightarrow de$                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |                                                |             |  |  |  |

| Status Affected:                                                                               | N, Z                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |                                                |             |  |  |  |

| Encoding:                                                                                      | 0100                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | 00da ff                                        | ff ffff     |  |  |  |

| Description:                                                                                   | 0100 00da ffff fff<br>The contents of register 'f' are rotated<br>one bit to the right. If 'd' is '0', the result<br>is placed in W. If 'd' is '1', the result is<br>placed back in register 'f' (default).<br>If 'a' is '0', the Access Bank will be<br>selected (default), overriding the BSR<br>value. If 'a' is '1', then the bank will be<br>selected as per the BSR value.<br>If 'a' is '0' and the extended instruction<br>set is enabled, this instruction operates<br>in Indexed Literal Offset Addressing<br>mode whenever f ≤ 95 (5Fh). See Sec-<br>tion 41.2.3 "Byte-Oriented and Bit-<br>Oriented Instructions in Indexed Lit-<br>eral Offset Mode" for details. |                                                |             |  |  |  |

| Words:                                                                                         | 1                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |                                                |             |  |  |  |

| Cycles:                                                                                        | 1                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |                                                |             |  |  |  |

| Q Cycle Activity:                                                                              |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |                                                |             |  |  |  |

| Q1                                                                                             | Q2                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | Q3                                             | Q4          |  |  |  |

| Decode                                                                                         | Read<br>register 'f'                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | Process<br>Data                                | Write to    |  |  |  |

| Evenue 1                                                                                       |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |                                                | destination |  |  |  |

| Example 1:                                                                                     |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | REG, 1, 0                                      | destination |  |  |  |

| Before Instruct<br>REG<br>After Instructio<br>REG                                              | tion<br>= 1101 (                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | REG, 1, 0                                      | destination |  |  |  |

| Before Instruct<br>REG<br>After Instructio<br>REG                                              | tion<br>= 1101 C<br>n<br>= 1110 1                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | REG, 1, 0<br>0111<br>1011                      | destination |  |  |  |

| Before Instruct<br>REG<br>After Instructio<br>REG<br><u>Example 2</u> :                        | tion<br>= 1101 C<br>n<br>= 1110 1<br>RRNCF F                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | REG, 1, 0<br>0111<br>1011                      | destination |  |  |  |

| Before Instruct<br>REG<br>After Instructio<br>REG                                              | tion<br>= 1101 C<br>n<br>= 1110 1<br>RRNCF F                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | REG, 1, 0<br>0111<br>1011                      | destination |  |  |  |

| Before Instruct<br>REG<br>After Instructio<br>REG<br><u>Example 2</u> :<br>Before Instruct     | tion<br>= 1101 C<br>n<br>= 1110 1<br>RRNCF 1<br>tion<br>= ?<br>= 1101 C                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | REG, 1, 0<br>0111<br>1011<br>REG, 0, 0         | destination |  |  |  |

| Before Instruct<br>REG<br>After Instructio<br>REG<br>Example 2:<br>Before Instruct<br>W<br>REG | tion<br>= 1101 C<br>n<br>= 1110 1<br>RRNCF 1<br>tion<br>= ?<br>= 1101 C                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | REG, 1, 0<br>0111<br>1011<br>REG, 0, 0<br>0111 | destination |  |  |  |

|       | _              |                                                                                                                                                         |                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |      |                       |  |  |  |  |

|-------|----------------|---------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------|-----------------------|--|--|--|--|

| SET   | F              | Set f                                                                                                                                                   |                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |      |                       |  |  |  |  |

| Synta | ax:            | SETF f{,                                                                                                                                                | SETF f {,a}                                                                                                                                                                                                                                                                                                                                                                                                                                                            |      |                       |  |  |  |  |

| Opera | ands:          | $\begin{array}{l} 0 \leq f \leq 255 \\ a \in [0,1] \end{array}$                                                                                         |                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |      |                       |  |  |  |  |

| Opera | ation:         | $FFh\tof$                                                                                                                                               |                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |      |                       |  |  |  |  |

| Statu | s Affected:    | None                                                                                                                                                    |                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |      |                       |  |  |  |  |

| Enco  | ding:          | 0110                                                                                                                                                    | 100a                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | ffff | ffff                  |  |  |  |  |

| Desc  | ription:       | are set to F<br>If 'a' is '0',<br>If 'a' is '1',<br>GPR bank.<br>If 'a' is '0' a<br>set is enab<br>in Indexed<br>mode when<br>tion 41.2.3<br>Oriented I | The contents of the specified register<br>are set to FFh.<br>If 'a' is '0', the Access Bank is selected.<br>If 'a' is '1', the BSR is used to select the<br>GPR bank.<br>If 'a' is '0' and the extended instruction<br>set is enabled, this instruction operates<br>in Indexed Literal Offset Addressing<br>mode whenever $f \le 95$ (5Fh). See Sec-<br>tion 41.2.3 "Byte-Oriented and Bit-<br>Oriented Instructions in Indexed Lit-<br>eral Offset Mode" for details. |      |                       |  |  |  |  |

| Word  | s:             | 1                                                                                                                                                       |                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |      |                       |  |  |  |  |

| Cycle | es:            | 1                                                                                                                                                       | 1                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |      |                       |  |  |  |  |

| QC    | ycle Activity: |                                                                                                                                                         |                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |      |                       |  |  |  |  |

| -     | Q1             | Q2                                                                                                                                                      | Q2 Q3 Q4                                                                                                                                                                                                                                                                                                                                                                                                                                                               |      |                       |  |  |  |  |

|       | Decode         | Read<br>register 'f'                                                                                                                                    | Proce<br>Dat                                                                                                                                                                                                                                                                                                                                                                                                                                                           |      | Write<br>register 'f' |  |  |  |  |

| Example:           | SETF |     | REG, | 1 |

|--------------------|------|-----|------|---|

| Before Instruction |      |     |      |   |

| REG                | =    | 5Ah |      |   |

| After Instruction  |      |     |      |   |

| REG                | =    | FFh |      |   |

| Address          | Name                  | Bit 7         | Bit 6                     | Bit 5   | Bit 4       | Bit 3          | Bit 2   | Bit 1   | Bit 0   | Registe<br>on pag |

|------------------|-----------------------|---------------|---------------------------|---------|-------------|----------------|---------|---------|---------|-------------------|

| 3A5Bh            | RB2I2C                | _             | SLEW                      | PU      |             | _              |         | TH      |         | 263               |

| 3A5Ah            | RB1I2C                | —             | SLEW                      | PU      |             | — — ТН         |         |         | TH      | 263               |

| 3A59h            | —                     |               | Reserved, maintain as '0' |         |             |                |         |         |         |                   |

| 3A58h            | —                     |               |                           |         | Reserved, m | aintain as '0' |         |         |         |                   |

| 3A57h            | IOCBF                 | IOCBF7        | IOCBF6                    | IOCBF5  | IOCBF4      | IOCBF3         | IOCBF2  | IOCBF1  | IOCBF0  | 287               |

| 3A56h            | IOCBN                 | IOCBN7        | IOCBN6                    | IOCBN5  | IOCBN4      | IOCBN3         | IOCBN2  | IOCBN1  | IOCBN0  | 287               |

| 3A55h            | IOCBP                 | IOCBP7        | IOCBP6                    | IOCBP5  | IOCBP4      | IOCBP3         | IOCBP2  | IOCBP1  | IOCBP0  | 287               |

| 3A54h            | INLVLB                | INLVLB7       | INLVLB6                   | INLVLB5 | INLVLB4     | INLVLB3        | INLVLB2 | INLVLB1 | INLVLB0 | 270               |

| 3A53h            | SLRCONB               | SLRB7         | SLRB6                     | SLRB5   | SLRB4       | SLRB3          | SLRB2   | SLRB1   | SLRB0   | 269               |

| 3A52h            | ODCONB                | ODCB7         | ODCB6                     | ODCB5   | ODCB4       | ODCB3          | ODCB2   | ODCB1   | ODCB0   | 268               |

| 3A51h            | WPUB                  | WPUB7         | WPUB6                     | WPUB5   | WPUB4       | WPUB3          | WPUB2   | WPUB1   | WPUB0   | 267               |

| 3A50h            | ANSELB                | ANSELB7       | ANSELB6                   | ANSELB5 | ANSELB4     | ANSELB3        | ANSELB2 | ANSELB1 | ANSELB0 | 266               |

| 3A4Fh -<br>3A4Ah | —                     |               |                           |         | Unimple     | emented        |         |         |         |                   |

| 3A49h            | —                     |               |                           |         | Reserved, m | aintain as '0' |         |         |         |                   |

| 3A48h            | —                     |               |                           |         | Reserved, m | aintain as '0' |         |         |         |                   |

| 3A47h            | IOCAF                 | IOCAF7        | IOCAF6                    | IOCAF5  | IOCAF4      | IOCAF3         | IOCAF2  | IOCAF1  | IOCAF0  | 287               |

| 3A46h            | IOCAN                 | IOCAN7        | IOCAN6                    | IOCAN5  | IOCAN4      | IOCAN3         | IOCAN2  | IOCAN1  | IOCAN0  | 287               |

| 3A45h            | IOCAP                 | IOCAP7        | IOCAP6                    | IOCAP5  | IOCAP4      | IOCAP3         | IOCAP2  | IOCAP1  | IOCAP0  | 287               |

| 3A44h            | INLVLA                | INLVLA7       | INLVLA6                   | INLVLA5 | INLVLA4     | INLVLA3        | INLVLA2 | INLVLA1 | INLVLA0 | 270               |

| 3A43h            | SLRCONA               | SLRA7         | SLRA6                     | SLRA5   | SLRA4       | SLRA3          | SLRA2   | SLRA1   | SLRA0   | 269               |

| 3A42h            | ODCONA                | ODCA7         | ODCA6                     | ODCA5   | ODCA4       | ODCA3          | ODCA2   | ODCA1   | ODCA0   | 268               |

| 3A41h            | WPUA                  | WPUA7         | WPUA6                     | WPUA5   | WPUA4       | WPUA3          | WPUA2   | WPUA1   | WPUA0   | 267               |

| 3A40h            | ANSELA                | ANSELA7       | ANSELA6                   | ANSELA5 | ANSELA4     | ANSELA3        | ANSELA2 | ANSELA1 | ANSELA0 | 266               |

| 3A3Fh -<br>3A30h | —                     | Unimplemented |                           |         |             |                |         |         |         |                   |

| 3A2Fh            | RF7PPS <sup>(3)</sup> | —             | —                         | —       | RF7PPS4     | RF7PPS3        | RF7PPS2 | RF7PPS1 | RF7PPS0 | 280               |

| 3A2Eh            | RF6PPS <sup>(3)</sup> | —             | —                         | —       | RF6PPS4     | RF6PPS3        | RF6PPS2 | RF6PPS1 | RF6PPS0 | 280               |

| 3A2Dh            | RF5PPS <sup>(3)</sup> | —             | —                         | —       | RF5PPS4     | RF5PPS3        | RF5PPS2 | RF5PPS1 | RF5PPS0 | 280               |

| 3A2Ch            | RF4PPS <sup>(3)</sup> | _             | —                         | —       | RF4PPS4     | RF4PPS3        | RF4PPS2 | RF4PPS1 | RF4PPS0 | 280               |

| 3A2Bh            | RF3PPS <sup>(3)</sup> | _             | —                         | —       | RF3PPS4     | RF3PPS3        | RF3PPS2 | RF3PPS1 | RF3PPS0 | 280               |

| 3A2Ah            | RF2PPS <sup>(3)</sup> | _             | —                         | —       | RF2PPS4     | RF2PPS3        | RF2PPS2 | RF2PPS1 | RF2PPS0 | 280               |

| 3A29h            | RF1PPS <sup>(3)</sup> | _             | —                         | —       | RF1PPS4     | RF1PPS3        | RF1PPS2 | RF1PPS1 | RF1PPS0 | 280               |

| 3A28h            | RF0PPS <sup>(3)</sup> | _             | —                         | —       | RF0PPS4     | RF0PPS3        | RF0PPS2 | RF0PPS1 | RF0PPS0 | 280               |

| 3A27h-<br>3A23h  | _                     |               |                           |         | Unimple     | emented        |         |         |         |                   |

| 3A22h            | RE2PPS <sup>(2)</sup> | —             | —                         | —       | RE2PPS4     | RE2PPS3        | RE2PPS2 | RE2PPS1 | RE2PPS0 | 280               |

| 3A21h            | RE1PPS <sup>(2)</sup> | —             | _                         | _       | RE1PPS4     | RE1PPS3        | RE1PPS2 | RE1PPS1 | RE1PPS0 | 280               |

| 3A20h            | RE0PPS <sup>(2)</sup> |               |                           | —       | RE0PPS4     | RE0PPS3        | RE0PPS2 | RE0PPS1 | RE0PPS0 | 280               |

| 3A1Fh            | RD7PPS <sup>(2)</sup> |               | _                         | _       | RD7PPS4     | RD7PPS3        | RD7PPS2 | RD7PPS1 | RD7PPS0 | 280               |

| 3A1Eh            | RD6PPS <sup>(2)</sup> |               | _                         | _       | RD6PPS4     | RD6PPS3        | RD6PPS2 | RD6PPS1 | RD6PPS0 | 280               |

| 3A1Dh            | RD5PPS <sup>(2)</sup> |               |                           | _       | RD5PPS4     | RD5PPS3        | RD5PPS2 | RD5PPS1 | RD5PPS0 | 280               |

| 3A1Ch            | RD4PPS <sup>(2)</sup> |               | _                         | _       | RD4PPS4     | RD4PPS3        | RD4PPS2 | RD4PPS1 | RD4PPS0 | 280               |

| 3A1Bh            | RD3PPS <sup>(2)</sup> |               | —                         | _       | RD3PPS4     | RD3PPS3        | RD3PPS2 | RD3PPS1 | RD3PPS0 | 280               |

| 3A1Ah            | RD2PPS <sup>(2)</sup> |               | —                         | _       | RD2PPS4     | RD2PPS3        | RD2PPS2 | RD2PPS1 | RD2PPS0 | 280               |

| 3A19h            | RD1PPS <sup>(2)</sup> | _             | _                         | _       | RD1PPS4     | RD1PPS3        | RD1PPS2 | RD1PPS1 | RD1PPS0 | 280               |

| 3A18h            | RD0PPS <sup>(2)</sup> | _             | _                         | _       | RD0PPS4     | RD0PPS3        | RD0PPS2 | RD0PPS1 | RD0PPS0 | 280               |

| 3A17h            | RC7PPS                | _             | _                         | _       | RC7PPS4     | RC7PPS3        | RC7PPS2 | RC7PPS1 | RC7PPS0 | 280               |

#### **TABLE 42-1**: REGISTER FILE SUMMARY FOR PIC18(L)F26/27/45/46/47/55/56/57K42 DEVICES

Legend: x = unknown, u = unchanged, — = unimplemented, q = value depends on condition

Note 1: Unimplemented in LF devices.

Unimplemented in PIC18(L)F26/27K42. 2:

Unimplemented on PIC18(L)F26/27/45/46/47K42 devices. 3:

4: Unimplemented in PIC18(L)F45/55K42.

# TABLE 44-15: ANALOG-TO-DIGITAL CONVERTER (ADC) ACCURACY SPECIFICATIONS<sup>(1,2)</sup>: