Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

#### Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

E·XFI

| Details                    |                                                                             |

|----------------------------|-----------------------------------------------------------------------------|

| Product Status             | Active                                                                      |

| Core Processor             | PIC                                                                         |

| Core Size                  | 8-Bit                                                                       |

| Speed                      | 64MHz                                                                       |

| Connectivity               | I <sup>2</sup> C, LINbus, SPI, UART/USART                                   |

| Peripherals                | Brown-out Detect/Reset, DMA, HLVD, POR, PWM, WDT                            |

| Number of I/O              | 36                                                                          |

| Program Memory Size        | 32KB (16K x 16)                                                             |

| Program Memory Type        | FLASH                                                                       |

| EEPROM Size                | 256 x 8                                                                     |

| RAM Size                   | 2K x 8                                                                      |

| Voltage - Supply (Vcc/Vdd) | 1.8V ~ 3.6V                                                                 |

| Data Converters            | A/D 35x12b; D/A 1x5b                                                        |

| Oscillator Type            | Internal                                                                    |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                           |

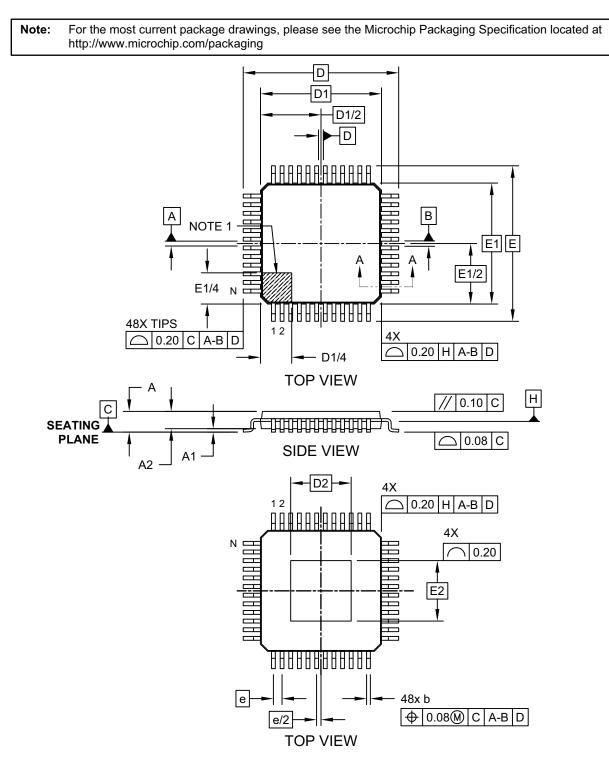

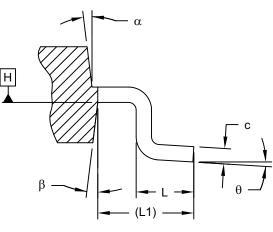

| Mounting Type              | Surface Mount                                                               |

| Package / Case             | 44-VQFN Exposed Pad                                                         |

| Supplier Device Package    | 44-QFN (8x8)                                                                |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/pic18lf45k42-i-ml |

|                            |                                                                             |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

## TO OUR VALUED CUSTOMERS

It is our intention to provide our valued customers with the best documentation possible to ensure successful use of your Microchip products. To this end, we will continue to improve our publications to better suit your needs. Our publications will be refined and enhanced as new volumes and updates are introduced.

If you have any questions or comments regarding this publication, please contact the Marketing Communications Department via E-mail at docerrors@microchip.com. We welcome your feedback.

#### Most Current Data Sheet

To obtain the most up-to-date version of this data sheet, please register at our Worldwide Website at:

#### http://www.microchip.com

You can determine the version of a data sheet by examining its literature number found on the bottom outside corner of any page. The last character of the literature number is the version number, (e.g., DS3000000A is version A of document DS30000000).

#### Errata

An errata sheet, describing minor operational differences from the data sheet and recommended workarounds, may exist for current devices. As device/documentation issues become known to us, we will publish an errata sheet. The errata will specify the revision of silicon and revision of document to which it applies.

To determine if an errata sheet exists for a particular device, please check with one of the following:

- Microchip's Worldwide Website; http://www.microchip.com

- Your local Microchip sales office (see last page)

When contacting a sales office, please specify which device, revision of silicon and data sheet (include literature number) you are using.

#### **Customer Notification System**

Register on our website at www.microchip.com to receive the most current information on all of our products.

## PIC18(L)F26/27/45/46/47/55/56/57K42

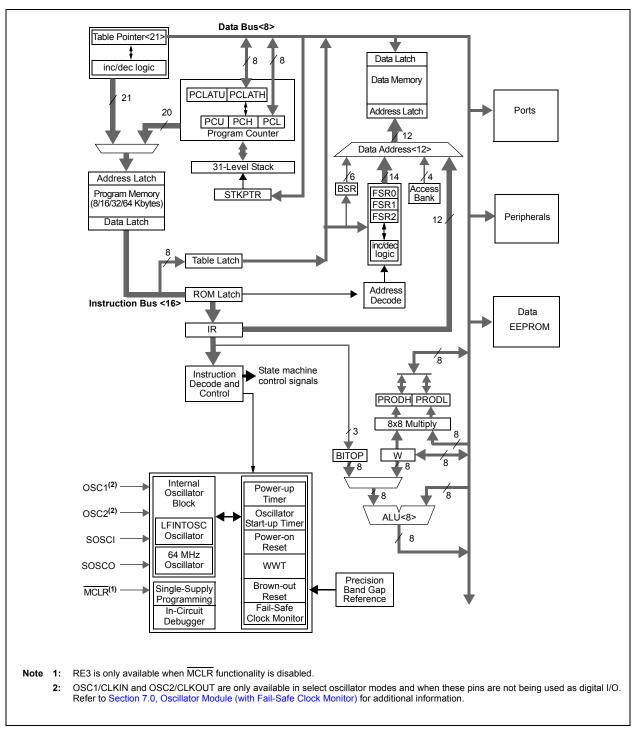

#### FIGURE 3-1: PIC18(L)F26/27/45/46/47/55/56/57K42 FAMILY BLOCK DIAGRAM

## 8.1 Clock Source

The input to the reference clock output can be selected using the CLKRCLK register.

#### 8.1.1 CLOCK SYNCHRONIZATION

Once the reference clock enable (EN) is set, the module is ensured to be glitch-free at start-up.

When the reference clock output is disabled, the output signal will be disabled immediately.

Clock dividers and clock duty cycles can be changed while the module is enabled, but glitches may occur on the output. To avoid possible glitches, clock dividers and clock duty cycles should be changed only when the CLKREN is clear.

### 8.2 **Programmable Clock Divider**

The module takes the clock input and divides it based on the value of the DIV<2:0> bits of the CLKRCON register (Register 8-1).

The following configurations can be made based on the DIV<2:0> bits:

- · Base Fosc value

- · Fosc divided by 2

- Fosc divided by 4

- Fosc divided by 8

- Fosc divided by 16

- · Fosc divided by 32

- Fosc divided by 64

- Fosc divided by 128

The clock divider values can be changed while the module is enabled; however, in order to prevent glitches on the output, the DIV<2:0> bits should only be changed when the module is disabled (EN = 0).

## 8.3 Selectable Duty Cycle

The DC<1:0> bits of the CLKRCON register can be used to modify the duty cycle of the output clock. A duty cycle of 25%, 50%, or 75% can be selected for all clock rates, with the exception of the undivided base Fosc value.

The duty cycle can be changed while the module is enabled; however, in order to prevent glitches on the output, the DC<1:0> bits should only be changed when the module is disabled (EN = 0).

**Note:** The DC1 bit is reset to '1'. This makes the default duty cycle 50% and not 0%.

## 8.4 Operation in Sleep Mode

The reference clock output module clock is based on the system clock. When the device goes to Sleep, the module outputs will remain in their current state. This will have a direct effect on peripherals using the reference clock output as an input signal. No change should occur in the module from entering or exiting from Sleep.

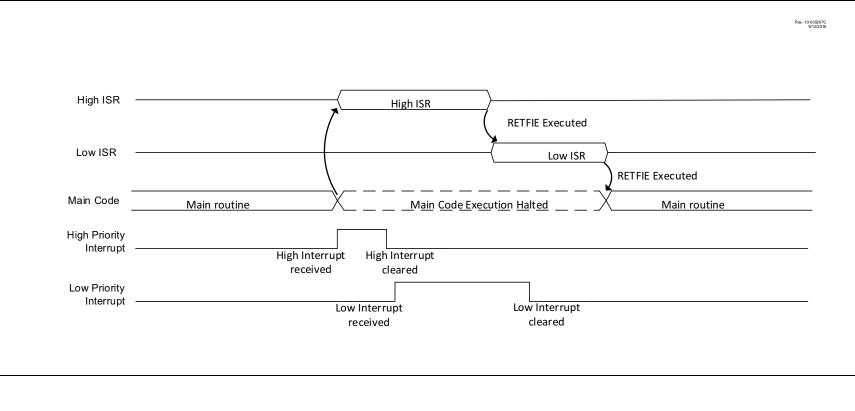

## 9.4.2 SERVING A HIGH PRIORITY INTERRUPT WHILE A LOW PRIORITY INTERRUPT PENDING

A high priority interrupt request will always take precedence over any interrupt of a lower priority. The high priority interrupt is acknowledged first, then the low-priority interrupt is acknowledged. Upon a return from the high priority ISR (by executing the RETFIE instruction), the low priority interrupt is serviced, see Figure 9-3.

If any other high priority interrupts are pending and enabled, then they are serviced before servicing the pending low priority interrupt. If no other high priority interrupt requests are active, the low priority interrupt is serviced.

## FIGURE 9-3: INTERRUPT EXECUTION: HIGH PRIORITY INTERRUPT WITH A LOW PRIORITY INTERRUPT PENDING

# PIC18(L)F26/27/45/46/47/55/56/57K42

| R-0/0                  | R-0/0                               | R-0/0                              | R-0/0                   | R/W/HS-0/0        | R/W/HS-0/0        | R/W/HS-0/0                                  | R/W/HS-0/0     |

|------------------------|-------------------------------------|------------------------------------|-------------------------|-------------------|-------------------|---------------------------------------------|----------------|

| I2C1RXIF <sup>(2</sup> | <sup>2)</sup> SPI1IF <sup>(3)</sup> | SPI1TXIF <sup>(4)</sup>            | SPI1RXIF <sup>(4)</sup> | DMA1AIF           | DMA10RIF          | DMA1DCNTIF                                  | DMA1SCNTIF     |

| bit 7                  |                                     |                                    |                         |                   |                   |                                             | bit (          |

|                        |                                     |                                    |                         |                   |                   |                                             |                |

| Legend:                |                                     |                                    |                         |                   |                   |                                             |                |

| R = Reada              |                                     | W = Writable                       |                         | •                 | ented bit, read   |                                             |                |

| u = Bit is u           | -                                   | x = Bit is unk                     |                         |                   |                   | Value at all othe                           | er Resets      |

| '1' = Bit is s         | set                                 | '0' = Bit is cle                   | ared                    | HS = Hardwar      | e set             |                                             |                |

| bit 7                  | I2C1RXIF:                           | <sup>2</sup> C1 Receive Ir         | nterrupt Flag b         | it(2)             |                   |                                             |                |

|                        |                                     | ot has occurred                    |                         |                   |                   |                                             |                |

|                        | 0 = Interrup                        | ot event has no                    | t occurred              |                   |                   |                                             |                |

| bit 6                  |                                     | 1 Interrupt Flag                   | -                       |                   |                   |                                             |                |

|                        |                                     | ot has occurred                    |                         |                   |                   |                                             |                |

|                        | -                                   | ot event has no                    |                         |                   |                   |                                             |                |

| bit 5                  |                                     | SPI1 Transmit I                    |                         | Dit               |                   |                                             |                |

|                        |                                     | ot has occurred<br>ot event has no |                         |                   |                   |                                             |                |

| bit 4                  | •                                   | SPI1 Receive I                     |                         |                   |                   |                                             |                |

| bit 4                  |                                     | ot has occurred                    | 1 0                     |                   |                   |                                             |                |

|                        |                                     | ot event has no                    |                         |                   |                   |                                             |                |

| bit 3                  | DMA1AIF: [                          | DMA1 Abort In                      | terrupt Flag bit        | t                 |                   |                                             |                |

|                        | 1 = Interrup                        | t has occurred                     | (must be clea           | red by software   | e)                |                                             |                |

|                        | 0 = Interrup                        | ot event has no                    | t occurred              |                   |                   |                                             |                |

| bit 2                  | DMA10RIF                            | : DMA1 Overru                      | in Interrupt Fla        | ag bit            |                   |                                             |                |

|                        | -                                   |                                    | -                       | red by software   | e)                |                                             |                |

|                        |                                     | ot event has no                    |                         |                   |                   |                                             |                |

| bit 1                  |                                     |                                    |                         | t Interrupt Flag  |                   |                                             |                |

|                        |                                     | ot has occurred<br>ot event has no |                         | red by software   | e)                |                                             |                |

| bit 0                  | •                                   | FIF: DMA1 Sou                      |                         | errunt Flag hit   |                   |                                             |                |

|                        |                                     |                                    |                         | red by software   | <del>.</del> )    |                                             |                |

|                        |                                     | ot event has no                    |                         |                   | -)                |                                             |                |

|                        |                                     | e global enable                    |                         |                   |                   | the state of its co<br>priate interrupt fla |                |

| 2:                     | -                                   | 2CxRXIF are r                      | ead-only bits.          | To clear the inte | errupt condition  | , the CLRBF bit i                           | n I2CxSTAT1    |

| 3:                     | SPIxIF is a rea                     | d-only bit. To c                   | lear the interru        | pt condition, al  | l bits in the SPI | kINTF register m                            | ust be cleared |

|                        |                                     |                                    |                         |                   |                   |                                             |                |

## REGISTER 9-5: PIR2: PERIPHERAL INTERRUPT REGISTER 2<sup>(1)</sup>

4: SPIxTXIF and SPIxRXIF are read-only bits and cannot be set/cleared by the software.

#### 15.9.4 TRANSFER FROM SFR TO GPR

The following visual reference describes the sequence of events when copying ADC results to a GPR location. The ADC Interrupt Flag can be chosen as the Source Hardware trigger, the Source address can be set to point to the ADC Result registers at 3EEF, the Destination address can be set to point to any GPR location of our choice (Example 0x100).

#### FIGURE 15-8: SFR SPACE TO GPR SPACE TRANSFER

| Instruction<br>Clock       |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |  |

|----------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|

| EN                         |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |  |

| SIRQEN                     |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |  |

| Source Hardware<br>Trigger |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |  |

| DGO                        |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |  |

| DMAxSPTR                   | Ox3EEF     Ox3EF0     S     Ox3EEF     Ox3EEF     Ox3EEF     S     S     S     S     S     S     S     S     S     S     S     S     S     S     S     S     S     S     S     S     S     S     S     S     S     S     S     S     S     S     S     S     S     S     S     S     S     S     S     S     S     S     S     S     S     S     S     S     S     S     S     S     S     S     S     S     S     S     S     S     S     S     S     S     S     S     S     S     S     S     S     S     S     S     S     S     S     S     S     S     S     S     S     S     S     S     S     S     S     S     S     S     S     S     S     S     S     S     S     S </th <th></th>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |  |

| DMAxDPTR                   | 0x100     0x101     ( 0x102     0x103     ( 0x103)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |  |

| DMAxSCNT                   |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |  |

| DMAxDCNT                   |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |  |

| DMA STATE                  | $ \left( \begin{array}{c} \text{IDLE} \end{array} \right) \left( SR^{(1)} \right) DW^{(2)} \left( SR^$ |  |

| DMAxSCNTIF                 |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |  |

| DMAxDCNTIF -               | <u>}</u>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |  |

|                            | DMAxSSA 0x3EEF DMAxDSA 0x100                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |  |

|                            | DMAxSSZ 0x2 DMAxDSZ 0xA                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |  |

|                            | SMODE 0x1 DMODE 0x1                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |  |

| Note 1:                    | SR - Source Read                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |  |

| 2:                         | DW - Destination Write                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |  |

|           |       |                  |              |       |           |         |        |       | 1 1                 |

|-----------|-------|------------------|--------------|-------|-----------|---------|--------|-------|---------------------|

| Name      | Bit 7 | Bit 6            | Bit 5        | Bit 4 | Bit 3     | Bit 2   | Bit 1  | Bit 0 | Register<br>on Page |

| DMAxCON0  | EN    | SIRQEN           | DGO          | —     | —         | AIRQEN  | _      | XIP   | 248                 |

| DMAxCON1  | DMOD  | E<1:0>           | DSTP         | SMR   | <1:0>     | SMOD    | E<1:0> | SSTP  | 249                 |

| DMAxBUF   | DBUF7 | DBUF6            | DBUF5        | DBUF4 | DBUF3     | DBUF2   | DBUF1  | DBUF0 | 250                 |

| DMAxSSAL  |       | SSA<7:0>         |              |       |           |         |        |       |                     |

| DMAxSSAH  |       |                  |              | SSA<  | :15:8>    |         |        |       | 250                 |

| DMAxSSAU  | —     | _                | — SSA<21:16> |       |           |         |        |       |                     |

| DMAxSPTRL |       |                  |              | SPTR  | <7:0>     |         |        |       | 251                 |

| DMAxSPTRH |       |                  |              | SPTR  | <15:8>    |         |        |       | 251                 |

| DMAxSPTRU | —     | _                |              |       | SPTR<     | :21:16> |        |       | 252                 |

| DMAxSSZL  |       | SSZ<7:0>         |              |       |           |         |        |       | 252                 |

| DMAxSSZH  | _     | —                |              | _     |           | SSZ<    | 11:8>  |       | 252                 |

| DMAxSCNTL |       |                  |              | SCNT  | <7:0>     |         |        |       | 253                 |

| DMAxSCNTH | _     | _                |              | _     |           | SCNT    | <11:8> |       | 253                 |

| DMAxDSAL  |       |                  |              | DSA   | <7:0>     |         |        |       | 253                 |

| DMAxDSAH  |       |                  |              | DSA<  | :15:8>    |         |        |       | 254                 |

| DMAxDPTRL |       |                  |              | DPTR  | <7:0>     |         |        |       | 254                 |

| DMAxDPTRH |       |                  |              | DPTR  | <15:8>    |         |        |       | 254                 |

| DMAxDSZL  |       |                  |              | DSZ   | <7:0>     |         |        |       | 255                 |

| DMAxDSZH  | —     | —                | _            | —     |           | DSZ<    | 11:8>  |       | 255                 |

| DMAxDCNTL |       | DCNT<7:0>        |              |       |           |         |        |       | 255                 |

| DMAxDCNTH | —     | — — — DCNT<11:8> |              |       |           |         |        | 256   |                     |

| DMAxSIRQ  | _     |                  |              |       |           |         |        |       | 256                 |

| DMAxAIRQ  |       |                  |              |       | AIRQ<6:0> |         |        |       | 256                 |

## TABLE 15-3: SUMMARY OF REGISTERS ASSOCIATED WITH DMA

Legend: — = unimplemented location, read as '0'. Shaded cells are not used by DMA.

## 21.7 Timer1/3/5 Interrupt

The Timer1/3/5 register pair (TMRxH:TMRxL) increments to FFFFh and rolls over to 0000h. When Timer1/3/5 rolls over, the Timer1/3/5 interrupt flag bit of the respective PIR register is set. To enable the interrupt-on-rollover, you must set these bits:

- ON bit of the TxCON register

- TMRxIE bits of the respective PIE register

- · GIE/GIEH bit of the INTCON0 register

The interrupt is cleared by clearing the TMRxIF bit in the Interrupt Service Routine.

For more information on selecting high or low priority status for the Timer1/3/5 Overflow Interrupt, see **Section 9.0 "Interrupt Controller**".

Note: The TMRxH:TMRxL register pair and the TMRxIF bit should be cleared before enabling interrupts.

## 21.8 Timer1/3/5 Operation During Sleep

Timer1/3/5 can only operate during Sleep when set up in Asynchronous Counter mode. In this mode, an external crystal or clock source can be used to increment the counter. To set up the timer to wake the device:

- ON bit of the TxCON register must be set

- TMRxIE bit of the respective PIE register must be set

- SYNC bit of the TxCON register must be set

- Configure the TMRxCLK register for using secondary oscillator as the clock source

- Enable the SOSCEN bit of the OSCEN register (Register 7-7)

The device will wake-up on an overflow and execute the next instruction. If the GIE/GIEH bit of the INTCON0 register is set, the device will call the Interrupt Service Routine.

The secondary oscillator will continue to operate in Sleep regardless of the SYNC bit setting.

### 21.9 CCP Capture/Compare Time Base

The CCP modules use the TMRxH:TMRxL register pair as the time base when operating in Capture or Compare mode.

In Capture mode, the value in the TMRxH:TMRxL register pair is copied into the CCPRxH:CCPRxL register pair on a configured event.

In Compare mode, an event is triggered when the value in the CCPRxH:CCPRxL register pair matches the value in the TMRxH:TMRxL register pair. This event can be a Special Event Trigger.

For more information, see Section 23.0 "Capture/ Compare/PWM Module".

## 21.10 CCP Special Event Trigger

When any of the CCP's are configured to trigger a special event, the trigger will clear the TMRxH:TMRxL register pair. This special event does not cause a Timer1/3/5 interrupt. The CCP module may still be configured to generate a CCP interrupt.

In this mode of operation, the CCPRxH:CCPRxL register pair becomes the period register for Timer1/3/ 5.

Timer1/3/5 should be synchronized and FOSC/4 should be selected as the clock source in order to utilize the Special Event Trigger. Asynchronous operation of Timer1/3/5 can cause a Special Event Trigger to be missed.

In the event that a write to TMRxH or TMRxL coincides with a Special Event Trigger from the CCP, the write will take precedence.

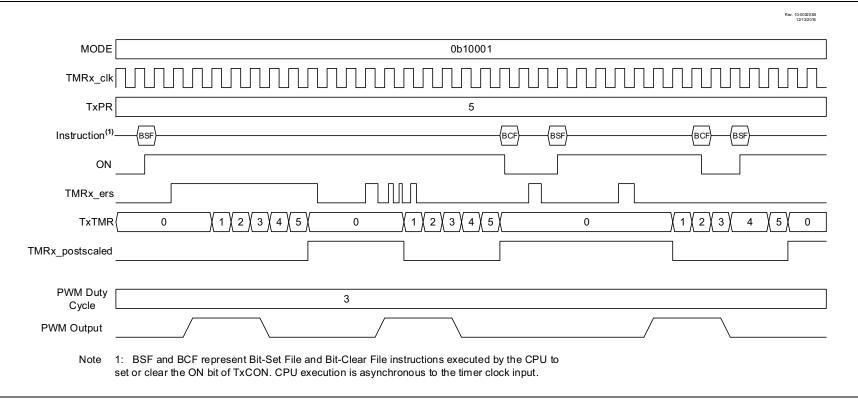

#### 22.5.9 EDGE-TRIGGERED MONOSTABLE MODES

The Edge-Triggered Monostable modes start the timer on an edge from the external Reset signal input, after the ON bit is set, and stop incrementing the timer when the timer matches the T2PR period value. The following edges will start the timer:

- Rising edge (MODE<4:0> = 10001)

- Falling edge (MODE<4:0> = 10010)

- Rising or Falling edge (MODE<4:0> = 10011)

When an Edge-Triggered Monostable mode is used in conjunction with the CCP PWM operation the PWM drive goes active with the external Reset signal edge that starts the timer, but will not go active when the timer matches the T2PR value. While the timer is incrementing, additional edges on the external Reset signal will not affect the CCP PWM.

#### FIGURE 22-12: RISING EDGE-TRIGGERED MONOSTABLE MODE TIMING DIAGRAM (MODE = 10001)

## 23.2 Capture Mode

Capture mode makes use of the 16-bit Timer1 resource. When an event occurs on the capture source, the 16-bit CCPRxH:CCPRxL register pair captures and stores the 16-bit value of the TMRxH:TMRxL register pair, respectively. An event is defined as one of the following and is configured by the MODE<3:0> bits of the CCPxCON register:

- · Every falling edge of CCPx input

- Every rising edge of CCPx input

- Every 4th rising edge of CCPx input

- · Every 16th rising edge of CCPx input

- Every edge of CCPx input (rising or falling)

When a capture is made, the Interrupt Request Flag bit CCPxIF of the respective PIR register is set. The interrupt flag must be cleared in software. If another capture occurs before the value in the CCPRxH:CCPRxL register pair is read, the old captured value is overwritten by the new captured value.

Note: If an event occurs during a 2-byte read, the high and low-byte data will be from different events. It is recommended while reading the CCPRxH:CCPRxL register pair to either disable the module or read the register pair twice for data integrity.

Figure 23-1 shows a simplified diagram of the capture operation.

### 23.2.1 CAPTURE SOURCES

In Capture mode, the CCPx pin should be configured as an input by setting the associated TRIS control bit.

| Note: | If the CCPx pin is configured as an output, |

|-------|---------------------------------------------|

|       | a write to the port can cause a capture     |

|       | condition.                                  |

The capture source is selected by configuring the CTS<2:0> bits of the CCPxCAP register. Refer to CCPxCAP register (Register 23-3) for a list of sources that can be selected.

#### 23.2.2 TIMER1 MODE RESOURCE

Timer1 must be running in Timer mode or Synchronized Counter mode for the CCP module to use the capture feature. In Asynchronous Counter mode, the capture operation may not work.

• See Section 21.0 "Timer1/3/5 Module with Gate Control" for more information on configuring Timer1.

Note: Clocking Timer1 from the system clock (Fosc) should not be used in Capture mode. In order for Capture mode to recognize the trigger event on the CCPx pin, Timer1 must be clocked from the instruction clock (Fosc/4) or from an external clock source.

### 26.3 Clock Source

The clock source is used to drive the dead-band timing circuits. The CWG module allows the following clock sources to be selected:

- Fosc (system clock)

- HFINTOSC

When the HFINTOSC is selected, the HFINTOSC will be kept running during Sleep. Therefore, CWG modes requiring dead band can operate in Sleep, provided that the CWG data input is also active during Sleep. The clock sources are selected using the CS bit of the CWGxCLKCON register (Register 26-3). The system clock Fosc, is disabled in Sleep and thus dead-band control cannot be used.

### 26.4 Selectable Input Sources

The CWG generates the output waveforms from the following input sources:

TABLE 26-1: SELECTABLE INPUT SOURCES

| Source<br>Peripheral | Signal Name                     | ISM<2:0> |

|----------------------|---------------------------------|----------|

| CWGxPPS              | Pin selected by<br>CWGxPPS      | 000      |

| CCP1                 | CCP1 Output                     | 001      |

| CCP2                 | CCP2 Output                     | 010      |

| PWM3                 | PWM3 Output                     | 011      |

| PWM4                 | PWM4 Output                     | 100      |

| CMP1                 | Comparator 1 Output             | 101      |

| CMP2                 | Comparator 2 Output             | 110      |

| DSM                  | Data signal modulator<br>output | 111      |

The input sources are selected using the IS<4:0> bits in the CWGxISM register (Register 26-4).

## 26.5 Output Control

#### 26.5.1 CWG OUTPUTS

Each CWG output can be routed to a Peripheral Pin Select (PPS) output via the RxyPPS register (see Section 17.0 "Peripheral Pin Select (PPS) Module").

#### 26.5.2 POLARITY CONTROL

The polarity of each CWG output can be selected independently. When the output polarity bit is set, the corresponding output is active-high. Clearing the output polarity bit configures the corresponding output as active-low. However, polarity does not affect the override levels. Output polarity is selected with the POLy bits of the CWGxCON1. Auto-shutdown and steering options are unaffected by polarity.

## 26.6 Dead-Band Control

The dead-band control provides non-overlapping PWM signals to prevent shoot-through current in PWM switches. Dead-band operation is employed for Half-Bridge and Full-Bridge modes. The CWG contains two 6-bit dead-band counters. One is used for the rising edge of the input source control in Half-Bridge mode or for reverse dead-band Full-Bridge mode. The other is used for the falling edge of the input source control in Half-Bridge mode or for forward dead band in Full-Bridge mode.

Dead band is timed by counting CWG clock periods from zero up to the value in the rising or falling deadband counter registers. See CWGxDBR and CWGxDBF registers, respectively.

## 26.6.1 DEAD-BAND FUNCTIONALITY IN HALF-BRIDGE MODE

In Half-Bridge mode, the dead-band counters dictate the delay between the falling edge of the normal output and the rising edge of the inverted output. This can be seen in Figure 26-2.

#### 26.6.2 DEAD-BAND FUNCTIONALITY IN FULL-BRIDGE MODE

In Full-Bridge mode, the dead-band counters are used when undergoing a direction change. The MODE<0> bit of the CWGxCON0 register can be set or cleared while the CWG is running, allowing for changes from Forward to Reverse mode. The CWGxA and CWGxC signals will change immediately upon the first rising input edge following a direction change, but the modulated signals (CWGxB or CWGxD, depending on the direction of the change) will experience a delay dictated by the dead-band counters.

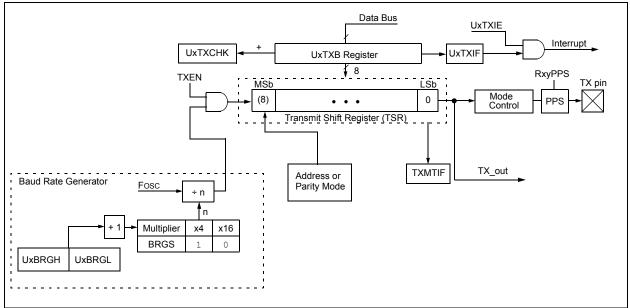

## 31.0 UNIVERSAL ASYNCHRONOUS RECEIVER TRANSMITTER (UART) WITH PROTOCOL SUPPORT

The Universal Asynchronous Receiver Transmitter (UART) module is a serial I/O communications peripheral. It contains all the clock generators, shift registers and data buffers necessary to perform an input or output serial data transfer, independent of device program execution. The UART, also known as a Serial Communications Interface (SCI), can be configured as a full-duplex asynchronous system or one of several automated protocols. Full-Duplex mode is useful for communications with peripheral systems, such as CRT terminals and personal computers.

Supported protocols include:

- LIN Master and Slave

- DMX mode

- · DALI control gear and control device

The UART module includes the following capabilities:

- · Full-duplex asynchronous transmit and receive

- · Two-character input buffer