Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

#### Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

E·XFI

| Details                    |                                                                              |

|----------------------------|------------------------------------------------------------------------------|

| Product Status             | Active                                                                       |

| Core Processor             | PIC                                                                          |

| Core Size                  | 8-Bit                                                                        |

| Speed                      | 64MHz                                                                        |

| Connectivity               | I <sup>2</sup> C, LINbus, SPI, UART/USART                                    |

| Peripherals                | Brown-out Detect/Reset, DMA, HLVD, POR, PWM, WDT                             |

| Number of I/O              | 36                                                                           |

| Program Memory Size        | 32KB (16K x 16)                                                              |

| Program Memory Type        | FLASH                                                                        |

| EEPROM Size                | 256 x 8                                                                      |

| RAM Size                   | 2K x 8                                                                       |

| Voltage - Supply (Vcc/Vdd) | 2.3V ~ 5.5V                                                                  |

| Data Converters            | A/D 35x12b; D/A 1x5b                                                         |

| Oscillator Type            | Internal                                                                     |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                            |

| Mounting Type              | Surface Mount                                                                |

| Package / Case             | 44-VQFN Exposed Pad                                                          |

| Supplier Device Package    | 44-QFN (8×8)                                                                 |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/pic18lf45k42t-i-ml |

|                            |                                                                              |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

| Device         | Data Sheet Index | Program Flash Memory (KB) | Data EEPROM (B) | Data SRAM (bytes) | I/O Pins | 12-bit ADC <sup>2</sup><br>(ch) | 5-bit DAC | Comparator | 8-bit/ (with HLT) /16-bit Timer | Window Watchdog Timer<br>(WWDT) | Signal Measurement Timer<br>(SMT) | CCP/10-bit PWM | CWG | NCO | CLC | Zero-Cross Detect | Direct Memory Access (DMA)<br>(ch) | Memory Access Partition | Vectored Interrupts | UART | l²C/SPI | Peripheral Pin Select | Peripheral Module Disable | Debug <sup>(1)</sup> |

|----------------|------------------|---------------------------|-----------------|-------------------|----------|---------------------------------|-----------|------------|---------------------------------|---------------------------------|-----------------------------------|----------------|-----|-----|-----|-------------------|------------------------------------|-------------------------|---------------------|------|---------|-----------------------|---------------------------|----------------------|

| PIC18(L)F24K42 | А                | 16                        | 256             | 1024              | 25       | 24                              | 1         | 2          | 3/4                             | Y                               | Y                                 | 4/4            | 3   | 1   | 4   | Y                 | 2                                  | Y                       | Y                   | 2    | 2/1     | Y                     | Υ                         | I                    |

| PIC18(L)F25K42 | А                | 32                        | 256             | 2048              | 25       | 24                              | 1         | 2          | 3/4                             | Y                               | Y                                 | 4/4            | 3   | 1   | 4   | Υ                 | 2                                  | Y                       | Y                   | 2    | 2/1     | Y                     | Υ                         | I                    |

| PIC18(L)F26K42 | В                | 64                        | 1024            | 4096              | 25       | 24                              | 1         | 2          | 3/4                             | Y                               | Y                                 | 4/4            | 3   | 1   | 4   | Υ                 | 2                                  | Y                       | Y                   | 2    | 2/1     | Y                     | Υ                         | I                    |

| PIC18(L)F27K42 | В                | 128                       | 1024            | 8192              | 25       | 24                              | 1         | 2          | 3/4                             | Y                               | Y                                 | 4/4            | 3   | 1   | 4   | Υ                 | 2                                  | Υ                       | Y                   | 2    | 2/1     | Υ                     | Υ                         | I                    |

| PIC18(L)F45K42 | В                | 32                        | 256             | 2048              | 36       | 35                              | 1         | 2          | 3/4                             | Y                               | Y                                 | 4/4            | 3   | 1   | 4   | Y                 | 2                                  | Υ                       | Y                   | 2    | 2/1     | Υ                     | Υ                         | I                    |

| PIC18(L)F46K42 | В                | 64                        | 1024            | 4096              | 36       | 35                              | 1         | 2          | 3/4                             | Y                               | Y                                 | 4/4            | 3   | 1   | 4   | Υ                 | 2                                  | Υ                       | Y                   | 2    | 2/1     | Υ                     | Υ                         | I                    |

| PIC18(L)F47K42 | В                | 128                       | 1024            | 8192              | 36       | 35                              | 1         | 2          | 3/4                             | Y                               | Y                                 | 4/4            | 3   | 1   | 4   | Y                 | 2                                  | Y                       | Y                   | 2    | 2/1     | Y                     | Υ                         | I                    |

| PIC18(L)F55K42 | В                | 32                        | 256             | 2048              | 44       | 43                              | 1         | 2          | 3/4                             | Y                               | Y                                 | 4/4            | 3   | 1   | 4   | Y                 | 2                                  | Y                       | Y                   | 2    | 2/1     | Y                     | Υ                         | I                    |

| PIC18(L)F56K42 | В                | 64                        | 1024            | 4096              | 44       | 43                              | 1         | 2          | 3/4                             | Y                               | Y                                 | 4/4            | 3   | 1   | 4   | Y                 | 2                                  | Y                       | Y                   | 2    | 2/1     | Y                     | Υ                         | I                    |

| PIC18(L)F57K42 | В                | 128                       | 1024            | 8192              | 44       | 43                              | 1         | 2          | 3/4                             | Y                               | Y                                 | 4/4            | 3   | 1   | 4   | Y                 | 2                                  | Y                       | Y                   | 2    | 2/1     | Y                     | Υ                         | I                    |

Note 1: I – Debugging integrated on chip.

# **Data Sheet Index:**

## Unshaded devices are not described in this document.

DS40001869 PIC18(L)F24/25K42 Data Sheet, 28-Pin **A**:

B:

DS40001919

PIC18(L)F26/27/45/46/47/55/56/57K42 Data Sheet, 28/40/44/48-Pin

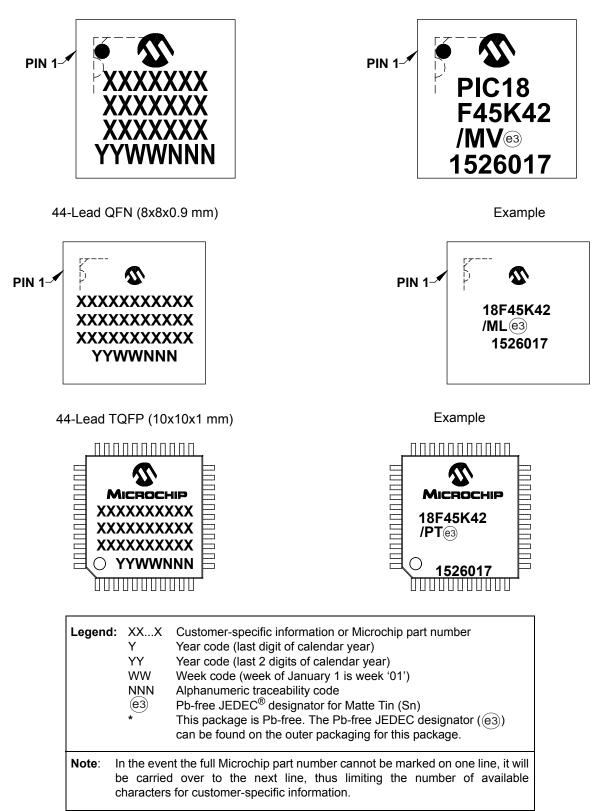

For other small form-factor package availability and marking information, visit **http://www.microchip.com/packaging** or contact your local sales office. Note:

# 7.4.4 RESET OR WAKE-UP FROM SLEEP

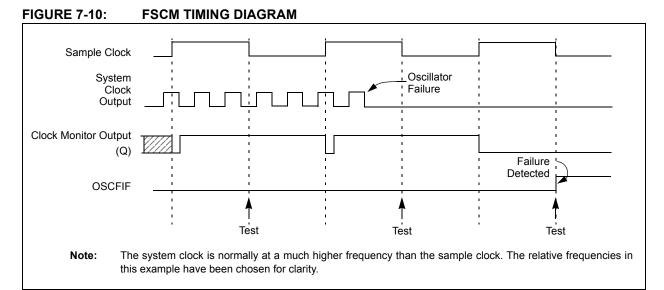

The FSCM is designed to detect an oscillator failure after the Oscillator Start-up Timer (OST) has expired. The OST is used after waking up from Sleep and after any type of Reset. The OST is not used with the EC Clock modes so that the FSCM will be active as soon as the Reset or wake-up has completed.

# TABLE 7-1: NOSC/COSC AND NDIV/CDIV BIT SETTINGS

| NOSC<2:0><br>COSC<2:0> | Clock Source                   | NDIV<<br>CDIV< |      | Clock Divider |

|------------------------|--------------------------------|----------------|------|---------------|

| 111                    | EXTOSC <sup>(1)</sup>          | 1111-          | 1010 | Reserved      |

| 110                    | HFINTOSC <sup>(2)</sup>        | 100            | 01   | 512           |

| 101                    | LFINTOSC                       | 100            | 00   | 256           |

| 100                    | SOSC                           | 011            | 11   | 128           |

| 011                    | Reserved                       | 011            | 10   | 64            |

| 010                    | EXTOSC + 4x PLL <sup>(3)</sup> | 010            | 01   | 32            |

| 001                    | Reserved                       | 010            | 00   | 16            |

| 000                    | Reserved                       | 001            | 11   | 8             |

|                        |                                | 001            | 10   | 4             |

|                        |                                | 000            | 01   | 2             |

0000

Note 1: EXTOSC configured by the FEXTOSC bits of Configuration Word 1 (Register 5-1).

- 2: HFINTOSC frequency is set with the FRQ bits of the OSCFRQ register (Register 7-5).

- **3:** EXTOSC must meet the PLL specifications (Table 44-11).

1

# 9.7.1 ABORTING INTERRUPTS

If the last instruction before the interrupt controller vectors to the ISR from main routine clears the GIE, PIE or PIR bit associated with the interrupt, the controller executes one force NOP cycle before it returns to the main routine.

Figure 9-10 illustrates the sequence of events when a peripheral interrupt is asserted and then cleared on the last executed instruction cycle.

If the GIE, PIE or PIR bit associated with the interrupt is cleared prior to vectoring to the ISR, then the controller continues executing the main routine.

# FIGURE 9-10: INTERRUPT TIMING DIAGRAM - ABORTING INTERRUPTS

|                         |      |                         |      |            |            | Rev. 10-002269D<br>7/6/2018 |

|-------------------------|------|-------------------------|------|------------|------------|-----------------------------|

|                         |      | 2                       | 3    | 4          | 5          |                             |

| Instruction<br>Clock    |      |                         |      |            |            |                             |

| Program<br>Counter      | X    | X+2                     | X+2  | X+4        | X+6        |                             |

| Instruction<br>Register |      | Inst @ X <sup>(1)</sup> | FNOP | Inst @ X+2 | Inst @ X+4 |                             |

| Interrupt               |      |                         |      |            |            |                             |

| Routine                 | MAII | N                       | FNOP | X MA       | N          | $\rangle$                   |

|                         |      |                         |      |            |            |                             |

Note 1: Inst @ X clears the interrupt flag, Example BCF INTCON0, GIE.

# 11.0 WINDOWED WATCHDOG TIMER (WWDT)

The Watchdog Timer (WDT) is a system timer that generates a Reset if the firmware does not issue a CLRWDT instruction within the time-out period. The Watchdog Timer is typically used to recover the system from unexpected events. The Windowed Watchdog Timer (WWDT) differs in that CLRWDT instructions are only accepted when they are performed within a specific window during the time-out period.

The WWDT has the following features:

- Selectable clock source

- Multiple operating modes

- WWDT is always On

- WWDT is off when in Sleep

- WWDT is controlled by software

- WWDT is always Off

- Configurable time-out period is from 1 ms to 256s (nominal)

- Configurable window size from 12.5% to 100% of the time-out period

- Multiple Reset conditions

The user needs to load the TBLPTR and TABLAT register with the address and data byte respectively before executing the write command. An unlock sequence needs to be followed for writing to the USER IDs/ DEVICE IDs/CONFIG words (Section 13.1.4, NVM Unlock Sequence). If WRTC = 0 or if TBLPTR points an invalid address location (see Table 13-1), WR bit is cleared without any effect and WRERR is set.

A single CONFIG word byte is written at once and the operation includes an implicit erase cycle for that byte (it is not necessary to set FREE). CPU execution is stalled and at the completion of the write cycle, the WR bit is cleared in hardware and the NVM Interrupt Flag bit (NVMIF) is set. The new CONFIG value takes effect when the CPU resumes operation.

| TABLE 13-3: | DIA, DCI, USER ID, DEV/REV ID AND CONFIGURATION WORD ACCESS |

|-------------|-------------------------------------------------------------|

|             | (REG<1:0> = x1)                                             |

| Address           | Function              | Read Access | Write Access |  |  |

|-------------------|-----------------------|-------------|--------------|--|--|

| 20 0000h-20 000Fh | User IDs              | Yes         | Yes          |  |  |

| 30 0000h-30 0009h | Configuration Words   | Yes         | Yes          |  |  |

| 3F 0000h-3F 003Fh | DIA                   | Yes         | No           |  |  |

| 3F FF00h-3F FF09h | DCI                   | Yes         | No           |  |  |

| 3F FFFCh-3F FFFFh | Revision ID/Device ID | Yes         | No           |  |  |

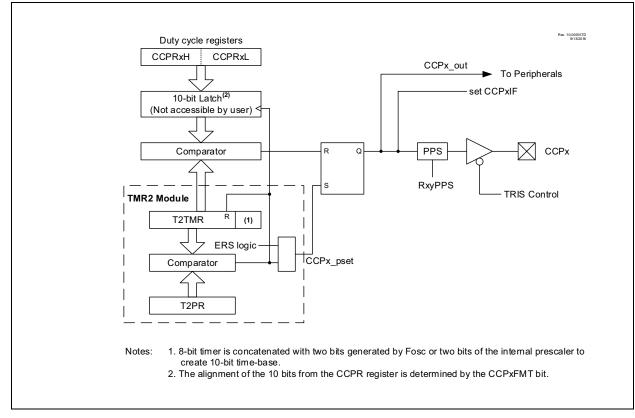

# 23.2 Capture Mode

Capture mode makes use of the 16-bit Timer1 resource. When an event occurs on the capture source, the 16-bit CCPRxH:CCPRxL register pair captures and stores the 16-bit value of the TMRxH:TMRxL register pair, respectively. An event is defined as one of the following and is configured by the MODE<3:0> bits of the CCPxCON register:

- · Every falling edge of CCPx input

- Every rising edge of CCPx input

- Every 4th rising edge of CCPx input

- · Every 16th rising edge of CCPx input

- Every edge of CCPx input (rising or falling)

When a capture is made, the Interrupt Request Flag bit CCPxIF of the respective PIR register is set. The interrupt flag must be cleared in software. If another capture occurs before the value in the CCPRxH:CCPRxL register pair is read, the old captured value is overwritten by the new captured value.

Note: If an event occurs during a 2-byte read, the high and low-byte data will be from different events. It is recommended while reading the CCPRxH:CCPRxL register pair to either disable the module or read the register pair twice for data integrity.

Figure 23-1 shows a simplified diagram of the capture operation.

# 23.2.1 CAPTURE SOURCES

In Capture mode, the CCPx pin should be configured as an input by setting the associated TRIS control bit.

| Note: | If the CCPx pin is configured as an output, |

|-------|---------------------------------------------|

|       | a write to the port can cause a capture     |

|       | condition.                                  |

The capture source is selected by configuring the CTS<2:0> bits of the CCPxCAP register. Refer to CCPxCAP register (Register 23-3) for a list of sources that can be selected.

# 23.2.2 TIMER1 MODE RESOURCE

Timer1 must be running in Timer mode or Synchronized Counter mode for the CCP module to use the capture feature. In Asynchronous Counter mode, the capture operation may not work.

• See Section 21.0 "Timer1/3/5 Module with Gate Control" for more information on configuring Timer1.

Note: Clocking Timer1 from the system clock (Fosc) should not be used in Capture mode. In order for Capture mode to recognize the trigger event on the CCPx pin, Timer1 must be clocked from the instruction clock (Fosc/4) or from an external clock source.

# 25.6.9 COUNTER MODE

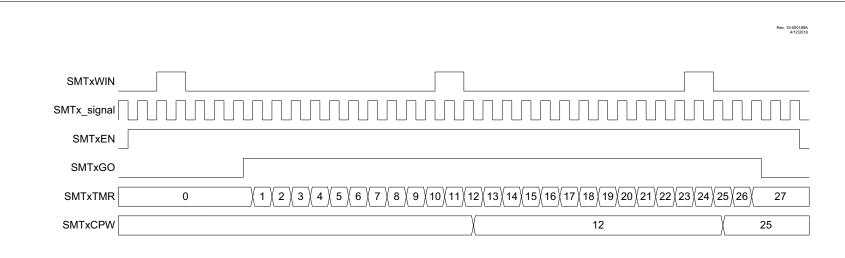

This mode increments the timer on each pulse of the SMT1\_signal input. This mode is asynchronous to the SMT clock and uses the SMT1\_signal as a time source. The SMT1CPW register will be updated with the current SMT1TMR value on the rising edge of the SMT1WIN input. See Figure 25-18.

# FIGURE 25-18: COUNTER MODE TIMING DIAGRAM

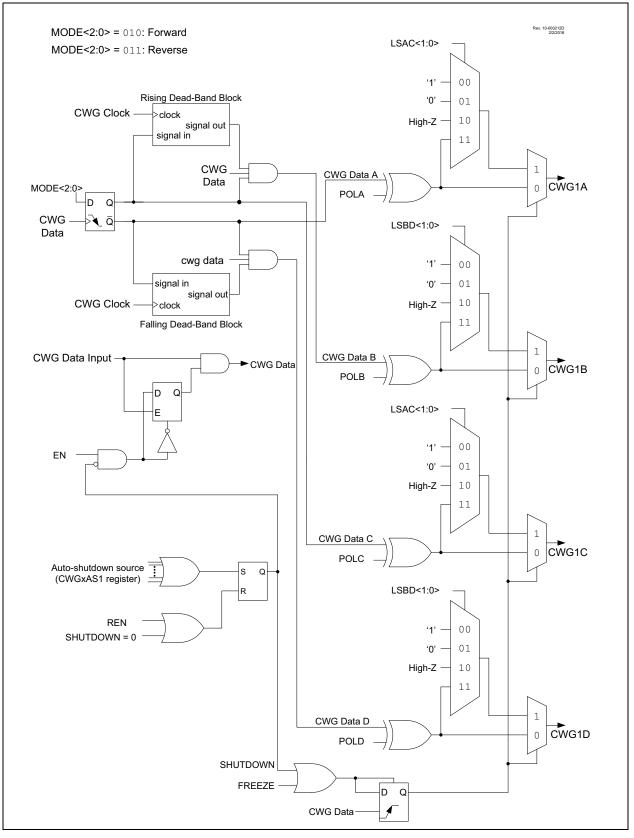

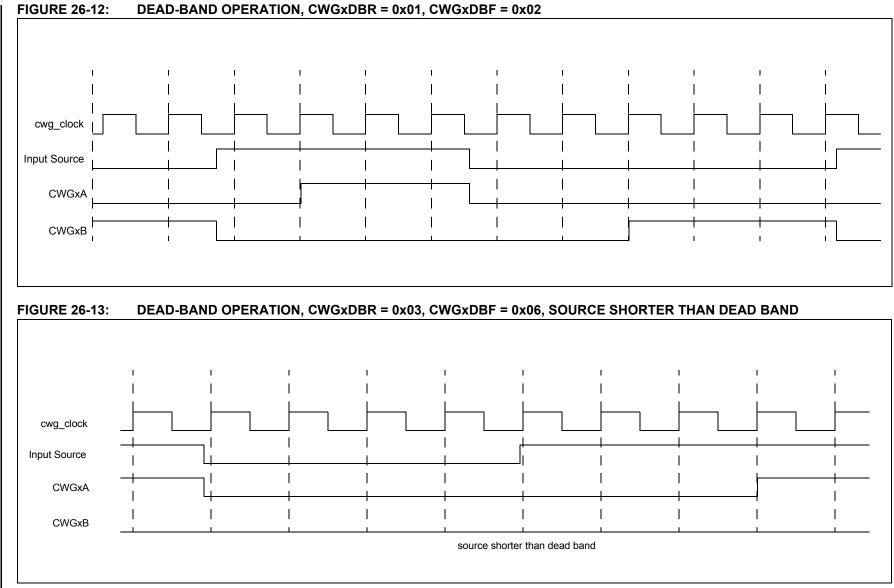

# FIGURE 26-6: SIMPLIFIED CWG BLOCK DIAGRAM (FORWARD AND REVERSE FULL-BRIDGE MODES)

# © 2016-2017 Microchip Technology Inc.

Preliminary

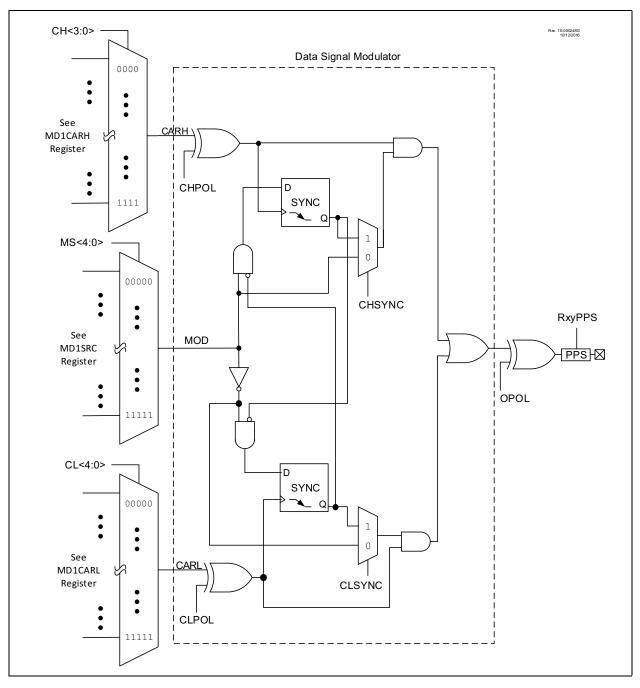

# 30.0 DATA SIGNAL MODULATOR (DSM) MODULE

The Data Signal Modulator (DSM) is a peripheral which allows the user to mix a data stream, also known as a modulator signal, with a carrier signal to produce a modulated output.

Both the carrier and the modulator signals are supplied to the DSM module either internally, from the output of a peripheral, or externally through an input pin.

The modulated output signal is generated by performing a logical "AND" operation of both the carrier and modulator signals and then provided to the MDOUT pin.

The carrier signal is comprised of two distinct and separate signals. A carrier high (CARH) signal and a carrier low (CARL) signal. During the time in which the modulator (MOD) signal is in a logic high state, the DSM mixes the carrier high signal with the modulator signal. When the modulator signal is in a logic low state, the DSM mixes the carrier low signal with the modulator signal.

Using this method, the DSM can generate the following types of Key Modulation schemes:

- Frequency-Shift Keying (FSK)

- Phase-Shift Keying (PSK)

- On-Off Keying (OOK)

Additionally, the following features are provided within the DSM module:

- Carrier Synchronization

- Carrier Source Polarity Select

- Programmable Modulator Data

- · Modulated Output Polarity Select

- Peripheral Module Disable, which provides the ability to place the DSM module in the lowest power consumption mode

Figure 30-1 shows a Simplified Block Diagram of the Data Signal Modulator peripheral.

# FIGURE 30-1: SIMPLIFIED BLOCK DIAGRAM OF THE DATA SIGNAL MODULATOR

© 2017 Microchip Technology Inc.

#### **REGISTER 32-4:** SPIxTCNTH: SPI TRANSFER COUNTER MSB REGISTER

| U-0   | U-0 | U-0 | U-0 | U-0 | R/W-0/0 | R/W-0/0 | R/W-0/0 |

|-------|-----|-----|-----|-----|---------|---------|---------|

| —     | _   | _   | -   | -   | TCNT10  | TCNT9   | TCNT8   |

| bit 7 |     |     |     |     |         |         | bit 0   |

| Legend:          |                  |                                    |

|------------------|------------------|------------------------------------|

| R = Readable bit | W = Writable bit | U = Unimplemented bit, read as '0' |

#### bit 7-3 Unimplemented: Read as '0'

| bit 2-0 | TCNT<10:8>:                                                                                        |

|---------|----------------------------------------------------------------------------------------------------|

|         | BMODE = 0                                                                                          |

|         | Bits 13-11 of the Transfer Counter, counting the total number of bits to transfer                  |

|         | BMODE = 1                                                                                          |

|         | Bits 10-8 of the Transfer Counter, counting the total number of bytes to transfer                  |

| Noto    | This register should not be written to while a transfer is in progress (PLISY hit of SPLyCON2 is a |

Note: This register should not be written to while a transfer is in progress (BUSY bit of SPIxCON2 is set).

#### REGISTER 32-5: SPIxTWIDTH: SPI TRANSFER WIDTH REGISTER

| U-0   | U-0 | U-0 | U-0 | U-0 | R/W-0/0 | R/W-0/0 | R/W-0/0 |

|-------|-----|-----|-----|-----|---------|---------|---------|

| —     | —   | —   | _   | —   | TWIDTH2 | TWIDTH1 | TWIDTH0 |

| bit 7 |     |     |     |     |         |         | bit 0   |

| Legend:          |                  |                                    |  |

|------------------|------------------|------------------------------------|--|

| R = Readable bit | W = Writable bit | U = Unimplemented bit, read as '0' |  |

- bit 7-3 Unimplemented: Read as '0'

- bit 2-0 TWIDTH<2:0>:

BMODE = 0

Bits 2-0 of the Transfer Counter, counting the total number of bits to transfer

BMODE = 1

Size (in bits) of each transfer counted by the transfer counter

- 111 **= 7 bits**

- 110 = 6 bits

- 101 **= 5 bits**

- 100 **= 4 bits**

- 011 = 3 bits

- 010 = 2 bits

- 001 **= 1 bit**

- 000 **= 8 bits**

Note: This register should not be written to while a transfer is in progress (BUSY bit of SPIxCON2 is set).

# 33.1 I<sup>2</sup>C Features

- Inter-Integrated Circuit (I<sup>2</sup>C) interface supports the following modes in hardware:

- Master mode

- Slave mode with byte NACKing

- Multi-Master mode

- · Dedicated Address, Receive and Transmit buffers

- · Up to four Slave addresses matching

- General Call address matching

- 7-bit and 10-bit addressing with masking

- Start, Restart, Stop, Address, Write, and ACK Interrupts

- Clock Stretching hardware for:

- RX Buffer Full

- TX Buffer Empty

- After Address, Write, and ACK

- Bus Collision Detection with arbitration

- Bus Timeout Detection

- SDA hold time selection

- I<sup>2</sup>C, SMBus 2.0, and SMBus 3.0 input level selections

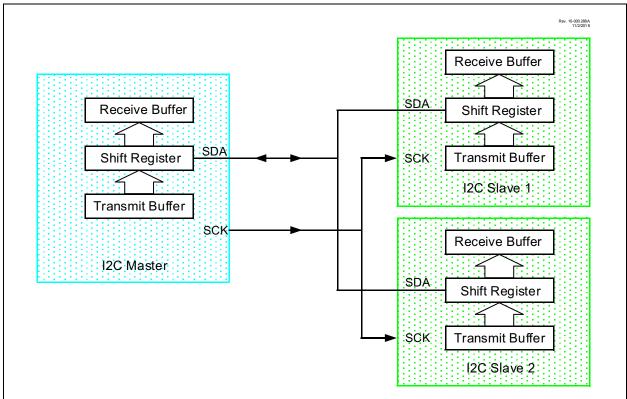

# 33.2 I<sup>2</sup>C Module Overview

The I<sup>2</sup>C module provides a synchronous interface between the microcontroller and other I<sup>2</sup>C-compatible devices using the two-wire I<sup>2</sup>C serial bus. Devices communicate in a master/slave environment. The I<sup>2</sup>C bus specifies two signal connections:

- Serial Clock (SCL)

- Serial Data (SDA)

Both the SCL and SDA connections are bidirectional open-drain lines, each requiring pull-up resistors to the supply voltage. Pulling the line to ground is considered a logical zero and letting the line float is considered a logical one. Every transaction on the I<sup>2</sup>C bus has to be initiated by the Master.

Figure 33-2 shows a typical connection between a master and more than one slave.

# FIGURE 33-2: I<sup>2</sup>C MASTER/SLAVE CONNECTIONS

#### **REGISTER 36-18:** ADRESH: ADC RESULT REGISTER HIGH, FM = 0

|                  |         |                     |         | •              |                  |                |              |

|------------------|---------|---------------------|---------|----------------|------------------|----------------|--------------|

| R/W-x/u          | R/W-x/u | R/W-x/u             | R/W-x/u | R/W-x/u        | R/W-x/u          | R/W-x/u        | R/W-x/u      |

|                  |         |                     | ADRE    | S<11:4>        |                  |                |              |

| bit 7            |         |                     |         |                |                  |                | bit 0        |

|                  |         |                     |         |                |                  |                |              |

| Legend:          |         |                     |         |                |                  |                |              |

| R = Readable I   | bit     | W = Writable bit    |         | U = Unimpler   | nented bit, read | d as '0'       |              |

| u = Bit is uncha | anged   | x = Bit is unknow   | wn      | -n/n = Value a | at POR and BC    | R/Value at all | other Resets |

| '1' = Bit is set |         | '0' = Bit is cleare | ed      |                |                  |                |              |

bit 7-0 **ADRES<11:4>**: ADC Result Register bits Upper eight bits of 12-bit conversion result.

# **REGISTER 36-19:** ADRESL: ADC RESULT REGISTER LOW, FM = 0

| R/W-x/u | R/W-x/u | R/W-x/u | R/W-x/u | U-0 | U-0 | U-0 | U-0   |

|---------|---------|---------|---------|-----|-----|-----|-------|

|         | ADRES   | 6<3:0>  |         | —   | —   | —   | —     |

| bit 7   |         |         |         |     |     |     | bit 0 |

| Legend:              |                      |                                                       |

|----------------------|----------------------|-------------------------------------------------------|

| R = Readable bit     | W = Writable bit     | U = Unimplemented bit, read as '0'                    |

| u = Bit is unchanged | x = Bit is unknown   | -n/n = Value at POR and BOR/Value at all other Resets |

| '1' = Bit is set     | '0' = Bit is cleared |                                                       |

bit 7-4 ADRES<3:0>: ADC Result Register bits. Lower four bits of 12-bit conversion result.

bit 3-0 Reserved

| _     | — | — | — | — | PCH<2:0> |       |

|-------|---|---|---|---|----------|-------|

| bit 7 |   |   |   |   |          | bit 0 |

# REGISTER 38-4: CMxPCH: COMPARATOR x NON-INVERTING CHANNEL SELECT REGISTER

| Legenu.           |                  |                             |                    |

|-------------------|------------------|-----------------------------|--------------------|

| R = Readable bit  | W = Writable bit | U = Unimplemented bit, read | l as '0'           |

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared        | x = Bit is unknown |

| bit 7-3 | Unimplemented: Read as '0'                                   |

|---------|--------------------------------------------------------------|

| bit 2-0 | PCH<2:0>: Comparator Non-Inverting Input Channel Select bits |

|         | 111 <b>= V</b> SS                                            |

|         | 110 = FVR_Buffer2                                            |

|         | 101 = DAC_Output                                             |

|         | 100 = PCH not connected                                      |

|         | 011 = PCH not connected                                      |

|         | 010 = PCH not connected                                      |

|         | 001 = CxIN1+                                                 |

|         | 000 = CxIN0+                                                 |

|         |                                                              |

# **REGISTER 38-5: CMOUT: COMPARATOR OUTPUT REGISTER**

| U-0   | U-0 | U-0 | U-0 | U-0 | U-0 | R-0/0 | R-0/0 |

|-------|-----|-----|-----|-----|-----|-------|-------|

| —     | —   | —   | —   | —   | —   | C2OUT | C1OUT |

| bit 7 |     |     |     |     |     |       | bit 0 |

| Legend:           |                  |                             |                    |

|-------------------|------------------|-----------------------------|--------------------|

| R = Readable bit  | W = Writable bit | U = Unimplemented bit, read | d as '0'           |

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared        | x = Bit is unknown |

bit 1 **C2OUT:** Mirror copy of C2OUT bit

bit 0 C1OUT: Mirror copy of C1OUT bit

# TABLE 38-3: SUMMARY OF REGISTERS ASSOCIATED WITH COMPARATOR MODULE

| Name    | Bit 7 | Bit 6 | Bit 5 | Bit 4 | Bit 3 | Bit 2    | Bit 1 | Bit 0 | Reset<br>Values<br>on page |

|---------|-------|-------|-------|-------|-------|----------|-------|-------|----------------------------|

| CMxCON0 | EN    | OUT   | —     | POL   | _     | _        | HYS   | SYNC  | 648                        |

| CMxCON1 | _     |       | _     |       | _     |          | INTP  | INTN  | 649                        |

| CMxNCH  | _     |       | _     |       |       | NCH<2:0> |       |       | 649                        |

| CMxPCH  | _     |       | _     |       |       | PCH<2:0> |       |       | 650                        |

| CMOUT   | _     | _     | _     | -     | _     | _        | C2OUT | C10UT | 650                        |

**Legend:** — = unimplemented, read as '0'. Shaded cells are unused by the comparator module.

W

| INFS   | NZ                | Incremen                     | Increment f, skip if not 0                                                       |                 |  |  |  |  |

|--------|-------------------|------------------------------|----------------------------------------------------------------------------------|-----------------|--|--|--|--|

| Synta  | x:                | INFSNZ f                     | {,d {,a}}                                                                        |                 |  |  |  |  |

| Opera  | ands:             | $0 \leq f \leq 255$          | $0 \le f \le 255$                                                                |                 |  |  |  |  |

|        |                   | d ∈ [0,1]<br>a ∈ [0,1]       |                                                                                  |                 |  |  |  |  |

| Opera  | ation.            | $f(f) + 1 \rightarrow de$    | et                                                                               |                 |  |  |  |  |

| Opere  |                   | skip if result               |                                                                                  |                 |  |  |  |  |

| Status | Affected:         | None                         | None                                                                             |                 |  |  |  |  |

| Encod  | ding:             | 0100                         | 10da ffi                                                                         | ff ffff         |  |  |  |  |

| Descr  | iption:           | The content                  | ts of register 'f                                                                | ' are           |  |  |  |  |

|        |                   |                              | <b>d. If 'd' is '</b> 0', th                                                     |                 |  |  |  |  |

|        |                   |                              | placed in W. If 'd' is '1', the result is placed back in register 'f' (default). |                 |  |  |  |  |

|        |                   |                              | If the result is not '0', the next                                               |                 |  |  |  |  |

|        |                   | instruction,                 | instruction, which is already fetched, is                                        |                 |  |  |  |  |

|        |                   |                              | ind a NOP is ex                                                                  |                 |  |  |  |  |

|        |                   | instead, ma                  | king it a 2-cyc                                                                  | le              |  |  |  |  |

|        |                   |                              | he Access Bar                                                                    | nk is selected. |  |  |  |  |

|        |                   |                              | he BSR is use                                                                    | d to select the |  |  |  |  |

|        |                   | GPR bank.<br>If 'a' is '∩' a | nd the extende                                                                   | ad instruction  |  |  |  |  |

|        |                   |                              | ed, this instruc                                                                 |                 |  |  |  |  |

|        |                   |                              | Literal Offset A                                                                 |                 |  |  |  |  |

|        |                   |                              | ever f ≤ 95 (5F                                                                  |                 |  |  |  |  |

|        |                   |                              | tion 41.2.3 "Byte-Oriented and Bit-<br>Oriented Instructions in Indexed Lit-     |                 |  |  |  |  |

|        |                   | eral Offset                  | Mode" for det                                                                    | tails.          |  |  |  |  |

| Words  | S:                | 1                            |                                                                                  |                 |  |  |  |  |

| Cycle  | s:                | 1(2)                         |                                                                                  |                 |  |  |  |  |

|        |                   |                              | cycles if skip a<br>a 2-word instr                                               |                 |  |  |  |  |

| Q Cv   | cle Activity:     | by                           |                                                                                  |                 |  |  |  |  |

| u oy   | Q1                | Q2                           | Q3                                                                               | Q4              |  |  |  |  |

| Γ      | Decode            | Read                         | Process                                                                          | Write to        |  |  |  |  |

| L      |                   | register 'f'                 | Data                                                                             | destination     |  |  |  |  |

| lf ski |                   | 02                           | 03                                                                               | 04              |  |  |  |  |

| Г      | Q1<br>No          | Q2<br>No                     | Q3<br>No                                                                         | Q4<br>No        |  |  |  |  |

|        | operation         | operation                    | operation                                                                        | operation       |  |  |  |  |

| lf ski | •                 | d by 2-word in               |                                                                                  |                 |  |  |  |  |

| F      | Q1                | Q2                           | Q3                                                                               | Q4              |  |  |  |  |

|        | No                | No                           | No                                                                               | No              |  |  |  |  |

| ╞      | operation<br>No   | operation                    | operation<br>No                                                                  | operation<br>No |  |  |  |  |

|        | operation         | No<br>operation              | operation                                                                        | operation       |  |  |  |  |

| Exam   | <u>ple</u> :      | HERE I<br>ZERO<br>NZERO      | INFSNZ REG                                                                       | , 1, 0          |  |  |  |  |

| F      | Before Instruc    |                              |                                                                                  |                 |  |  |  |  |

| E      | PC                | = Address                    | (HERE)                                                                           |                 |  |  |  |  |

| A      | After Instruction | on                           |                                                                                  |                 |  |  |  |  |

|        | REG<br>If REG     | = REG + <sup>2</sup>         | 1                                                                                |                 |  |  |  |  |

|        | PC                | $\neq$ 0;<br>= Address       | (NZERO)                                                                          |                 |  |  |  |  |

|        | lf REG<br>PC      | = 0;<br>= Address            | (ZERO)                                                                           |                 |  |  |  |  |

|        | . •               | ,                            | . (22100)                                                                        |                 |  |  |  |  |

| IORLW             | Inclusive                     | clusive OR literal with W |          |            |      |  |

|-------------------|-------------------------------|---------------------------|----------|------------|------|--|

| Syntax:           | IORLW k                       |                           |          |            |      |  |

| Operands:         | $0 \le k \le 255$             |                           |          |            |      |  |

| Operation:        | (W) .OR. $k \rightarrow W$    |                           |          |            |      |  |

| Status Affected:  | N, Z                          |                           |          |            |      |  |

| Encoding:         | 0000                          | 1001                      | .001 kkk |            | kkkk |  |

| Description:      | The conten<br>bit literal 'k' |                           |          |            |      |  |

| Words:            | 1                             |                           |          |            |      |  |

| Cycles:           | 1                             |                           |          |            |      |  |

| Q Cycle Activity: |                               |                           |          |            |      |  |

| Q1                | Q2                            | Q3                        | Q3       |            | Q4   |  |

| Decode            | Read<br>literal 'k'           | Process<br>Data           |          | Write to W |      |  |

| Evennler          | TODIN                         | 251                       |          |            |      |  |

| Example:          | IORLW                         | 35h                       |          |            |      |  |

| Before Instruc    | tion                          |                           |          |            |      |  |

| W                 | = 9Ah                         |                           |          |            |      |  |

| After Instruction | n                             |                           |          |            |      |  |

BFh

=

© 2017 Microchip Technology Inc.

Example

# Package Marking Information (Continued)

40-Lead UQFN (5x5x0.5 mm)