Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

#### Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

E·XFI

| Details                    |                                                                              |

|----------------------------|------------------------------------------------------------------------------|

| Product Status             | Active                                                                       |

| Core Processor             | PIC                                                                          |

| Core Size                  | 8-Bit                                                                        |

| Speed                      | 64MHz                                                                        |

| Connectivity               | I <sup>2</sup> C, LINbus, SPI, UART/USART                                    |

| Peripherals                | Brown-out Detect/Reset, DMA, HLVD, POR, PWM, WDT                             |

| Number of I/O              | 36                                                                           |

| Program Memory Size        | 32KB (16K x 16)                                                              |

| Program Memory Type        | FLASH                                                                        |

| EEPROM Size                | 256 x 8                                                                      |

| RAM Size                   | 2K x 8                                                                       |

| Voltage - Supply (Vcc/Vdd) | 2.3V ~ 5.5V                                                                  |

| Data Converters            | A/D 35x12b; D/A 1x5b                                                         |

| Oscillator Type            | Internal                                                                     |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                            |

| Mounting Type              | Surface Mount                                                                |

| Package / Case             | 40-UFQFN Exposed Pad                                                         |

| Supplier Device Package    | 40-UQFN (5x5)                                                                |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/pic18lf45k42t-i-mv |

|                            |                                                                              |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

| U                       |

|-------------------------|

|                         |

| IC                      |

| <u>``</u>               |

| $\overline{\mathbf{x}}$ |

| 8                       |

| Ξ                       |

|                         |

| ¥                       |

|                         |

| N                       |

| 6                       |

|                         |

| Ν                       |

| 7                       |

|                         |

| 4                       |

| 5                       |

| 1                       |

| 4                       |

| G                       |

| 1                       |

| /47/                    |

| Z                       |

| /55/                    |

| <b>M</b>                |

| 5                       |

| ;/56                    |

| Q                       |

| σ                       |

| 5                       |

| 5                       |

| Z                       |

| Σ                       |

|                         |

| 42                      |

| N                       |

| IABLE 1            | -                      |               |                  |                   | TABLE (PIC18) | (_)//          | (00.1.1           |                              |                     |                                            |     |                                                                                              |                                                                          |                                                                                                                   |                                          |     |                        |                     |             |

|--------------------|------------------------|---------------|------------------|-------------------|---------------|----------------|-------------------|------------------------------|---------------------|--------------------------------------------|-----|----------------------------------------------------------------------------------------------|--------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------|------------------------------------------|-----|------------------------|---------------------|-------------|

| 0/I                | 28-Pin SPDIP/SOIC/SSOP | 28-Pin (U)QFN | DDA              | Voltage Reference | DAC           | Comparators    | Zero Cross Detect | 1²C                          | IdS                 | UART                                       | WSQ | Timers/SMT                                                                                   | CCP and PWM                                                              | 9M0                                                                                                               | כרכ                                      | NCO | Clock Reference (CLKR) | Interrupt-on-Change | Basic       |

| RC0                | 11                     | 8             | ANC0             | 1                 | _             | -              | -                 | _                            | 1                   | _                                          | _   | T1CKI <sup>(1)</sup><br>T3CKI <sup>(1)</sup><br>T3G <sup>(1)</sup><br>SMTWIN1 <sup>(1)</sup> | _                                                                        | 1                                                                                                                 | 1                                        | 1   | -                      | IOCC0               | SOSCO       |

| RC1                | 12                     | 9             | ANC1             | -                 | _             | _              | -                 | _                            | -                   | _                                          | _   | SMTSIG1 <sup>(1)</sup>                                                                       | CCP2 <sup>(1)</sup>                                                      | -                                                                                                                 | -                                        | -   | _                      | IOCC1               | SOSCI       |

| RC2                | 13                     | 10            | ANC2             | _                 | _             | —              | —                 | _                            | _                   | _                                          | _   | T5CKI <sup>(1)</sup>                                                                         | CCP1 <sup>(1)</sup>                                                      | _                                                                                                                 | _                                        | _   | _                      | IOCC2               | _           |

| RC3                | 14                     | 11            | ANC3             | _                 | —             | —              | _                 | SCL1 <sup>(3,4)</sup>        | SCK1 <sup>(1)</sup> | _                                          | -   | T2IN <sup>(1)</sup>                                                                          | —                                                                        | _                                                                                                                 | _                                        | _   | —                      | IOCC3               | -           |

| RC4                | 15                     | 12            | ANC4             | —                 | —             | —              | —                 | SDA1 <sup>(3,4)</sup>        | SDI1 <sup>(1)</sup> | —                                          | —   | —                                                                                            | —                                                                        | —                                                                                                                 | _                                        | —   | —                      | IOCC4               | —           |

| RC5                | 16                     | 13            | ANC5             | _                 | —             | _              | _                 | —                            | —                   | _                                          |     | T4IN <sup>(1)</sup>                                                                          | —                                                                        | —                                                                                                                 | -                                        | _   | _                      | IOCC5               | _           |

| RC6                | 17                     | 14            | ANC6             | —                 | —             | -              | —                 | —                            | —                   | CTS1 <sup>(1)</sup>                        | -   | —                                                                                            | _                                                                        | —                                                                                                                 | _                                        | —   | —                      | IOCC6               | —           |

| RC7                | 18                     | 15            | ANC7             | _                 | —             | —              | _                 | _                            | _                   | RX1 <sup>(1)</sup>                         |     | —                                                                                            | _                                                                        | _                                                                                                                 | _                                        | _   | _                      | IOCC7               | _           |

| RE3                | 1                      | 26            | -                | _                 | -             | —              | -                 | -                            | —                   | -                                          | _   | _                                                                                            | -                                                                        | _                                                                                                                 | _                                        | _   | —                      | IOCE3               | MCLR<br>VPP |

| VDD                | 20                     | 17            | _                | _                 | —             | —              | —                 | —                            | _                   | —                                          | _   | _                                                                                            | —                                                                        | _                                                                                                                 | _                                        | _   | —                      | -                   | —           |

| Vss                | 8,<br>19               | 5,<br>16      | _                | -                 | —             | -              | -                 | -                            | -                   | -                                          | —   | —                                                                                            | —                                                                        | —                                                                                                                 | _                                        | -   | —                      | _                   | —           |

| OUT <sup>(2)</sup> | _                      | _             | ADGRDA<br>ADGRDB |                   | _             | C1OUT<br>C2OUT | _                 | SDA1<br>SCL1<br>SDA2<br>SCL2 | SS1<br>SCK1<br>SDO1 | DTR1<br>RTS1<br>TX1<br>DTR2<br>RTS2<br>TX2 | DSM | TMR0                                                                                         | CCP1<br>CCP2<br>CCP3<br>CCP4<br>PWM50UT<br>PWM60UT<br>PWM70UT<br>PWM80UT | CWG1A<br>CWG1B<br>CWG1C<br>CWG1D<br>CWG2A<br>CWG2A<br>CWG2A<br>CWG2C<br>CWG3A<br>CWG3A<br>CWG3B<br>CWG3C<br>CWG3D | CLC10UT<br>CLC20UT<br>CLC30UT<br>CLC40UT | NCO | CLKR                   | _                   | _           |

TABLE 1: 28-PIN ALLOCATION TABLE (PIC18(L)F2XK42) (CONTINUED)

2: All output signals shown in this row are PPS remappable.

This is a bidirectional signal. For normal module operation, the firmware should map this signal to the same pin in both the PPS input and PPS output registers. These pins can be configured for I<sup>2</sup>C and SMB™ 3.0/2.0 logic levels; The SCLx/SDAx signals may be assigned to any of the RB1/RB2/RC3/RC4 pins. PPS assignments to the other pins (e.g., RA5) will operate, but input logic levels will be standard TTL/ST as selected by the INLVL register, instead of the I<sup>2</sup>C specific or SMBUs input buffer thresholds. 4:

3:

| R/W-1          | R/W-1                                                                 | R/W-1                                                                                           | R/W-1                                            | R/W-1                              | R/W-1           | R/W-1               | R/W-1 |  |

|----------------|-----------------------------------------------------------------------|-------------------------------------------------------------------------------------------------|--------------------------------------------------|------------------------------------|-----------------|---------------------|-------|--|

| BOR            | REN<1:0>                                                              | LPBOREN                                                                                         | IVT1WAY                                          | MVECEN                             | PWRT            | <sup>-</sup> S<1:0> | MCLRE |  |

| bit 7          |                                                                       |                                                                                                 |                                                  |                                    |                 |                     | bit ( |  |

|                |                                                                       |                                                                                                 |                                                  |                                    |                 |                     |       |  |

| Legend:        |                                                                       |                                                                                                 |                                                  |                                    |                 |                     |       |  |

| R = Readable   |                                                                       | W = Writable                                                                                    |                                                  | •                                  | mented bit, rea |                     |       |  |

| -n = Value for | r blank device                                                        | '1' = Bit is set                                                                                |                                                  | '0' = Bit is cle                   | ared            | x = Bit is unk      | nown  |  |

| bit 7-6        | BOREN<1:0>                                                            | : Brown-out Re                                                                                  | set Enable bit                                   | S                                  |                 |                     |       |  |

|                | 11 = Brown-ou<br>10 = Brown-ou<br>01 = Brown-ou                       | l, Brown-out Re<br>ut Reset is enat<br>ut Reset is enat<br>ut Reset is enat<br>ut Reset is disa | oled, SBOREI<br>oled while run<br>oled according | N bit is ignored<br>ning, disabled |                 |                     | d     |  |

| bit 5          | 1 = Low-Powe                                                          | ow-Power BOR<br>er BOR is disab<br>er BOR is enabl                                              | led                                              |                                    |                 |                     |       |  |

| bit 4          | 1 = IVTLOCK<br>cycle                                                  | LOCK bit One-'<br>ED bit can be c<br>ED bit can be s                                            | leared and se                                    | t only once; IV                    |                 |                     |       |  |

| bit 3          | <b>MVECEN:</b> Mu<br>1 = Multi-vect                                   | lti-vector Enable<br>or enabled; Vec<br>terrupt behavior                                        | e bit<br>stor table used                         | ·                                  | ()              |                     | ,     |  |

| bit 2-1        | 11 = PWRT is<br>10 = PWRT se<br>01 = PWRT se                          | : Power-up Tim<br>disabled<br>et at 64 ms (204<br>et at 16 ms (512<br>et at 1 ms (32 L          | 8 LFINTOSC                                       | Cycles)<br>Cycles)                 |                 |                     |       |  |

| bit 0          | <u>If LVP = 1:</u><br>RE3 pin function<br>If LVP = 0:<br>1 = MCLR pin |                                                                                                 |                                                  | nction                             |                 |                     |       |  |

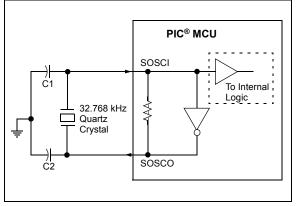

## 7.2.1.5 Secondary Oscillator

The secondary oscillator is a separate oscillator block that can be used as an alternate system clock source. The secondary oscillator is optimized for 32.768 kHz, and can be used with an external crystal oscillator connected to the SOSCI and SOSCO device pins, or an external clock source connected to the SOSCIN pin. The secondary oscillator can be selected during runtime using clock switching. Refer to Section 7.3 "Clock Switching" for more information.

Two power modes are available for the secondary oscillator. These modes are selected with the SOSCPWR (OSCCON3<6>). Clearing this bit selects the lower Crystal Gain mode which provides lowest microcontroller power consumption. Setting this bit enables a higher Gain mode to support faster crystal start-up or crystals with higher ESR.

### FIGURE 7-5: QUARTZ CRYSTAL OPERATION (SECONDARY OSCILLATOR)

- Note 1: Quartz crystal characteristics vary according to type, package and manufacturer. The user should consult the manufacturer data sheets for specifications and recommended application.

- Always verify oscillator performance over the VDD and temperature range that is expected for the application.

- **3:** For oscillator design assistance, reference the following Microchip Application Notes:

- AN826, "Crystal Oscillator Basics and Crystal Selection for PIC<sup>®</sup> and PIC<sup>®</sup> Devices" (DS00826)

- AN849, "Basic PIC<sup>®</sup> Oscillator Design" (DS00849)

- AN943, "Practical PIC<sup>®</sup> Oscillator Analysis and Design" (DS00943)

- AN949, "Making Your Oscillator Work" (DS00949)

- TB097, "Interfacing a Micro Crystal MS1V-T1K 32.768 kHz Tuning Fork Crystal to a PIC16F690/SS" (DS91097)

- AN1288, "Design Practices for Low-Power External Oscillators" (DS01288)

| TRIGEN | BURSTMD | Scanner Operation                                                                                                                                                                   |

|--------|---------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 0      | 0       | Memory access is requested when the CRC module is ready to accept data; the request is granted if no other higher priority source request is pending.                               |

| 1      | 0       | Memory access is requested when the CRC module is ready to accept data and trigger selection is true; the request is granted if no other higher priority source request is pending. |

| x      | 1       | Memory access is always requested, the request is granted if no other higher priority source request is pending.                                                                    |

# TABLE 14-1: SCANNER OPERATING MODES<sup>(1)</sup>

Note 1: See Section 3.1 "System Arbitration" for Priority selection and Section 3.2 "Memory Access Scheme" for Memory Access Scheme.

#### REGISTER 14-12: SCANLADRU: SCAN LOW ADDRESS UPPER BYTE REGISTER

| U-0   | U-0 | R/W-0/0 | R/W-0/0 | R/W-0/0 | R/W-0/0             | R/W-0/0 | R/W-0/0 |

|-------|-----|---------|---------|---------|---------------------|---------|---------|

| —     | —   |         |         | LADR<2  | 21:16> <b>(1,2)</b> |         |         |

| bit 7 | •   | •       |         |         |                     |         | bit 0   |

| Legend:              |                      |                                                       |

|----------------------|----------------------|-------------------------------------------------------|

| R = Readable bit     | W = Writable bit     | U = Unimplemented bit, read as '0'                    |

| u = Bit is unchanged | x = Bit is unknown   | -n/n = Value at POR and BOR/Value at all other Resets |

| '1' = Bit is set     | '0' = Bit is cleared |                                                       |

bit 7-6 Unimplemented: Read as '0'

bit 5-0 **LADR<21:16>:** Scan Start/Current Address bits<sup>(1,2)</sup> Upper bits of the current address to be fetched from, value increments on each fetch of memory.

- **Note 1:** Registers SCANLADRU/H/L form a 22-bit value, but are not guarded for atomic or asynchronous access; registers should only be read or written while SGO = 0 (SCANCON0 register).

- 2: While SGO = 1 (SCANCON0 register), writing to this register is ignored.

#### REGISTER 14-13: SCANLADRH: SCAN LOW ADDRESS HIGH BYTE REGISTER

| R/W-0/0                      | R/W-0/0 | R/W-0/0 | R/W-0/0 | R/W-0/0 | R/W-0/0 | R/W-0/0 | R/W-0/0 |  |

|------------------------------|---------|---------|---------|---------|---------|---------|---------|--|

| LADR<15:8> <sup>(1, 2)</sup> |         |         |         |         |         |         |         |  |

| bit 7 bit 0                  |         |         |         |         |         |         |         |  |

| Legend:              |                      |                                                       |

|----------------------|----------------------|-------------------------------------------------------|

| R = Readable bit     | W = Writable bit     | U = Unimplemented bit, read as '0'                    |

| u = Bit is unchanged | x = Bit is unknown   | -n/n = Value at POR and BOR/Value at all other Resets |

| '1' = Bit is set     | '0' = Bit is cleared |                                                       |

bit 7-0 LADR<15:8>: Scan Start/Current Address bits<sup>(1, 2)</sup> Most Significant bits of the current address to be fetched from, value increments on each fetch of memory.

- **Note 1:** Registers SCANLADRU/H/L form a 22-bit value, but are not guarded for atomic or asynchronous access; registers should only be read or written while SGO = 0 (SCANCON0 register).

- **2:** While SGO = 1 (SCANCON0 register), writing to this register is ignored.

#### 15.9.5 OVERRUN INTERRUPT

The Overrun Interrupt flag is set if the DMA receives a trigger to start a new message before the current message is completed.

|                              | 1 2 3           | (4)                 | 6 6                                   | ) (8)            | 9 10  | (i) (i)                             | 13 14                               | 15 | 19 f) | 13 | Ray. 10.000275E<br>8/11/2016 |

|------------------------------|-----------------|---------------------|---------------------------------------|------------------|-------|-------------------------------------|-------------------------------------|----|-------|----|------------------------------|

| Instruction<br>Clock         |                 |                     |                                       |                  |       |                                     |                                     |    |       |    |                              |

| EN                           |                 |                     |                                       |                  |       |                                     |                                     |    |       |    |                              |

| SIRQEN                       |                 |                     |                                       |                  |       |                                     |                                     |    |       |    |                              |

| Source Hardware<br>Trigger - |                 |                     |                                       |                  |       |                                     |                                     |    |       |    |                              |

| DGO-                         |                 |                     |                                       |                  |       |                                     |                                     |    |       |    |                              |

| DMAxSPTR                     | (0x100          | )                   | 0x101                                 | X                | 0x100 |                                     | 0x101                               | X  | 0x10  | 0  |                              |

| DMAxDPTR                     | (0x200          | )                   | 0x201                                 | χ                | 0x202 |                                     | 0x203                               | χ  | 0x20  | 0  |                              |

| DMAxSCNT                     | 2               |                     | 1                                     | _X               | 2     |                                     | 1                                   | X  | 2     |    |                              |

| DMAxDCNT                     | 4               |                     | 3                                     | _X               | 2     |                                     | 1                                   | χ  | 4     |    |                              |

| DMA STATE                    | IDLE            | SR <sup>(1)</sup> D | W <sup>(2)</sup> SR <sup>(1)</sup> DW | / <sup>(2)</sup> | IDLE  | SR <sup>(1)</sup> DW <sup>(2)</sup> | SR <sup>(1)</sup> DW <sup>(2)</sup> |    | IDLE  |    |                              |

| DMAxSCNTIF                   |                 |                     |                                       |                  | 1     |                                     |                                     |    |       |    |                              |

| DMAxDCNTIF                   |                 |                     |                                       |                  |       |                                     |                                     |    |       |    |                              |

| DMAxORIF _                   |                 |                     |                                       |                  |       |                                     |                                     | 1  |       |    |                              |

|                              | DMAxCON1bits.SM | A = 01              |                                       |                  |       |                                     |                                     |    |       |    |                              |

|                              | DMAxSSA 0x10    | 00                  | DMAxDSA                               | 0x200            |       |                                     |                                     |    |       |    |                              |

|                              | DMAxSSZ 0x2     | 2                   | DMAxDSZ                               | 0x20             |       |                                     |                                     |    |       |    |                              |

| Note 1:                      | SR - Source Re  | ead                 |                                       |                  |       |                                     |                                     |    |       |    |                              |

| 2:                           | DW - Destinatio | on Write            |                                       |                  |       |                                     |                                     |    |       |    |                              |

#### FIGURE 15-9: OVERRUN INTERRUPT

x = bit is unknown u = bit is unchanged

| REGISTER 15-1: DMAXCON0: DMAX CONTROL REGISTER 0 |            |               |     |             |                  |          |             |  |  |

|--------------------------------------------------|------------|---------------|-----|-------------|------------------|----------|-------------|--|--|

| R/W-0/0                                          | R/W/HC-0/0 | R/W/HS/HC-0/0 | U-0 | U-0         | R/W/HC-0/0       | U-0      | R/HS/HC-0/0 |  |  |

| EN                                               | SIRQEN     | DGO           | _   | _           | AIRQEN           | _        | XIP         |  |  |

| bit 7 bit 0                                      |            |               |     |             |                  |          |             |  |  |

|                                                  |            |               |     |             |                  |          |             |  |  |

| Legend:                                          | Legend:    |               |     |             |                  |          |             |  |  |

| R = Readable bit W = Writable bit                |            |               |     | U = Unimple | mented bit, read | d as '0' |             |  |  |

| -n/n = Value at POR  | 0 = bit is cleared |   |

|----------------------|--------------------|---|

| and BOR/Value at all |                    | I |

| other Resets         |                    |   |

|                      |                    |   |

| bit 7 EN: DMA Module Enable b | oit |

|-------------------------------|-----|

|-------------------------------|-----|

- 1 = Enables module

- 0 = Disables module

- SIRQEN: Start of Transfer Interrupt Request Enable bits

- 1 = Hardware triggers are allowed to start DMA transfers

- 0 = Hardware triggers are not allowed to start DMA transfers

## bit 5 DGO: DMA transaction bit

bit 6

- 1 = DMA transaction is in progress

- 0 = DMA transaction is not in progress

- bit 4-3 Unimplemented: Read as '0'

## bit 2 AIRQEN: Abort of Transfer Interrupt Request Enable bits

- 1 = Hardware triggers are allowed to abort DMA transfers

- 0 = Hardware triggers are not allowed to abort DMA transfers

## bit 1 Unimplemented: Read as '0'

- bit 0 XIP: Transfer in Progress Status bit

- 1 = The DMAxBUF register currently holds contents from a read operation and has not transferred data to the destination.

- 0 = The DMAxBUF register is empty or has successfully transferred data to the destination address

# 19.0 PERIPHERAL MODULE DISABLE (PMD)

Sleep, Idle and Doze modes allow users to substantially reduce power consumption by slowing or stopping the CPU clock. Even so, peripheral modules still remain clocked, and thus, consume some amount of power. There may be cases where the application needs what these modes do not provide: the ability to allocate limited power resources to the CPU while eliminating power consumption from the peripherals.

The PIC18F26/27/45/46/47/55/56/57K42 microcontrollers address this requirement by allowing peripheral modules to be selectively enabled or disabled, placing them into the lowest possible power mode.

All modules are ON by default following any Reset.

# **19.1** Disabling a Module

Disabling a module has the following effects:

- All clock and control inputs to the module are suspended; there are no logic transitions, and the module will not function.

- The module is held in Reset.

- · Any SFR becomes "unimplemented"

- Writing is disabled

- Reading returns 00h

- I/O functionality is prioritized as per Section 16.1, I/O Priorities

- All associated Input Selection registers are also disabled

# 19.2 Enabling a Module

When the PMD register bit is cleared, the module is re-enabled and will be in its Reset state (Power-on Reset). SFR data will reflect the POR Reset values.

Depending on the module, it may take up to one full instruction cycle for the module to become active. There should be no interaction with the module (e.g., writing to registers) for at least one instruction after it has been re-enabled.

# 19.3 Effects of a Reset

Following any Reset, each control bit is set to '0', enabling all modules.

# **19.4** System Clock Disable

Setting SYSCMD (PMD0, Register 19-1) disables the system clock (Fosc) distribution network to the peripherals. Not all peripherals make use of SYSCLK, so not all peripherals are affected. Refer to the specific peripheral description to see if it will be affected by this bit.

#### **REGISTER 21-3:** TxCLK: TIMERx CLOCK REGISTER

| U-0   | U-0 | U-0 | R/W-0/u | R/W-0/u | R/W-0/u | R/W-0/u | R/W-0/u |

|-------|-----|-----|---------|---------|---------|---------|---------|

| —     | —   | —   |         |         | CS<4:0> |         |         |

| bit 7 |     |     |         |         |         |         | bit 0   |

|       |     |     |         |         |         |         |         |

|       |     |     |         |         |         |         |         |

| Legend:           |                  |                       |               |  |

|-------------------|------------------|-----------------------|---------------|--|

| R = Readable bit  | W = Writable bit | U = Unimplemented bit | , read as '0' |  |

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared  | u = unchanged |  |

#### bit 7-5 Unimplemented: Read as '0'

bit 4-0 **CS<4:0>:** Timerx Clock Source Selection bits

| CS          | Timer1             | Timer3             | Timer5             |

|-------------|--------------------|--------------------|--------------------|

| CS          | Clock Source       | Clock Source       | Clock Source       |

| 11111-10001 | Reserved           | Reserved           | Reserved           |

| 10000       | CLC4               | CLC4               | CLC4               |

| 01111       | CLC3               | CLC3               | CLC3               |

| 01110       | CLC2               | CLC2               | CLC2               |

| 01101       | CLC1               | CLC1               | CLC1               |

| 01100       | TMR5 overflow      | TMR5 overflow      | Reserved           |

| 01011       | TMR3 overflow      | Reserved           | TMR3 overflow      |

| 01010       | Reserved           | TMR1 overflow      | TMR1 overflow      |

| 01001       | TMR0 overflow      | TMR0 overflow      | TMR0 overflow      |

| 01000       | CLKREF             | CLKREF             | CLKREF             |

| 00111       | SOSC               | SOSC               | SOSC               |

| 00110       | MFINTOSC (32 kHz)  | MFINTOSC (32 kHz)  | MFINTOSC (32 kHz)  |

| 00101       | MFINTOSC (500 kHz) | MFINTOSC (500 kHz) | MFINTOSC (500 kHz) |

| 00100       | LFINTOSC           | LFINTOSC           | LFINTOSC           |

| 00011       | HFINTOSC           | HFINTOSC           | HFINTOSC           |

| 00010       | Fosc               | Fosc               | Fosc               |

| 00001       | Fosc/4             | Fosc/4             | Fosc/4             |

| 00000       | T1CKIPPS           | T3CKIPPS           | T5CKIPPS           |

## 25.6.7 TIME OF FLIGHT MEASURE MODE

This mode measures the time interval between a rising edge on the SMTWINx input and a rising edge on the SMT1\_signal input, beginning to increment the timer upon observing a rising edge on the SMTWINx input, while updating the SMT1CPR register and resetting the timer upon observing a rising edge on the SMT1\_signal input. In the event of two SMTWINx rising edges without an SMT1\_signal rising edge, it will update the SMT1CPW register with the current value of the timer and reset the timer value. See Figure 25-14 and Figure 25-15.

-n/n = Value at POR and BOR/Value at all other Resets

q = Value depends on condition

| U-0            | U-0 | U-0          | R/W-0/0 | R/W-0/0      | R/W-0/0          | R/W-0/0 | R/W-0/0 |

|----------------|-----|--------------|---------|--------------|------------------|---------|---------|

| —              | —   | —            |         |              | ISM<4:0>         |         |         |

| bit 7          |     |              |         |              |                  |         | bit 0   |

|                |     |              |         |              |                  |         |         |

| Legend:        |     |              |         |              |                  |         |         |

| R = Readable b | bit | W = Writable | bit     | U = Unimpler | mented bit, read | as '0'  |         |

#### REGISTER 26-4: CWGxISM: CWGx INPUT SELECTION REGISTER

#### bit 7-5 Unimplemented Read as '0'

u = Bit is unchanged

'1' = Bit is set

bit 4-0 ISM<4:0>: CWG Data Input Selection Multiplexer Select bits

x = Bit is unknown

'0' = Bit is cleared

| ICM (4:0)   | CWG1                       | CWG2                       | CWG3                       |

|-------------|----------------------------|----------------------------|----------------------------|

| ISM<4:0>    | Input Selection            | Input Selection            | Input Selection            |

| 11111-10011 | Reserved                   | Reserved                   | Reserved                   |

| 10010       | CLC4_out                   | CLC4_out                   | CLC4_out                   |

| 10001       | CLC3_out                   | CLC3_out                   | CLC3_out                   |

| 10000       | CLC2_out                   | CLC2_out                   | CLC2_out                   |

| 01111       | CLC1_out                   | CLC1_out                   | CLC1_out                   |

| 01110       | DSM_out                    | DSM_out                    | DSM_out                    |

| 01101       | CMP2OUT                    | CMP2OUT                    | CMP2OUT                    |

| 01100       | CMP1OUT                    | CMP1OUT                    | CMP1OUT                    |

| 01011       | NCO10UT                    | NCO1OUT                    | NCO10UT                    |

| 01010-01001 | Reserved                   | Reserved                   | Reserved                   |

| 01000       | PWM8OUT                    | PWM8OUT                    | PWM8OUT                    |

| 00111       | PWM7OUT                    | PWM7OUT                    | PWM7OUT                    |

| 00110       | PWM6OUT                    | PWM6OUT                    | PWM6OUT                    |

| 00101       | PWM5OUT                    | PWM5OUT                    | PWM5OUT                    |

| 00100       | CCP4_out                   | CCP4_out                   | CCP4_out                   |

| 00011       | CCP3_out                   | CCP3_out                   | CCP3_out                   |

| 00010       | CCP2_out                   | CCP2_out                   | CCP2_out                   |

| 00001       | CCP1_out                   | CCP1_out                   | CCP1_out                   |

| 00000       | Pin selected by<br>CWG1PPS | Pin selected by<br>CWG2PPS | Pin selected by<br>CWG3PPS |

#### REGISTER 28-5: NCO1ACCU: NCO1 ACCUMULATOR REGISTER – UPPER BYTE<sup>(1)</sup>

| U-0   | U-0 | U-0 | U-0 | R/W-0/0 | R/W-0/0 | R/W-0/0 | R/W-0/0 |

|-------|-----|-----|-----|---------|---------|---------|---------|

| _     | —   | _   | —   |         | ACC<    | 19:16>  |         |

| bit 7 |     |     |     |         |         |         | bit 0   |

| Legend:              |                      |                                                       |

|----------------------|----------------------|-------------------------------------------------------|

| R = Readable bit     | W = Writable bit     | U = Unimplemented bit, read as '0'                    |

| u = Bit is unchanged | x = Bit is unknown   | -n/n = Value at POR and BOR/Value at all other Resets |

| '1' = Bit is set     | '0' = Bit is cleared |                                                       |

#### bit 7-4 Unimplemented: Read as '0'

#### bit 3-0 ACC<19:16>: NCO1 Accumulator, Upper Byte

**Note 1:** The accumulator spans registers NCO1ACCU:NCO1ACCH: NCO1ACCL. The 24 bits are reserved but not all are used. This register updates in real time, asynchronously to the CPU; there is no provision to guarantee atomic access to this 24-bit space using an 8-bit bus. Writing to this register while the module is operating will produce undefined results.

# **REGISTER 28-6:** NCO1INCL: NCO1 INCREMENT REGISTER – LOW BYTE<sup>(1,2)</sup>

| R/W-0/0     | R/W-0/0 | R/W-0/0 | R/W-0/0 | R/W-0/0 | R/W-0/0 | R/W-0/0 | R/W-1/1 |

|-------------|---------|---------|---------|---------|---------|---------|---------|

| INC<7:0>    |         |         |         |         |         |         |         |

| bit 7 bit 0 |         |         |         |         |         |         |         |

|             |         |         |         |         |         |         |         |

| Legend:              |                      |                                                       |

|----------------------|----------------------|-------------------------------------------------------|

| R = Readable bit     | W = Writable bit     | U = Unimplemented bit, read as '0'                    |

| u = Bit is unchanged | x = Bit is unknown   | -n/n = Value at POR and BOR/Value at all other Resets |

| '1' = Bit is set     | '0' = Bit is cleared |                                                       |

bit 7-0 INC<7:0>: NCO1 Increment, Low Byte

Note 1: The logical increment spans NCO1INCU:NCO1INCH:NCO1INCL.

2: NCO1INC is double-buffered as INCBUF; INCBUF is updated on the next falling edge of NCOCLK after writing to NCO1INCL; NCO1INCU and NCO1INCH should be written prior to writing NCO1INCL.

#### **REGISTER 28-7:** NCO1INCH: NCO1 INCREMENT REGISTER – HIGH BYTE<sup>(1)</sup>

| R/W-0/0     | R/W-0/0 | R/W-0/0 | R/W-0/0 | R/W-0/0 | R/W-0/0 | R/W-0/0 | R/W-0/0 |

|-------------|---------|---------|---------|---------|---------|---------|---------|

| INC<15:8>   |         |         |         |         |         |         |         |

| bit 7 bit 0 |         |         |         |         |         |         |         |

|             |         |         |         |         |         |         |         |

| Legend:              |                      |                                                       |

|----------------------|----------------------|-------------------------------------------------------|

| R = Readable bit     | W = Writable bit     | U = Unimplemented bit, read as '0'                    |

| u = Bit is unchanged | x = Bit is unknown   | -n/n = Value at POR and BOR/Value at all other Resets |

| '1' = Bit is set     | '0' = Bit is cleared |                                                       |

#### bit 7-0 INC<15:8>: NCO1 Increment, High Byte

Note 1: The logical increment spans NCO1INCU:NCO1INCH:NCO1INCL.

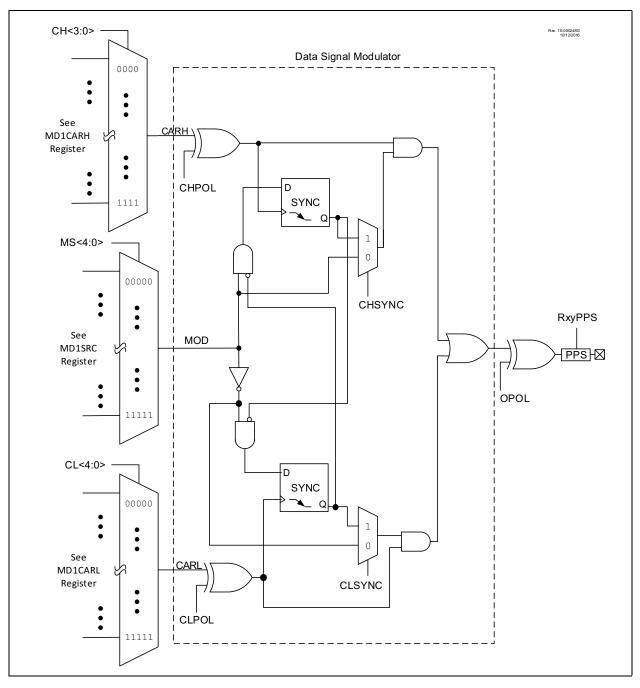

# 30.0 DATA SIGNAL MODULATOR (DSM) MODULE

The Data Signal Modulator (DSM) is a peripheral which allows the user to mix a data stream, also known as a modulator signal, with a carrier signal to produce a modulated output.

Both the carrier and the modulator signals are supplied to the DSM module either internally, from the output of a peripheral, or externally through an input pin.

The modulated output signal is generated by performing a logical "AND" operation of both the carrier and modulator signals and then provided to the MDOUT pin.

The carrier signal is comprised of two distinct and separate signals. A carrier high (CARH) signal and a carrier low (CARL) signal. During the time in which the modulator (MOD) signal is in a logic high state, the DSM mixes the carrier high signal with the modulator signal. When the modulator signal is in a logic low state, the DSM mixes the carrier low signal with the modulator signal.

Using this method, the DSM can generate the following types of Key Modulation schemes:

- Frequency-Shift Keying (FSK)

- Phase-Shift Keying (PSK)

- On-Off Keying (OOK)

Additionally, the following features are provided within the DSM module:

- Carrier Synchronization

- Carrier Source Polarity Select

- Programmable Modulator Data

- · Modulated Output Polarity Select

- Peripheral Module Disable, which provides the ability to place the DSM module in the lowest power consumption mode

Figure 30-1 shows a Simplified Block Diagram of the Data Signal Modulator peripheral.

#### FIGURE 30-1: SIMPLIFIED BLOCK DIAGRAM OF THE DATA SIGNAL MODULATOR

© 2017 Microchip Technology Inc.

| R/C/HS-0/0   | U-0                                                                   | R-1/1              | U-0           | R/C/HS-0/0                    | S-0/0            | U-0    | R-0/0 |  |  |

|--------------|-----------------------------------------------------------------------|--------------------|---------------|-------------------------------|------------------|--------|-------|--|--|

| TXWE         | _                                                                     | TXBE               |               | RXRE                          | CLRBF            | _      | RXBF  |  |  |

| bit 7        |                                                                       |                    |               | · ·                           |                  |        | bit 0 |  |  |

|              |                                                                       |                    |               |                               |                  |        |       |  |  |

| Legend:      |                                                                       |                    |               |                               |                  |        |       |  |  |

| R = Readable | bit                                                                   | W = Writable       | bit           | U = Unimplen<br>C = Clearable | nented bit, read | as '0' |       |  |  |

|              |                                                                       |                    |               | S = Settable I                |                  |        |       |  |  |

|              |                                                                       |                    |               | HS = Bit can                  | be set by hardw  | are    |       |  |  |

|              |                                                                       |                    |               |                               |                  |        |       |  |  |

| bit 7        | TXWE: Transmit Buffer Write Error bit                                 |                    |               |                               |                  |        |       |  |  |

|              | 1 = SPIxTxB                                                           | was written wh     | ile TxFIFO w  | vas full                      |                  |        |       |  |  |

|              | 0 = No error h                                                        | as occurred        |               |                               |                  |        |       |  |  |

| bit 6        | Unimplemen                                                            | ted: Read as '     | o'            |                               |                  |        |       |  |  |

| bit 5        | <b>TXBE</b> : Transmit Buffer Empty bit (read-only)                   |                    |               |                               |                  |        |       |  |  |

|              | 1 = Transmit buffer TxFIFO is empty                                   |                    |               |                               |                  |        |       |  |  |

|              | 0 = Transmit b                                                        | ouffer is not en   | npty          |                               |                  |        |       |  |  |

| bit 4        | Unimplemen                                                            | ted: Read as '     | ) <b>`</b>    |                               |                  |        |       |  |  |

| bit 3        | RXRE: Receive Buffer Read Error bit                                   |                    |               |                               |                  |        |       |  |  |

|              | 1 = SPIxRB was read while RxFIFO was empty                            |                    |               |                               |                  |        |       |  |  |

|              | 0 = No error has occurred                                             |                    |               |                               |                  |        |       |  |  |

| bit 2        | CLRBF: Clear Buffer Control bit (write only)                          |                    |               |                               |                  |        |       |  |  |

|              | 1 = Reset the receive and transmit buffers, making both buffers empty |                    |               |                               |                  |        |       |  |  |

|              | 0 = Take no a                                                         | ction              |               |                               |                  |        |       |  |  |

| bit 1        | Unimplemen                                                            | ted: Read as '     | D'            |                               |                  |        |       |  |  |

| bit 0        | RXBF: Receiv                                                          | ve Buffer Full b   | it (read-only | )                             |                  |        |       |  |  |

|              | 1 = Receive b                                                         | ouffer is full     |               |                               |                  |        |       |  |  |

|              | 0 = Receive b                                                         | ouffer is not full |               |                               |                  |        |       |  |  |

|              |                                                                       |                    |               |                               |                  |        |       |  |  |

#### REGISTER 32-11: SPIxRxB: SPI READ BUFFER REGISTER

| R-0   | R-0  | R-0  | R-0  | R-0  | R-0  | R-0  | R-0   |

|-------|------|------|------|------|------|------|-------|

| RXB7  | RXB6 | RXB5 | RXB4 | RXB3 | RXB2 | RXB1 | RXB0  |

| bit 7 |      |      |      |      |      |      | bit 0 |

| Legend:          |                  |                                    |

|------------------|------------------|------------------------------------|

| R = Readable bit | W = Writable bit | U = Unimplemented bit, read as '0' |

bit 7-0 **RXB<7:0>**: Receiver Buffer bits (read-only)

If RX buffer is not empty:

Contains the top-most byte of RXFIFO, and reading this register will remove the top-most byte RXFIFO and decrease the occupancy of the RXFIFO

### If RX buffer is empty:

Reading this register will read as '0', leave the occupancy unchanged, and set the RXRE bit of SPIxSTATUS

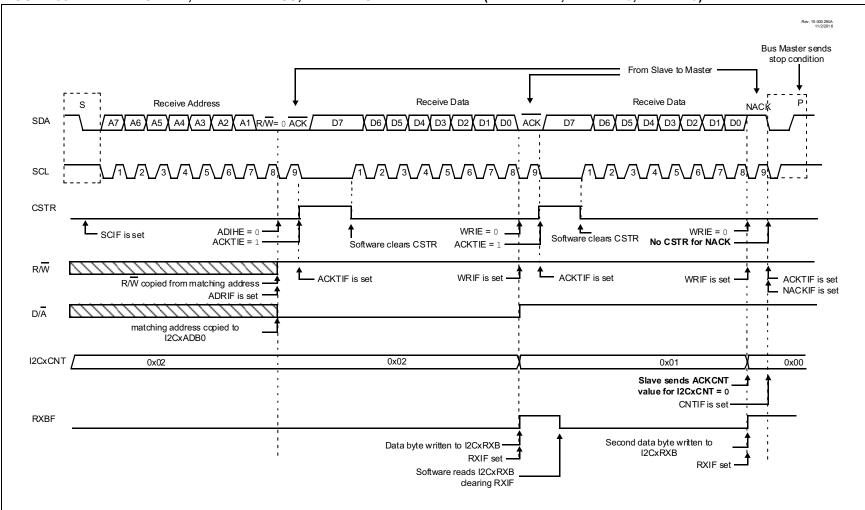

### FIGURE 33-7: $I^{2}C$ SLAVE, 7-BIT ADDRESS, RECEPTION WITH I2CxCNT (ACKTIE = 1, ADRIE = 0, WRIE = 0)

PIC18(L)F26/27/45/46/47/55/56/57K42

# **36.1 ADC Configuration**

When configuring and using the ADC the following functions must be considered:

- Port configuration

- Channel selection

- ADC voltage reference selection

- ADC conversion clock source

- Interrupt control

- Result formatting

- Conversion Trigger Selection

- ADC Acquisition Time

- ADC Precharge Time

- · Additional Sample and Hold Capacitor

- Single/Double Sample Conversion

- Guard Ring Outputs

## 36.1.1 PORT CONFIGURATION

The ADC can be used to convert both analog and digital signals. When converting analog signals, the I/O pin should be configured for analog by setting the associated TRIS and ANSEL bits. Refer to **Section 16.0 "I/O Ports"** for more information.

**Note:** Analog voltages on any pin that is defined as a digital input may cause the input buffer to conduct excess current.

### 36.1.2 CHANNEL SELECTION

There are several channel selections available:

- Eight PORTA pins (RA<7:0>)

- Eight PORTB pins (RB<7:0>)

- Eight PORTC pins (RC<7:0>)

- Eight PORTD pins (RD<7:0>, PIC18(L)F45/46/47/ 55/56/57K42 only)

- Three PORTE pins (RE<2:0>, PIC18(L)F45/46/47/ 55/56/57K42 only)

- Eight PORTF pins (RD<7:0>, PIC18(L)F55/56/ 57K42 only)

- Temperature Indicator

- DAC output

- Fixed Voltage Reference (FVR)

- Vss (ground)

The ADPCH register determines which channel is connected to the sample and hold circuit.

When changing channels, a delay is required before starting the next conversion.

Refer to Section 36.2 "ADC Operation" for more information.

### 36.1.3 ADC VOLTAGE REFERENCE

The PREF<1:0> bits of the ADREF register provide control of the positive voltage reference. The positive voltage reference can be:

- VREF+ pin

- VDD

- FVR outputs

The NREF bit of the ADREF register provides control of the negative voltage reference. The negative voltage reference can be:

- VREF- pin

- Vss

See **Section 34.0 "Fixed Voltage Reference (FVR)"** for more details on the Fixed Voltage Reference.

### 36.1.4 CONVERSION CLOCK

The source of the conversion clock is software selectable via the ADCLK register and the CS bits of the ADCON0 register. If Fosc is selected as the ADC clock, there is a prescaler available to divide the clock so that it meets the ADC clock period specification. The ADC clock source options are the following:

- Fosc/(2\*n)(where n is from 1 to 128)

- · FRC (dedicated RC oscillator)

The time to complete one bit conversion is defined as TAD. Refer Figure 36-2 for the complete timing details of the ADC conversion.

For correct conversion, the appropriate TAD specification must be met. Refer to Table 44-16 for more information. Table 36-1 gives examples of appropriate ADC clock selections.

- **Note 1:** Unless using the FRC, any changes in the system clock frequency will change the ADC clock frequency, which may adversely affect the ADC result.

- 2: The internal control logic of the ADC runs off of the clock selected by the CS bit of ADCON0. What this can mean is when the CS bit of ADCON0 is set to '1' (ADC runs on FRC), there may be unexpected delays in operation when setting ADC control bits.

#### 36.1.5 INTERRUPTS

The ADC module allows for the ability to generate an interrupt upon completion of an Analog-to-Digital conversion. The ADC Interrupt Flag is the ADIF bit in the PIRx register. The ADC Interrupt Enable is the ADIE bit in the PIEx register. The ADIF bit must be cleared in software.

- **Note 1:** The ADIF bit is set at the completion of every conversion, regardless of whether or not the ADC interrupt is enabled.

- **2:** The ADC operates during Sleep only when the FRC oscillator is selected.

This interrupt can be generated while the device is operating or while in Sleep. If the device is in Sleep, the interrupt will wake up the device. Upon waking from Sleep, the next instruction following the SLEEP instruction is always executed. If the user is attempting to wake up from Sleep and resume in-line code execution, the ADIE bit of the PIEx register and the GIE bits of the INTCON0 register must both be set. If all these bits are set, the execution will switch to the Interrupt Service Routine.

#### 36.1.6 RESULT FORMATTING

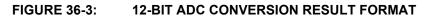

The 12-bit ADC conversion result can be supplied in two formats, left justified or right justified. The FM bits of the ADCON0 register controls the output format.

Figure 36-3 shows the two output formats.

Writes to the ADRES register pair are always right justified regardless of the selected format mode. Therefore, data read after writing to ADRES when ADFRM0 = 0 will be shifted left four places.

| TABLE 36-6: | SUMMARY OF REGISTERS ASSOCIATED WITH ADC (CONTINUED) |

|-------------|------------------------------------------------------|

|-------------|------------------------------------------------------|

| Name   | Bit 7     | Bit 6     | Bit 5 | Bit 4      | Bit 3 | Bit 2 | Bit 1 | Bit 0 | Register<br>on Page |

|--------|-----------|-----------|-------|------------|-------|-------|-------|-------|---------------------|

| ADERRL | ERR<7:0>  |           |       |            |       |       | 633   |       |                     |

| ADERRH |           | ERR<15:8> |       |            |       |       |       | 633   |                     |

| ADLTHH |           | LTH<15:8> |       |            |       |       |       | 633   |                     |

| ADLTHL | LTH<7:0>  |           |       |            |       |       | 634   |       |                     |

| ADUTHH | UTH<15:8> |           |       |            |       |       | 634   |       |                     |

| ADUTHL | UTH<7:0>  |           |       |            |       |       | 634   |       |                     |

| ADERRL | ERR<15:8> |           |       |            |       | 633   |       |       |                     |

| ADACT  | —         | —         | _     | ADACT<4:0> |       |       | 619   |       |                     |

| ADCP   | CPON      | _         | _     | _          | _     | _     | _     | CPRDY | 636                 |

**Legend:** – = unimplemented read as '0'. Shaded cells are not used for the ADC module.

| тѕт                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | FSZ             | Test f, skip if 0        |                     |                 |  |  |  |  |

|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------|--------------------------|---------------------|-----------------|--|--|--|--|

| Synta                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | ax:             | TSTFSZ f {               | a}                  |                 |  |  |  |  |

| Operands:                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |                 | 0 ≤ f ≤ 255<br>a ∈ [0,1] |                     |                 |  |  |  |  |

| Oper                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | ation:          | skip if f = 0            |                     |                 |  |  |  |  |

| Statu                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | s Affected:     | None                     | None                |                 |  |  |  |  |

| Enco                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | ding:           | 0110                     | 0110 011a ffff ffff |                 |  |  |  |  |

| Description:<br>If 'f' = 0, the next instruction fetched<br>during the current instruction execution<br>is discarded and a NOP is executed,<br>making this a 2-cycle instruction.<br>If 'a' is '0', the Access Bank is selected<br>If 'a' is '1', the BSR is used to select th<br>GPR bank.<br>If 'a' is '0' and the extended instruction<br>set is enabled, this instruction operate<br>in Indexed Literal Offset Addressing<br>mode whenever f ≤ 95 (5Fh). See Sec<br>tion 41.2.3 "Byte-Oriented and Bit-<br>Oriented Instructions in Indexed Lite<br>eral Offset Mode" for details. |                 |                          |                     |                 |  |  |  |  |

| Word                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | ls:             | 1                        |                     |                 |  |  |  |  |

| Cycles: 1(2)<br>Note: 3 cycles if skip and followed<br>by a 2-word instruction.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |                 |                          |                     |                 |  |  |  |  |

| QC                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | ycle Activity:  | - , -                    |                     |                 |  |  |  |  |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | Q1              | Q2                       | Q3                  | Q4              |  |  |  |  |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | Decode          | Read                     | Process             | No              |  |  |  |  |

| 16 - 1                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |                 | register 'f'             | Data                | operation       |  |  |  |  |

| lf sk                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | •               | 02                       | 03                  | 04              |  |  |  |  |

| 1                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | Q1<br>No        | Q2<br>No                 | Q3<br>No            | Q4<br>No        |  |  |  |  |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | operation       | operation                | operation           | operation       |  |  |  |  |

| lf sk                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | ip and followed | •                        |                     | I               |  |  |  |  |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | Q1              | Q2                       | Q3                  | Q4              |  |  |  |  |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | No              | No                       | No                  | No              |  |  |  |  |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | operation       | operation                | operation           | operation       |  |  |  |  |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | No<br>operation | No<br>operation          | No<br>operation     | No<br>operation |  |  |  |  |

| Example: HERE TSTFSZ CNT, 1<br>NZERO :<br>ZERO :                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |                 |                          |                     |                 |  |  |  |  |

| Before Instruction PC = Address (HERE)   After Instruction If CNT = 00h,   PC = Address (ZERO)   If CNT ≠ 00h,                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |                 |                          |                     |                 |  |  |  |  |

| PC = Address (NZERO)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |                 |                          |                     |                 |  |  |  |  |