Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

E·XFI

| Product Status             | Active                                                                       |

|----------------------------|------------------------------------------------------------------------------|

| Core Processor             | PIC                                                                          |

| Core Size                  | 8-Bit                                                                        |

| Speed                      | 64MHz                                                                        |

| Connectivity               | I <sup>2</sup> C, LINbus, SPI, UART/USART                                    |

| Peripherals                | Brown-out Detect/Reset, DMA, HLVD, POR, PWM, WDT                             |

| Number of I/O              | 36                                                                           |

| Program Memory Size        | 32KB (16K x 16)                                                              |

| Program Memory Type        | FLASH                                                                        |

| EEPROM Size                | 256 x 8                                                                      |

| RAM Size                   | 2K x 8                                                                       |

| Voltage - Supply (Vcc/Vdd) | 2.3V ~ 5.5V                                                                  |

| Data Converters            | A/D 35x12b; D/A 1x5b                                                         |

| Oscillator Type            | Internal                                                                     |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                            |

| Mounting Type              | Surface Mount                                                                |

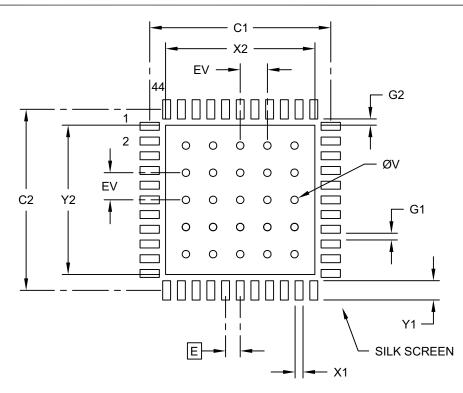

| Package / Case             | 44-TQFP                                                                      |

| Supplier Device Package    | 44-TQFP (10x10)                                                              |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/pic18lf45k42t-i-pt |

|                            |                                                                              |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

| R/W-0/0          | R/W-0/0                         | U-0               | U-0            | U-0                                                   | U-0                          | U-0 | U-0   |  |  |

|------------------|---------------------------------|-------------------|----------------|-------------------------------------------------------|------------------------------|-----|-------|--|--|

| TMR5GIE          | TMR5IE                          | —                 | —              | —                                                     |                              | —   | —     |  |  |

| bit 7            |                                 |                   |                |                                                       |                              |     | bit 0 |  |  |

|                  |                                 |                   |                |                                                       |                              |     |       |  |  |

| Legend:          |                                 |                   |                |                                                       |                              |     |       |  |  |

| R = Readable     | bit                             | W = Writable      | bit            | U = Unimpler                                          | implemented bit, read as '0' |     |       |  |  |

| u = Bit is uncha | u = Bit is unchanged x = Bit is |                   | iown           | -n/n = Value at POR and BOR/Value at all other Resets |                              |     |       |  |  |

| '1' = Bit is set |                                 | '0' = Bit is clea | ared           |                                                       |                              |     |       |  |  |

|                  |                                 |                   |                |                                                       |                              |     |       |  |  |

| bit 7            | TMR5GIE: TN                     | /IR5 Gate Inter   | rupt Enable bi | it                                                    |                              |     |       |  |  |

|                  | 1 = Enabled                     |                   |                |                                                       |                              |     |       |  |  |

|                  | 0 = Disabled                    |                   |                |                                                       |                              |     |       |  |  |

| bit 6            | TMR5IE: TMF                     | R5 Interrupt En   | able bit       |                                                       |                              |     |       |  |  |

|                  | 1 = Enabled                     |                   |                |                                                       |                              |     |       |  |  |

|                  | 0 = Disabled                    |                   |                |                                                       |                              |     |       |  |  |

| bit 5-0          | 5-0 Unimplemented: Read as '0'  |                   |                |                                                       |                              |     |       |  |  |

#### REGISTER 9-22: PIE8: PERIPHERAL INTERRUPT ENABLE REGISTER 8

#### REGISTER 9-23: PIE9: PERIPHERAL INTERRUPT ENABLE REGISTER 9

| U-0   | U-0 | U-0 | U-0 | R/W-0/0 | R/W-0/0 | R/W-0/0 | R/W-0/0 |

|-------|-----|-----|-----|---------|---------|---------|---------|

| —     | —   | —   | —   | CLC3IE  | CWG3IE  | CCP3IE  | TMR6IE  |

| bit 7 |     |     |     |         |         |         | bit 0   |

| Legend:              |                      |                                                       |

|----------------------|----------------------|-------------------------------------------------------|

| R = Readable bit     | W = Writable bit     | U = Unimplemented bit, read as '0'                    |

| u = Bit is unchanged | x = Bit is unknown   | -n/n = Value at POR and BOR/Value at all other Resets |

| '1' = Bit is set     | '0' = Bit is cleared |                                                       |

| bit 7-4 | Unimplemented: Read as '0'        |

|---------|-----------------------------------|

| bit 3   | CLC3IE: CLC3 Interrupt Enable bit |

|         | 1 = Enabled<br>0 = Disabled       |

| bit 2   |                                   |

| DIT Z   | CWG3IE: CWG3 Interrupt Enable bit |

|         | 1 = Enabled                       |

|         | 0 = Disabled                      |

| bit 1   | CCP3IE: CCP3 Interrupt Enable bit |

|         | 1 = Enabled                       |

|         | 0 = Disabled                      |

| bit 0   | TMR6IE: TMR6 Interrupt Enable bit |

|         | 1 = Enabled                       |

|         | 0 = Disabled                      |

| R/W-1/1         | R/W-1/1       | R/W-1/1                      | R/W-1/1             | R/W-1/1             | R/W-1/1            | R/W-1/1         | R/W-1/1    |

|-----------------|---------------|------------------------------|---------------------|---------------------|--------------------|-----------------|------------|

| I2C2TXIP        | I2C2RXIP      | DMA2AIP                      | DMA2ORIP            | DMA2DCNTIP          | DMA2SCNTIP         | C2IP            | INT1IP     |

| bit 7           |               |                              |                     |                     |                    |                 | bit (      |

|                 |               |                              |                     |                     |                    |                 |            |

| Legend:         |               |                              |                     |                     |                    | (a)             |            |

| R = Readabl     |               | W = Writable b               |                     | •                   | ented bit, read as |                 |            |

| u = Bit is und  | •             | x = Bit is unkno             |                     | -n/n = Value at     | POR and BOR/       | /alue at all ot | her Resets |

| '1' = Bit is se | t             | '0' = Bit is clea            | red                 |                     |                    |                 |            |

| bit 7           |               | <sup>2</sup> C2 Transmit Int | orrupt Driarity b   | :+                  |                    |                 |            |

|                 | 1 = High pri  |                              |                     | п                   |                    |                 |            |

|                 | 0 = Low price |                              |                     |                     |                    |                 |            |

| bit 6           | -             | <sup>2</sup> C2 Receive Inte | errupt Priority bi  | t                   |                    |                 |            |

|                 | 1 = High pri  | ority                        |                     |                     |                    |                 |            |

|                 | 0 = Low price | ority                        |                     |                     |                    |                 |            |

| bit 5           |               | DMA2 Abort Inte              | rrupt Priority bit  |                     |                    |                 |            |

|                 | 1 = High pri  | •                            |                     |                     |                    |                 |            |

| bit 4           | 0 = Low price | : DMA2 Overrun               | Interrupt Driarit   | hy hit              |                    |                 |            |

| DIL 4           | 1 = High pri  |                              | i interrupt Priorit | ly Dit              |                    |                 |            |

|                 | 0 = Low price |                              |                     |                     |                    |                 |            |

| bit 3           |               |                              | nation Count Int    | errupt Priority bit |                    |                 |            |

|                 | 1 = High pri  | ority                        |                     |                     |                    |                 |            |

|                 | 0 = Low price | ority                        |                     |                     |                    |                 |            |

| bit 2           |               | IP: DMA2 Sour                | ce Count Interru    | pt Priority bit     |                    |                 |            |

|                 | 1 = High pri  |                              |                     |                     |                    |                 |            |

| bit 1           | 0 = Low price | errupt Priority bi           | :+                  |                     |                    |                 |            |

|                 | 1 = High pri  |                              | IL                  |                     |                    |                 |            |

|                 | 0 = Low price |                              |                     |                     |                    |                 |            |

| bit 0           | •             | ernal Interrupt 1            | Interrupt Priority  | / bit               |                    |                 |            |

|                 | 1 = High pri  | •                            |                     |                     |                    |                 |            |

|                 | 0 = Low price | hrity                        |                     |                     |                    |                 |            |

## REGISTER 9-30: IPR5: PERIPHERAL INTERRUPT PRIORITY REGISTER 5

#### 13.3.5 WRITE VERIFY

;

Depending on the application, good programming practice may dictate that the value written to the memory should be verified against the original value. This should be used in applications where excessive writes can stress bits near the specification limit.

#### EXAMPLE 13-5: DATA EEPROM READ

| Data | Memory Addres | s to read   |   |                          |

|------|---------------|-------------|---|--------------------------|

|      | CLRF          | NVMCON1     | ; | Setup Data EEPROM Access |

|      | MOVF          | EE_ADDRL, W | ; |                          |

|      | MOVWF         | NVMADRL     | ; | Setup Address            |

|      | BSF           | NVMCON1, RD | ; | Issue EE Read            |

|      | MOVF          | NVMDAT, W   | ; | W = EE_DATA              |

#### EXAMPLE 13-6: DATA EEPROM WRITE

| ; Data Memory | / Address | to write  |      |   |                          |

|---------------|-----------|-----------|------|---|--------------------------|

| C             | LRF       | NVMCON1   |      | ; | Setup Data EEPROM Access |

| M             | OVF       | EE_ADDRL, | W    | ; |                          |

| M             | OVWF      | NVMADRL   |      | ; | Setup Address            |

| ; Data Memory | y Value t | o write   |      |   |                          |

| M             | OVF       | EE_DATA,  | Ŵ    | ; |                          |

| M             | OVWF      | NVMDAT    |      | ; |                          |

| ; Enable writ | es        |           |      |   |                          |

| В             | SF        | NVMCON1,  | WREN | ; |                          |

| ; Disable int | errupts   |           |      |   |                          |

| В             | CF        | INTCON0,  | GIE  | ; |                          |

| ; Required ur | nlock sec | luence    |      |   |                          |

| М             | OVLW      | 55h       |      | ; |                          |

| M             | OVWF      | NVMCON2   |      | ; |                          |

| M             | OVLW      | AAh       |      | ; |                          |

| М             | OVWF      | NVMCON2   |      | ; |                          |

| ; Set WR bit  | to begin  | n write   |      |   |                          |

| В             | SF        | NVMCON1,  | WR   | ; |                          |

| ; Enable INT  |           |           |      |   |                          |

| В             | SF        | INTCON0,  | GIE  | ; |                          |

| ; Wait for ir | -         | write do  | ne   |   |                          |

| -             | LEEP      |           |      | ; |                          |

| ; Disable wri | tes       |           |      |   |                          |

| B             | CF        | NVMCON1,  | WREN | ; |                          |

|               |           |           |      |   |                          |

#### 13.3.6 OPERATION DURING CODE-PROTECT

Data EEPROM Memory has its own code-protect bits in Configuration Words. External read and write operations are disabled if code protection is enabled.

If the Data EEPROM is write-protected or if NVMADR points an invalid address location, the WR bit is cleared without any effect. WRERR is signaled in this scenario.

#### 13.3.7 PROTECTION AGAINST SPURIOUS WRITE

There are conditions when the user may not want to write to the Data EEPROM Memory. To protect against spurious EEPROM writes, various mechanisms have been implemented. On power-up, the WREN bit is cleared. In addition, writes to the EEPROM are blocked during the Power-up Timer period (TPWRT).

The unlock sequence and the WREN bit together help prevent an accidental write during brown-out, power glitch or software malfunction.

## **19.5** Register Definitions: Peripheral Module Disable

| REGISTER        | 19-1: PMD                                                                                                    | 0: PMD CON                                            | ROL REGIS                       | STER 0                                         |                  |                  |              |

|-----------------|--------------------------------------------------------------------------------------------------------------|-------------------------------------------------------|---------------------------------|------------------------------------------------|------------------|------------------|--------------|

| R/W-0/0         | R/W-0/0                                                                                                      | R/W-0/0                                               | R/W-0/0                         | R/W-0/0                                        | R/W-0/0          | R/W-0/0          | R/W-0/0      |

| SYSCMD          | FVRMD                                                                                                        | HLVDMD                                                | CRCMD                           | SCANMD                                         | NVMMD            | CLKRMD           | IOCMD        |

| 7               |                                                                                                              |                                                       |                                 |                                                |                  |                  |              |

| Legend:         |                                                                                                              |                                                       |                                 |                                                |                  |                  |              |

| R = Readabl     | e bit                                                                                                        | W = Writable                                          | bit                             | U = Unimplem                                   | nented bit, read | d as '0'         |              |

| u = Bit is und  | hanged                                                                                                       | x = Bit is unkr                                       | nown                            | -n/n = Value a                                 | t POR and BO     | R/Value at all o | ther Resets  |

| '1' = Bit is se | t                                                                                                            | '0' = Bit is clea                                     | ared                            | q = Value dep                                  | ends on condi    | tion             |              |

| bit 7           | See descripti<br>1 = System o                                                                                |                                                       | 9.4 "System (<br>isabled (Fosc) | k Network bit <sup>(1)</sup><br>Clock Disable" |                  |                  |              |

| bit 6           | FVRMD: Disa                                                                                                  | able Fixed Volta<br>dule disabled                     |                                 | bit                                            |                  |                  |              |

| bit 5           | 1 = HLVD m                                                                                                   | sable High/Low<br>odule disabled<br>odule enabled     | -Voltage Deteo                  | et bit                                         |                  |                  |              |

| bit 4           | 1 = CRC mo                                                                                                   | able CRC Engined<br>Indule disabled<br>Indule enabled | ne bit                          |                                                |                  |                  |              |

| bit 3           | 1 = NVM Me                                                                                                   | isable NVM Me<br>emory Scan mo<br>emory Scan mo       | dule disabled                   | bit <sup>(2)</sup>                             |                  |                  |              |

| bit 2           | 1 = All Memo                                                                                                 | M Module Disa<br>ory reading and<br>odule enabled     |                                 | bled; NVMCON                                   | registers canr   | not be written   |              |

| bit 1           | 1 = CLKR m                                                                                                   | isable Clock Re<br>odule disabled<br>odule enabled    | ference bit                     |                                                |                  |                  |              |

| bit 0           | IOCMD: Disable Interrupt-on-Change bit, All Ports<br>1 = IOC module(s) disabled<br>0 = IOC module(s) enabled |                                                       |                                 |                                                |                  |                  |              |

|                 | learing the SYS<br>y Fosc/4 are no                                                                           |                                                       | es the system                   | clock (Fosc) to                                | peripherals, h   | owever periphe   | rals clocked |

## REGISTER 19-1: PMD0: PMD CONTROL REGISTER 0

- 2: Subject to SCANE bit in CONFIG4H.

- **3:** When enabling NVM, a delay of up to 1 µs may be required before accessing data.

| U-0   | U-0 | U-0 | U-0 | U-0 | U-0 | R/W-0/0 | R/W-0/0 |

|-------|-----|-----|-----|-----|-----|---------|---------|

| —     | —   | —   | —   | —   | —   | DMA2MD  | DMA1MD  |

| bit 7 |     |     |     |     |     |         | bit 0   |

#### REGISTER 19-8: PMD7: PMD CONTROL REGISTER 7

| Legend:              |                      |                                                       |

|----------------------|----------------------|-------------------------------------------------------|

| R = Readable bit     | W = Writable bit     | U = Unimplemented bit, read as '0'                    |

| u = Bit is unchanged | x = Bit is unknown   | -n/n = Value at POR and BOR/Value at all other Resets |

| '1' = Bit is set     | '0' = Bit is cleared | q = Value depends on condition                        |

| bit 7-2 | Unimplemented: Read as '0'                                                 |

|---------|----------------------------------------------------------------------------|

| bit 1   | DMA2MD: Disable DMA2 Module bit                                            |

|         | <ul><li>1 = DMA2 module disabled</li><li>0 = DMA2 module enabled</li></ul> |

| bit 0   | DMA1MD: Disable DMA1 Module bit                                            |

|         | 1 - DMA1 madula disabled                                                   |

1 = DMA1 module disabled 0 = DMA1 module enabled

# TABLE 19-1: SUMMARY OF REGISTERS ASSOCIATED WITH PERIPHERAL MODULE DISABLE

| Name | Bit 7  | Bit 6  | Bit 5  | Bit 4  | Bit 3  | Bit 2  | Bit 1  | Bit 0  | Register<br>on Page |

|------|--------|--------|--------|--------|--------|--------|--------|--------|---------------------|

| PMD0 | SYSCMD | FVRMD  | HLVDMD | CRCMD  | SCANMD | NVMMD  | CLKRMD | IOCMD  | 290                 |

| PMD1 | NCO1MD | TMR6MD | TMR5MD | TMR4MD | TMR3MD | TMR2MD | TMR1MD | TMR0MD | 291                 |

| PMD2 | —      | DACMD  | ADCMD  | _      | _      | CMP2MD | CMP1MD | ZCDMD  | 292                 |

| PMD3 | PWM8MD | PWM7MD | PWM6MD | PWM5MD | CCP4MD | CCP3MD | CCP2MD | CCP1MD | 293                 |

| PMD4 | CWG3MD | CWG2MD | CWG1MD | _      | _      | _      | _      | _      | 294                 |

| PMD5 | —      | _      | U2MD   | U1MD   | _      | SPI1MD | I2C2MD | I2C1MD | 295                 |

| PMD6 | —      | _      | SMT1MD | CLC4MD | CLC3MD | CLC2MD | CLC1MD | DSMMD  | 295                 |

| PMD7 | _      | _      | _      | _      | _      | _      | DMA2MD | DMA1MD | 297                 |

Legend: — = unimplemented location, read as '0'. Shaded cells are not used by peripheral module disable.

| FIGURE 21-7:   | TIMER1/3/5 GATE SING                    | GLE-PULSE AND TOGGLE COME                                             | BINED MODE                                       |

|----------------|-----------------------------------------|-----------------------------------------------------------------------|--------------------------------------------------|

| TMRxGE         |                                         |                                                                       |                                                  |

| TxGPOL         |                                         |                                                                       |                                                  |

| TxGSPM         |                                         |                                                                       |                                                  |

| TxGTM          |                                         |                                                                       |                                                  |

| TxGG <u>O/</u> | Set by software                         | •                                                                     | Cleared by hardware on<br>falling edge of TxGVAL |

| DONE           | Counting enabled o                      | on                                                                    |                                                  |

| TxG_IN         | rising edge of TxG                      |                                                                       |                                                  |

| ТхСКІ          |                                         |                                                                       |                                                  |

| TxGV <u>AL</u> |                                         |                                                                       |                                                  |

| TIMER1/3/5     | Ν                                       | $\underbrace{N+1} \underbrace{N+2} \underbrace{N+3} \underbrace{N+4}$ |                                                  |

| TMRxGIF        | <ul> <li>Cleared by software</li> </ul> | Set by hardware on<br>falling edge of TxGVAL ——▶                      | Cleared by<br>software                           |

## 21.11 Peripheral Module Disable

When a peripheral module is not used or inactive, the module can be disabled by setting the Module Disable bit in the PMD registers. This will reduce power consumption to an absolute minimum. Setting the PMD bits holds the module in Reset and disconnects the module's clock source. The Module Disable bits for Timer1 (TMR1MD), Timer3 (TMR3MD) and Timer5 (TMR5MD) are in the respective PMD registers. See **Section 19.0 "Peripheral Module Disable (PMD)"** for more information.

|                   | MODE   | <4:0> | Output                                         | Onersting                                               | Timer Control            |              |                                        |  |

|-------------------|--------|-------|------------------------------------------------|---------------------------------------------------------|--------------------------|--------------|----------------------------------------|--|

| Mode              | <4:3>  | <2:0> | Operation                                      | Operation                                               | Start                    | Reset        | Stop                                   |  |

|                   |        | 000   |                                                | Software gate (Figure 22-6)                             | <b>ON =</b> 1            | _            | <b>ON =</b> 0                          |  |

|                   |        | 001   | Period<br>Pulse                                | Hardware gate, active-high<br>(Figure 22-7)             | ON = 1 &<br>TMRx_ers = 1 | _            | ON = 0 or<br>TMRx_ers = 0              |  |

|                   |        | 010   | 1 0136                                         | Hardware gate, active-low                               | ON = 1 &<br>TMRx_ers = 0 | _            | ON = 0 or<br>TMRx_ers = 1              |  |

| Free              |        | 011   |                                                | Rising or Falling Edge Reset                            |                          | TMRx_ers     |                                        |  |

| Running<br>Period | 00     | 100   | Period                                         | Rising Edge Reset (Figure 22-8)                         |                          | TMRx_ers ↑   | <b>ON =</b> 0                          |  |

|                   |        | 101   | Pulse                                          | Falling Edge Reset                                      | ]                        | TMRx_ers ↓   |                                        |  |

|                   |        | 110   | with<br>Hardware                               | Low Level Reset                                         | <b>ON =</b> 1            | TMRx_ers = 0 | ON = 0 or<br>TMRx_ers = 0              |  |

|                   |        | 111   | Reset                                          | High Level Reset (Figure 22-9)                          |                          | TMRx_ers = 1 | ON = 0 or<br>TMRx_ers = 1              |  |

|                   |        | 000   | One-Shot                                       | Software Start (Figure 22-10)                           | <b>ON =</b> 1            | _            |                                        |  |

|                   |        | 001   | Edge                                           | Rising Edge Start (Figure 22-9)                         | ON = 1 &<br>TMRx_ers ↑   | _            |                                        |  |

|                   | 01     | 010   | Triggered<br>Start                             | Falling Edge Start                                      | ON = 1 &<br>TMRx_ers ↓   | _            |                                        |  |

|                   |        | 011   | (Note 1)                                       | Any eEdge Start                                         | ON = 1 &<br>TMRx_ers     | _            | ON = 0<br>or                           |  |

| One-shot          |        | 100   | Edge                                           | Rising Edge Start &<br>Rising Edge Reset (Figure 22-12) | ON = 1 &<br>TMRx_ers ↑   | TMRx_ers ↑   | Next clock after<br>TMRx = PRx         |  |

|                   |        | 101   | Triggered<br>Start<br>and<br>Hardware<br>Reset | Falling Edge Start &<br>Falling Edge Reset              | ON = 1 &<br>TMRx_ers ↓   | TMRx_ers ↓   | (Note 2)                               |  |

|                   |        | 110   |                                                | Rising Edge Start &<br>Low Level Reset (Figure 22-13)   | ON = 1 &<br>TMRx_ers ↑   | TMRx_ers = 0 |                                        |  |

|                   |        | 111   | (Note 1)                                       | Falling Edge Start &<br>High Level Reset                | ON = 1 &<br>TMRx_ers ↓   | TMRx_ers = 1 |                                        |  |

|                   |        | 000   |                                                | Res                                                     | erved                    |              |                                        |  |

|                   |        | 001   | Edge                                           | Rising Edge Start<br>(Figure 22-12)                     | ON = 1 &<br>TMRx_ers ↑   | —            | ON=0                                   |  |

| Monostable        |        | 010   | Triggered<br>Start                             | Falling Edge Start                                      | ON = 1 &<br>TMRx_ers ↓   | —            | or<br>Next clock after<br>TxTMR = TxPR |  |

|                   |        | 011   | (Note 1)                                       | Any Edge Start                                          | ON = 1 &<br>TMRx_ers     | _            | (Note 3)                               |  |

| Reserved          | 10     | 100   | Reserved                                       |                                                         |                          |              |                                        |  |

| Reserved          | served |       |                                                | Res                                                     | erved                    |              |                                        |  |

|                   |        | 110   | Level<br>Triggered                             | High Level Start &<br>Low Level Reset (Figure 22-13)    | ON = 1 &<br>TMRx_ers = 1 | TMRx_ers = 0 | ON = 0 or                              |  |

| One-shot          |        |       | Start<br>and                                   | Low Level Start &                                       | ON = 1 &                 |              | Held in Reset                          |  |

| One-shot          |        | 111   | Hardware<br>Reset                              | High Level Reset                                        | TMRx_ers = 0             | TMRx_ers = 1 | (Note 2)                               |  |

#### TABLE 22-1: TIMER2 OPERATING MODES

**Note 1:** If ON = 0 then an edge is required to restart the timer after ON = 1.

2: When TxTMR = TxPR then the next clock clears ON and stops TxTMR at 00h.

3: When TxTMR = TxPR then the next clock stops TxTMR at 00h but does not clear ON.

# © 2016-2017 Microchip Technology Inc.

Preliminary

| R/W-0/0                   | R/W-0/0                                               | R/W-0/0                                                                                                                                    | U-0           | R/W-0/0        | R/W-0/0          | R/W-0/0          | R/W-0/0      |  |  |  |  |

|---------------------------|-------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------|---------------|----------------|------------------|------------------|--------------|--|--|--|--|

| PWS<2:0> <sup>(1,2)</sup> |                                                       |                                                                                                                                            | _             |                | CKS              | CKS<3:0>         |              |  |  |  |  |

| bit 7                     |                                                       |                                                                                                                                            |               |                |                  |                  | bit C        |  |  |  |  |

|                           |                                                       |                                                                                                                                            |               |                |                  |                  |              |  |  |  |  |

| Legend:                   |                                                       |                                                                                                                                            |               |                |                  |                  |              |  |  |  |  |

| R = Readab                | ole bit                                               | W = Writable I                                                                                                                             | oit           | U = Unimplem   | nented bit, read | l as '0'         |              |  |  |  |  |

| u = Bit is un             | changed                                               | x = Bit is unkn                                                                                                                            | own           | -n/n = Value a | t POR and BO     | R/Value at all o | other Resets |  |  |  |  |

| '1' = Bit is se           | et                                                    | '0' = Bit is clea                                                                                                                          | ared          |                |                  |                  |              |  |  |  |  |

|                           |                                                       |                                                                                                                                            |               | (4.0)          |                  |                  |              |  |  |  |  |

| bit 7-5                   |                                                       | ICO1 Output Pi                                                                                                                             |               |                |                  |                  |              |  |  |  |  |

|                           |                                                       | 111 = NCO1 output is active for 128 input clock periods                                                                                    |               |                |                  |                  |              |  |  |  |  |

|                           |                                                       | 110 = NCO1 output is active for 64 input clock periods                                                                                     |               |                |                  |                  |              |  |  |  |  |

|                           |                                                       | <ul> <li>101 = NCO1 output is active for 32 input clock periods</li> <li>100 = NCO1 output is active for 16 input clock periods</li> </ul> |               |                |                  |                  |              |  |  |  |  |

|                           |                                                       | 011 = NCO1 output is active for 8 input clock periods                                                                                      |               |                |                  |                  |              |  |  |  |  |

|                           | 010 = NCO1 output is active for 4 input clock periods |                                                                                                                                            |               |                |                  |                  |              |  |  |  |  |

|                           | 001 = NCO1 output is active for 2 input clock periods |                                                                                                                                            |               |                |                  |                  |              |  |  |  |  |

|                           | 000 = NCO                                             | 1 output is activ                                                                                                                          | e for 1 input | clock period   |                  |                  |              |  |  |  |  |

| bit 4                     | Unimplemen                                            | ted: Read as '                                                                                                                             | )'            |                |                  |                  |              |  |  |  |  |

| bit 3-0                   | CKS<3:0>: NCO1 Clock Source Select bits               |                                                                                                                                            |               |                |                  |                  |              |  |  |  |  |

|                           | 1111 = Rese                                           | 1111 = Reserved                                                                                                                            |               |                |                  |                  |              |  |  |  |  |

|                           | •                                                     |                                                                                                                                            |               |                |                  |                  |              |  |  |  |  |

|                           | •                                                     |                                                                                                                                            |               |                |                  |                  |              |  |  |  |  |

|                           | •<br>1011 - Deee                                      | m ( a d                                                                                                                                    |               |                |                  |                  |              |  |  |  |  |

|                           |                                                       | 1011 = Reserved                                                                                                                            |               |                |                  |                  |              |  |  |  |  |

|                           |                                                       | 1010 = CLC4_out<br>1001 = CLC3 out                                                                                                         |               |                |                  |                  |              |  |  |  |  |

|                           |                                                       | $1000 = \text{CLC3_out}$                                                                                                                   |               |                |                  |                  |              |  |  |  |  |

|                           |                                                       | 0111 = CLC1  out                                                                                                                           |               |                |                  |                  |              |  |  |  |  |

|                           | 0110 = CLKREF_out                                     |                                                                                                                                            |               |                |                  |                  |              |  |  |  |  |

|                           | 0101 <b>= SOSC</b>                                    |                                                                                                                                            |               |                |                  |                  |              |  |  |  |  |

|                           |                                                       | TOSC/4 (32 kH                                                                                                                              |               |                |                  |                  |              |  |  |  |  |

|                           |                                                       | TOSC (500 kH                                                                                                                               | z)            |                |                  |                  |              |  |  |  |  |

|                           | 0010 = LFIN                                           |                                                                                                                                            |               |                |                  |                  |              |  |  |  |  |

|                           | 0001 = HFIN<br>0000 = Fosc                            |                                                                                                                                            |               |                |                  |                  |              |  |  |  |  |

- **Note 1:** N1PWS applies only when operating in Pulse Frequency mode.

- 2: If NCO1 pulse width is greater than NCO1 overflow period, operation is undefined.

# 29.0 ZERO-CROSS DETECTION (ZCD) MODULE

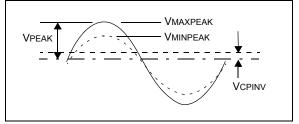

The ZCD module detects when an A/C signal crosses through the ground potential. The actual zero-crossing threshold is the zero-crossing reference voltage, VCPINV, which is typically 0.75V above ground.

The connection to the signal to be detected is through a series current-limiting resistor. The module applies a current source or sink to the ZCD pin to maintain a constant voltage on the pin, thereby preventing the pin voltage from forward biasing the ESD protection diodes. When the applied voltage is greater than the reference voltage, the module sinks current. When the applied voltage is less than the reference voltage, the module sources current. The current source and sink action keeps the pin voltage constant over the full range of the applied voltage. The ZCD module is shown in the simplified block diagram Figure 29-2.

The ZCD module is useful when monitoring an A/C waveform for, but not limited to, the following purposes:

- A/C period measurement

- Accurate long term time measurement

- Dimmer phase delayed drive

- Low EMI cycle switching

## 29.1 External Resistor Selection

The ZCD module requires a current-limiting resistor in series with the external voltage source. The impedance and rating of this resistor depends on the external source peak voltage. Select a resistor value that will drop all of the peak voltage when the current through the resistor is nominally 300  $\mu$ A. Refer to Equation 29-1 and Figure 29-1. Make sure that the ZCD I/O pin internal weak pull-up is disabled so it does not interfere with the current source and sink.

#### EQUATION 29-1: EXTERNAL RESISTOR

$$RSERIES = \frac{VPEAK}{3 \times 10^{-4}}$$

FIGURE 29-1: EXTERN

| REGISTER :       | R/W-0/0                                                                                                                                                  | N2: UART CONTE<br>R/W-0/0 R/                                | W-0/0     | R/W-0/0           | R/W-0/0            | R/W-0/0           | R/W-0/0      |  |  |  |

|------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------|-----------|-------------------|--------------------|-------------------|--------------|--|--|--|

| RUNOVF           | RXPOL                                                                                                                                                    | STP<1:0>                                                    | •• 0/0    | C0EN              | TXPOL              |                   | <1:0>        |  |  |  |

| bit 7            | 101 02                                                                                                                                                   |                                                             |           | OULIN             | 174 02             | 120               | bit (        |  |  |  |

|                  |                                                                                                                                                          |                                                             |           |                   |                    |                   |              |  |  |  |

| Legend:          |                                                                                                                                                          |                                                             |           |                   |                    |                   |              |  |  |  |

| R = Readable     |                                                                                                                                                          | W = Writable bit                                            |           |                   | nented bit, read   |                   |              |  |  |  |

| u = Bit is uncl  | •                                                                                                                                                        | x = Bit is unknown                                          |           | -n/n = Value a    | at POR and BO      | R/Value at all o  | other Resets |  |  |  |

| '1' = Bit is set |                                                                                                                                                          | '0' = Bit is cleared                                        |           |                   |                    |                   |              |  |  |  |

| bit 7            |                                                                                                                                                          | In During Overflow C                                        | `ontrol h | it                |                    |                   |              |  |  |  |

|                  |                                                                                                                                                          | shifter continues to                                        |           |                   | hits after overflo | w condition       |              |  |  |  |

|                  |                                                                                                                                                          | shifter stops all activ                                     |           |                   |                    |                   |              |  |  |  |

| bit 6            | RXPOL: Rec                                                                                                                                               | eive Polarity Control                                       | bit       |                   |                    |                   |              |  |  |  |

|                  | 1 = Invert RX polarity, Idle state is low                                                                                                                |                                                             |           |                   |                    |                   |              |  |  |  |

|                  | -                                                                                                                                                        | ity is not inverted, Id                                     |           | s high            |                    |                   |              |  |  |  |

| bit 5-4          | <b>STP&lt;1:0&gt;:</b> Stop Bit Mode Control bits <sup>(1)</sup><br>11 = Transmit 2 Stop bits, receiver verifies first Stop bit                          |                                                             |           |                   |                    |                   |              |  |  |  |

|                  | 10 = Transmit 2 Stop bits, receiver verifies first Stop bit<br>10 = Transmit 2 Stop bits, receiver verifies first and second Stop bits                   |                                                             |           |                   |                    |                   |              |  |  |  |

|                  | 01 = Transmit 1.5 Stop bits, receiver verifies first Stop bit                                                                                            |                                                             |           |                   |                    |                   |              |  |  |  |

|                  |                                                                                                                                                          | nit 1 Stop bit, receive                                     |           | s first Stop bit  |                    |                   |              |  |  |  |

| bit 3            | COEN: Check                                                                                                                                              | C0EN: Checksum Mode Select bit <sup>(2)</sup>               |           |                   |                    |                   |              |  |  |  |

|                  | LIN mode:                                                                                                                                                |                                                             |           |                   |                    |                   |              |  |  |  |

|                  | <ol> <li>Checksum Mode 1, enhanced LIN checksum includes PID in sum</li> <li>Checksum Mode 0, legacy LIN checksum does not include PID in sum</li> </ol> |                                                             |           |                   |                    |                   |              |  |  |  |

|                  | 0 - Checksum mode 0, legacy Lin checksum does not include PID in sum                                                                                     |                                                             |           |                   |                    |                   |              |  |  |  |

|                  | 1 = Add all TX and RX characters                                                                                                                         |                                                             |           |                   |                    |                   |              |  |  |  |

|                  | 0 = Checksums disabled                                                                                                                                   |                                                             |           |                   |                    |                   |              |  |  |  |

| bit 2            | TXPOL: Transmit Polarity Control bit                                                                                                                     |                                                             |           |                   |                    |                   |              |  |  |  |

|                  |                                                                                                                                                          | 1 = Output data is inverted, TX output is low in Idle state |           |                   |                    |                   |              |  |  |  |

|                  | -                                                                                                                                                        | ata is not inverted, T                                      | -         | t is high in Idle | state              |                   |              |  |  |  |

| bit 1-0          |                                                                                                                                                          | landshake Flow Cont                                         | trol bits |                   |                    |                   |              |  |  |  |

|                  | $11 = \frac{\text{Reserv}}{\text{RTS/C}}$                                                                                                                | ved<br>CTS and TXDE Hardv                                   | ware flow | v control         |                    |                   |              |  |  |  |

|                  |                                                                                                                                                          | OFF Software flow                                           |           | Veontion          |                    |                   |              |  |  |  |

|                  | 00 = Flow c                                                                                                                                              | ontrol is off                                               |           |                   |                    |                   |              |  |  |  |

| Note 1: All      | modes transmit                                                                                                                                           | t selected number of                                        | Stop bit  | s. Only DMX a     | nd DALI receive    | ers verify select | ted number o |  |  |  |

|                  |                                                                                                                                                          | thers verify only the f                                     |           |                   |                    | -                 |              |  |  |  |

|                  |                                                                                                                                                          |                                                             |           |                   |                    |                   |              |  |  |  |

## REGISTER 31-3: UxCON2: UART CONTROL REGISTER 2

2: UART1 only.

# 33.5 I<sup>2</sup>C Master Mode

Master mode is enabled by setting and clearing the appropriate Mode<2:0> bits in I2CxCON and then by setting the I2CEN bit. Master mode of operation is supported by interrupt generation on buffer full (RXIF), buffer empty (TXIF), and the detection of the Start, Restart, and Stop conditions. The Stop (P), Restart (RS) and Start (S) bits are cleared from a Reset or when the I<sup>2</sup>C module is disabled. Control of the I<sup>2</sup>C bus is asserted when the BFRE bit of I2CSTAT0 is set.

#### 33.5.1 I<sup>2</sup>C MASTER MODE OPERATION

The master device generates all of the serial clock pulses and the Start, Restart, and Stop conditions. A transfer is ended with a Stop condition or with a Restart condition. Since the Repeated Start condition is also the beginning of the next serial transfer, the I<sup>2</sup>C bus will not be released, and MMA bit will stay set signifying that the Master module is still active.

The steps to initiate a transaction depends on the setting of the address buffer disable bit (ABD) of the I2CxCON2 register.

• ABD = 0 (Address buffers are enabled)

In this case, the master module will use the address stored in the address buffer registers (I2CxADB0/1) to initiate communication with a slave device. User software needs to set the Start bit (S) in the I2CxCON0 register to start communication. This is valid for both 7-bit and 10-bit Addressing modes.

• ABD = 1 (Address buffers are disabled)

In this case, the slave address is transmitted through the transmit buffer and the contents of the address buffers are ignored. User software needs to write the slave address to the transmit buffer (I2CxTXB) to initiate communication. Writing to the Start bit is ignored in this mode. This is valid for both 7-bit and 10bit Addressing modes.

#### 33.5.1.1 Master Transmitter

In Master Transmitter mode, the first byte transmitted contains the slave address of the receiving device (7 bits) and the Read/Write (R/W) bit. In the case of master transmitter, the R/W bit will be logic '0'. Serial data is transmitted eight bits at a time. After each byte is transmitted, an Acknowledge bit is received. Start and Stop conditions are output to indicate the beginning and the end of a serial transfer.

#### 33.5.1.2 Master Receiver

In Master Receive mode, the first byte transmitted contains the slave address of the transmitting device (7 bits) and the R/W bit. In this case, the R/W bit will be logic '1'. Thus, the first byte transmitted is a 7-bit slave address followed by a '1' to indicate the receive bit. Serial data is received via SDA, while SCL outputs the serial clock. Serial data is received eight bits at a time.

After each byte is received, an Acknowledge bit is transmitted. Start and Stop conditions indicate the beginning and end of the transmission.

# 33.5.2 MASTER CLOCK SOURCE AND ARBITRATION

The  $I^2C$  module clock source is selected by the I2CxCLK register. The  $I^2C$  Clock provides the SCL output clock for Master mode and is used by the Bus Free timer. The  $I^2C$  clock can be sourced from several peripherals.

#### 33.5.3 BUS FREE TIME

In Master modes, the BFRE bit of the I2CxSTAT0 register gives an indication of the bus idle status. The master hardware cannot assert a Start condition until this bit is set by the hardware. This prevents the master from colliding with other masters that may already be talking on the bus. The BFRET<1:0> bits of I2CxCON1 allow selection of 8 to 64 pulses of the I<sup>2</sup>C clock input before asserting the BFRE bit. The BFRET bits are used to ensure that the I<sup>2</sup>C module always follows the minimum Stop Hold Time. The I<sup>2</sup>C timing requirements are listed in the electrical specifications chapter.

| Note: | I <sup>2</sup> C clock is not required to have a 50% |

|-------|------------------------------------------------------|

|       | duty cycle.                                          |

## 33.5.4 MASTER CLOCK TIMING

The clock generation in the  $l^2C$  module can be configured using the Fast Mode Enable (FME) bit of the l2CxCON2 register. This bit controls the number of times the SCL pin is sampled before the master hardware drives it.

#### 33.5.4.1 Clock Timing with FME = 0

One Tscl, consists of five clocks of the  $I^2C$  clock input. The first clock is used to drive SCL low, the third releases SCL high. The fourth and fifth clocks are used to detect if the SCL pin is, in fact, high or being stretched by a slave.

If a slave is clock stretching, the hardware waits; checking SCL on each successive  $I^2C$  clock, proceeding only after detecting SCL high. Figure 33-13 shows the clock synthesis timing when FME = 0.

#### 33.5.11 MASTER TRANSMISSION IN 10-BIT ADDRESSING MODE

This section describes the sequence of events for the  $I^2C$  module configured as an  $I^2C$  master in 10-bit Addressing mode and is transmitting data. Figure 33-21 is used as a visual reference for this description

1. If ABD = 0; i.e., Address buffers are enabled

Master software loads number of bytes to be transmitted in one sequence in I2CxCNT, high address byte of slave address in I2CxADB1 with R/W = 0, low address byte in I2CxADB0 and the first byte of data in I2CxTXB. Master software has to set the Start (S) bit to initiate communication.

If ABD = 1; i.e., Address buffers are disabled

Master software loads the number of bytes to be transmitted in one sequence in I2CxCNT and the high address byte of the slave address with R/W = 0 into the I2CxTXB register. Writing to the I2CxTXB will assert the start condition on the bus and sets the S bit. Software writes to the S bit are ignored in this case.

- 2. Master hardware waits for BFRE bit to be set; then shifts out the start and high address and waits for acknowledge.

- 3. If NACK, master hardware sends Stop.

- 4. If ABD = 0; i.e., Address buffer are enabled

If ACK, master hardware sends the low address byte from I2CxADB0.

If ABD = 1; i.e., Address buffer are disabled

If ACK, master hardware sets TXIF and MDR bits and the software has to write the low address byte into I2CxTXB. Writing to I2CxTXB sends the low address on the bus.

- If TXBE = 1 and I2CxCNT! = 0, I2CxTXIF and MDR bits are set. Clock is stretched on 8th falling SCL edge until master software writes next data byte to I2CxTXB.

- Master hardware sends ninth SCL pulse for ACK from slave and loads the shift register from I2CxTXB. I2CxCNT is decremented.

- 7. If slave sends a NACK, master hardware sends Stop and ends transmission.

- If slave sends an ACK, master hardware outputs data in the shift register on SDA. I2CxCNT value is checked on the 8th falling SCL edge. If I2CxCNT = 0; master hardware sends 9th SCL pulse for ACK and CNTIF is set.

- 9. If I2CxCNT! = 0; go to step 5.

## 39.10 Register Definitions: HLVD Control

Long bit name prefixes for the HLVD peripheral is shown in Table 39-1. Refer to **Section 1.3.2.2 "Long Bit Names"** for more information.

#### TABLE 39-1:

| Peripheral | Bit Name Prefix |  |  |  |  |

|------------|-----------------|--|--|--|--|

| HLVD       | HLVD            |  |  |  |  |

#### REGISTER 39-1: HLVDCON0: HIGH/LOW-VOLTAGE DETECT CONTROL REGISTER 0

| R/W-0/0 | U-0 | R-x | R-x | U-0 | U-0 | R/W-0/0 | R/W-0/0 |

|---------|-----|-----|-----|-----|-----|---------|---------|

| EN      | _   | OUT | RDY | —   | —   | INTH    | INTL    |

| bit 7   |     |     |     |     |     |         | bit 0   |

|         |     |     |     |     |     |         |         |

| Legend: |     |     |     |     |     |         |         |

| Legena.           |                  |                       |                    |

|-------------------|------------------|-----------------------|--------------------|

| R = Readable bit  | W = Writable bit | U = Unimplemented bit | , read as '0'      |

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared  | x = Bit is unknown |

| bit 7   | <ul> <li>EN: High/Low-voltage Detect Power Enable bit</li> <li>1 = Enables HLVD, powers up HLVD circuit and supporting reference circuitry</li> <li>0 = Disables HLVD, powers down HLVD and supporting circuitry</li> </ul> |

|---------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| bit 6   | Unimplemented: Read as '0'                                                                                                                                                                                                  |

| bit 5   | OUT: HLVD Comparator Output bit                                                                                                                                                                                             |

|         | <ul> <li>1 = Voltage ≤ selected detection limit (HLVDL&lt;3:0&gt;)</li> <li>0 = Voltage ≥ selected detection limit (HLVDL&lt;3:0&gt;)</li> </ul>                                                                            |

| bit 4   | RDY: Band Gap Reference Voltages Stable Status Flag bit                                                                                                                                                                     |

|         | <ul> <li>1 = Indicates HLVD Module is ready and output is stable</li> <li>0 = Indicates HLVD Module is not ready</li> </ul>                                                                                                 |

| bit 3-2 | Unimplemented: Read as '0'                                                                                                                                                                                                  |

| bit 1   | INTH: HLVD Positive going (High Voltage) Interrupt Enable                                                                                                                                                                   |

|         | <ul> <li>1 = HLVDIF will be set when voltage ≥ selected detection limit (SEL&lt;3:0&gt;)</li> <li>0 = HLVDIF will not be set</li> </ul>                                                                                     |

| bit 0   | INTL: HLVD Negative going (Low Voltage) Interrupt Enable                                                                                                                                                                    |

|         | <ul> <li>1 = HLVDIF will be set when voltage ≤ selected detection limit (SEL&lt;3:0&gt;)</li> <li>0 = HLVDIF will not be set</li> </ul>                                                                                     |

| ADDWFC                                                                        | ADD W and CARRY bit to f                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |  |  |  |  |  |

|-------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|--|

| Syntax:                                                                       | ADDWFC f {,d {,a}}                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |  |  |  |  |  |

| Operands:                                                                     | $0 \le f \le 255$<br>$d \in [0,1]$<br>$a \in [0,1]$                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |  |  |  |  |  |

| Operation:                                                                    | $(W) + (f) + (C) \rightarrow dest$                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |  |  |  |  |  |

| Status Affected:                                                              | N,OV, C, DC, Z                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |  |  |  |  |  |

| Encoding:                                                                     | 0010 00da ffff ffff                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |  |  |  |  |  |

|                                                                               | ory location 'f'. If 'd' is '0', the result is<br>placed in W. If 'd' is '1', the result is<br>placed in data memory location 'f'.<br>If 'a' is '0', the Access Bank is selected.<br>If 'a' is '1', the BSR is used to select the<br>GPR bank.<br>If 'a' is '0' and the extended instruction<br>set is enabled, this instruction operates<br>in Indexed Literal Offset Addressing<br>mode whenever $f \le 95$ (5Fh). See Sec-<br>tion 41.2.3 "Byte-Oriented and Bit-<br>Oriented Instructions in Indexed Lit-<br>eral Offset Mode" for details. |  |  |  |  |  |

| Words:                                                                        | 1                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |  |  |  |  |  |

| Cycles:                                                                       | 1                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |  |  |  |  |  |