Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

### Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Details                    |                                                                             |

|----------------------------|-----------------------------------------------------------------------------|

| Product Status             | Active                                                                      |

| Core Processor             | PIC                                                                         |

| Core Size                  | 8-Bit                                                                       |

| Speed                      | 64MHz                                                                       |

| Connectivity               | I <sup>2</sup> C, LINbus, SPI, UART/USART                                   |

| Peripherals                | Brown-out Detect/Reset, DMA, HLVD, POR, PWM, WDT                            |

| Number of I/O              | 36                                                                          |

| Program Memory Size        | 64KB (32K x 16)                                                             |

| Program Memory Type        | FLASH                                                                       |

| EEPROM Size                | 1K x 8                                                                      |

| RAM Size                   | 4K x 8                                                                      |

| Voltage - Supply (Vcc/Vdd) | 1.8V ~ 3.6V                                                                 |

| Data Converters            | A/D 35x12b; D/A 1x5b                                                        |

| Oscillator Type            | Internal                                                                    |

| Operating Temperature      | -40°C ~ 125°C (TA)                                                          |

| Mounting Type              | Surface Mount                                                               |

| Package / Case             | 44-VQFN Exposed Pad                                                         |

| Supplier Device Package    | 44-QFN (8x8)                                                                |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/pic18lf46k42-e-ml |

|                            |                                                                             |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

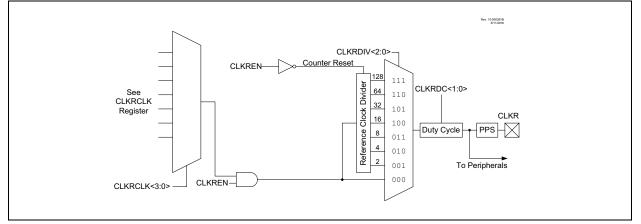

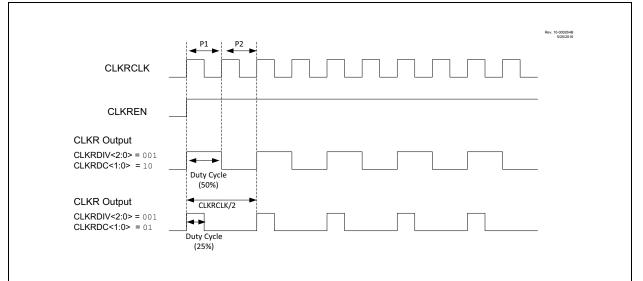

## 8.0 REFERENCE CLOCK OUTPUT MODULE

The reference clock output module provides the ability to send a clock signal to the clock reference output pin (CLKR). The reference clock output can also be used as a signal for other peripherals, such as the Data Signal Modulator (DSM), Memory Scanner and Timer module.

The reference clock output module has the following features:

- Selectable clock source using the CLKRCLK register

- Programmable clock divider

- · Selectable duty cycle

| R/W-0/0          | R/W-0/0                                         | R/W-0/0           | R/W-0/0        | R/W-0/0        | R/W-0/0          | R/W-0/0          | R/W-0/0      |

|------------------|-------------------------------------------------|-------------------|----------------|----------------|------------------|------------------|--------------|

| TMR0IE           | U1IE                                            | U1EIE             | U1TXIE         | U1RXIE         | I2C1EIE          | I2C1IE           | I2C1TXIE     |

| bit 7            |                                                 |                   |                |                |                  |                  | bit (        |

|                  |                                                 |                   |                |                |                  |                  |              |

| Legend:          |                                                 |                   |                |                |                  |                  |              |

| R = Readable     |                                                 | W = Writable      |                | •              | mented bit, read |                  |              |

| u = Bit is unch  | anged                                           | x = Bit is unkr   |                | -n/n = Value a | at POR and BO    | R/Value at all c | other Resets |

| '1' = Bit is set |                                                 | '0' = Bit is clea | ared           |                |                  |                  |              |

| bit 7            | TMROIF                                          | R0 Interrupt En   | able bit       |                |                  |                  |              |

|                  | 1 = Enabled<br>0 = Disabled                     |                   |                |                |                  |                  |              |

| bit 6            | U1IE: UART1                                     | Interrupt Enab    | ole bit        |                |                  |                  |              |

|                  | 1 = Enabled                                     |                   |                |                |                  |                  |              |

|                  | 0 = Disabled                                    |                   |                |                |                  |                  |              |

| bit 5            | U1EIE: UART1 Framing Error Interrupt Enable bit |                   |                |                |                  |                  |              |

|                  | 1 = Enabled<br>0 = Disabled                     |                   |                |                |                  |                  |              |

| bit 4            |                                                 | RT1 Transmit In   | terrupt Enabl  | e bit          |                  |                  |              |

|                  | 1 = Enabled                                     |                   |                |                |                  |                  |              |

|                  | 0 = Disabled                                    |                   |                |                |                  |                  |              |

| bit 3            |                                                 | RT1 Receive In    | terrupt Enable | e bit          |                  |                  |              |

|                  | 1 = Enabled<br>0 = Disabled                     |                   |                |                |                  |                  |              |

| bit 2            |                                                 | 1 Error Interrup  | t Enable bit   |                |                  |                  |              |

|                  | 1 = Enabled                                     |                   |                |                |                  |                  |              |

|                  | 0 = Disabled                                    |                   |                |                |                  |                  |              |

| bit 1            | <b>I2C1IE:</b> I <sup>2</sup> C1                | Interrupt Enabl   | e bit          |                |                  |                  |              |

|                  | 1 = Enabled                                     |                   |                |                |                  |                  |              |

|                  | 0 = Disabled                                    |                   |                |                |                  |                  |              |

| bit 0            |                                                 | C1 Transmit Int   | errupt Enable  | bit            |                  |                  |              |

|                  | 1 = Enabled                                     |                   |                |                |                  |                  |              |

## REGISTER 9-17: PIE3: PERIPHERAL INTERRUPT ENABLE REGISTER 3

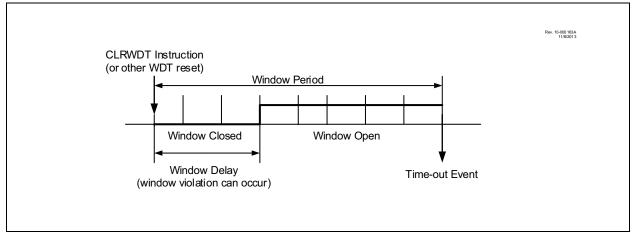

## 11.6 Operation During Sleep

When the device enters Sleep, the WWDT is cleared. If the WWDT is enabled during Sleep, the WWDT resumes counting. When the device exits Sleep, the WWDT is cleared again.

The WWDT remains clear until the Oscillator Start-up Timer (OST) completes, if enabled. See **Section 7.2.1.3 "Oscillator Start-up Timer (OST)**" for more information on the OST.

When a WWDT time-out occurs while the device is in Sleep, no Reset is generated. Instead, the device wakes up and resumes operation. The  $\overline{TO}$  and  $\overline{PD}$  bits in the STATUS register are changed to indicate the event. The RWDT bit in the PCON0 register can also be used. See Section 4.0 "Memory Organization" for more information.

### TABLE 11-2: WWDT CLEARING CONDITIONS

| Conditions                                              | WWDT                         |

|---------------------------------------------------------|------------------------------|

| WDTE<1:0> = 00                                          |                              |

| WDTE<1:0> = 01 and SEN = 0                              |                              |

| WDTE<1:0> = 10 and enter Sleep                          | Cleared                      |

| CLRWDT Command                                          | Cleared                      |

| Oscillator Fail Detected                                |                              |

| Exit Sleep + System Clock = SOSC, EXTRC, INTOSC, EXTCLK |                              |

| Exit Sleep + System Clock = XT, HS, LP                  | Cleared until the end of OST |

| Change INTOSC divider (IRCF bits)                       | Unaffected                   |

## FIGURE 11-2: WINDOW PERIOD AND DELAY

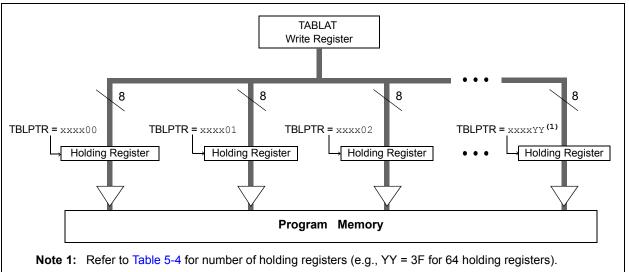

### FIGURE 13-8: TABLE WRITES TO PROGRAM FLASH MEMORY

## 13.1.6.1 Program Flash Memory Write Sequence

The sequence of events for programming an internal program memory location should be:

- 1. Read appropriate number of bytes into RAM. Refer to Table 5-4 for Write latch size.

- 2. Update data values in RAM as necessary.

- 3. Load Table Pointer register with address being erased.

- 4. Execute the block erase procedure.

- 5. Load Table Pointer register with address of first byte being written.

- 6. Write the n-byte block into the holding registers with auto-increment. Refer to Table 5-4 for Write latch size.

- 7. Set REG<1:0> bits to point to program memory.

- 8. Clear FREE bit and set WREN bit in NVMCON1 register.

- 9. Disable interrupts.

- 10. Execute the unlock sequence (see Section 13.1.4 "NVM Unlock Sequence").

- 11. WR bit is set in NVMCON1 register.

- 12. The CPU will stall for the duration of the write (about 2 ms using internal timer).

- 13. Re-enable interrupts.

- 14. Verify the memory (table read).

This procedure will require about 6 ms to update each write block of memory. An example of the required code is given in Example 13-4.

**Note:** Before setting the WR bit, the Table Pointer address needs to be within the intended address range of the bytes in the holding registers.

## **REGISTER 14-3:** CRCDATH: CRC DATA HIGH BYTE REGISTER

| R/W-xx          | R/W-x/x | R/W-x/x         | R/W-x/x | R/W-x/x        | R/W-x/x          | R/W-x/x          | R/W-x/x     |

|-----------------|---------|-----------------|---------|----------------|------------------|------------------|-------------|

|                 |         |                 | DATA    | <15:8>         |                  |                  |             |

| bit 7           |         |                 |         |                |                  |                  | bit 0       |

|                 |         |                 |         |                |                  |                  |             |

| Legend:         |         |                 |         |                |                  |                  |             |

| R = Readable    | bit     | W = Writable    | bit     | U = Unimpler   | nented bit, read | as '0'           |             |

| u = Bit is unch | anged   | x = Bit is unkr | nown    | -n/n = Value a | at POR and BO    | R/Value at all o | ther Resets |

bit 7-0 DATA<15:8>: CRC Input/Output Data bits

'1' = Bit is set

## REGISTER 14-4: CRCDATL: CRC DATA LOW BYTE REGISTER

'0' = Bit is cleared

| R/W-xx | R/W-x/x |

|--------|---------|---------|---------|---------|---------|---------|---------|

|        |         |         | DATA    | <7:0>   |         |         |         |

| bit 7  | bit 7   |         |         |         |         |         | bit 0   |

| Legend:              |                      |                                                       |

|----------------------|----------------------|-------------------------------------------------------|

| R = Readable bit     | W = Writable bit     | U = Unimplemented bit, read as '0'                    |

| u = Bit is unchanged | x = Bit is unknown   | -n/n = Value at POR and BOR/Value at all other Resets |

| '1' = Bit is set     | '0' = Bit is cleared |                                                       |

bit 7-0 **DATA<7:0>**: CRC Input/Output Data bits Writing to this register fills the shifter.

## REGISTER 14-5: CRCACCH: CRC ACCUMULATOR HIGH BYTE REGISTER

| R/W-0/0 |

|---------|---------|---------|---------|---------|---------|---------|---------|

|         |         |         | ACC<    | :15:8>  |         |         |         |

| bit 7   |         |         |         |         |         |         |         |

| Legend:              |                      |                                                       |

|----------------------|----------------------|-------------------------------------------------------|

| R = Readable bit     | W = Writable bit     | U = Unimplemented bit, read as '0'                    |

| u = Bit is unchanged | x = Bit is unknown   | -n/n = Value at POR and BOR/Value at all other Resets |

| '1' = Bit is set     | '0' = Bit is cleared |                                                       |

bit 7-0 ACC<15:8>: CRC Accumulator Register bits

## 15.0 DIRECT MEMORY ACCESS (DMA)

## 15.1 Introduction

The Direct Memory Access (DMA) module is designed to service data transfers between different memory regions directly without intervention from the CPU. By eliminating the need for CPU-intensive management of handling interrupts intended for data transfers, the CPU now can spend more time on other tasks.

PIC18(L)F26/27/45/46/47/55/56/57K42 family has two DMA modules which can be independently programmed to transfer data between different memory locations, move different data sizes, and use a wide range of hardware triggers to initiate transfers. The two DMA registers can even be programmed to work together, in order to carry out more complex data transfers without CPU overhead.

Key features of the DMA module include:

- Support access to the following memory regions:

- GPR and SFR space (R/W)

- Program Flash Memory (R only)

- Data EEPROM Memory (R only)

- Programmable priority between the DMA and CPU Operations. Refer to Section 3.1 "System Arbitration" for details.

- Programmable Source and Destination address

modes

- Fixed address

- Post-increment address

- Post-decrement address

- Programmable Source and Destination sizes

- Source and destination pointer register, dynamically updated and reloadable

- Source and destination count register, dynamically updated and reloadable

- Programmable auto-stop based on Source or Destination counter

- · Software triggered transfers

- Multiple user selectable sources for hardware triggered transfers

- Multiple user selectable sources for aborting DMA transfers

## 15.2 DMA Registers

The operation of the DMA module has the following registers:

- Control registers (DMAxCON0, DMAxCON1)

- Data buffer register (DMAxBUF)

- Source Start Address Register (DMAxSSAU:H:L)

- Source Pointer Register (DMAxSPTRU:H:L)

- · Source Message Size Register (DMAxSSZH:L)

- Source Count Register (DMAxSCNTH:L)

- Destination Start Address Register (DMAxDSAH:L)

- Destination Pointer Register (DMAxDPTRH:L)

- Destination Message Size Register (DMAxDSZH:L)

- Destination Count Register (DMAxDCNTH:L)

- Start Interrupt Request Source Register (DMAxSIRQ)

- Abort Interrupt Request Source Register (DMAxAIRQ)

These registers are detailed in Section 15.13 "Register definitions: DMA".

| U-0                                                                            | U-0                        | R/W-0/0                      | R/W-0/0 | U-0            | R/W-0/0          | R/W-0/0          | R/W-0/0      |

|--------------------------------------------------------------------------------|----------------------------|------------------------------|---------|----------------|------------------|------------------|--------------|

| —                                                                              | —                          | U2MD                         | U1MD    | —              | SPI1MD           | I2C2MD           | I2C1MD       |

| bit 7                                                                          |                            |                              |         |                |                  |                  | bit 0        |

|                                                                                |                            |                              |         |                |                  |                  |              |

| Legend:                                                                        |                            |                              |         |                |                  |                  |              |

| R = Reada                                                                      | ble bit                    | W = Writable                 | bit     | U = Unimplen   | nented bit, read | as '0'           |              |

| u = Bit is u                                                                   | nchanged                   | x = Bit is unkn              | iown    | -n/n = Value a | t POR and BOF    | R/Value at all o | other Resets |

| '1' = Bit is :                                                                 | set                        | '0' = Bit is clea            | ared    | q = Value dep  | ends on conditi  | on               |              |

|                                                                                |                            |                              |         |                |                  |                  |              |

| bit 7-6                                                                        | Unimpleme                  | nted: Read as '0             | )'      |                |                  |                  |              |

| bit 5                                                                          | U2MD: Disa                 | ble UART2 bit                |         |                |                  |                  |              |

|                                                                                |                            | module disabled              |         |                |                  |                  |              |

|                                                                                | 0 = UART2                  | module enabled               |         |                |                  |                  |              |

| bit 4                                                                          |                            | ble UART1 bit                |         |                |                  |                  |              |

|                                                                                | -                          | module disabled              |         |                |                  |                  |              |

| L:1 0                                                                          |                            | module enabled               |         |                |                  |                  |              |

| bit 3                                                                          | Unimplemented: Read as '0' |                              |         |                |                  |                  |              |

| bit 2                                                                          |                            | sable SPI1 Modu              | ile bit |                |                  |                  |              |

|                                                                                | -                          | odule disabled               |         |                |                  |                  |              |

|                                                                                | 0 = SPI1 module enabled    |                              |         |                |                  |                  |              |

| bit 1 <b>I2C2MD:</b> Disable $I^2C2$ Module bit<br>1 = $I^2C2$ module disabled |                            |                              |         |                |                  |                  |              |

|                                                                                | -                          | odule disabled               |         |                |                  |                  |              |

|                                                                                |                            |                              |         |                |                  |                  |              |

| bit 0                                                                          | -                          | sable I <sup>2</sup> C1 Modu | le bit  |                |                  |                  |              |

|                                                                                |                            | odule disabled               |         |                |                  |                  |              |

|                                                                                | 0 = 1 - 0.1  m             | odule enabled                |         |                |                  |                  |              |

## REGISTER 19-6: PMD5: PMD CONTROL REGISTER 5

| O-0         O-0         R/W-0/0         R/W-0/0         R/W-0/0         R/W-0/0           —         —         —         RSEL<4:0>         bit 7         bit |

|-------------------------------------------------------------------------------------------------------------------------------------------------------------|

| RSEL<4:0>                                                                                                                                                   |

|                                                                                                                                                             |

|                                                                                                                                                             |

| U-0 U-0 U-0 R/W-0/0 R/W-0/0 R/W-0/0 R/W-0/0 R/W-0/0                                                                                                         |

## REGISTER 22-2: TxRST: TIMER2 EXTERNAL RESET SIGNAL SELECTION REGISTER

| Legend:              |                      |                                                       |

|----------------------|----------------------|-------------------------------------------------------|

| R = Readable bit     | W = Writable bit     | U = Unimplemented bit, read as '0'                    |

| u = Bit is unchanged | x = Bit is unknown   | -n/n = Value at POR and BOR/Value at all other Resets |

| '1' = Bit is set     | '0' = Bit is cleared |                                                       |

### bit 7-5 Unimplemented: Read as '0'

bit 4-0 RSEL<4:0>: Timer2 External Reset Signal Source Selection bits

| RSEL<4:0>   | T2TMR                   | TMR4                    | TMR6                    |  |

|-------------|-------------------------|-------------------------|-------------------------|--|

| R5EL<4:0>   | Reset Source            | Reset Source            | Reset Source            |  |

| 11111-11001 | Reserved                | Reserved                | Reserved                |  |

| 11000       | UART2_tx_edge           | UART2_tx_edge           | UART2_tx_edge           |  |

| 10111       | UART2_rx_edge           | UART2_rx_edge           | UART2_rx_edge           |  |

| 10110       | UART1_tx_edge           | UART1_tx_edge           | UART1_tx_edge           |  |

| 10101       | UART1_rx_edge           | UART1_rx_edge           | UART1_rx_edge           |  |

| 10100       | CLC4_out                | CLC4_out                | CLC4_out                |  |

| 10011       | CLC3_out                | CLC3_out                | CLC3_out                |  |

| 10010       | CLC2_out                | CLC2_out                | CLC2_out                |  |

| 10001       | CLC1_out                | CLC1_out                | CLC1_out                |  |

| 10000       | ZCD_OUT                 | ZCD_OUT                 | ZCD_OUT                 |  |

| 01111       | CMP2OUT                 | CMP2OUT                 | CMP2OUT                 |  |

| 01110       | CMP1OUT                 | CMP1OUT                 | CMP1OUT                 |  |

| 01101-01100 | Reserved                | Reserved                | Reserved                |  |

| 01011       | PWM8OUT                 | PWM8OUT                 | PWM8OUT                 |  |

| 01010       | PWM7OUT                 | PWM7OUT                 | PWM7OUT                 |  |

| 01001       | PWM6OUT                 | PWM6OUT                 | PWM6OUT                 |  |

| 01000       | PWM5OUT                 | PWM5OUT                 | PWM5OUT                 |  |

| 00111       | CCP4OUT                 | CCP4OUT                 | CCP4OUT                 |  |

| 00110       | CCP3OUT                 | CCP3OUT                 | CCP3OUT                 |  |

| 00101       | CCP2OUT                 | CCP2OUT                 | CCP2OUT                 |  |

| 00100       | CCP1OUT                 | CCP1OUT                 | CCP10UT                 |  |

| 00011       | TMR6 postscaled         | TMR6 postscaled         | Reserved                |  |

| 00010       | TMR4 postscaled         | Reserved                | TMR4 postscaled         |  |

| 00001       | Reserved                | T2TMR postscaled        | T2TMR postscaled        |  |

| 00000       | Pin selected by T2INPPS | Pin selected by T4INPPS | Pin selected by T6INPPS |  |

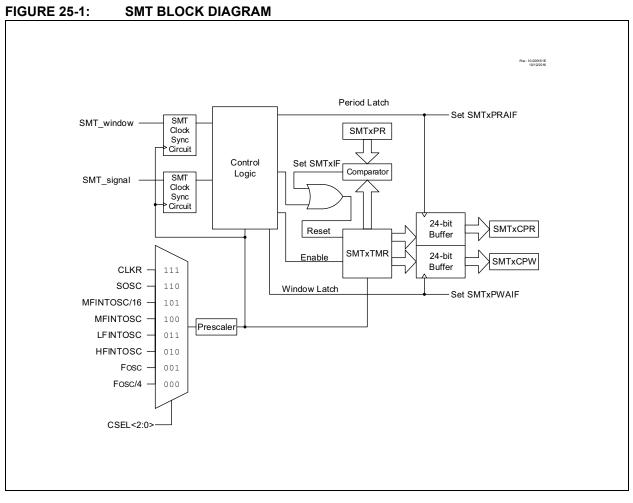

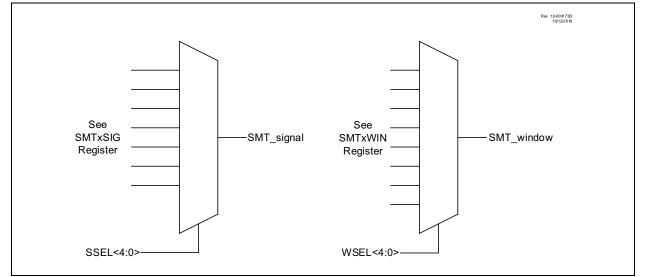

## 25.0 SIGNAL MEASUREMENT TIMER (SMT)

The SMT is a 24-bit counter with advanced clock and gating logic, which can be configured for measuring a variety of digital signal parameters such as pulse width, frequency and duty cycle, and the time difference between edges on two signals. The device has only one SMT module implemented.

Features of the SMT include:

- 24-bit timer/counter

- Three 8-bit registers (SMT1L/H/U)

- Readable and writable

- Optional 16-bit operating mode

- Two 24-bit measurement capture registers

- · One 24-bit period match register

- Multi-mode operation, including relative timing measurement

- · Interrupt on period match

- Multiple clock, gate and signal sources

- · Interrupt on acquisition complete

- · Ability to read current input values

© 2017 Microchip Technology Inc.

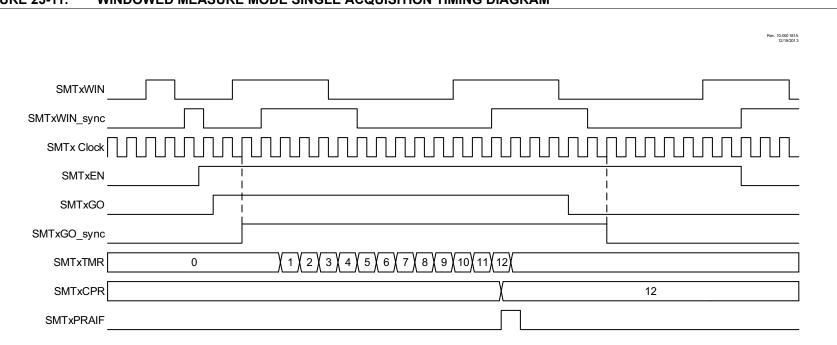

## FIGURE 25-11: WINDOWED MEASURE MODE SINGLE ACQUISITION TIMING DIAGRAM

PIC18(L)F26/27/45/46/47/55/56/57K42

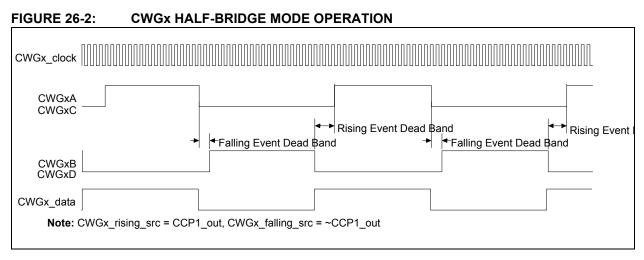

### 26.2.2 PUSH-PULL MODE

In Push-Pull mode, two output signals are generated, alternating copies of the input as illustrated in Figure 26-4. This alternation creates the push-pull effect required for driving some transformer-based power supply designs. Steering modes are not used in Push-Pull mode. A basic block diagram for the Push-Pull mode is shown in Figure 26-3.

The push-pull sequencer is reset whenever EN = 0 or if an auto-shutdown event occurs. The sequencer is clocked by the first input pulse, and the first output appears on CWGxA.

The unused outputs CWGxC and CWGxD drive copies of CWGxA and CWGxB, respectively, but with polarity controlled by the POLC and POLD bits of the CWGxCON1 register, respectively.

## 31.3 Asynchronous Address Mode

A special Address Detection mode is available for use when multiple receivers share the same transmission line, such as in RS-485 systems.

When Asynchronous Address mode is enabled, all data is transmitted and received as 9-bit characters. The 9th bit determines whether the character is an address or data. When the 9th bit is set, the eight Least Significant bits are the address. When the 9th bit is clear, the Least Significant bits are data. In either case, the 9th bit is stored in PERIF when the byte is written to the receive FIFO. When PERIE is also set, the RXIF will be suppressed, thereby suspending DMA transfers allowing software to process the received address.

An address character will enable all receivers that match the address and disable all other receivers. Once a receiver is enabled, all non-address characters will be received until an address character is received that does not match.

### 31.3.1 ADDRESS MODE TRANSMIT

The UART transmitter is enabled for asynchronous address operation by configuring the following control bits:

- TXEN = 1

- MODE<3:0> = 0100

- UxBRGH:L = desired baud rate

- RxyPPS = code for desired output pin

- ON = 1

Addresses are sent by writing to the UxP1L register. This transmits the written byte with the 9th bit set, which indicates that the byte is an address.

Data is sent by writing to the UxTXB register. This transmits the written byte with the 9th bit cleared, which indicates that the byte is data.

To send data to a particular device on the transmission bus, first transmit the address of the intended device. All subsequent data will be accepted only by that device until an address of another device is transmitted.

Writes to UxP1L take precedence over writes to UxTXB. When both the UxP1L and UxTXB registers are written while the TSR is busy, the next byte to be transmitted will be from UxP1L.

To ensure that all data intended for one device is sent before the address is changed, wait until the TXMTIF bit is high before writing UxP1L with the new address.

## 31.3.2 ADDRESS MODE RECEIVE

The UART receiver is enabled for asynchronous address operation by configuring the following control bits:

- RXEN = 1

- MODE<3:0> = 0100

- UxBRGH:L = desired baud rate

- RXPPS = code for desired input pin

- Input pin ANSEL bit = 0

- UxP2L = receiver address

- UxP3L = address mask

- ON = 1

In Address mode, no data will be transferred to the input FIFO until a valid address is received. This is the default state. Any of the following conditions will cause the UART to revert to the default state:

- ON = 0

- RXEN = 0

- · Received address does not match

When a character with the 9th bit set is received, the Least Significant eight bits of that character will be qualified by the values in the UxP2L and UxP3L registers.

The byte is XOR'd with UxP2L then AND'd with UxP3L. A match occurs when the result is 0h, in which case, the unaltered received character is stored in the receive FIFO, thereby setting the UxRXIF interrupt bit. The 9th bit is stored in the corresponding PERIF bit, identifying this byte as an address.

An address match also enables the receiver for all data such that all subsequent characters without the 9th bit set will be stored in the receive FIFO.

When the 9th bit is set and a match does not occur, the character is not stored in the receive FIFO and all subsequent data is ignored.

The UxP3L register mask allows a range of addresses to be accepted. Software can then determine the subaddress of the range by processing the received address character.

## 32.0 SERIAL PERIPHERAL INTERFACE (SPI) MODULE

## 32.1 SPI Module Overview

The SPI (Serial Peripheral Interface) module is a synchronous serial data communication bus that operates in Full-Duplex mode. Devices communicate in a master/slave environment where the master device initiates the communication. A slave device is controlled through a Chip Select known as Slave Select. Example slave devices include serial EEPROMs, shift registers, display drivers, A/D converters, or another  $PIC^{\mathbb{R}}$  device.

The SPI bus specifies four signal connections:

- Serial Clock (SCK)

- Serial Data Out (SDO)

- Serial Data IN (SDI)

- Slave Select (SS)

The SPI interface supports the following modes and features:

- Master mode

- Slave mode

- · Clock Polarity and Edge Select

- · SDI, SDO, and SS Polarity Control

- Separate Transmit and Receive Enables

- · Slave Select Synchronization

- Daisy-chain connection of slave devices

- Separate Transmit and Receive Buffers with 2-byte FIFO and DMA capabilities

Figure 32-1 shows the block diagram of the SPI module.

| Mnemonic,<br>Operands |                    | Description                             | Quality | 16-Bit Instruction Word |      |      |      | Status          | Natas |

|-----------------------|--------------------|-----------------------------------------|---------|-------------------------|------|------|------|-----------------|-------|

|                       |                    | Description                             | Cycles  | MSb                     |      |      | LSb  | Affected        | Notes |

| LITERAL IN            | ISTRUC             | ΓIONS                                   |         |                         |      |      |      |                 |       |

| ADDLW                 | k                  | Add literal and WREG                    | 1       | 0000                    | 1111 | kkkk | kkkk | C, DC, Z, OV, N |       |

| ANDLW                 | k                  | AND literal with WREG                   | 1       | 0000                    | 1011 | kkkk | kkkk | Z, N            |       |

| IORLW                 | k                  | Inclusive OR literal with WREG          | 1       | 0000                    | 1001 | kkkk | kkkk | Z, N            |       |

| LFSR                  | f <sub>n</sub> , k | Load FSR(f <sub>n</sub> ) with a 14-bit | 2       | 1110                    | 1110 | 00ff | kkkk | None            |       |

|                       |                    | literal (k)                             |         | 1111                    | 00kk | kkkk | kkkk |                 |       |

| ADDFSR                | f <sub>n</sub> , k | Add FSR(f <sub>n</sub> ) with (k)       | 1       | 1110                    | 1000 | ffkk | kkkk | None            |       |

| SUBFSR                | f <sub>n</sub> , k | Subtract (k) from FSR(f <sub>n</sub> )  | 1       | 1110                    | 1001 | ffkk | kkkk | None            |       |

| MOVLB                 | k                  | Move literal to BSR<5:0>                | 1       | 0000                    | 0001 | 00kk | kkkk | None            |       |

| MOVLW                 | k                  | Move literal to WREG                    | 1       | 0000                    | 1110 | kkkk | kkkk | None            |       |

| MULLW                 | k                  | Multiply literal with WREG              | 1       | 0000                    | 1101 | kkkk | kkkk | None            |       |

| RETLW                 | k                  | Return with literal in WREG             | 2       | 0000                    | 1100 | kkkk | kkkk | None            |       |

| SUBLW                 | k                  | Subtract WREG from literal              | 1       | 0000                    | 1000 | kkkk | kkkk | C, DC, Z, OV, N |       |

| XORLW                 | k                  | Exclusive OR literal with WREG          | 1       | 0000                    | 1010 | kkkk | kkkk | Z, N            |       |

| DATA MEM              | IORY – P           | ROGRAM MEMORY INSTRUCTIONS              |         |                         |      |      |      |                 |       |

| TBLRD*                |                    | Table Read                              | 2 - 5   | 0000                    | 0000 | 0000 | 1000 | None            |       |

| TBLRD*+               |                    | Table Read with post-increment          |         | 0000                    | 0000 | 0000 | 1001 | None            |       |

| TBLRD*-               |                    | Table Read with post-decrement          |         | 0000                    | 0000 | 0000 | 1010 | None            |       |

| TBLRD+*               |                    | Table Read with pre-increment           |         | 0000                    | 0000 | 0000 | 1011 | None            |       |

| TBLWT*                |                    | Table Write                             | 2 - 5   | 0000                    | 0000 | 0000 | 1100 | None            |       |

| TBLWT*+               |                    | Table Write with post-increment         |         | 0000                    | 0000 | 0000 | 1101 | None            |       |

| TBLWT*-               |                    | Table Write with post-decrement         |         | 0000                    | 0000 | 0000 | 1110 | None            |       |

| TBLWT+*               |                    | Table Write with pre-increment          |         | 0000                    | 0000 | 0000 | 1111 | None            |       |

### TABLE 41-2: INSTRUCTION SET (CONTINUED)

Note 1: If Program Counter (PC) is modified or a conditional test is true, the instruction requires an additional cycle. The extra cycle is executed as a NOP.

2: Some instructions are multi word instructions. The second/third words of these instructions will be decoded as a NOP, unless the first word of the instruction retrieves the information embedded in these 16-bits. This ensures that all program memory locations have a valid instruction.

3:  $f_s$  and  $f_d$  do not cover the full memory range. 2 MSBs of bank selection are forced to 'b00 to limit the range of these instructions to lower 4k addressing space.

Subtract Literal from FSR

1001

The 6-bit literal 'k' is subtracted from

the contents of the FSR specified by

Q3

Process

Data

ffkk

kkkk

Q4

Write to

destination

SUBFSR f, k  $0 \le k \le 63$

$f \in [0, 1, 2]$  $FSR(f) - k \rightarrow FSRf$

None 1110

'f'. 1 1

Q2

Read

register 'f'

SUBFSR 2, 23h

03FFh

03DCh

| SLE         | SLEEP Enter Sleep mode                                                           |                                                                                                                                                                          |                                                                                       |                                      |                      | SUBFSR | S                                                        |             |

|-------------|----------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------|--------------------------------------|----------------------|--------|----------------------------------------------------------|-------------|

| Synta       | ax:                                                                              | SLEEP                                                                                                                                                                    |                                                                                       |                                      |                      |        | Syntax:                                                  | S           |

| Oper        | ands:                                                                            | None                                                                                                                                                                     |                                                                                       |                                      |                      |        | Operands:                                                | 0           |

| Oper        | ation:                                                                           | $\begin{array}{l} \text{00h} \rightarrow \text{WE} \\ 0 \rightarrow \text{WDT} \\ 1 \rightarrow \overline{\text{TO}}, \\ 0 \rightarrow \overline{\text{PD}} \end{array}$ | DT,<br>postscaler,                                                                    |                                      |                      |        | Operation:<br>Status Affected:<br>Encoding:              | f<br>F<br>N |

| Statu       | s Affected:                                                                      | TO, PD                                                                                                                                                                   |                                                                                       |                                      |                      |        | Description:                                             | Т           |

| Enco        | ding:                                                                            | 0000                                                                                                                                                                     | 0000                                                                                  | 0000                                 | 0011                 |        |                                                          | ti<br>'f    |

| Desc        | ription:                                                                         | cleared. T<br>is set. Wat<br>postscaler<br>The proce                                                                                                                     | r-down Stat<br>he Time-ou<br>chdog Time<br>are cleare<br>ssor is put<br>scillator sto | t Status<br>er and<br>d.<br>into Sle | s bit (TO)<br>its    |        | Words:<br>Cycles:<br>Q Cycle Activity:<br>Q1<br>Decode   | 1           |

| Word        | ls:                                                                              | 1                                                                                                                                                                        |                                                                                       |                                      |                      |        | Decode                                                   | reç         |

| Cycle       | es:                                                                              | 1                                                                                                                                                                        |                                                                                       |                                      |                      |        |                                                          |             |

| QC          | ycle Activity:                                                                   |                                                                                                                                                                          |                                                                                       |                                      |                      |        |                                                          |             |

|             | Q1<br>Decode                                                                     | Q2<br>No<br>operation                                                                                                                                                    | Q3<br>Process<br>Data                                                                 | ;                                    | Q4<br>Go to<br>Sleep | ]      | Example:<br>Before Instruct<br>FSR2<br>After Instruction | =           |

| <u>Exan</u> | <u>nple</u> :<br>Before Instruc                                                  | SLEEP                                                                                                                                                                    |                                                                                       |                                      |                      |        | FSR2                                                     | =           |

|             | $\frac{\overline{TO}}{PD} =$ After Instruction $\frac{\overline{TO}}{PD} =$ PD = | ?<br>?                                                                                                                                                                   |                                                                                       |                                      |                      |        |                                                          |             |

† If WDT causes wake-up, this bit is cleared.

| Address          | Name       | Bit 7         | Bit 6     | Bit 5    | Bit 4    | Bit 3           | Bit 2           | Bit 1           | Bit 0      | Regis<br>on pa |

|------------------|------------|---------------|-----------|----------|----------|-----------------|-----------------|-----------------|------------|----------------|

| 3989h            | IPR9       | —             | —         | —        | _        | CLC3IP          | CWG3IP          | CCP3IP          | TMR6IP     | 165            |

| 3988h            | IPR8       | TMR5GIP       | TMR5IP    | _        | _        | —               | _               | _               | —          | 164            |

| 3987h            | IPR7       |               | _         | INT2IP   | CLC2IP   | CWG2IP          | -               | CCP2IP          | TMR4IP     | 164            |

| 3986h            | IPR6       | TMR3GIP       | TMR3IP    | U2IP     | U2EIP    | U2TXIP          | U2RXIP          | I2C2EIP         | I2C2IP     | 163            |

| 3985h            | IPR5       | I2C2TXIP      | I2C2RXIP  | DMA2AIP  | DMA2ORIP | DMA2DCN-<br>TIP | DMA2SCN-<br>TIP | C2IP            | INT1IP     | 162            |

| 3984h            | IPR4       | CLC1IP        | CWG1IP    | NCO1IP   | _        | CCP1IP          | TMR2IP          | TMR1GIP         | TMR1IP     | 161            |

| 3983h            | IPR3       | TMR0IP        | U1IP      | U1EIP    | U1TXIP   | U1RXIP          | I2C1EIP         | I2C1IP          | I2C1TXIP   | 16             |

| 3982h            | IPR2       | I2C1RXIP      | SPI1IP    | SPI1TXIP | SPI1RXIP | DMA1AIP         | DMA10RIP        | DMA1DCN-<br>TIP | DMA1SCNTIP | 15             |

| 3981h            | IPR1       | SMT1PWAIP     | SMT1PRAIP | SMT1IP   | C1IP     | ADTIP           | ADIP            | ZCDIP           | INT0IP     | 15             |

| 3980h            | IPR0       | IOCIP         | CRCIP     | SCANIP   | NVMIP    | CSWIP           | OSFIP           | HLVDIP          | SWIP       | 15             |

| 397Fh -<br>397Eh | _          |               |           |          | Unimple  | emented         |                 |                 |            |                |

| 397Dh            | SCANTRIG   | _             | _         | —        | _        |                 | T               | SEL             |            | 22             |

| 397Ch            | SCANCON0   | EN            | TRIGEN    | SGO      | _        | —               | MREG            | BURSTMD         | BUSY       | 22             |

| 397Bh            | SCANHADRU  | —             | —         |          | •        | F               | IADR            | •               | •          | 22             |

| 397Ah            | SCANHADRH  |               |           |          | HA       | DR              |                 |                 |            | 22             |

| 3979h            | SCANHADRL  | HADR          |           |          |          |                 |                 |                 | 22         |                |

| 3978h            | SCANLADRU  | _             | _         |          |          | LADR            |                 |                 |            |                |

| 3977h            | SCANLADRH  |               |           |          | LA       | LADR            |                 |                 |            |                |

| 3976h            | SCANLADRL  |               | LADR      |          |          |                 |                 |                 | 22<br>22   |                |

| 3975h -<br>396Ah | -          | Unimplemented |           |          |          |                 |                 |                 |            |                |

| 3969h            | CRCCON1    |               | DLEI      | N        |          |                 | Р               | LEN             |            | 21             |

| 3968h            | CRCCON0    | EN            | CRCGO     | BUSY     | ACCM     | _               | _               | SHIFTM          | FULL       | 21             |

| 3967h            | CRCXORH    | X15           | X14       | X13      | X12      | X11             | X10             | X9              | X8         | 22             |

| 3966h            | CRCXORL    | X7            | X6        | X5       | X4       | X3              | X2              | X1              | _          | 22             |

| 3965h            | CRCSHIFTH  | SHFT15        | SHFT14    | SHFT13   | SHFT12   | SHFT11          | SHFT10          | SHFT9           | SHFT8      | 22             |

| 3964h            | CRCSHIFTL  | SHFT7         | SHFT6     | SHFT5    | SHFT4    | SHFT3           | SHFT2           | SHFT1           | SHFT0      | 22             |

| 3963h            | CRCACCH    | ACC15         | ACC14     | ACC13    | ACC12    | ACC11           | ACC10           | ACC9            | ACC8       | 21             |

| 3962h            | CRCACCL    | ACC7          | ACC6      | ACC5     | ACC4     | ACC3            | ACC2            | ACC1            | ACC0       | 22             |

| 3961h            | CRCDATH    | DATA15        | DATA14    | DATA13   | DATA12   | DATA11          | DATA10          | DATA9           | DATA8      | 21             |

| 3960h            | CRCDATL    | DATA7         | DATA6     | DATA5    | DATA4    | DATA3           | DATA2           | DATA1           | DATA0      | 21             |

| 395Fh            | WDTTMR     |               |           | WDTTMR   | I        |                 | STATE           |                 | SCNT       | 18             |

| 395Eh            | WDTPSH     |               |           |          | PS       | CNT             |                 |                 |            | 18             |

| 395Dh            | WDTPSL     | PSCNT         |           |          |          |                 |                 |                 | 18         |                |

| 395Ch            | WDTCON1    | _             |           | CS       |          | _               | — WINDOW        |                 |            |                |

| 395Bh            | WDTCON0    | _             |           |          |          | PS              |                 | / -             | SEN        | 18<br>18       |

| 395Ah -<br>38A0h | _          |               |           |          | Unimple  | emented         |                 |                 |            |                |

| 389Fh            | IVTADU     |               |           |          | A        | D               |                 |                 |            | 16             |

| 389Eh            | IVTADH     |               |           |          |          | D               |                 |                 |            | 16             |

| 389Dh            | IVTADL     |               |           |          | A        |                 |                 |                 |            | 16             |

| 389Ch -<br>3891h | _          | Unimplemented |           |          |          |                 |                 |                 |            |                |

| 3890h            | PRODH SHAD |               |           |          | PRO      | DDH             |                 |                 |            | 12             |

|                  |            | PRODL         |           |          |          |                 |                 |                 |            |                |

| 388Fh            | PRODL_SHAD |               |           |          | PRO      | DDL             |                 |                 |            | 12             |

#### **TABLE 42-1**: REGISTER FILE SUMMARY FOR PIC18(L)F26/27/45/46/47/55/56/57K42 DEVICES

Note 1: Unimplemented in LF devices.

Unimplemented in PIC18(L)F26/27K42. 2:

Unimplemented on PIC18(L)F26/27/45/46/47K42 devices. 3:

4: Unimplemented in PIC18(L)F45/55K42.

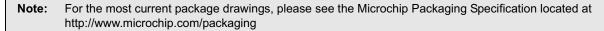

## 28-Lead Plastic Shrink Small Outline (SS) - 5.30 mm Body [SSOP]

|                          | Units            |          |          | MILLIMETERS |  |  |  |

|--------------------------|------------------|----------|----------|-------------|--|--|--|

| Dimensior                | Dimension Limits |          |          | MAX         |  |  |  |

| Number of Pins           | Ν                | 28       |          |             |  |  |  |

| Pitch                    | е                |          | 0.65 BSC |             |  |  |  |

| Overall Height           | А                | -        | -        | 2.00        |  |  |  |

| Molded Package Thickness | A2               | 1.65     | 1.75     | 1.85        |  |  |  |

| Standoff                 | A1               | 0.05     | -        | -           |  |  |  |

| Overall Width            | E                | 7.40     | 7.80     | 8.20        |  |  |  |

| Molded Package Width     | E1               | 5.00     | 5.30     | 5.60        |  |  |  |

| Overall Length           | D                | 9.90     | 10.20    | 10.50       |  |  |  |

| Foot Length              | L                | 0.55     | 0.75     | 0.95        |  |  |  |

| Footprint                |                  | 1.25 REF |          |             |  |  |  |

| Lead Thickness           | С                | 0.09     | _        | 0.25        |  |  |  |

| Foot Angle               | φ                | 0°       | 4°       | 8°          |  |  |  |

| Lead Width               | b                | 0.22     | -        | 0.38        |  |  |  |

#### Notes:

- 1. Pin 1 visual index feature may vary, but must be located within the hatched area.

- 2. Dimensions D and E1 do not include mold flash or protrusions. Mold flash or protrusions shall not exceed 0.20 mm per side.

- 3. Dimensioning and tolerancing per ASME Y14.5M.

- BSC: Basic Dimension. Theoretically exact value shown without tolerances.

REF: Reference Dimension, usually without tolerance, for information purposes only.

Microchip Technology Drawing C04-073B

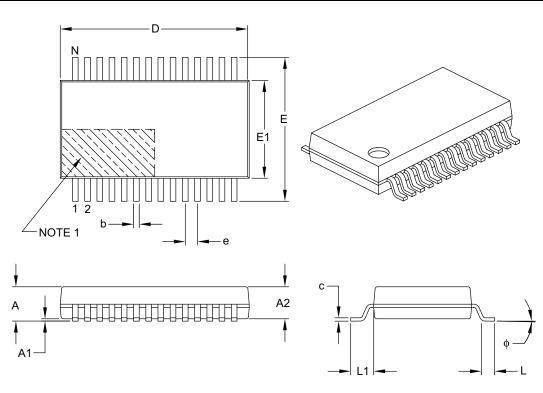

## 28-Lead Plastic Quad Flat, No Lead Package (ML) - 6x6 mm Body [QFN] With 0.55 mm Terminal Length

**Note:** For the most current package drawings, please see the Microchip Packaging Specification located at http://www.microchip.com/packaging

|                         | Units  | М        | ;        |      |  |

|-------------------------|--------|----------|----------|------|--|

| Dimension               | Limits | MIN      | NOM      | MAX  |  |

| Number of Pins          | Ν      |          | 28       |      |  |

| Pitch                   | е      |          | 0.65 BSC |      |  |

| Overall Height          | А      | 0.80     | 0.90     | 1.00 |  |

| Standoff                | A1     | 0.00     | 0.02     | 0.05 |  |

| Terminal Thickness      | A3     |          | 0.20 REF |      |  |

| Overall Width           | E      |          | 6.00 BSC |      |  |

| Exposed Pad Width       | E2     | 3.65     | 3.70     | 4.20 |  |

| Overall Length          | D      | 6.00 BSC |          |      |  |

| Exposed Pad Length      | D2     | 3.65     | 3.70     | 4.20 |  |

| Terminal Width          | b      | 0.23     | 0.30     | 0.35 |  |

| Terminal Length         | L      | 0.50     | 0.55     | 0.70 |  |

| Terminal-to-Exposed Pad | К      | 0.20     | -        | -    |  |

Notes:

1. Pin 1 visual index feature may vary, but must be located within the hatched area.

2. Package is saw singulated

3. Dimensioning and tolerancing per ASME Y14.5M.

BSC: Basic Dimension. Theoretically exact value shown without tolerances.

REF: Reference Dimension, usually without tolerance, for information purposes only.

Microchip Technology Drawing C04-105C Sheet 2 of 2

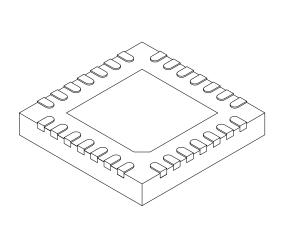

## 28-Lead Plastic Quad Flat, No Lead Package (MX) - 6x6x0.5mm Body [UQFN] Ultra-Thin with 0.40 x 0.60 mm Terminal Width/Length and Corner Anchors

**Note:** For the most current package drawings, please see the Microchip Packaging Specification located at http://www.microchip.com/packaging

|                             | MILLIMETERS      |          |           |      |  |  |

|-----------------------------|------------------|----------|-----------|------|--|--|

| Dimensior                   | Dimension Limits |          |           | MAX  |  |  |

| Number of Pins              | N                | 28       |           |      |  |  |

| Pitch                       | е                | 0.65 BSC |           |      |  |  |

| Overall Height              | Α                | 0.40     | 0.50      | 0.60 |  |  |

| Standoff                    | A1               | 0.00     | 0.02      | 0.05 |  |  |

| Terminal Thickness          | (A3)             |          | 0.127 REF |      |  |  |

| Overall Width               | E                | 6.00 BSC |           |      |  |  |

| Exposed Pad Width           | E2               |          | 4.00      |      |  |  |

| Overall Length              | D                | 6.00 BSC |           |      |  |  |

| Exposed Pad Length          | D2               |          | 4.00      |      |  |  |

| Terminal Width              | b                | 0.35     | 0.40      | 0.45 |  |  |

| Corner Pad                  | b1               | 0.55     | 0.60      | 0.65 |  |  |

| Corner Pad, Metal Free Zone | b2               | 0.15     | 0.20      | 0.25 |  |  |

| Terminal Length             | L                | 0.55     | 0.60      | 0.65 |  |  |

| Terminal-to-Exposed Pad     | K                | 0.20     | -         | -    |  |  |

Notes:

- 1. Pin 1 visual index feature may vary, but must be located within the hatched area.

- 2. Package is saw singulated

- 3. Dimensioning and tolerancing per ASME Y14.5M

- BSC: Basic Dimension. Theoretically exact value shown without tolerances. REF: Reference Dimension, usually without tolerance, for information purposes only.

- 4. Outermost portions of corner structures may vary slightly.

Microchip Technology Drawing C04-0209 Rev C Sheet 2 of 2