Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

#### Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

E·XFl

| Details                    |                                                                             |

|----------------------------|-----------------------------------------------------------------------------|

| Product Status             | Active                                                                      |

| Core Processor             | PIC                                                                         |

| Core Size                  | 8-Bit                                                                       |

| Speed                      | 64MHz                                                                       |

| Connectivity               | I <sup>2</sup> C, LINbus, SPI, UART/USART                                   |

| Peripherals                | Brown-out Detect/Reset, DMA, HLVD, POR, PWM, WDT                            |

| Number of I/O              | 36                                                                          |

| Program Memory Size        | 64KB (32K x 16)                                                             |

| Program Memory Type        | FLASH                                                                       |

| EEPROM Size                | 1K x 8                                                                      |

| RAM Size                   | 4K x 8                                                                      |

| Voltage - Supply (Vcc/Vdd) | 1.8V ~ 3.6V                                                                 |

| Data Converters            | A/D 35x12b; D/A 1x5b                                                        |

| Oscillator Type            | Internal                                                                    |

| Operating Temperature      | -40°C ~ 125°C (TA)                                                          |

| Mounting Type              | Surface Mount                                                               |

| Package / Case             | 40-UFQFN Exposed Pad                                                        |

| Supplier Device Package    | 40-UQFN (5x5)                                                               |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/pic18lf46k42-e-mv |

|                            |                                                                             |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

# 5.7.4 FIXED VOLTAGE REFERENCE DATA

The DIA stores measured FVR voltages for this device in mV for the different buffer settings of 1x, 2x or 4x at Program Memory locations 3F0030h to 3F003Bh. For more information on the FVR, refer to **Section 34.0 "Fixed Voltage Reference (FVR)"**.

- FVRA1X stores the value of ADC FVR1 Output voltage for 1x setting (in mV)

- FVRA2X stores the value of ADC FVR1 Output Voltage for 2x setting (in mV)

- FVRA4X stores the value of ADC FVR1 Output Voltage for 4x setting (in mV)

- FVRC1X stores the value of Comparator FVR2 output voltage for 2x setting (in mV)

- FVRC2X stores the value of Comparator FVR2 output voltage for 2x setting (in mV)

- FVRC4X stores the value of Comparator FVR2 output voltage for 4x setting (in mV)

# 5.8 Device Configuration Information

The Device Configuration Information (DCI) is a dedicated region in the Program memory space mapped from 3FFF00h to 3FFF09h. The data stored in these locations is read-only and cannot be erased.

Refer to Table 5-4: Device Configuration Information for PIC18(L)F26/27/45/55/46/47/56/57K42 for the complete DCI table address and description. The DCI holds information about the device which is useful for programming and Bootloader applications.

The erase size is the minimum erasable unit in the PFM, expressed as rows. The total device Flash memory capacity is (Row Size \* Number of rows)

| ADDRESS           | News  | DECODIDION                      |                       | VALUE                    |                          |       |

|-------------------|-------|---------------------------------|-----------------------|--------------------------|--------------------------|-------|

|                   | Name  | DESCRIPTION                     | PIC18(L)F45/55K42     | PIC18(L)F26/46/56K42     | PIC18(L)F27/47/57K42     | UNITS |

| 3F FF00h-3F FF01h | ERSIZ | Erase Row Size                  | 64                    | 64                       | 64                       | Words |

| 3F FF02h-3F FF03h | WLSIZ | Number of write latches per row | 128                   | 128                      | 128                      | Bytes |

| 3F FF04h-3F FF05h | URSIZ | Number of User Rows             | 256                   | 512                      | 1024                     | Rows  |

| 3F FF06h-3F FF07h | EESIZ | Data EEPROM memory size         | 256                   | 1024                     | 1024                     | Bytes |

| 3F FF08h-3F FF09h | PCNT  | Pin Count                       | 40 <sup>(1)</sup> /48 | 28/40 <sup>(1)</sup> /48 | 28/40 <sup>(1)</sup> /48 | Pins  |

#### TABLE 5-4:DEVICE CONFIGURATION INFORMATION FOR PIC18(L)F26/27/45/55/46/47/56/57K42

Note 1: Pin count of 40 is also used for 44-pin part.

#### 7.2.2.3 Internal Oscillator Frequency Adjustment

The internal oscillator is factory-calibrated. This internal oscillator can be adjusted in software by writing to the OSCTUNE register (Register 7-3).

The default value of the OSCTUNE register is 00h. The value is a 6-bit two's complement number. A value of 1Fh will provide an adjustment to the maximum frequency. A value of 20h will provide an adjustment to the minimum frequency.

When the OSCTUNE register is modified, the oscillator frequency will begin shifting to the new frequency. Code execution continues during this shift. There is no indication that the shift has occurred.

OSCTUNE **does not affect** the LFINTOSC frequency. Operation of features that depend on the LFINTOSC clock source frequency, such as the Power-up Timer (PWRT), WWDT, Fail-Safe Clock Monitor (FSCM) and peripherals, are *not* affected by the change in frequency.

# 7.2.2.4 LFINTOSC

The Low-Frequency Internal Oscillator (LFINTOSC) is a factory-calibrated 31 kHz internal clock source.

The LFINTOSC is the frequency for the Power-up Timer (PWRT), Windowed Watchdog Timer (WWDT) and Fail-Safe Clock Monitor (FSCM).

The LFINTOSC is enabled through one of the following methods:

- Programming the RSTOSC<2:0> bits of Configuration Word 1 to enable LFINTOSC.

- Write to the NOSC<2:0> bits of the OSCCON1 register during run-time. See Section 7.3, Clock Switching for more information.

# 7.2.2.5 ADCRC

The ADCRC is an oscillator dedicated to the  $ADC^2$  module. The ADCRC oscillator can be manually enabled using the ADOEN bit of the OSCEN register. The ADCRC runs at a fixed frequency of 600 kHz. ADCRC is automatically enabled if it is selected as the clock source for the  $ADC^2$  module.

| R-0/0                  | R-0/0                               | R-0/0                              | R-0/0                   | R/W/HS-0/0        | R/W/HS-0/0        | R/W/HS-0/0                                  | R/W/HS-0/0     |

|------------------------|-------------------------------------|------------------------------------|-------------------------|-------------------|-------------------|---------------------------------------------|----------------|

| I2C1RXIF <sup>(2</sup> | <sup>2)</sup> SPI1IF <sup>(3)</sup> | SPI1TXIF <sup>(4)</sup>            | SPI1RXIF <sup>(4)</sup> | DMA1AIF           | DMA10RIF          | DMA1DCNTIF                                  | DMA1SCNTIF     |

| bit 7                  |                                     |                                    |                         |                   |                   |                                             | bit (          |

|                        |                                     |                                    |                         |                   |                   |                                             |                |

| Legend:                |                                     |                                    |                         |                   |                   |                                             |                |

| R = Reada              |                                     | W = Writable                       |                         | •                 | ented bit, read   |                                             |                |

| u = Bit is u           | -                                   | x = Bit is unk                     |                         |                   |                   | Value at all othe                           | er Resets      |

| '1' = Bit is s         | set                                 | '0' = Bit is cle                   | ared                    | HS = Hardwar      | e set             |                                             |                |

| bit 7                  | I2C1RXIF:                           | <sup>2</sup> C1 Receive Ir         | nterrupt Flag b         | it(2)             |                   |                                             |                |

|                        |                                     | ot has occurred                    |                         |                   |                   |                                             |                |

|                        | 0 = Interrup                        | ot event has no                    | t occurred              |                   |                   |                                             |                |

| bit 6                  |                                     | 1 Interrupt Flag                   | -                       |                   |                   |                                             |                |

|                        |                                     | ot has occurred                    |                         |                   |                   |                                             |                |

|                        | -                                   | ot event has no                    |                         | (4)               |                   |                                             |                |

| bit 5                  |                                     | SPI1 Transmit I                    |                         | DIL               |                   |                                             |                |

|                        |                                     | ot has occurred<br>ot event has no |                         |                   |                   |                                             |                |

| bit 4                  | •                                   | SPI1 Receive I                     |                         | oit(4)            |                   |                                             |                |

|                        |                                     | ot has occurred                    | 1 0                     |                   |                   |                                             |                |

|                        |                                     | ot event has no                    |                         |                   |                   |                                             |                |

| bit 3                  | DMA1AIF: [                          | DMA1 Abort In                      | terrupt Flag bit        | t                 |                   |                                             |                |

|                        | 1 = Interrup                        | ot has occurred                    | (must be clea           | red by software   | e)                |                                             |                |

|                        | •                                   | ot event has no                    |                         |                   |                   |                                             |                |

| bit 2                  |                                     | : DMA1 Overru                      | •                       | •                 |                   |                                             |                |

|                        | -                                   |                                    | -                       | red by software   | e)                |                                             |                |

| bit 1                  |                                     | ot event has no                    |                         | t Interrupt Flag  | hit               |                                             |                |

|                        |                                     |                                    |                         | red by software   |                   |                                             |                |

|                        |                                     | ot event has no                    |                         | incu by software  | -)                |                                             |                |

| bit 0                  | •                                   | <b>FIF:</b> DMA1 Sou               |                         | errupt Flag bit   |                   |                                             |                |

|                        |                                     |                                    |                         | red by software   | e)                |                                             |                |

|                        | 0 = Interrup                        | ot event has no                    | toccurred               | -                 |                   |                                             |                |

|                        |                                     | e global enable                    |                         |                   |                   | the state of its co<br>priate interrupt fla |                |

| 2:                     | -                                   | 2CxRXIF are r                      | ead-only bits.          | To clear the inte | errupt condition  | , the CLRBF bit i                           | n I2CxSTAT1    |

| 3:                     | SPIxIF is a rea                     | d-only bit. To c                   | lear the interru        | pt condition, al  | l bits in the SPI | kINTF register m                            | ust be cleared |

|                        |                                     |                                    |                         |                   |                   |                                             |                |

# REGISTER 9-5: PIR2: PERIPHERAL INTERRUPT REGISTER 2<sup>(1)</sup>

4: SPIxTXIF and SPIxRXIF are read-only bits and cannot be set/cleared by the software.

| U-0   | U-0 | U-0 | U-0 | U-0 | U-0 | R/W-0/0 | R/W-0/0 |

|-------|-----|-----|-----|-----|-----|---------|---------|

| —     | —   | —   | —   | —   | —   | DMA2MD  | DMA1MD  |

| bit 7 |     |     |     |     |     |         | bit 0   |

#### REGISTER 19-8: PMD7: PMD CONTROL REGISTER 7

| Legend:              |                      |                                                       |

|----------------------|----------------------|-------------------------------------------------------|

| R = Readable bit     | W = Writable bit     | U = Unimplemented bit, read as '0'                    |

| u = Bit is unchanged | x = Bit is unknown   | -n/n = Value at POR and BOR/Value at all other Resets |

| '1' = Bit is set     | '0' = Bit is cleared | q = Value depends on condition                        |

| bit 7-2 | Unimplemented: Read as '0'                                                 |

|---------|----------------------------------------------------------------------------|

| bit 1   | DMA2MD: Disable DMA2 Module bit                                            |

|         | <ul><li>1 = DMA2 module disabled</li><li>0 = DMA2 module enabled</li></ul> |

| bit 0   | DMA1MD: Disable DMA1 Module bit                                            |

|         | 1 - DMA1 madula disabled                                                   |

1 = DMA1 module disabled 0 = DMA1 module enabled

# TABLE 19-1: SUMMARY OF REGISTERS ASSOCIATED WITH PERIPHERAL MODULE DISABLE

| Name | Bit 7  | Bit 6  | Bit 5  | Bit 4  | Bit 3  | Bit 2  | Bit 1  | Bit 0  | Register<br>on Page |

|------|--------|--------|--------|--------|--------|--------|--------|--------|---------------------|

| PMD0 | SYSCMD | FVRMD  | HLVDMD | CRCMD  | SCANMD | NVMMD  | CLKRMD | IOCMD  | 290                 |

| PMD1 | NCO1MD | TMR6MD | TMR5MD | TMR4MD | TMR3MD | TMR2MD | TMR1MD | TMR0MD | 291                 |

| PMD2 | —      | DACMD  | ADCMD  | _      | _      | CMP2MD | CMP1MD | ZCDMD  | 292                 |

| PMD3 | PWM8MD | PWM7MD | PWM6MD | PWM5MD | CCP4MD | CCP3MD | CCP2MD | CCP1MD | 293                 |

| PMD4 | CWG3MD | CWG2MD | CWG1MD | _      | _      | _      | _      | _      | 294                 |

| PMD5 | —      | _      | U2MD   | U1MD   | _      | SPI1MD | I2C2MD | I2C1MD | 295                 |

| PMD6 | —      | _      | SMT1MD | CLC4MD | CLC3MD | CLC2MD | CLC1MD | DSMMD  | 295                 |

| PMD7 | _      | _      | _      | _      | _      | _      | DMA2MD | DMA1MD | 297                 |

Legend: — = unimplemented location, read as '0'. Shaded cells are not used by peripheral module disable.

#### 22.5.9 EDGE-TRIGGERED MONOSTABLE MODES

The Edge-Triggered Monostable modes start the timer on an edge from the external Reset signal input, after the ON bit is set, and stop incrementing the timer when the timer matches the T2PR period value. The following edges will start the timer:

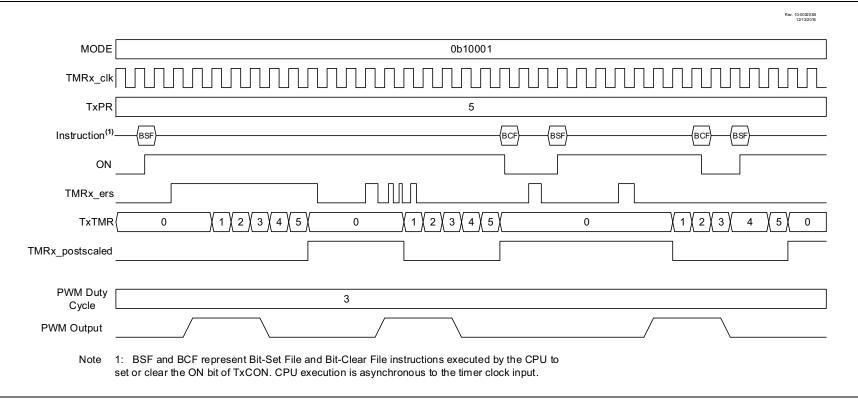

- Rising edge (MODE<4:0> = 10001)

- Falling edge (MODE<4:0> = 10010)

- Rising or Falling edge (MODE<4:0> = 10011)

When an Edge-Triggered Monostable mode is used in conjunction with the CCP PWM operation the PWM drive goes active with the external Reset signal edge that starts the timer, but will not go active when the timer matches the T2PR value. While the timer is incrementing, additional edges on the external Reset signal will not affect the CCP PWM.

### FIGURE 22-12: RISING EDGE-TRIGGERED MONOSTABLE MODE TIMING DIAGRAM (MODE = 10001)

# FIGURE 25-9: HIGH AND LOW MEASURE MODE SINGLE ACQUISITION TIMING DIAGRAM

PIC18(L)F26/27/45/46/47/55/56/57K42

| <b>TABLE 30-2:</b> | MD1SRC SELECTION MUX |

|--------------------|----------------------|

|                    | CONNECTIONS          |

| MS<4:0> | >   | Connection |

|---------|-----|------------|

| 1 1111  | 31- | Reserved   |

| -       | 23  |            |

| 1 0111  |     |            |

| 1 0110  | 22  | SPI1 SDO   |

| 1 0101  | 21  | Reserved   |

| 1 0100  | 20  | UART2 TX   |

| 1 0011  | 19  | UART1 TX   |

| 1 0010  | 18  | CLC4 OUT   |

| 1 0001  | 17  | CLC3 OUT   |

| 1 0000  | 16  | CLC2 OUT   |

| 0 1111  | 15  | CLC1 OUT   |

| 0 1110  | 14  | CMP2 OUT   |

| 0 1101  | 13  | CMP1 OUT   |

| 0 1100  | 12  | NCO1 OUT   |

| 0 1011  | 11  | Reserved   |

| 0 1010  | 10  | Reserved   |

| 0 1001  | 9   | PWM8 OUT   |

| 0 1000  | 8   | PWM7 OUT   |

| 0 0111  | 7   | PWM6 OUT   |

| 0 0110  | 6   | PWM5 OUT   |

# TABLE 30-2: MD1SRC SELECTION MUX CONNECTIONS

| MS<4:0> | > | Connection               |

|---------|---|--------------------------|

| 0 0101  | 5 | CCP4 OUT                 |

| 0 0100  | 4 | CCP3 OUT                 |

| 0 0011  | 3 | CCP2 OUT                 |

| 0 0010  | 2 | CCP1 OUT                 |

| 0 0001  | 1 | DSM1 BIT                 |

| 0 0000  | 0 | Pin selected by MDSRCPPS |

#### TABLE 30-3: SUMMARY OF REGISTERS ASSOCIATED WITH DATA SIGNAL MODULATOR MODE

| Name    | Bit 7 | Bit 6 | Bit 5 | Bit 4  | Bit 3     | Bit 2    | Bit 1 | Bit 0  | Register<br>on Page |

|---------|-------|-------|-------|--------|-----------|----------|-------|--------|---------------------|

| MD1CON0 | EN    | _     | OUT   | OPOL   | —         | —        | -     | BIT    | 469                 |

| MD1CON1 | —     | _     | CHPOL | CHSYNC | _         | _        | CLPOL | CLSYNC | 470                 |

| MD1CARH | —     | _     | _     | —      | _         | CHS<2:0> |       |        | 471                 |

| MD1CARL | —     | _     | _     | —      | _         | CLS<2:0> |       |        | 471                 |

| MDSRC   | _     | _     | —     | —      | SRCS<3:0> |          |       |        | 472                 |

Legend: — = unimplemented, read as '0'. Shaded cells are not used in the Data Signal Modulator mode.

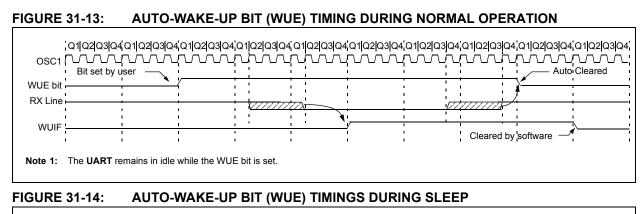

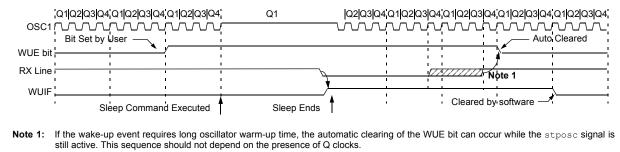

<sup>2:</sup> The **UART** remains in idle while the WUE bit is set.

# 31.18 Transmitting a Break

The UART module has the capability of sending either a fixed length Break period or a software timed Break period. The fixed length Break consists of a Start bit, followed by 12 '0' bits and a Stop bit. The software timed Break is generated by setting and clearing the BRKOVR bit in the UxCON1 register.

To send the fixed length Break, set the SENDB and TXEN bits in the UxCON0 register. The Break sequence is then initiated by a write to UxTXB. The timed Break will occur first, followed by the character written to UxTXB that initiated the Break. The initiating character is typically the Sync character of the LIN specification.

SENB is disabled in the LIN and DMX modes because those modes generate the Break sequence automatically.

The SENDB bit is automatically reset by hardware after the Break Stop bit is complete.

The TXMTIF bit in the UxERRIR register indicates when the transmit operation is active or idle, just as it does during normal transmission. See Figure 31-15 for the timing of the Break sequence.

# 31.19 Receiving a Break

The UART has counters to detect when the RX input remains in the space state for an extended period of time. When this happens, the RXBKIF bit in the UxERRIR register is set.

A Break is detected when the RX input remains in the space state for 11 bit periods for asynchronous and LIN modes, and 23 bit periods for DMX mode.

The user can select to receive the Break interrupt as soon as the Break is detected or at the end of the Break, when the RX input returns to the Idle state. When the RXBIMD bit in the UxCON1 is '1' then RXBKIF is set immediately upon Break detection. When RXBIMD is '0' then RXBKIF is set when the RX input returns to the Idle state.

# 31.20 UART Operation During Sleep

The UART ceases to operate during Sleep. The safe way to wake the device from Sleep by a serial operation is to use the Wake-on-Break feature of the UART. See Section 31.17.3, Auto-Wake-up on Break

| Name    | Bit 7     | Bit 6 | Bit 5  | Bit 4 | Bit 3  | Bit 2  | Bit 1  | Bit 0 | Register<br>on page |

|---------|-----------|-------|--------|-------|--------|--------|--------|-------|---------------------|

| UxCON0  | BRGS      | ABDEN | TXEN   | RXEN  |        | MODE   | <3:0>  |       | 498                 |

| UxCON1  | ON        | _     | —      | WUE   | RXBIMD | —      | BRKOVR | SENDB | 499                 |

| UxCON2  | RUNOVF    | RXPOL | STP    | <1:0> | C0EN   | TXPOL  | FLO<   | <1:0> | 500                 |

| UxERRIR | TXMTIF    | PERIF | ABDOVF | CERIF | FERIF  | RXBKIF | RXFOIF | TXCIF | 501                 |

| UxERRIE | TXMTIE    | PERIE | ABDOVE | CERIE | FERIE; | RXBKIE | RXFOIE | TXCIE | 502                 |

| UxUIR   | WUIF      | ABDIF | _      | _     | _      | ABDIE  | _      | _     | 503                 |

| UxFIFO  | TXWRE     | STPMD | TXBE   | TXBF  | RXIDL  | XON    | RXBE   | RXBF  | 504                 |

| UxBRGL  | BRG<7:0>  |       |        |       |        |        |        |       |                     |

| UxBRGH  | BRG<15:8> |       |        |       |        |        |        |       |                     |

| UxRXB   |           |       |        | RXB   | <7:0>  |        |        |       | 506                 |

| UxTXB   |           |       |        | TXB   | <7:0>  |        |        |       | 506                 |

| UxP1H   | _         | _     | _      | _     | —      | _      | _      | P1<8> | 507                 |

| UxP1L   |           |       | •      | P1<   | 7:0>   |        |        |       | 507                 |

| UxP2H   | _         | _     | _      | _     | —      | _      | _      | P2<8> | 508                 |

| UxP2L   |           |       | •      | P2<   | 7:0>   |        |        |       | 508                 |

| UxP3H   | —         | —     | —      | —     | —      | —      | —      | P3<8> | 509                 |

| UxP3L   |           |       | •      | P3<   | 7:0>   | •      | •      |       | 509                 |

| UxTXCHK |           |       |        | TXCH  | K<7:0> |        |        |       | 510                 |

| UxRXCHK |           |       |        | RXCH  | K<7:0> |        |        |       | 510                 |

### TABLE 31-3: SUMMARY OF REGISTERS ASSOCIATED WITH THE UART

Legend: — = unimplemented, read as '0'. Shaded cells are unused by the UART module.

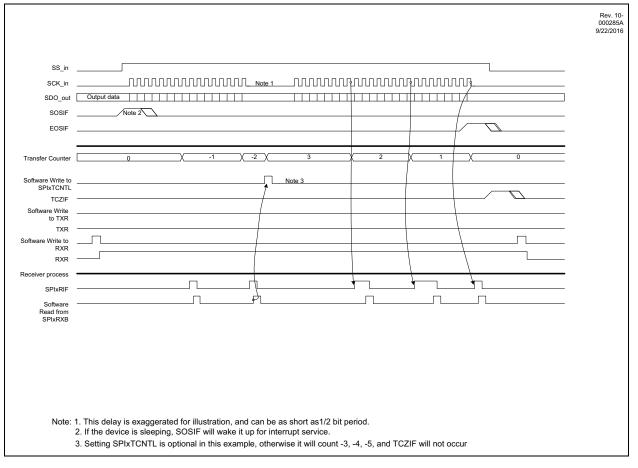

### 32.6.2 SLAVE MODE RECEIVE OPTIONS

The RXR bit controls the nature of receptions in slave mode. When RXR is set, the SDI input data will be stored in the RXFIFO if it is not full. If the RXFIFO is full, the RXOIF bit will be set to indicate an RXFIFO overflow error and the data is discarded. When RXR is cleared, all received data will be ignored and not stored in the RXFIFO (although it may still be used for transmission if TXFIFO is empty). Figure 32-11 shows a typical slave mode communication, showing a case where the master writes two then three bytes, showing interrupts as well as the behavior of the transfer counter in slave mode (see Section 32.4.3 "Transfer Counter in Slave mode" for more details on tSection 32.8 "SPI Interrupts" he transfer counter in slave mode as well as Section X.8 for more information on interrupts).

FIGURE 32-11: SPI SLAVE MODE OPERATION – INTERRUPT-DRIVEN, MASTER WRITES 2+3 BYTES

| R/C/HS-0/0  | ) U-0                                               | R-1/1            | U-0              | R/C/HS-0/0                    | S-0/0            | U-0    | R-0/0 |  |  |  |

|-------------|-----------------------------------------------------|------------------|------------------|-------------------------------|------------------|--------|-------|--|--|--|

| TXWE        |                                                     | TXBE             | _                | RXRE                          | CLRBF            | _      | RXBF  |  |  |  |

| bit 7       |                                                     |                  |                  |                               |                  |        | bit 0 |  |  |  |

|             |                                                     |                  |                  |                               |                  |        |       |  |  |  |

| Legend:     |                                                     |                  |                  |                               |                  |        |       |  |  |  |

| R = Readabl | le bit                                              | W = Writable     | bit              | U = Unimplen<br>C = Clearable | nented bit, read | as '0' |       |  |  |  |

|             |                                                     |                  |                  | S = Settable b                |                  |        |       |  |  |  |

|             |                                                     |                  |                  | HS = Bit can I                | be set by hardw  | are    |       |  |  |  |

|             |                                                     |                  |                  |                               |                  |        |       |  |  |  |

| bit 7       | TXWE: Trans                                         | mit Buffer Writ  | e Error bit      |                               |                  |        |       |  |  |  |

|             | 1 = SPIxTxB                                         | was written wh   | ile TxFIFO v     | vas full                      |                  |        |       |  |  |  |

|             | 0 = No error h                                      | nas occurred     |                  |                               |                  |        |       |  |  |  |

| bit 6       | Unimplemen                                          | ted: Read as '   | 0'               |                               |                  |        |       |  |  |  |

| bit 5       | <b>TXBE</b> : Transmit Buffer Empty bit (read-only) |                  |                  |                               |                  |        |       |  |  |  |

|             | 1 = Transmit                                        | buffer TxFIFO    | is empty         |                               |                  |        |       |  |  |  |

|             | 0 = Transmit                                        | buffer is not en | npty             |                               |                  |        |       |  |  |  |

| bit 4       | Unimplemen                                          | ted: Read as '   | 0'               |                               |                  |        |       |  |  |  |

| bit 3       | RXRE: Receive Buffer Read Error bit                 |                  |                  |                               |                  |        |       |  |  |  |

|             | 1 = SPIxRB v                                        | as read while    | RxFIFO was       | s empty                       |                  |        |       |  |  |  |

|             | 0 = No error h                                      | nas occurred     |                  |                               |                  |        |       |  |  |  |

| bit 2       | CLRBF: Clea                                         | r Buffer Contro  | ol bit (write or | nly)                          |                  |        |       |  |  |  |

|             | 1 = Reset the                                       | receive and tr   | ansmit buffe     | rs, making both I             | ouffers empty    |        |       |  |  |  |

|             | 0 = Take no a                                       | ction            |                  |                               |                  |        |       |  |  |  |

| bit 1       | Unimplemen                                          | ted: Read as '   | 0'               |                               |                  |        |       |  |  |  |

| bit 0       | RXBF: Receiv                                        | ve Buffer Full b | oit (read-only   | )                             |                  |        |       |  |  |  |

|             |                                                     |                  |                  |                               |                  |        |       |  |  |  |

|             | 1 = Receive b                                       | ouffer is full   |                  |                               |                  |        |       |  |  |  |

#### REGISTER 32-11: SPIxRxB: SPI READ BUFFER REGISTER

| R-0   | R-0  | R-0  | R-0  | R-0  | R-0  | R-0  | R-0   |

|-------|------|------|------|------|------|------|-------|

| RXB7  | RXB6 | RXB5 | RXB4 | RXB3 | RXB2 | RXB1 | RXB0  |

| bit 7 |      |      |      |      |      |      | bit 0 |

| Legend:          |                  |                                    |

|------------------|------------------|------------------------------------|

| R = Readable bit | W = Writable bit | U = Unimplemented bit, read as '0' |

bit 7-0 **RXB<7:0>**: Receiver Buffer bits (read-only)

If RX buffer is not empty:

Contains the top-most byte of RXFIFO, and reading this register will remove the top-most byte RXFIFO and decrease the occupancy of the RXFIFO

#### If RX buffer is empty:

Reading this register will read as '0', leave the occupancy unchanged, and set the RXRE bit of SPIxSTATUS

#### 33.5.10 MASTER RECEPTION IN 7-BIT ADDRESSING MODE

This section describes the sequence of events for the  $I^2C$  module configured as an  $I^2C$  master in 7-bit Addressing mode and is receiving data. Figure 33-20 is used as a visual reference for this description.

- Master software loads slave address in I2CxADB1 with R/W bit = d and number of bytes to be received in one sequence in I2CxCNT register.

- Master hardware waits for BFRE bit to be set; then shifts out start and address with R/W = 1.

- 3. Master sends out the 9th SCL pulse for ACK, master hardware clocks in ACK from Slave

- 4. If ABD = 0; i.e., Address buffers are enabled

If NACK, master hardware sends Stop or sets MDR (if RSEN = 1) and waits for user software to write to S bit for restart.

If ABD = 1; i.e., Address buffers are disabled

If NACK, master hardware sends Stop or sets MDR (if RSEN = 1) and waits for user software to load the new address into I2CxTXB. Software writes to the S bit are ignored in this case.

- 5. If ACK, master hardware receives 7-bits of data into the shift register.

- 6. If the receive buffer is full (i.e., RXBF = 1), clock is stretched on 7th falling SCL edge.

- 7. Master software must read previous data out of I2CxRXB to clear RXBF.

- Master hardware receives 8th bit of data into the shift register and loads it into I2CxRXB, sets I2CxRXIF and RXBF bits. I2CxCNT is decremented.

- 9. If I2CxCNT! = 0, master hardware clocks out ACKDT as ACK value to slave. If I2CxCNT = 0, master hardware clocks out ACKCNT as ACK value to slave. It is up to the user to set the values of ACKDT and ACKCNT correctly. If the user does not set ACKCNT to '1', the master hardware will never send a NACK when I2CxCNT becomes zero. Since a NACK was not seen on the bus, the master hardware will also not assert a Stop condition.

- 10. Go to step 4.

### 36.2.5 AUTO-CONVERSION TRIGGER

The auto-conversion trigger allows periodic ADC measurements without software intervention. When a rising edge of the selected source occurs, the GO bit is set by hardware.

The auto-conversion trigger source is selected by the ADACT register.

Using the auto-conversion trigger does not assure proper ADC timing. It is the user's responsibility to ensure that the ADC timing requirements are met. See Register 36-33 for auto-conversion sources.

#### 36.2.6 ADC CONVERSION PROCEDURE (BASIC MODE)

This is an example procedure for using the ADC to perform an analog-to-digital conversion:

- 1. Configure Port:

- Disable pin output driver (Refer to the TRISx register)

- Configure pin as analog (Refer to the ANSELx register)

- 2. Configure the ADC module:

- Select ADC conversion clock

- Select voltage reference

- Select ADC input channel

# **EXAMPLE 36-1: ADC CONVERSION** /\*This code block configures the ADC

- Precharge and acquisition

- Turn on ADC module

- 3. Configure ADC interrupt (optional):

- Clear ADC interrupt flag

- Enable ADC interrupt

- Enable global interrupt<sup>(1)</sup>

- If ADACQ = 0, software must wait the required acquisition time<sup>(2)</sup>.

- 5. Start conversion by setting the GO bit.

- 6. Wait for ADC conversion to complete by one of the following:

- Polling the GO bit

- Polling the ADIF bit

- Waiting for the ADC interrupt (interrupts enabled)

- 7. Read ADC Result.

- 8. Clear the ADC interrupt flag (required if interrupt is enabled).

- **Note 1:** The global interrupt can be disabled if the user is attempting to wake-up from Sleep and resume in-line code execution.

- 2: Refer to Section 36.3 "ADC Acquisition Requirements".

for polling, VDD and VSS references, FRC oscillator and ANO input. Conversion start & polling for completion are included. \*/ void main() { //System Initialize initializeSystem(); //Setup ADC ADCONObits.FM = 1; //right justify ADCONObits.CS = 1; //FRC Clock  $ADPCH = 0 \times 00; //RA0$  is Analog channel TRISAbits.TRISA0 = 1; //Set RA0 to input ANSELAbits.ANSELA0 = 1; //Set RA0 to analog ADCONObits.ON = 1; //Turn ADC On while (1) { ADCONObits.GO = 1; //Start conversion while (ADCONObits.GO); //Wait for conversion done resultHigh = ADRESH; //Read result resultLow = ADRESL; //Read result }

#### REGISTER 36-24: ADACCU: ADC ACCUMULATOR REGISTER UPPER

| U-0                                                                  | U-0                                                                                          | U-0 | U-0 | U-0 | U-0 | R/W-x/x      | R/W-x/x |

|----------------------------------------------------------------------|----------------------------------------------------------------------------------------------|-----|-----|-----|-----|--------------|---------|

| —                                                                    | _                                                                                            | _   | —   |     | —   | ACC<         | 17:16>  |

| bit 7                                                                |                                                                                              |     | •   |     |     |              | bit 0   |

|                                                                      |                                                                                              |     |     |     |     |              |         |

| Legend:                                                              |                                                                                              |     |     |     |     |              |         |

| R = Readable bit W = Writable bit U = Unimplemented bit, read as '0' |                                                                                              |     |     |     |     |              |         |

| u = Bit is unch                                                      | x = Bit is unchanged $x = Bit$ is unknown $-n/n = Value$ at POR and BOR/Value at all other R |     |     |     |     | other Resets |         |

bit 7-2 Unimplemented: Read as '0'

'1' = Bit is set

bit 1-0 ACC<17:16>: ADC Accumulator MSB. Upper two bits of accumulator value. See Table 36-2 for more details.

#### **REGISTER 36-25: ADACCH: ADC ACCUMULATOR REGISTER HIGH**

'0' = Bit is cleared

| R/W-x/x   | R/W-x/x | R/W-x/x | R/W-x/x | R/W-x/x | R/W-x/x | R/W-x/x | R/W-x/x |

|-----------|---------|---------|---------|---------|---------|---------|---------|

| ACC<15:8> |         |         |         |         |         |         |         |

| bit 7     |         |         |         |         |         |         | bit 0   |

| Legend:              |                      |                                                       |

|----------------------|----------------------|-------------------------------------------------------|

| R = Readable bit     | W = Writable bit     | U = Unimplemented bit, read as '0'                    |

| u = Bit is unchanged | x = Bit is unknown   | -n/n = Value at POR and BOR/Value at all other Resets |

| '1' = Bit is set     | '0' = Bit is cleared |                                                       |

bit 7-0 ACC<15:8>: ADC Accumulator middle bits. Middle eight bits of accumulator value. See Table 36-2 for more details.

#### REGISTER 36-26: ADACCL: ADC ACCUMULATOR REGISTER LOW

| R/W-x/x     | R/W-x/x | R/W-x/x | R/W-x/x | R/W-x/x | R/W-x/x | R/W-x/x | R/W-x/x |

|-------------|---------|---------|---------|---------|---------|---------|---------|

|             |         |         | ACC<    | <7:0>   |         |         |         |

| bit 7       |         |         |         |         |         |         | bit 0   |

|             |         |         |         |         |         |         |         |

| I a manuali |         |         |         |         |         |         |         |

| Legend:              |                      |                                                       |

|----------------------|----------------------|-------------------------------------------------------|

| R = Readable bit     | W = Writable bit     | U = Unimplemented bit, read as '0'                    |

| u = Bit is unchanged | x = Bit is unknown   | -n/n = Value at POR and BOR/Value at all other Resets |

| '1' = Bit is set     | '0' = Bit is cleared |                                                       |

|                      |                      |                                                       |

bit 7-0 ACC<7:0>: ADC Accumulator LSB. Lower eight bits of accumulator value. See Table 36-2 for more details.

$\ensuremath{\textcircled{}^{\odot}}$  2017 Microchip Technology Inc.

# REGISTER 36-29: ADERRH: ADC SETPOINT ERROR REGISTER HIGH

| R-x              | R-x   | R-x                  | R-x | R-x            | R-x              | R-x            | R-x          |

|------------------|-------|----------------------|-----|----------------|------------------|----------------|--------------|

|                  |       |                      | ERR | <15:8>         |                  |                |              |

| bit 7            |       |                      |     |                |                  |                | bit 0        |

|                  |       |                      |     |                |                  |                |              |

| Legend:          |       |                      |     |                |                  |                |              |

| R = Readable I   | bit   | W = Writable bit     |     | U = Unimplen   | nented bit, read | d as '0'       |              |

| u = Bit is uncha | anged | x = Bit is unknowr   | ı   | -n/n = Value a | t POR and BC     | R/Value at all | other Resets |

| '1' = Bit is set |       | '0' = Bit is cleared |     |                |                  |                |              |

bit 7-0 **ERR<15:8>**: ADC Setpoint Error MSB. Upper byte of ADC Setpoint Error. Setpoint Error calculation is determined by CALC bits of ADCON3, see Register 36-4 for more details.

#### REGISTER 36-30: ADERRL: ADC SETPOINT ERROR LOW BYTE REGISTER

| R-x      | R-x | R-x | R-x | R-x | R-x | R-x | R-x   |

|----------|-----|-----|-----|-----|-----|-----|-------|

| ERR<7:0> |     |     |     |     |     |     |       |

| bit 7    |     |     |     |     |     |     | bit 0 |

| Legend:              |                      |                                                       |

|----------------------|----------------------|-------------------------------------------------------|

| R = Readable bit     | W = Writable bit     | U = Unimplemented bit, read as '0'                    |

| u = Bit is unchanged | x = Bit is unknown   | -n/n = Value at POR and BOR/Value at all other Resets |

| '1' = Bit is set     | '0' = Bit is cleared |                                                       |

bit 7-0 **ERR<7:0>**: ADC Setpoint Error LSB. Lower byte of ADC Setpoint Error calculation is determined by CALC bits of ADCON3, see Register 36-4 for more details.

#### REGISTER 36-31: ADLTHH: ADC LOWER THRESHOLD HIGH BYTE REGISTER

| R/W-0/0 |

|---------|---------|---------|---------|---------|---------|---------|---------|

|         |         |         | LTH<    | 15:8>   |         |         |         |

| bit 7   |         |         |         |         |         |         | bit 0   |

|         |         |         |         |         |         |         |         |

| Legend:              |                      |                                                       |

|----------------------|----------------------|-------------------------------------------------------|

| R = Readable bit     | W = Writable bit     | U = Unimplemented bit, read as '0'                    |

| u = Bit is unchanged | x = Bit is unknown   | -n/n = Value at POR and BOR/Value at all other Resets |

| '1' = Bit is set     | '0' = Bit is cleared |                                                       |

bit 7-0 LTH<15:8>: ADC Lower Threshold MSB. LTH and UTH are compared with ERR to set the ADUTHR and ADLTHR bits of ADSTAT. Depending on the setting of ADTMD, an interrupt may be triggered by the results of this comparison.

© 2017 Microchip Technology Inc.

| RETURN Return from Subroutine |                   |                                                                                                                                                                                                                                                           |                                                                                                                                                              |      |      |                    |  |  |  |

|-------------------------------|-------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------|------|------|--------------------|--|--|--|

| Synta                         | ax:               | RETURN                                                                                                                                                                                                                                                    | RETURN {s}                                                                                                                                                   |      |      |                    |  |  |  |

| Oper                          | ands:             | s ∈ [0,1]                                                                                                                                                                                                                                                 | s ∈ [0,1]                                                                                                                                                    |      |      |                    |  |  |  |

| Oper                          | ation:            | if s = $1$<br>(WS) $\rightarrow$ W,<br>(STATUSS)<br>(BSRS) $\rightarrow$                                                                                                                                                                                  | $(TOS) \rightarrow PC,$<br>if s = 1<br>$(WS) \rightarrow W,$<br>$(STATUSS) \rightarrow Status,$<br>$(BSRS) \rightarrow BSR,$<br>PCLATU, PCLATH are unchanged |      |      |                    |  |  |  |

| Statu                         | s Affected:       | None                                                                                                                                                                                                                                                      |                                                                                                                                                              |      |      |                    |  |  |  |

| Enco                          | ding:             | 0000                                                                                                                                                                                                                                                      | 0000                                                                                                                                                         | 000  | 001s |                    |  |  |  |

| Word                          | ls:               | is loaded into the program counter. If<br>'s'= 1, the contents of the shadow<br>registers, WS, STATUSS and BSRS,<br>are loaded into their corresponding<br>registers, W, Status and BSR. If<br>'s' = 0, no update of these registers<br>occurs (default). |                                                                                                                                                              |      |      |                    |  |  |  |

| Cycle                         | es:               | 2                                                                                                                                                                                                                                                         | 2                                                                                                                                                            |      |      |                    |  |  |  |

| QC                            | ycle Activity:    |                                                                                                                                                                                                                                                           |                                                                                                                                                              |      |      |                    |  |  |  |

|                               | Q1                | Q2                                                                                                                                                                                                                                                        | Q                                                                                                                                                            | 3    |      | Q4                 |  |  |  |

|                               | Decode            | No<br>operation                                                                                                                                                                                                                                           | Proc<br>Dat                                                                                                                                                  |      |      | POP PC<br>om stack |  |  |  |

|                               | No                | No                                                                                                                                                                                                                                                        | No                                                                                                                                                           |      |      | No                 |  |  |  |

|                               | operation         | operation                                                                                                                                                                                                                                                 | opera                                                                                                                                                        | tion | 0    | peration           |  |  |  |

| _                             |                   |                                                                                                                                                                                                                                                           |                                                                                                                                                              |      |      |                    |  |  |  |

| Exan                          | <u>nple</u> :     | RETURN                                                                                                                                                                                                                                                    | RETURN                                                                                                                                                       |      |      |                    |  |  |  |

|                               | After Instruction | on:                                                                                                                                                                                                                                                       |                                                                                                                                                              |      |      |                    |  |  |  |

PC = TOS

| RLCF Rotate Left f through Carry                 |                                                                                                                                                                                                                                                            |                                 |                                                                                             |                                                                               |  |  |  |  |

|--------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------|---------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------|--|--|--|--|

| Syntax:                                          | RLCF f{                                                                                                                                                                                                                                                    | ,d {,a}}                        |                                                                                             |                                                                               |  |  |  |  |

| Operands:                                        | $0 \le f \le 255$<br>$d \in [0,1]$<br>$a \in [0,1]$                                                                                                                                                                                                        |                                 |                                                                                             |                                                                               |  |  |  |  |

| Operation:                                       | $(f < n >) \rightarrow dest < n + 1 >,$<br>$(f < 7 >) \rightarrow C,$<br>$(C) \rightarrow dest < 0 >$                                                                                                                                                      |                                 |                                                                                             |                                                                               |  |  |  |  |

| Status Affected:                                 | C, N, Z                                                                                                                                                                                                                                                    |                                 |                                                                                             |                                                                               |  |  |  |  |

| Encoding:                                        | 0011                                                                                                                                                                                                                                                       | 01da ff                         | ff                                                                                          | ffff                                                                          |  |  |  |  |

| Description:                                     | one bit to th<br>flag. If 'd' is<br>W. If 'd' is '1<br>in register 'f<br>If 'a' is '0', th<br>selected. If '<br>select the G<br>If 'a' is '0' ar<br>set is enable<br>operates in<br>Addressing<br>$f \le 95$ (5Fh).<br><b>41.2.3 "Byte</b><br>ented Instru | ne Access B<br>a' is '1', the I | n the<br>t is p<br>is sto<br>ank is<br>3SR<br>ded ir<br>al O<br>ever<br>n<br>n<br>ever<br>n | CARRY<br>laced in<br>ored back<br>s<br>is used to<br>nstruction<br>n<br>ffset |  |  |  |  |

| Words:                                           | 1                                                                                                                                                                                                                                                          |                                 |                                                                                             |                                                                               |  |  |  |  |

| Cycles:                                          | 1                                                                                                                                                                                                                                                          |                                 |                                                                                             |                                                                               |  |  |  |  |

| Q Cycle Activity:                                |                                                                                                                                                                                                                                                            |                                 |                                                                                             |                                                                               |  |  |  |  |

| Q1                                               | Q2                                                                                                                                                                                                                                                         | Q3                              |                                                                                             | Q4                                                                            |  |  |  |  |

| Decode                                           | Read<br>register 'f'                                                                                                                                                                                                                                       | Process<br>Data                 |                                                                                             | Write to<br>estination                                                        |  |  |  |  |

| Example:                                         | RLCF                                                                                                                                                                                                                                                       | REG, 0,                         | 0                                                                                           |                                                                               |  |  |  |  |

| Before Instruction    REG = 1110 0110      C = 0 |                                                                                                                                                                                                                                                            |                                 |                                                                                             |                                                                               |  |  |  |  |

| Address          | Name    | Bit 7                                                                 | Bit 6         | Bit 5  | Bit 4  | Bit 3   | Bit 2    | Bit 1 | Bit 0 | Register<br>on page |  |

|------------------|---------|-----------------------------------------------------------------------|---------------|--------|--------|---------|----------|-------|-------|---------------------|--|

| 3FA1h            | T4HLT   | PSYNC                                                                 | CKPOL         | CKSYNC |        |         | 339      |       |       |                     |  |

| 3FA0h            | T4CON   | PSYNC      CKPOL      CKSYNC      MODE        ON      CKPS      OUTPS |               |        |        |         |          |       |       |                     |  |

| 3F9Fh            | T4PR    | PR4                                                                   |               |        |        |         |          |       |       |                     |  |

| 3F9Eh            | T4TMR   | TMR4                                                                  |               |        |        |         |          |       |       |                     |  |

| 3F9Dh            | T5CLK   | CS                                                                    |               |        |        |         |          |       |       |                     |  |

| 3F9Ch            | T5GATE  | GSS                                                                   |               |        |        |         |          |       |       | 316                 |  |

| 3F9Bh            | T5GCON  | GE                                                                    | GPOL          | GTM    | GSPM   | GGO     | 314      |       |       |                     |  |

| 3F9Ah            | T5CON   | —                                                                     | _             | СК     | PS     | _       | NOT_SYNC | RD16  | ON    | 338                 |  |

| 3F99h            | TMR5H   | TMR5H                                                                 |               |        |        |         |          |       |       |                     |  |

| 3F98h            | TMR5L   | TMR5L                                                                 |               |        |        |         |          |       |       | 317                 |  |

| 3F97h            | T6RST   | —                                                                     | _             | —      |        |         | RSEL     |       |       | 336                 |  |

| 3F96h            | T6CLK   | —                                                                     | _             | _      | _      |         | (        | CS    |       | 315                 |  |

| 3F95h            | T6HLT   | PSYNC                                                                 | CKPOL         | CKSYNC |        |         | MODE     |       |       | 339                 |  |

| 3F94h            | T6CON   | ON                                                                    |               | CKPS   |        |         | OU       | TPS   |       | 338                 |  |

| 3F93h            | T6PR    |                                                                       |               |        | P      | R6      |          |       |       | 337                 |  |

| 3F92h            | T6TMR   |                                                                       |               |        | T      | /IR6    |          |       |       | 337                 |  |

| 3F91h -<br>3F80h | _       |                                                                       | Unimplemented |        |        |         |          |       |       |                     |  |

| 3F7Fh            | CCP1CAP |                                                                       |               |        | C      | TS      |          |       |       | 352                 |  |

| 3F7Eh            | CCP1CON | EN                                                                    | _             | OUT    | FMT    |         | 350      |       |       |                     |  |

| 3F7Dh            | CCPR1H  | RH                                                                    |               |        |        |         |          |       |       | 353                 |  |

| 3F7Ch            | CCPR1L  | RL                                                                    |               |        |        |         |          |       |       | 352                 |  |

| 3F7Bh            | CCP2CAP | CTS                                                                   |               |        |        |         |          |       |       | 352                 |  |

| 3F7Ah            | CCP2CON | EN — OUT FMT MODE                                                     |               |        |        |         |          |       | 350   |                     |  |

| 3F79h            | CCPR2H  | RH                                                                    |               |        |        |         |          |       | 353   |                     |  |

| 3F78h            | CCPR2L  |                                                                       | RL            |        |        |         |          |       |       |                     |  |

| 3F77h            | CCP3CAP |                                                                       |               |        | C      | TS      |          |       |       | 352                 |  |

| 3F76h            | CCP3CON | EN – OUT FMT MODE                                                     |               |        |        |         |          |       | 350   |                     |  |

| 3F75h            | CCPR3H  | RH                                                                    |               |        |        |         |          |       | 353   |                     |  |

| 3F74h            | CCPR3L  | RL                                                                    |               |        |        |         |          |       | 352   |                     |  |

| 3F73h            | CCP4CAP | CTS                                                                   |               |        |        |         |          |       | 352   |                     |  |

| 3F72h            | CCP4CON | EN – OUT FMT MODE                                                     |               |        |        |         |          |       | 350   |                     |  |

| 3F71h            | CCPR4H  | RH                                                                    |               |        |        |         |          |       | 353   |                     |  |

| 3F70h            | CCPR4L  |                                                                       |               |        |        | ٦L      |          |       |       | 352                 |  |

| 3F6Fh            | _       |                                                                       |               |        | Unimpl | emented |          |       |       |                     |  |

| 3F6Eh            | PWM5CON | EN                                                                    | _             | OUT    | POL    | _       | _        | —     | _     | 358                 |  |

| 3F6Dh            | PWM5DCH | DC9                                                                   | DC8           | DC7    | DC6    | DC5     | DC4      | DC3   | DC2   | 360                 |  |

| 3F6Dh            | PWM5DCH |                                                                       |               |        | C      | C8      |          |       |       | 360                 |  |

| 3F6Ch            | PWM5DCL | DC1                                                                   | DC0           | —      | —      | -       | _        | —     | —     | 360                 |  |

| 3F6Ch            | PWM5DCL | D                                                                     | С             | _      | _      | —       | _        | —     | _     | 360                 |  |

| 3F6Bh            | _       |                                                                       |               |        | Unimpl | emented |          |       |       |                     |  |

| 3F6Ah            | PWM6CON | EN                                                                    | _             | OUT    | POL    |         | _        | —     | _     | 358                 |  |

| 3F69h            | PWM6DCH | DC9 DC7 DC6 DC5 DC4 DC3 DC2                                           |               |        |        |         |          | 360   |       |                     |  |

| 3F69h            | PWM6DCH | DC                                                                    |               |        |        |         |          | 360   |       |                     |  |

| 3F68h            | PWM6DCL | DC1                                                                   | DC0           | —      | —      | -       | _        | —     | —     | 360                 |  |

| 3F68h            | PWM6DCL | D                                                                     | С             | _      | _      | _       | _        | —     | —     | 360                 |  |

| 3F67h            | —       |                                                                       |               |        | Unimpl | emented |          |       |       |                     |  |

#### TABLE 42-1:REGISTER FILE SUMMARY FOR PIC18(L)F26/27/45/46/47/55/56/57K42 DEVICES

Legend: x = unknown, u = unchanged, — = unimplemented, q = value depends on condition

Note 1: Unimplemented in LF devices.

2: Unimplemented in PIC18(L)F26/27K42.

3: Unimplemented on PIC18(L)F26/27/45/46/47K42 devices.

4: Unimplemented in PIC18(L)F45/55K42.

| — EN | SIRQEN<br>DMODE<br>— | DGO<br>DSTP |                | AIRQ                                                                                 |                                                                   |                                                            |                             | 256                                                                                                         |  |  |  |  |  |

|------|----------------------|-------------|----------------|--------------------------------------------------------------------------------------|-------------------------------------------------------------------|------------------------------------------------------------|-----------------------------|-------------------------------------------------------------------------------------------------------------|--|--|--|--|--|

|      |                      |             |                | —                                                                                    |                                                                   |                                                            |                             | 200                                                                                                         |  |  |  |  |  |

|      |                      | DSTP        | SN             |                                                                                      | AIRQEN                                                            |                                                            | XIP                         | 249                                                                                                         |  |  |  |  |  |

|      | -                    |             |                | /IR                                                                                  | SMC                                                               | DE                                                         | SSTP                        | 248                                                                                                         |  |  |  |  |  |

| -    | _                    |             |                |                                                                                      |                                                                   |                                                            |                             |                                                                                                             |  |  |  |  |  |

| -    | _                    |             | SSA            |                                                                                      |                                                                   |                                                            |                             |                                                                                                             |  |  |  |  |  |

| -    | _                    | SSA         |                |                                                                                      |                                                                   |                                                            |                             |                                                                                                             |  |  |  |  |  |

| _    | SSZ                  |             |                |                                                                                      |                                                                   |                                                            |                             |                                                                                                             |  |  |  |  |  |

| —    | SSZ                  |             |                |                                                                                      |                                                                   |                                                            |                             |                                                                                                             |  |  |  |  |  |

|      | SPTR                 |             |                |                                                                                      |                                                                   |                                                            |                             |                                                                                                             |  |  |  |  |  |

|      | SPTR                 |             |                |                                                                                      |                                                                   |                                                            |                             |                                                                                                             |  |  |  |  |  |

|      |                      |             | SP             | TR                                                                                   |                                                                   |                                                            |                             | 251                                                                                                         |  |  |  |  |  |