Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

E·XFI

| Product Status             | Active                                                                      |

|----------------------------|-----------------------------------------------------------------------------|

| Core Processor             | PIC                                                                         |

| Core Size                  | 8-Bit                                                                       |

| Speed                      | 64MHz                                                                       |

| Connectivity               | I <sup>2</sup> C, LINbus, SPI, UART/USART                                   |

| Peripherals                | Brown-out Detect/Reset, DMA, HLVD, POR, PWM, WDT                            |

| Number of I/O              | 36                                                                          |

| Program Memory Size        | 64KB (32K x 16)                                                             |

| Program Memory Type        | FLASH                                                                       |

| EEPROM Size                | 1K x 8                                                                      |

| RAM Size                   | 4K x 8                                                                      |

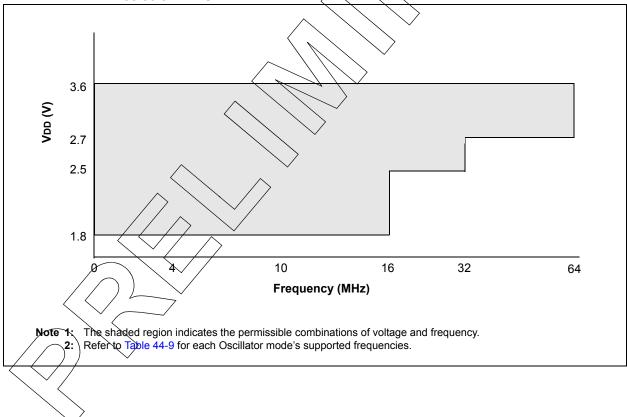

| Voltage - Supply (Vcc/Vdd) | 1.8V ~ 3.6V                                                                 |

| Data Converters            | A/D 35x12b; D/A 1x5b                                                        |

| Oscillator Type            | Internal                                                                    |

| Operating Temperature      | -40°C ~ 125°C (TA)                                                          |

| Mounting Type              | Surface Mount                                                               |

| Package / Case             | 44-TQFP                                                                     |

| Supplier Device Package    | 44-TQFP (10x10)                                                             |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/pic18lf46k42-e-pt |

|                            |                                                                             |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

| 2016-2017 Microchin Technology Inc | <u>ABLE 3:</u> | 48 Din TOED |

|------------------------------------|----------------|-------------|

| n.                                 | RA0            | 2           |

|                                    | RA1            | 2           |

| TABLE 3 | :           |             | 48-PIN ALLO                   | CATION TAI        | BLE FOR PIC1     | 8(L)F5XK42       |                   |                       |                    |                     |                       |                                                                                              |                     |                       |                       |     |                        |                              |                |

|---------|-------------|-------------|-------------------------------|-------------------|------------------|------------------|-------------------|-----------------------|--------------------|---------------------|-----------------------|----------------------------------------------------------------------------------------------|---------------------|-----------------------|-----------------------|-----|------------------------|------------------------------|----------------|

| Ol      | 48-Pin TQFP | 48-Pin UQFN | ADC                           | Voltage Reference | DAC              | Comparators      | Zero Cross Detect | I <sup>2</sup> C      | IdS                | UART                | MSD                   | Timers/SMT                                                                                   | CCP and PWM         | CWG                   | CLC                   | NCO | Clock Reference (CLKR) | Interrupt-on-Change          | Basic          |

| RA0     | 21          | 21          | ANA0                          | —                 | -                | C1IN0-<br>C2IN0- | -                 | -                     | _                  | -                   | -                     | -                                                                                            | _                   | —                     | CLCIN0 <sup>(1)</sup> | _   | -                      | IOCA0                        | _              |

| RA1     | 22          | 22          | ANA1                          | —                 | —                | C1IN1-<br>C2IN1- | _                 | —                     | _                  | —                   | —                     | —                                                                                            | _                   | _                     | CLCIN1 <sup>(1)</sup> | _   | _                      | IOCA1                        | _              |

| RA2     | 23          | 23          | ANA2                          | VREF-             | DAC1OUT1         | C1IN0+<br>C2IN0+ | -                 | —                     | _                  | —                   | —                     | —                                                                                            | _                   | -                     | —                     | —   |                        | IOCA2                        | _              |

| RA3     | 24          | 24          | ANA3                          | VREF+             | _                | C1IN1+           | _                 | _                     |                    | _                   | MDCARL <sup>(1)</sup> | -                                                                                            | _                   | _                     | _                     | _   | _                      | IOCA3                        |                |

| RA4     | 25          | 25          | ANA4                          | _                 | _                | -                |                   | _                     | _                  | _                   | MDCARH <sup>(1)</sup> | T0CKI <sup>(1)</sup>                                                                         |                     | _                     | —                     | _   |                        | IOCA4                        | _              |

| RA5     | 26          | 26          | ANA5                          | _                 | _                |                  | I                 | _                     | SS1 <sup>(1)</sup> | _                   | MDSRC <sup>(1)</sup>  | _                                                                                            | I                   | _                     | _                     | -   | I                      | IOCA5                        |                |

| RA6     | 33          | 33          | ANA6                          | _                 | —                |                  | I                 | —                     |                    | _                   | —                     | —                                                                                            |                     | —                     | —                     |     |                        | IOCA6                        | OSC2<br>CLKOUT |

| RA7     | 32          | 32          | ANA7                          | —                 | —                |                  |                   | —                     |                    | —                   | —                     | —                                                                                            | -                   | —                     | —                     | —   |                        | IOCA7                        | OSC1<br>CLKIN  |

| RB0     | 8           | 8           | ANB0                          | —                 | —                | C2IN1+           | ZCD               | _                     | -                  | —                   | —                     | —                                                                                            | CCP4 <sup>(1)</sup> | CWG1IN <sup>(1)</sup> | -                     | Ι   | -                      | INT0 <sup>(1)</sup><br>IOCB0 | -              |

| RB1     | 9           | 9           | ANB1                          | —                 | _                | C1IN3-<br>C2IN3- | -                 | SCL2 <sup>(3,4)</sup> | -                  | —                   | —                     | —                                                                                            | _                   | CWG2IN <sup>(1)</sup> | -                     |     | _                      | INT1 <sup>(1)</sup><br>IOCB1 | -              |

| RB2     | 10          | 10          | ANB2                          | _                 | —                | -                | -                 | SDA2 <sup>(3,4)</sup> | -                  | _                   | —                     | —                                                                                            | _                   | CWG3IN <sup>(1)</sup> | -                     |     | _                      | INT2 <sup>(1)</sup><br>IOCB2 | _              |

| RB3     | 11          | 11          | ANB3                          | —                 | —                | C1IN2-<br>C2IN2- | _                 | -                     | _                  | —                   | —                     | —                                                                                            | _                   | -                     | —                     | -   | _                      | IOCB3                        | _              |

| RB4     | 16          | 16          | ANB4<br>ADCACT <sup>(1)</sup> | -                 | -                | —                |                   | —                     | -                  | —                   | _                     | T5G <sup>(1)</sup>                                                                           | -                   | -                     | —                     | -   |                        | IOCB4                        | -              |

| RB5     | 17          | 17          | ANB5                          | —                 | —                |                  | I                 | _                     |                    | —                   | —                     | T1G <sup>(1)</sup>                                                                           | CCP3 <sup>(1)</sup> | -                     | _                     | _   |                        | IOCB5                        |                |

| RB6     | 18          | 18          | ANB6                          | _                 | _                | _                |                   | —                     |                    | CTS2 <sup>(1)</sup> | _                     | _                                                                                            |                     | —                     | CLCIN2 <sup>(1)</sup> | _   | l                      | IOCB6                        | ICSPCLK        |

| RB7     | 19          | 19          | ANB7                          | _                 | DAC1OUT2         |                  | -                 | _                     | -                  | RX2 <sup>(1)</sup>  | _                     | T6IN <sup>(1)</sup>                                                                          |                     | _                     | CLCIN3 <sup>(1)</sup> | _   | I                      | IOCB7                        | ICSPDAT        |

| RC0     | 34          | 34          | ANC0                          | —                 | -                | _                |                   | —                     | _                  | —                   | —                     | T1CKI <sup>(1)</sup><br>T3CKI <sup>(1)</sup><br>T3G <sup>(1)</sup><br>SMTWIN1 <sup>(1)</sup> | _                   | —                     | —                     | _   |                        | IOCC0                        | SOSCO          |

| RC1     | 35          | 35          | ANC1                          | _                 | -                |                  |                   | _                     |                    | _                   | _                     | SMTSIG1 <sup>(1)</sup>                                                                       | CCP2 <sup>(1)</sup> | _                     | _                     | _   |                        | IOCC1                        | SOSCI          |

| Note    | 1:          | This is     | a PPS remapp                  | bable input s     | ignal. The input | function may     | y be mov          | ed from the d         | efault locatio     | on shown to         | one of several o      | ther PORTx pins                                                                              | S.                  |                       |                       |     |                        |                              |                |

2: All output signals shown in this row are PPS remappable.

This is a bidirectional signal. For normal module operation, the firmware should map this signal to the same pin in both the PPS input and PPS output registers. 3:

These pins can be configured for I<sup>2</sup>C and SMB<sup>TM</sup> 3.0/2.0 logic levels; The SCLx/SDAx signals may be assigned to any of the RB1/RB2/RC3/RC4/RD0/RD1 pins. PPS assignments to the other pins (e.g., RA5) will operate, but input logic levels will be standard TTL/ST as selected by the INLVL register, instead of the I<sup>2</sup>C specific or SMBus input buffer thresholds. 4:

#### 15.9.4 TRANSFER FROM SFR TO GPR

The following visual reference describes the sequence of events when copying ADC results to a GPR location. The ADC Interrupt Flag can be chosen as the Source Hardware trigger, the Source address can be set to point to the ADC Result registers at 3EEF, the Destination address can be set to point to any GPR location of our choice (Example 0x100).

#### FIGURE 15-8: SFR SPACE TO GPR SPACE TRANSFER

| Instruction<br>Clock       |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |  |

|----------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|

| EN                         |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |  |

| SIRQEN                     |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |  |

| Source Hardware<br>Trigger |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |  |

| DGO                        |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |  |

| DMAxSPTR                   | Ox3EEF         Ox3EF0         S         Ox3EEF         Ox3EEF         Ox3EEF         S         S         S         S         S         S         S         S         S         S         S         S         S         S         S         S         S         S         S         S         S         S         S         S         S         S         S         S         S         S         S         S         S         S         S         S         S         S         S         S         S         S         S         S         S         S         S         S         S         S         S         S         S         S         S         S         S         S         S         S         S         S         S         S         S         S         S         S         S         S         S         S         S         S         S         S         S         S         S         S         S         S         S         S         S         S         S         S         S         S         S         S         S         S         S         S         S         S         S         S </th <th></th>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |  |

| DMAxDPTR                   | 0x100         0x101         ( 0x102         0x103         ( 0x103)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |  |

| DMAxSCNT                   |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |  |

| DMAxDCNT                   |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |  |

| DMA STATE                  | $ \left( \begin{array}{c} \text{IDLE} \end{array} \right) \left( SR^{(1)} \right) DW^{(2)} \left( SR^$ |  |

| DMAxSCNTIF                 |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |  |

| DMAxDCNTIF -               | <u>}</u>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |  |

|                            | DMAxSSA 0x3EEF DMAxDSA 0x100                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |  |

|                            | DMAxSSZ 0x2 DMAxDSZ 0xA                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |  |

|                            | SMODE 0x1 DMODE 0x1                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |  |

| Note 1:                    | SR - Source Read                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |  |

| 2:                         | DW - Destination Write                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |  |

|                      | PPS Input  | Default Pin         | Register              |                   |   |   |                      | In | put Ava | ilable fro | m Selecte | ed POR | Тх       |          |     |   |   |

|----------------------|------------|---------------------|-----------------------|-------------------|---|---|----------------------|----|---------|------------|-----------|--------|----------|----------|-----|---|---|

| Peripheral           | Register   | Selection at<br>POR | Reset Value<br>at POR | PIC18(L)F26/27K42 |   |   | PIC18(L)F45/46/47K42 |    |         |            |           | Р      | IC18(L)F | 55/56/57 | K42 |   |   |

| Interrupt 0          | INTOPPS    | RB0                 | 0b0 1000              | А                 | В | _ | Α                    | В  | _       | —          | —         | Α      | В        | —        | _   |   | — |

| Interrupt 1          | INT1PPS    | RB1                 | 0b0 1001              | А                 | В | — | Α                    | В  | _       | —          | —         | _      | В        | —        | D   | _ | - |

| Interrupt 2          | INT2PPS    | RB2                 | 0b0 1010              | А                 | В | — | А                    | В  | —       | —          | —         | _      | В        | —        | -   | — | F |

| Timer0 Clock         | TOCKIPPS   | RA4                 | 0b0 0100              | А                 | В | — | Α                    | В  | _       | —          | —         | А      | _        | —        | _   | _ | F |

| Timer1 Clock         | T1CKIPPS   | RC0                 | 0b1 0000              | А                 | _ | С | Α                    |    | С       | —          | —         | _      | _        | С        | _   | E | - |

| Timer1 Gate          | T1GPPS     | RB5                 | 0b0 1101              | _                 | В | С | _                    | В  | С       | —          | —         | _      | В        | С        | _   | _ | - |

| Timer3 Clock         | T3CKIPPS   | RC0                 | 0b1 0000              | _                 | В | С | _                    | В  | С       | —          | —         | -      | _        | С        | _   | E | - |

| Timer3 Gate          | T3GPPS     | RC0                 | 0b1 0000              | А                 | — | С | Α                    | _  | С       | —          | —         | А      | _        | С        | _   | — |   |

| Timer5 Clock         | T5CKIPPS   | RC2                 | 0b1 0010              | А                 | _ | С | А                    | _  | С       |            |           | _      | _        | С        | _   | E | _ |

| Timer5 Gate          | T5GPPS     | RB4                 | 0b0 1100              | _                 | В | С | _                    | В  | -       | D          | —         | —      | В        | _        | D   |   | _ |

| Timer2 Clock         | T2INPPS    | RC3                 | 0b1 0011              | А                 | — | С | Α                    | _  | С       | —          | —         | А      | _        | С        | _   |   | _ |

| Timer4 Clock         | T4INPPS    | RC5                 | 0b1 0101              | _                 | В | С | _                    | В  | С       | —          | —         | _      | В        | С        | _   |   | _ |

| Timer6 Clock         | T6INPPS    | RB7                 | 0b0 1111              | _                 | В | С | _                    | В  | -       | D          | _         | —      | В        | _        | D   | _ | _ |

| CCP1                 | CCP1PPS    | RC2                 | 0b1 0010              | _                 | В | С | _                    | В  | С       | _          | _         | —      |          | С        | _   | _ | F |

| CCP2                 | CCP2PPS    | RC1                 | 0b1 0001              | _                 | В | С |                      | В  | С       | _          | _         | —      |          | С        | _   | _ | F |

| CCP3                 | CCP3PPS    | RB5                 | 0b0 1101              | _                 | В | С | _                    | В  | _       | D          | _         | —      | В        | _        | D   | _ | _ |

| CCP4                 | CCP4PPS    | RB0                 | 0b0 1000              | _                 | В | С | _                    | В  | _       | D          | _         | —      | В        | _        | D   | _ | _ |

| SMT1 Window          | SMT1WINPPS | RC0                 | 0b1 0000              | _                 | В | С |                      | В  | С       | —          | —         | _      | _        | С        | _   | _ | F |

| SMT1 Signal          | SMT1SIGPPS | RC1                 | 0b1 0001              | _                 | В | С |                      | В  | С       | _          | _         | —      |          | С        | _   | _ | F |

| CWG1                 | CWG1PPS    | RB0                 | 0b0 1000              | _                 | В | С | _                    | В  | _       | D          | _         | —      | В        | _        | D   | _ | _ |

| CWG2                 | CWG2PPS    | RB1                 | 0b0 1001              | _                 | В | С |                      | В  | _       | D          | _         | —      | В        | _        | D   | _ | _ |

| CWG3                 | CWG3PPS    | RB2                 | 0b0 1010              | _                 | В | С | _                    | В  | _       | D          | _         | —      | В        | _        | D   | _ | _ |

| DSM1 Carrier<br>Low  | MD1CARLPPS | RA3                 | 0b0 0011              | А                 | _ | С | A                    | —  |         | D          | —         | A      | —        | —        | D   | — | - |

| DSM1 Carrier<br>High | MD1CARHPPS | RA4                 | 0b0 0100              | А                 | — | С | A                    | —  |         | D          | —         | A      | —        | —        | D   | — | — |

| DSM1 Source          | MD1SRCPPS  | RA5                 | 0b0 0101              | А                 | _ | С | Α                    | —  | _       | D          | _         | А      |          | _        | D   | _ | _ |

| CLCx Input 1         | CLCIN0PPS  | RA0                 | 0000 0000             | А                 | — | С | А                    | _  | С       | —          | —         | Α      | —        | С        | _   | — | — |

| CLCx Input 2         | CLCIN1PPS  | RA1                 | 0b0 0001              | А                 | — | С | А                    | _  | С       | —          | —         | Α      | —        | С        | _   | — | — |

| CLCx Input 3         | CLCIN2PPS  | RB6                 | 0b0 1110              | _                 | В | С | —                    | В  | -       | D          | —         | _      | В        | —        | D   | — | — |

| CLCx Input 4         | CLCIN3PPS  | RB7                 | 0b0 1111              | _                 | В | С |                      | В  |         | D          | _         | _      | В        | _        | D   | _ | _ |

## TABLE 17-1: PPS INPUT REGISTER DETAILS

## TABLE 17-1: PPS INPUT REGISTER DETAILS

|                           | PPS Input  | Default Pin         | Register              |       |          |      |   | Ir                   | nput Avai | ilable from | n Selecte | d POR                | Tx |   |   |   |   |

|---------------------------|------------|---------------------|-----------------------|-------|----------|------|---|----------------------|-----------|-------------|-----------|----------------------|----|---|---|---|---|

| Peripheral                | Register   | Selection at<br>POR | Reset Value<br>at POR | PIC18 | (L)F26/2 | 7K42 |   | PIC18(L)F45/46/47K42 |           |             |           | PIC18(L)F55/56/57K42 |    |   |   |   |   |

| ADC Conversion<br>Trigger | ADACTPPS   | RB4                 | 0b0 1100              | —     | В        | С    | - | В                    | -         | D           | —         | -                    | В  | — | D | — |   |

| SPI1 Clock                | SPI1SCKPPS | RC3                 | 0b1 0011              | _     | В        | С    | _ | В                    | С         |             |           | —                    | В  | С | _ | _ | _ |

| SPI1 Data                 | SPI1SDIPPS | RC4                 | 0b1 0100              | _     | В        | С    | _ | В                    | С         |             |           | —                    | В  | С |   | _ | _ |

| SPI1 Slave<br>Select      | SPI1SSPPS  | RA5                 | 0b0 0101              | A     | —        | С    | A | _                    | —         | D           | —         | A                    | —  | - | D | _ | — |

| I <sup>2</sup> C1 Clock   | I2C1SCLPPS | RC3                 | 0b1 0011              | _     | В        | С    | _ | В                    | С         |             |           | —                    | В  | С |   | _ | _ |

| I <sup>2</sup> C1 Data    | I2C1SDAPPS | RC4                 | 0b1 0100              | _     | В        | С    | _ | В                    | С         |             |           | —                    | В  | С |   | _ | _ |

| I <sup>2</sup> C2 Clock   | I2C2SCLPPS | RB1                 | 0b0 1001              | _     | В        | С    |   | В                    | _         | D           |           | —                    | В  | _ | D | _ | _ |

| I <sup>2</sup> C2 Data    | I2C2SDAPPS | RB2                 | 0b0 1010              | _     | В        | С    | _ | В                    | _         | D           |           | —                    | В  | _ | D | _ | _ |

| UART1 Receive             | U1RXPPS    | RC7                 | 0b1 0111              | _     | В        | С    | _ | В                    | С         |             |           | —                    | _  | С |   | _ | F |

| UART1 Clear To<br>Send    | U1CTSPPS   | RC6                 | 0b1 0110              | —     | В        | С    | — | В                    | С         | —           | —         | —                    | _  | С | — |   | F |

| UART2 Receive             | U2RXPPS    | RB7                 | 0b0 1111              |       | В        | С    |   | В                    |           | D           |           | _                    | В  | — | D | _ | _ |

| UART2 Clear To<br>Send    | U2CTSPPS   | RB6                 | 0b0 1110              | —     | В        | С    | — | В                    | —         | D           | —         | —                    | В  |   | D |   | — |

## TABLE 17-2: PPS OUTPUT REGISTER DETAILS

|                          |                         |     |             |     |   |      | Device       | Configurati | on |   |     |           |           |          |   |

|--------------------------|-------------------------|-----|-------------|-----|---|------|--------------|-------------|----|---|-----|-----------|-----------|----------|---|

| RxyPPS<5:0>              | Pin Rxy Output Source   | PIC | 18(L)F26/27 | K42 |   | PIC1 | 8(L)F45/46/4 | 47K42       |    |   | P   | PIC18(L)F | 55/56/57k | (42      |   |

| 0b11 1111 -<br>0b11 0011 |                         |     |             |     |   | Rese | rved         |             |    |   |     |           |           |          |   |

| 0b11 0010                | ADGRDB                  | A   | _           | С   | А | _    | С            | _           | _  | A | I _ |           | <u> </u>  | <u> </u> | F |

| 0b11 0001                | ADGRDA                  | A   | _           | С   | A | _    | С            | _           | _  | А | _   | _         | _         | _        | F |

| 0b11 0000                | CWG3D                   | A   | _           | С   | А | _    | _            | D           | _  | A | _   | _         | D         | _        | _ |

| 0b10 1111                | CWG3C                   | A   |             | С   | А | _    | _            | D           |    | Α |     |           | D         | _        | _ |

| 0b10 1110                | CWG3B                   | A   |             | С   | А | _    | _            | _           | E  | Α |     |           | _         | E        | _ |

| 0b10 1101                | CWG3A                   | _   | В           | С   | _ | В    | С            | _           | _  | _ | В   | С         | _         | _        | _ |

| 0b10 1100                | CWG2D                   | _   | В           | С   | _ | В    | _            | D           | _  | _ | В   | _         | D         | _        | _ |

| 0b10 1011                | CWG2C                   | _   | В           | С   | _ | В    | _            | D           | _  | _ | В   | _         | D         | _        | _ |

| 0b10 1010                | CWG2B                   | _   | В           | С   | _ | В    | _            | D           | _  | _ | В   | —         | D         | —        | _ |

| 0b10 1001                | CWG2A                   | _   | В           | С   | _ | В    | С            | _           | _  | _ | В   | С         | _         | _        | _ |

| 0b10 1000                | DSM1                    | А   | _           | С   | A | _    | _            | D           | _  | Α | —   | —         | D         | -        | — |

| 0b10 0111                | CLKR                    | —   | В           | С   | _ | В    | С            | _           | _  | _ | В   | _         | —         | E        | — |

| 0b10 0110                | NCO1                    | А   | _           | С   | A | _    | _            | D           | _  | Α | —   | —         | D         | —        | _ |

| 0b10 0101                | TMR0                    | —   | В           | С   | _ | В    | С            | _           | —  | _ | —   | С         | —         | _        | F |

| 0b10 0100                | I <sup>2</sup> C2 (SDA) | —   | В           | С   | — | В    | _            | D           | _  | _ | В   | —         | D         | _        | _ |

| 0b10 0011                | I <sup>2</sup> C2 (SCL) | —   | В           | С   | _ | В    | _            | D           | _  | _ | В   | —         | D         | _        | _ |

| 0b10 0010                | I <sup>2</sup> C1 (SDA) | —   | В           | С   | — | В    | С            | _           | _  | _ | В   | С         | —         | _        | — |

| 0b10 0001                | I <sup>2</sup> C1 (SCL) |     | В           | С   | _ | В    | С            | _           | —  | _ | В   | С         | _         |          | _ |

| 0b10 0000                | SPI1 (SS)               | А   | _           | С   | А | _    | _            | D           | _  | А | —   | —         | D         | _        | _ |

| 0b01 1111                | SPI1 (SDO)              | _   | В           | С   | _ | В    | С            | _           | —  | — | В   | С         | _         | _        | _ |

| 0b01 1110                | SPI1 (SCK)              | —   | В           | С   | _ | В    | С            | _           | _  | — | В   | С         | _         | _        | — |

| 0b01 1101                | C2OUT                   | А   | _           | С   | А | —    | —            | —           | E  | А | —   | —         | —         | E        | — |

| 0b01 1100                | C1OUT                   | А   | _           | С   | А | _    | _            | D           | _  | А | —   | —         | D         | —        | — |

| 0b01 1011 -<br>0b01 1001 | Reserved                |     |             |     |   |      |              |             |    |   |     |           |           |          |   |

| 0b01 1000                | UART2 (RTS)             | _   | В           | С   | _ | В    | —            | D           | —  | — | В   | _         | D         | —        | — |

| 0b01 0111                | UART2 (TXDE)            | _   | В           | С   | _ | В    | —            | D           | —  | — | В   | —         | D         | _        | — |

| 0b01 0110                | UART2 (TX)              | _   | В           | С   | — | В    | —            | D           | —  | — | В   | —         | D         | _        | — |

| 0b01 0101                | UART1 (RTS)             | —   | В           | С   | _ | В    | С            | _           | —  | — | _   | С         | —         | —        | F |