Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

#### Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

E·XFI

| Details                    |                                                                             |

|----------------------------|-----------------------------------------------------------------------------|

| Product Status             | Active                                                                      |

| Core Processor             | PIC                                                                         |

| Core Size                  | 8-Bit                                                                       |

| Speed                      | 64MHz                                                                       |

| Connectivity               | I <sup>2</sup> C, LINbus, SPI, UART/USART                                   |

| Peripherals                | Brown-out Detect/Reset, DMA, HLVD, POR, PWM, WDT                            |

| Number of I/O              | 36                                                                          |

| Program Memory Size        | 64KB (32K x 16)                                                             |

| Program Memory Type        | FLASH                                                                       |

| EEPROM Size                | 1K x 8                                                                      |

| RAM Size                   | 4K x 8                                                                      |

| Voltage - Supply (Vcc/Vdd) | 1.8V ~ 3.6V                                                                 |

| Data Converters            | A/D 35x12b; D/A 1x5b                                                        |

| Oscillator Type            | Internal                                                                    |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                           |

| Mounting Type              | Surface Mount                                                               |

| Package / Case             | 44-VQFN Exposed Pad                                                         |

| Supplier Device Package    | 44-QFN (8x8)                                                                |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/pic18lf46k42-i-ml |

|                            |                                                                             |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

#### 6.1 **Power-on Reset (POR)**

The POR circuit holds the device in Reset until VDD has reached an acceptable level for minimum operation. Slow rising VDD, fast operating speeds or analog performance may require greater than minimum VDD. The PWRT, BOR or MCLR features can be used to extend the start-up period until all device operation conditions have been met.

### 6.2 Brown-out Reset (BOR)

The BOR circuit holds the device in Reset when VDD reaches a selectable minimum level. Between the POR and BOR, complete voltage range coverage for execution protection can be implemented.

The Brown-out Reset module has four operating modes controlled by the BOREN<1:0> bits in Configuration Words. The four operating modes are:

- · BOR is always on

- BOR is off when in Sleep

- BOR is controlled by software

- BOR is always off

Refer to Table 6-1 for more information.

The Brown-out Reset voltage level is selectable by configuring the BORV<1:0> bits in Configuration Words.

A VDD noise rejection filter prevents the BOR from triggering on small events. If VDD falls below VBOR for a duration greater than parameter TBORDC, the device will reset. See Table 44-13 for more information.

#### 6.2.1 BOR IS ALWAYS ON

When the BOREN bits of Configuration Words are programmed to '11', the BOR is always on. The device start-up will be delayed until the BOR is ready and VDD is higher than the BOR threshold.

BOR protection is active during Sleep. The BOR does not delay wake-up from Sleep.

#### 6.2.2 BOR IS OFF IN SLEEP

When the BOREN bits of Configuration Words are programmed to '10', the BOR is on, except in Sleep. The device start-up will be delayed until the BOR is ready and VDD is higher than the BOR threshold.

BOR protection is not active during Sleep. The device wake-up will be delayed until the BOR is ready.

### 6.2.3 BOR CONTROLLED BY SOFTWARE

When the BOREN bits of Configuration Words are programmed to '01', the BOR is controlled by the SBOREN bit of the BORCON register. The device startup is not delayed by the BOR ready condition or the VDD level.

BOR protection begins as soon as the BOR circuit is ready. The status of the BOR circuit is reflected in the BORRDY bit of the BORCON register.

BOR protection is unchanged by Sleep.

#### 6.2.4 BOR AND BULK ERASE

BOR is forced ON during PFM Bulk Erase operations to make sure that a safe erase voltage is maintained for a successful erase cycle.

During Bulk Erase, the BOR is enabled at 2.45V for F and LF devices, even if it is configured to some other value. If VDD falls, the erase cycle will be aborted, but the device will not be reset.

### 9.3 Interrupt Priority

The final priority level for any pending source of interrupt is determined first by the user-assigned priority of that source in the IPRx register, then by the natural order priority within the IVT. The sections below detail the operation of Interrupt priorities.

### 9.3.1 USER (SOFTWARE) PRIORITY

User-assigned interrupt priority is enabled by setting the IPEN bit in the INTCON0 register (Register 9-1). Each peripheral interrupt source can be assigned a high or low priority level by the user. The userassignable interrupt priority control bits for each interrupt are located in the IPRx registers (Registers 9-25 through 9-35).

The interrupts are serviced based on predefined interrupt priority scheme defined below.

- Interrupts set by the user as high-priority interrupt have higher precedence of execution. High-priority interrupts will override a low-priority request when:

- a) A low priority interrupt has been requested or its request is already pending.

- b) A low- and high-priority interrupt are triggered concurrently, i.e., on the same instruction cycle<sup>(1)</sup>.

- c) A low-priority interrupt was requested and the corresponding Interrupt Service Routine is currently executing. In this case, the lower priority interrupt routine will complete executing after the high-priority interrupt has been serviced<sup>(2)</sup>.

- 2. Interrupts set by the user as a low priority have the lower priority of execution and are preempted by any high-priority interrupt.

- Interrupts defined with the same software priority cannot preempt or interrupt each other. Concurrent pending interrupts with the same user priority are resolved using the natural order priority. (when MVECEN = ON) or in the order the interrupt flag bits are polled in the ISR (when MVECEN = OFF).

- Note 1: When a high priority interrupt preempts a concurrent low priority interrupt, the GIEL bit may be cleared in the high priority Interrupt Service Routine. If the GIEL bit is cleared, the low priority interrupt will NOT be serviced even if it was originally requested. The corresponding interrupt flag needs to be cleared in user code.

- 2: When a high priority interrupt is requested while a low priority Interrupt Service Routine is executing, the GIEL bit may be cleared in the high priority Interrupt Service Routine. The pending low priority interrupt will resume even if the GIEL bit is cleared.

#### **Register Definitions: Interrupt Control REGISTER 9-1:** INTCON0: INTERRUPT CONTROL REGISTER 0 R/W-0/0 R/W-0/0 R/W-0/0 U-0 U-0 R/W-1/1 R/W-1/1 R/W-1/1 **GIE/GIEH** GIEL **IPEN** INT2EDG INT1EDG INT0EDG bit 7 bit 0 Legend: R = Readable bit W = Writable bit U = Unimplemented bit, read as '0' -n = Value at POR '1' = Bit is set '0' = Bit is cleared x = Bit is unknown bit 7 **GIE/GIEH:** Global Interrupt Enable bits If IPEN = 0: GIE: 1 = Enables all unmasked interrupts 0 = Disables all interrupts If IPEN = 1: GIEH: 1 = Enables all unmasked high priority interrupts: bit also needs to be set for enabling low priority interrupts 0 = Disables all interrupts bit 6 GIEL: Global Low Priority Interrupt Enable bit If IPEN = 0: Reserved, read as '0' If IPEN = 1: GIEL: 1 = Enables all unmasked low priority interrupts, GIEH also needs to be set for low priority interrupts 0 = Disables all low priority bit 5 IPEN: Interrupt Priority Enable bit 1 = Enable priority levels on interrupts 0 = Disable priority levels on interrupts; all interrupts are treated as high priority interrupts bit 4-3 Unimplemented: Read as '0' bit 2 INT2EDG: External Interrupt 2 Edge Select bit 1 = Interrupt on rising edge of INT2 pin 0 = Interrupt on falling edge of INT2 pin bit 1 INT1EDG: External Interrupt 1 Edge Select bit 1 = Interrupt on rising edge of INT1 pin 0 = Interrupt on falling edge of INT1 pin INTOEDG: External Interrupt 0 Edge Select bit bit 0 1 = Interrupt on rising edge of INT0 pin 0 = Interrupt on falling edge of INTO pin

9.12

|                 | <b>3-32</b> . II K7.         |                                    |                |              |                  | 1                |              |  |  |  |

|-----------------|------------------------------|------------------------------------|----------------|--------------|------------------|------------------|--------------|--|--|--|

| U-0             | U-0                          | R/W-1/1                            | R/W-1/1        | R/W-1/1      | U-0              | R/W-1/1          | R/W-1/1      |  |  |  |

| _               | -                            | INT2IP                             | CLC2IP         | CWG2IP       | _                | CCP2IP           | TMR4IP       |  |  |  |

| bit 7           |                              |                                    |                |              | -                |                  | bit (        |  |  |  |

|                 |                              |                                    |                |              |                  |                  |              |  |  |  |

| Legend:         |                              |                                    |                |              |                  |                  |              |  |  |  |

| R = Readab      | le bit                       | W = Writable                       | bit            | U = Unimple  | mented bit, read | as '0'           |              |  |  |  |

| u = Bit is un   | changed                      | x = Bit is unki                    | nown           | -n/n = Value | at POR and BO    | R/Value at all o | other Resets |  |  |  |

| '1' = Bit is se | et                           | '0' = Bit is cle                   | ared           |              |                  |                  |              |  |  |  |

|                 |                              |                                    |                |              |                  |                  |              |  |  |  |

| bit 7-6         | Unimpleme                    | n <b>ted:</b> Read as '            | 0'             |              |                  |                  |              |  |  |  |

| bit 5           | INT2IP: Exte                 | ernal Interrupt 2                  | Interrupt Prio | rity bit     |                  |                  |              |  |  |  |

|                 | 1 = High pri                 |                                    |                |              |                  |                  |              |  |  |  |

|                 | 0 = Low price                | prity                              |                |              |                  |                  |              |  |  |  |

| bit 4           | CLC2IP: CL                   | C2 Interrupt Prie                  | ority bit      |              |                  |                  |              |  |  |  |

|                 | 1 = High price               | •                                  |                |              |                  |                  |              |  |  |  |

|                 | 0 = Low price                | •                                  |                |              |                  |                  |              |  |  |  |

| bit 3           |                              | NG2 Interrupt F                    | riority bit    |              |                  |                  |              |  |  |  |

|                 | 1 = High prior               |                                    |                |              |                  |                  |              |  |  |  |

| <b>h</b> # 0    | 0 = Low pric                 | •                                  | ~              |              |                  |                  |              |  |  |  |

| bit 2           | -                            | nted: Read as '                    |                |              |                  |                  |              |  |  |  |

| bit 1           |                              | CCP2IP: CRC Interrupt Priority bit |                |              |                  |                  |              |  |  |  |

|                 | 1 = High pri<br>0 = Low pric | ,                                  |                |              |                  |                  |              |  |  |  |

| bit 0           | •                            | •                                  | iority hit     |              |                  |                  |              |  |  |  |

|                 |                              | IR4 Interrupt Pr                   |                |              |                  |                  |              |  |  |  |

|                 | 1 = High prid0 = Low prid    | ,                                  |                |              |                  |                  |              |  |  |  |

|                 | 5 2017 pric                  |                                    |                |              |                  |                  |              |  |  |  |

### REGISTER 9-32: IPR7: PERIPHERAL INTERRUPT PRIORITY REGISTER 7

#### REGISTER 9-33: IPR8: PERIPHERAL INTERRUPT PRIORITY REGISTER 8

| R/W-1/1 | R/W-1/1 | U-0 | U-0 | U-0 | U-0 | U-0 | U-0   |

|---------|---------|-----|-----|-----|-----|-----|-------|

| TMR5GIP | TMR5IP  | —   | —   | —   | —   | —   | —     |

| bit 7   |         |     |     |     |     |     | bit 0 |

| Legend:              |                      |                                                       |

|----------------------|----------------------|-------------------------------------------------------|

| R = Readable bit     | W = Writable bit     | U = Unimplemented bit, read as '0'                    |

| u = Bit is unchanged | x = Bit is unknown   | -n/n = Value at POR and BOR/Value at all other Resets |

| '1' = Bit is set     | '0' = Bit is cleared |                                                       |

| bit 7   | TMR5GIP: TMR5 Gate Interrupt Priority bit |

|---------|-------------------------------------------|

|         | 1 = High priority                         |

|         | 0 = Low priority                          |

| bit 6   | TMR5IP: TMR5 Interrupt Priority bit       |

|         | 1 = High priority                         |

|         | 0 = Low priority                          |

| bit 5-0 | Unimplemented: Read as '0'                |

© 2017 Microchip Technology Inc.

#### REGISTER 13-5: NVMDAT: DATA EEPROM MEMORY DATA

| R/W-0/0         | R/W-0/0 | R/W-0/0           | R/W-0/0 | R/W-0/0          | R/W-0/0          | R/W-0/0  | R/W-0/0 |

|-----------------|---------|-------------------|---------|------------------|------------------|----------|---------|

|                 |         |                   | DAT     | <7:0>            |                  |          |         |

| bit 7           |         |                   |         |                  |                  |          | bit 0   |

|                 |         |                   |         |                  |                  |          |         |

| Legend:         |         |                   |         |                  |                  |          |         |

| R = Readable    | bit     | W = Writable I    | bit     | U = Unimpler     | nented bit, read | d as '0' |         |

| x = Bit is unkn | own     | '0' = Bit is clea | ared    | '1' = Bit is set |                  |          |         |

| -n = Value at F | POR     |                   |         |                  |                  |          |         |

bit 7-0 **DAT<7:0>:** The value of the data memory word returned from NVMADR after a Read command, or the data written by a Write command.

# TABLE 13-4: SUMMARY OF REGISTERS ASSOCIATED WITH NONVOLATILE MEMORY CONTROL

| Name                   | Bit 7 | Bit 6                 | Bit 5 | Bit 4 | Bit 3   | Bit 2 | Bit 1 | Bit 0 | Register<br>on Page |

|------------------------|-------|-----------------------|-------|-------|---------|-------|-------|-------|---------------------|

| NVMCON1                | REG   | <1:0>                 | —     | FREE  | WRERR   | WREN  | WR    | RD    | 210                 |

| NVMCON2                |       | Unlock Pattern        |       |       |         |       |       |       |                     |

| NVMADRL                |       |                       |       | NVMA  | DR<7:0> |       |       |       | 211                 |

| NVMADRH <sup>(1)</sup> | —     | — — — — — NVMADR<9:8> |       |       |         |       |       |       | 211                 |

| NVMDAT                 |       |                       |       | NVME  | AT<7:0> |       |       |       | 212                 |

Legend: — = unimplemented, read as '0'. Shaded bits are not used during EEPROM access.

\*Page provides register information.

**Note 1:** The NVMADRH register is not implemented on PIC18(L)F45/55K42.

| R/W-0/0          | R/W-0/0                                           | R/W-0/0                                                              | R/W-0/0                                          | R/W-0/0                                                                | R/W-0/0              | R/W-0/0            | R/W-0/0 |

|------------------|---------------------------------------------------|----------------------------------------------------------------------|--------------------------------------------------|------------------------------------------------------------------------|----------------------|--------------------|---------|

| DMC              | DDE<1:0>                                          | DSTP                                                                 | SMR<1:0>                                         |                                                                        | SMODE<1:0>           |                    | SSTP    |

| bit 7            |                                                   |                                                                      |                                                  |                                                                        |                      |                    | bit 0   |

| Legend:          |                                                   |                                                                      |                                                  |                                                                        |                      |                    |         |

| R = Reada        | able bit                                          | W = Writable bit                                                     |                                                  | U = Unimplemen                                                         | ted bit, read as '0' |                    |         |

| u = Bit is u     | inchanged                                         | x = Bit is unknow                                                    | vn                                               | -n/n = Value at P                                                      | OR and BOR/Valu      | ue at all other Re | sets    |

| bit 7-6<br>bit 5 | 11 = Resen<br>10 = DMAx<br>01 = DMAx<br>00 = DMAx | DPTR<15:0> is                                                        | decremented a<br>incremented af<br>mains unchang | fter each transfe<br>ter each transfer<br>ed after each tra            | completion           | n                  |         |

|                  |                                                   |                                                                      |                                                  | n Counter reload<br>ation Counter rel                                  | -                    |                    |         |

| bit 4-3          | 1x = DMAx<br>01 = DMAx                            | ource Memory R<br>SSA<21:0> poir<br>SSA<21:0> poir<br>SSA<21:0> poir | nts to Data EEP<br>nts to Program I              | ROM<br>Flash Memory                                                    |                      |                    |         |

| bit 2-1          | 11 = Reser<br>10 = DMAx<br>01 = DMAx              | SPTR<21:0> is                                                        | decremented a incremented af                     | on bits<br>fter each transfe<br>ter each transfer<br>ed after each tra | completion           | n                  |         |

| bit 0            | SSTP: Source                                      | e Counter Reloa                                                      | ad Stop bit                                      |                                                                        | ·                    |                    |         |

- 1 = SIRQEN bit is cleared when Source Counter reloads

- 0 = SIRQEN bit is not cleared when Source Counter reloads

|           |       | _      |               |               | [         |         |        |       | 1 1                 |

|-----------|-------|--------|---------------|---------------|-----------|---------|--------|-------|---------------------|

| Name      | Bit 7 | Bit 6  | Bit 5         | Bit 4         | Bit 3     | Bit 2   | Bit 1  | Bit 0 | Register<br>on Page |

| DMAxCON0  | EN    | SIRQEN | DGO           | —             | —         | AIRQEN  | _      | XIP   | 248                 |

| DMAxCON1  | DMOD  | E<1:0> | DSTP          | SMR           | <1:0>     | SMOD    | E<1:0> | SSTP  | 249                 |

| DMAxBUF   | DBUF7 | DBUF6  | DBUF5         | DBUF4         | DBUF3     | DBUF2   | DBUF1  | DBUF0 | 250                 |

| DMAxSSAL  |       |        |               | SSA           | <7:0>     |         |        |       | 250                 |

| DMAxSSAH  |       |        |               | SSA<          | :15:8>    |         |        |       | 250                 |

| DMAxSSAU  | —     | _      |               |               | SSA<      | 21:16>  |        |       | 251                 |

| DMAxSPTRL |       |        |               | SPTR          | <7:0>     |         |        |       | 251                 |

| DMAxSPTRH |       |        |               | SPTR          | <15:8>    |         |        |       | 251                 |

| DMAxSPTRU | —     | _      |               |               | SPTR<     | :21:16> |        |       | 252                 |

| DMAxSSZL  |       |        |               | SSZ<7:0>      |           |         |        |       |                     |

| DMAxSSZH  | _     | —      |               | — — SSZ<11:8> |           |         |        |       | 252                 |

| DMAxSCNTL |       |        |               | SCNT          | <7:0>     |         |        |       | 253                 |

| DMAxSCNTH | _     | _      |               | _             |           | SCNT    | <11:8> |       | 253                 |

| DMAxDSAL  |       |        |               | DSA           | <7:0>     |         |        |       | 253                 |

| DMAxDSAH  |       |        |               | DSA<          | :15:8>    |         |        |       | 254                 |

| DMAxDPTRL |       |        |               | DPTR          | <7:0>     |         |        |       | 254                 |

| DMAxDPTRH |       |        |               | DPTR          | <15:8>    |         |        |       | 254                 |

| DMAxDSZL  |       |        |               | DSZ           | <7:0>     |         |        |       | 255                 |

| DMAxDSZH  | —     | —      | — — DSZ<11:8> |               |           |         |        |       | 255                 |

| DMAxDCNTL |       |        | DCNT<7:0>     |               |           |         |        |       | 255                 |

| DMAxDCNTH | —     | —      | _             | —             |           | DCNT    | <11:8> |       | 256                 |

| DMAxSIRQ  | _     |        |               |               | SIRQ<6:0> |         |        |       | 256                 |

| DMAxAIRQ  |       |        |               |               | AIRQ<6:0> |         |        |       | 256                 |

## TABLE 15-3: SUMMARY OF REGISTERS ASSOCIATED WITH DMA

Legend: — = unimplemented location, read as '0'. Shaded cells are not used by DMA.

#### 22.5.1 SOFTWARE GATE MODE

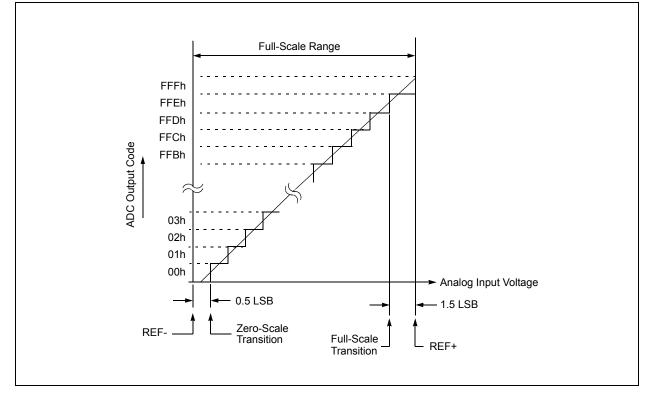

The timer increments with each clock input when ON = 1and does not increment when ON = 0. When the T2TMR count equals the T2PR period count the timer resets on the next clock and continues counting from 0. Operation with the ON bit software controlled is illustrated in Figure 22-4. With T2PR = 5, the counter advances until T2TMR = 5, and goes to zero with the next clock.

| MODE                               | 060000                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |       |

|------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------|

|                                    |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |       |

| Instruction <sup>(1)</sup> ——(BSF) | (BCF)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |       |

| ON                                 |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |       |

| TxPR                               | 5                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |       |

| TxTMR 0 1                          | $2 \left( 3 \right) \left( 4 \right) \left( 5 \right) \left( 0 \right) \left( 1 \right) \left( 2 \right) \left( 3 \right) \left( 4 \right) \left( 5 \right) \left( 0 \right) \left( 1 \right) \left( 2 \right) \left( 3 \right) \left( 4 \right) \left( 5 \right) \left( 0 \right) \left( 1 \right) \left( 2 \right) \left( 3 \right) \left( 4 \right) \left( 5 \right) \left( 0 \right) \left( 1 \right) \left( 2 \right) \left( 3 \right) \left( 4 \right) \left( 5 \right) \left( 0 \right) \left( 1 \right) \left( 2 \right) \left( 3 \right) \left( 4 \right) \left( 5 \right) \left( 0 \right) \left( 1 \right) \left( 2 \right) \left( 3 \right) \left( 4 \right) \left( 5 \right) \left( 0 \right) \left( 1 \right) \left( 2 \right) \left( 3 \right) \left( 4 \right) \left( 5 \right) \left($ | ) (1) |

| TMRx_postscaled                    |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |       |

| PWM Duty<br>Cycle                  | 3                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |       |

| PWM Output                         |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |       |

| R/W/HS/HC-0/0      | R/W-0/0         | R/W-0/0          | R/W-1/1             | R/W-0/0                               | R/W-1/1           | U-0           | U-0           |

|--------------------|-----------------|------------------|---------------------|---------------------------------------|-------------------|---------------|---------------|

| SHUTDOWN           | REN             | LSBE             | )<1:0>              | LSAC                                  | C<1:0>            | —             | —             |

| bit 7              |                 |                  |                     |                                       |                   |               | bit 0         |

|                    |                 |                  |                     |                                       |                   |               |               |

| Legend:            |                 |                  |                     |                                       |                   | (0)           |               |

| R = Readable bit   |                 | W = Writable     |                     | •                                     | nented bit, read  |               |               |

| u = Bit is unchang | ged             | x = Bit is unk   |                     |                                       | t POR and BOF     |               | other Resets  |

| '1' = Bit is set   |                 | '0' = Bit is cle | eared               | HS/HC = Bit is                        | s set/cleared by  | hardware      |               |

| q = Value depend   | s on condition  | ۱                |                     |                                       |                   |               |               |

| bit 7              | SHUTDOWN        | I: Auto-Shutdo   | wn Event Stat       | tus bit <sup>(1,2)</sup>              |                   |               |               |

|                    | 1 = An auto     | o-shutdown sta   | te is in effect     |                                       |                   |               |               |

|                    | 0 = No auto     | o-shutdown ev    | ent has occuri      | red                                   |                   |               |               |

| bit 6              | REN: Auto-R     | Restart Enable   | bit                 |                                       |                   |               |               |

|                    |                 | start is enable  |                     |                                       |                   |               |               |

|                    |                 | start is disable |                     |                                       |                   |               |               |

| bit 5-4            |                 |                  |                     | Shutdown State                        |                   |               |               |

|                    |                 |                  |                     | /hen an auto-sh<br>/hen an auto-sh    |                   |               |               |

|                    | 0               |                  |                     | an auto-shutdo                        |                   |               |               |

|                    | 00 = The ina    | active state of  | the pin, inclu      | iding polarity, is<br>nutdown event c | placed on CV      |               | the required  |

| bit 3-2            | LSAC<1:0>:      | CWGxA and        | CWGxC Auto-         | Shutdown State                        | e Control bits    |               |               |

|                    | •               | •                |                     | /hen an auto-sh                       |                   |               |               |

|                    | •               | •                |                     | /hen an auto-sh                       |                   |               |               |

|                    |                 |                  |                     | an auto-shutdo<br>iding polarity, is  |                   |               | the required  |

|                    |                 |                  |                     | nutdown event o                       | •                 |               | ine required  |

| bit 1-0            | Unimplemen      | nted: Read as    | <b>'</b> 0 <b>'</b> |                                       |                   |               |               |

| Note 1: This bi    | t may be writt  | en while EN =    | 0 (Register 26      | 6-1), to place the                    | e outputs into th | ie shutdown d | onfiguration. |

|                    | utputs will rem |                  |                     | intil the next risi                   | -                 |               | -             |

#### REGISTER 26-6: CWGxAS0: CWG AUTO-SHUTDOWN CONTROL REGISTER 0

| FIGURE 30-2:             | On Off Keying | (OOK) Synchroni | zation   |       |                  |

|--------------------------|---------------|-----------------|----------|-------|------------------|

| Carrier Low (CARL)       |               |                 |          |       |                  |

| Carrier High (CARH)      |               |                 |          |       |                  |

| Modulator (BIT)          | Ż             | ,               | <u>`</u> |       |                  |

| CHSYNC = 1<br>CLSYNC = 0 |               |                 |          |       |                  |

| CHSYNC = 1<br>CLSYNC = 1 |               |                 |          |       |                  |

| CHSYNC = 0<br>CLSYNC = 0 |               |                 |          | X/\_/ | $\sum_{i=1}^{i}$ |

| CHSYNC = 0<br>CLSYNC = 1 |               | <u>`</u>        |          | į́    | \_/ <u>\</u>     |

|                          |               |                 |          |       |                  |

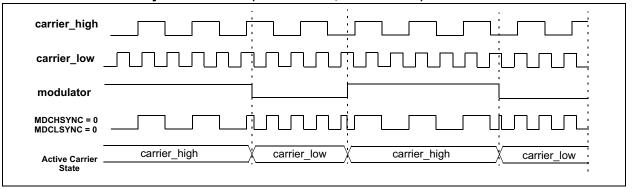

#### FIGURE 30-3: No Synchronization (CHSYNC = 0, CLSYNC = 0)

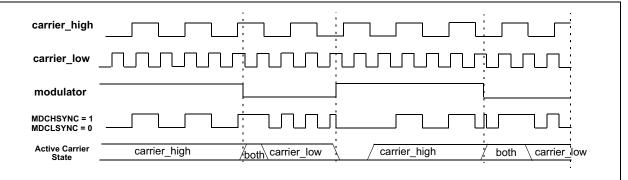

#### Carrier High Synchronization (CHSYNC = 1, CLSYNC = 0)

### 31.2.2 UART ASYNCHRONOUS RECEIVER

The Asynchronous mode is typically used in RS-232 systems. The receiver block diagram is shown in Figure 31-2. The data is received on the RX pin and drives the data recovery block. The data recovery block is actually a high-speed shifter operating at 4 or 16 times the baud rate, whereas the serial Receive Shift Register (RSR) operates at the bit rate. When all bits of the character have been shifted in, they are immediately transferred to a two character First-In-First-Out (FIFO) memory. The FIFO buffering allows reception of two complete characters and the start of a third character before software must start servicing the UART receiver. The FIFO registers and RSR are not directly accessible by software. Access to the received data is via the UXRXB register.

#### 31.2.2.1 Enabling the Receiver

The UART receiver is enabled for asynchronous operation by configuring the following control bits:

- RXEN = 1

- MODE<3:0> = 0h through 3h

- UxBRGH:L = desired baud rate

- RXPPS = code for desired input pin

- Input pin ANSEL bit = 0

- ON = 1

All other UART control bits are assumed to be in their default state.

Setting the RXEN bit in the UxCON0 register enables the receiver circuitry of the UART. Setting the MODE<3:0> bits in the UxCON0 register configures the UART for the desired asynchronous mode. Setting the ON bit in the UxCON1 register enables the UART. The TRIS bit corresponding to the selected RX I/O pin must be set to configure the pin as an input.

Note: If the RX function is on an analog pin, the corresponding ANSEL bit must be cleared for the receiver to function.

#### 31.2.2.2 Receiving Data

Data is recovered from the bit stream by timing to the center of the bits and sampling the input level. In High-Speed mode, there are four BRG clocks per bit and only one sample is taken per bit. In Normal-Speed mode, there are 16 BRG clocks per bit and three samples are taken per bit.

The receiver data recovery circuit initiates character reception on the falling edge of the Start bit. The Start bit, is always a '0'. The Start bit is qualified in the middle of the bit. In Normal-Speed mode only, the Start bit is also qualified at the leading edge of the bit. The following paragraphs describe the majority detect sampling of Normal-Speed mode.

The falling edge starts the baud rate generator (BRG) clock. The input is sampled at the first and second BRG clocks.

If both samples are high then the falling edge is deemed a glitch and the UART returns to the Start bit detection state without generating an error.

If either sample is low, the data recovery circuit continues counting BRG clocks and takes samples at clock counts 7, 8, and 9. When less than two samples are low, the Start bit is deemed invalid and the data recovery circuit aborts character reception, without generating an error, and resumes looking for the falling edge of the Start bit.

When two or more samples are low, the Start bit is deemed valid and the data recovery continues. After a valid Start bit is detected, the BRG clock counter continues and resets at count 16. This is the beginning of the first data bit.

The data recovery circuit counts BRG clocks from the beginning of the bit and takes samples at clocks 7, 8, and 9. The bit value is determined from the majority of the samples. The resulting '0' or '1' is shifted into the RSR.The BRG clock counter continues and resets at count 16. This sequence repeats until all data bits have been sampled and shifted into the RSR.

After all data bits have been shifted in, the first Stop bit is sampled. Stop bits are always a '1'. If the bit sampling determines that a '0' is in the Stop bit position, the framing error is set for this character. Otherwise, the framing error is cleared for this character. See **Section 31.2.2.4 "Receive Framing Error"** for more information on framing errors.

#### 31.2.2.3 Receive Interrupts

Immediately after all data bits and the Stop bit have been received, the character in the RSR is transferred to the UART receive FIFO. The UxRXIF interrupt flag in the respective PIR register is set at this time, provided it is not being suppressed.

The UxRXIF is suppressed by any of the following:

- FERIF if FERIE is set

- PERIF if PERIE is set

This suspends DMA transfer of data until software processes the error and reads UxRXB to advance the FIFO beyond the error.

UxRXIF interrupts are enabled by setting all of the following bits:

- UxRXIE, Interrupt Enable bit in the PIE register

- GIE, Global Interrupt Enable bits in the INTCON0

register

The UxRXIF interrupt flag bit will be set when not suppressed and there is an unread character in the FIFO, regardless of the state of interrupt enable bits. Reading the UxRXB register will transfer the top character out of the FIFO and reduce the FIFO contents by one. The UxRXIF interrupt flag bit is read-only, it cannot be set or cleared by software.

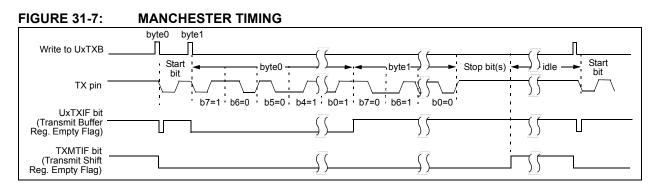

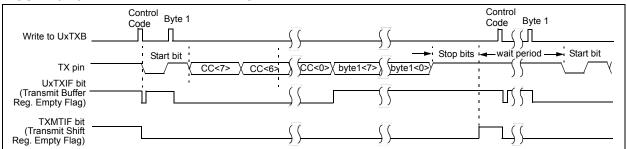

#### FIGURE 31-8: DALI FRAME TIMING

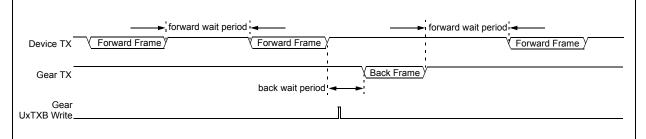

### FIGURE 31-9: DALI FORWARD/BACK FRAME TIMING

### 31.7 General Purpose Manchester (UART1 only)

General purpose Manchester is a subset of the DALI mode. When the UxP1L register is cleared, there is no minimum wait time between frames. This allows full and half-duplex operation because writes to the UxTXB are not held waiting for a receive operation to complete.

General purpose Manchester operation maintains all other aspects of DALI mode such as:

- Single-pulse Start bit

- · Most Significant bit first

- · No stop periods between back-to-back bytes