Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

#### Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

E·XFI

| Details                    |                                                                              |

|----------------------------|------------------------------------------------------------------------------|

| Product Status             | Active                                                                       |

| Core Processor             | PIC                                                                          |

| Core Size                  | 8-Bit                                                                        |

| Speed                      | 64MHz                                                                        |

| Connectivity               | I²C, LINbus, SPI, UART/USART                                                 |

| Peripherals                | Brown-out Detect/Reset, DMA, HLVD, POR, PWM, WDT                             |

| Number of I/O              | 36                                                                           |

| Program Memory Size        | 64KB (32K x 16)                                                              |

| Program Memory Type        | FLASH                                                                        |

| EEPROM Size                | 1K x 8                                                                       |

| RAM Size                   | 4K x 8                                                                       |

| Voltage - Supply (Vcc/Vdd) | 1.8V ~ 3.6V                                                                  |

| Data Converters            | A/D 35x12b; D/A 1x5b                                                         |

| Oscillator Type            | Internal                                                                     |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                            |

| Mounting Type              | Surface Mount                                                                |

| Package / Case             | 44-VQFN Exposed Pad                                                          |

| Supplier Device Package    | 44-QFN (8x8)                                                                 |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/pic18lf46k42t-i-ml |

|                            |                                                                              |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

#### 2.5 External Oscillator Pins

Many microcontrollers have options for at least two oscillators: a high-frequency primary oscillator and a low-frequency secondary oscillator (refer to Section 7.0 "Oscillator Module (with Fail-Safe Clock Monitor)" for details).

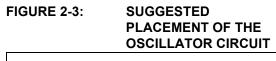

The oscillator circuit should be placed on the same side of the board as the device. Place the oscillator circuit close to the respective oscillator pins with no more than 0.5 inch (12 mm) between the circuit components and the pins. The load capacitors should be placed next to the oscillator itself, on the same side of the board.

Use a grounded copper pour around the oscillator circuit to isolate it from surrounding circuits. The grounded copper pour should be routed directly to the MCU ground. Do not run any signal traces or power traces inside the ground pour. Also, if using a two-sided board, avoid any traces on the other side of the board where the crystal is placed.

Layout suggestions are shown in Figure 2-3. In-line packages may be handled with a single-sided layout that completely encompasses the oscillator pins. With fine-pitch packages, it is not always possible to completely surround the pins and components. A suitable solution is to tie the broken guard sections to a mirrored ground layer. In all cases, the guard trace(s) must be returned to ground.

In planning the application's routing and I/O assignments, ensure that adjacent port pins, and other signals in close proximity to the oscillator, are benign (i.e., free of high frequencies, short rise and fall times, and other similar noise).

For additional information and design guidance on oscillator circuits, refer to these Microchip application notes, available at the corporate website (www.microchip.com):

- AN826, "Crystal Oscillator Basics and Crystal Selection for rfPIC<sup>™</sup> and PICmicro<sup>®</sup> Devices"

- AN849, "Basic PICmicro<sup>®</sup> Oscillator Design"

- AN943, "Practical PICmicro<sup>®</sup> Oscillator Analysis and Design"

- AN949, "Making Your Oscillator Work"

### 2.6 Unused I/Os

Unused I/O pins should be configured as outputs and driven to a logic low state. Alternatively, connect a 1 k $\Omega$  to 10 k $\Omega$  resistor to Vss on unused pins and drive the output to logic low.

#### 9.5 Context Saving

The Interrupt controller supports a two-level deep context saving (Main routine context and Low ISR context). Refer to state machine shown in Figure 9-6 for details.

The Program Counter (PC) is saved on the dedicated device PC stack. CPU registers saved include STATUS, WREG, BSR, FSR0/1/2, PRODL/H and PCLATH/U.

After WREG has been saved to the context registers, the resolved vector number of the interrupt source to be serviced is copied into WREG. Context save and restore operation is completed by the interrupt controller based on current state of the interrupts and the order in which they were sent to the CPU.

Context save/restore works the same way in both states of MVECEN. When IPEN = 0, there is only one level interrupt active. Hence, only the main context is saved when an interrupt is received.

#### 9.5.1 ACCESSING SHADOW REGISTERS

The Interrupt controller automatically saves the context information in the shadow registers available in Bank 56. Both the saved context values (i.e., main routine and low ISR) can be accessed using the same set of shadow registers. By clearing the SHADLO bit in the SHADCON register (Register 9-43), the CPU register values saved for main routine context can accessed, and by setting the SHADLO bit of the CPU register, values saved for low ISR context can accessed. Low ISR context is automatically restored to the CPU registers upon exiting the high ISR. Similarly, the main context is automatically restored to the CPU registers upon exiting the low ISR.

The Shadow registers in Bank 56 are readable and writable, so if the user desires to modify the context, then the corresponding shadow register should be modified and the value will be restored when exiting the ISR. Depending on the user's application, other registers may also need to be saved.

# PIC18(L)F26/27/45/46/47/55/56/57K42

| R/W-1/1 |

|---------|---------|---------|---------|---------|---------|---------|---------|

| ANSELx7 | ANSELx6 | ANSELx5 | ANSELx4 | ANSELx3 | ANSELx2 | ANSELx1 | ANSELx0 |

| bit 7   |         |         |         |         |         |         | bit 0   |

|         |         |         |         |         |         |         |         |

#### REGISTER 16-4: ANSELX: ANALOG SELECT REGISTER

Legend:R = Readable bitW = Writable bitU = Unimplemented bit, read as '0''1' = Bit is set'0' = Bit is clearedx = Bit is unknown-n/n = Value at POR and BOR/Value at all other Resets

bit 7-0

- ANSELx<7:0>: Analog Select on Pins Rx<7:0>

- 1 = Digital Input buffers are disabled.

- 0 = ST and TTL input devices are enabled

#### TABLE 16-5: ANALOG SELECT PORT REGISTERS

| Name                  | Bit 7   | Bit 6   | Bit 5   | Bit 4   | Bit 3   | Bit 2   | Bit 1   | Bit 0   |

|-----------------------|---------|---------|---------|---------|---------|---------|---------|---------|

| ANSELA                | ANSELA7 | ANSELA6 | ANSELA5 | ANSELA4 | ANSELA3 | ANSELA2 | ANSELA1 | ANSELA0 |

| ANSELB                | ANSELB7 | ANSELB6 | ANSELB5 | ANSELB4 | ANSELB3 | ANSELB2 | ANSELB1 | ANSELB0 |

| ANSELC                | ANSELC7 | ANSELC6 | ANSELC5 | ANSELC4 | ANSELC3 | ANSELC2 | ANSELC1 | ANSELC0 |

| ANSELD <sup>(1)</sup> | ANSELD7 | ANSELD6 | ANSELD5 | ANSELD4 | ANSELD3 | ANSELD2 | ANSELD1 | ANSELD0 |

| ANSELE <sup>(1)</sup> | _       | _       | _       | —       | _       | ANSELE2 | ANSELE1 | ANSELE0 |

| ANSELF <sup>(2)</sup> | ANSELF7 | ANSELF6 | ANSELF5 | ANSELF4 | ANSELF3 | ANSELF2 | ANSELF1 | ANSELF0 |

Note 1: Unimplemented in PIC18(L)F26/27K42.

2: Unimplemented in PIC18(L)F26/45/46/47K42.

#### 23.4.5 PWM DUTY CYCLE

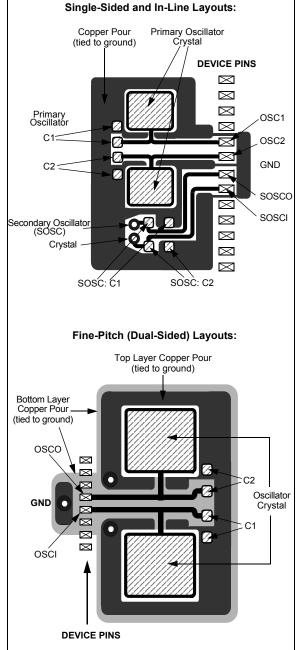

The PWM duty cycle is specified by writing a 10-bit value to the CCPRxH:CCPRxL register pair. The alignment of the 10-bit value is determined by the FMT bit of the CCPxCON register (see Figure 23-5). The CCPRxH:CCPRxL register pair can be written to at any time; however the duty cycle value is not latched into the 10-bit buffer until after a match between T2PR and T2TMR.

Equation 23-2 is used to calculate the PWM pulse width. Equation 23-3 is used to calculate the PWM duty cycle ratio.

FIGURE 23-5: PWM 10-BIT ALIGNMENT

#### EQUATION 23-2: PULSE WIDTH

| Pulse Width = (CCPRx) | H:CCPRxL register pair) • |

|-----------------------|---------------------------|

| Tosc                  | • (TMR2 Prescale Value)   |

# EQUATION 23-3: DUTY CYCLE RATIO

$$Duty Cycle Ratio = \frac{(CCPRxH:CCPRxL register pair)}{4(T2PR + 1)}$$

CCPRxH:CCPRxL register pair are used to double buffer the PWM duty cycle. This double buffering provides glitchless PWM operation.

The 8-bit timer T2TMR register is concatenated with either the 2-bit internal system clock (Fosc), or two bits of the prescaler, to create the 10-bit time base. The system clock is used if the Timer2 prescaler is set to 1:1.

When the 10-bit time base matches the CCPRxH:CCPRxL register pair, then the CCPx pin is cleared (see Figure 23-4).

#### 23.4.6 PWM RESOLUTION

The resolution determines the number of available duty cycles for a given period. For example, a 10-bit resolution will result in 1024 discrete duty cycles, whereas an 8-bit resolution will result in 256 discrete duty cycles.

The maximum PWM resolution is ten bits when T2PR is 255. The resolution is a function of the T2PR register value as shown by Equation 23-4.

#### EQUATION 23-4: PWM RESOLUTION

Resolution =

$$\frac{\log[4(T2PR+1)]}{\log(2)}$$

bits

**Note:** If the pulse-width value is greater than the period, the assigned PWM pin(s) will remain unchanged.

PIC18(L)F26/27/45/46/47/55/56/57K42

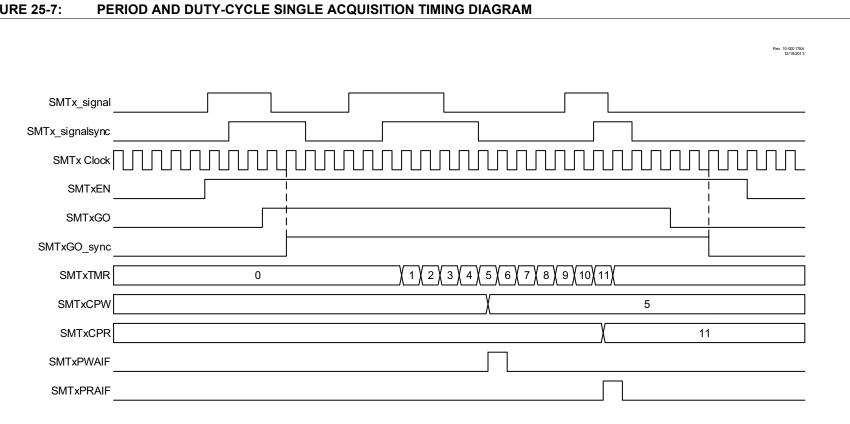

## FIGURE 25-7:

PIC18(L)F26/27/45/46/47/55/56/57K42

#### 28.2 FIXED DUTY CYCLE MODE

In Fixed Duty Cycle (FDC) mode, every time the accumulator overflows (NCO\_overflow), the output is toggled. This provides a 50% duty cycle, provided that the increment value remains constant. For more information, see Figure 28-2.

#### 28.3 PULSE FREQUENCY MODE

In Pulse Frequency (PF) mode, every time the Accumulator overflows, the output becomes active for one or more clock periods. Once the clock period expires, the output returns to an inactive state. This provides a pulsed output. The output becomes active on the rising clock edge immediately following the overflow event. For more information, see Figure 28-2.

The value of the active and inactive states depends on the polarity bit, POL in the NCO1CON register.

The PF mode is selected by setting the PFM bit in the NCO1CON register.

28.3.1 OUTPUT PULSE-WIDTH CONTROL

When operating in PF mode, the active state of the output can vary in width by multiple clock periods. Various pulse widths are selected with the PWS<2:0> bits in the NCO1CLK register.

When the selected pulse width is greater than the Accumulator overflow time frame, then DDS operation is undefined.

#### 28.4 OUTPUT POLARITY CONTROL

The last stage in the NCO module is the output polarity. The POL bit in the NCO1CON register selects the output polarity. Changing the polarity while the interrupts are enabled will cause an interrupt for the resulting output transition. The NCO output signal is available to most of the other peripherals available on the device.

#### 28.5 Interrupts

When the accumulator overflows (NCO\_overflow), the NCO Interrupt Flag bit, NCO1IF, of the PIR4 register is set. To enable the interrupt event (NCO\_interrupt), the following bits must be set:

- · EN bit of the NCO1CON register

- NCO1IE bit of the PIE4 register

- · GIE/GIEH bit of the INTCON0 register

The interrupt must be cleared by software by clearing the NCO1IF bit in the Interrupt Service Routine.

#### 28.6 Effects of a Reset

All of the NCO registers are cleared to zero as the result of a Reset.

#### 28.7 Operation in Sleep

The NCO module operates independently from the system clock and will continue to run during Sleep, provided that the clock source selected remains active.

The HFINTOSC remains active during Sleep when the NCO module is enabled and the HFINTOSC is selected as the clock source, regardless of the system clock source selected.

In other words, if the HFINTOSC is simultaneously selected as the system clock and the NCO clock source, when the NCO is enabled, the CPU will go idle during Sleep, but the NCO will continue to operate and the HFINTOSC will remain active.

This will have a direct effect on the Sleep mode current.

#### 30.11 Register Definitions: Modulation Control

Long bit name prefixes for the Modulation peripheral is shown below. Refer to **Section 1.3.2.2 "Long Bit Names**" for more information.

| Peripheral | Bit Name Prefix |

|------------|-----------------|

| MD1        | MD1             |

#### REGISTER 30-1: MD1CON0: MODULATION CONTROL REGISTER 0

| R/W-0/0 | U-0 | R-0/0 | R/W-0/0 | U-0 | U-0 | U-0 | R/W-0/0 |

|---------|-----|-------|---------|-----|-----|-----|---------|

| EN      | —   | OUT   | OPOL    | —   | —   | —   | BIT     |

| bit 7   |     |       |         |     |     |     | bit 0   |

| Legend:              |                      |                                                       |

|----------------------|----------------------|-------------------------------------------------------|

| R = Readable bit     | W = Writable bit     | U = Unimplemented bit, read as '0'                    |

| u = Bit is unchanged | x = Bit is unknown   | -n/n = Value at POR and BOR/Value at all other Resets |

| '1' = Bit is set     | '0' = Bit is cleared |                                                       |

| bit 7   | EN: Modulator Module Enable bit                                                                                                                                                             |

|---------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|         | 1 = Modulator module is enabled and mixing input signals                                                                                                                                    |

|         | 0 = Modulator module is disabled and has no output                                                                                                                                          |

| bit 6   | Unimplemented: Read as '0'                                                                                                                                                                  |

| bit 5   | OUT: Modulator Output bit                                                                                                                                                                   |

|         | Displays the current output value of the Modulator module. <sup>(1)</sup>                                                                                                                   |

| bit 4   | OPOL: Modulator Output Polarity Select bit                                                                                                                                                  |

|         | 1 = Modulator output signal is inverted; idle high output                                                                                                                                   |

|         | 0 = Modulator output signal is not inverted; idle low output                                                                                                                                |

| bit 3-1 | Unimplemented: Read as '0'                                                                                                                                                                  |

| bit 0   | BIT: Allows software to manually set modulation source input to module <sup>(2)</sup>                                                                                                       |

|         | 1 = Modulator selects Carrier High                                                                                                                                                          |

|         | 0 = Modulator selects Carrier Low                                                                                                                                                           |

| Note 1: | The modulated output frequency can be greater and asynchronous from the clock that updates this register bit, the bit value may not be valid for higher speed modulator or carrier signals. |

2: BIT bit must be selected as the modulation source in the MD1SRC register for this operation.

### 31.21 Register Definitions: UART Control

Long bit name prefixes for the UART peripherals are shown below. Refer to **Section 1.3 "Register and Bit naming conventions**" for more information.

| Peripheral | Bit Name Prefix |

|------------|-----------------|

| UART 1     | U1              |

| UART 2     | U2              |

#### REGISTER 31-1: UxCON0: UART CONTROL REGISTER 0

| R/W-0/0 | R/W/HS/HC-0/0 | R/W-0/0 | R/W-0/0 | R/W-0/0 | R/W-0/0 | R/W-0/0 | R/W-0/0 |

|---------|---------------|---------|---------|---------|---------|---------|---------|

| BRGS    | ABDEN         | TXEN    | RXEN    |         | MODE    | <3:0>   |         |

| bit 7   |               |         |         |         |         |         | bit 0   |

| Legend:              |                      |                                                       |

|----------------------|----------------------|-------------------------------------------------------|

| R = Readable bit     | W = Writable bit     | U = Unimplemented bit, read as '0'                    |

| u = Bit is unchanged | x = Bit is unknown   | -n/n = Value at POR and BOR/Value at all other Resets |

| '1' = Bit is set     | '0' = Bit is cleared | HC = Hardware clear                                   |

| bit 7               | <ul> <li>BRGS: Baud rate Generator Speed Select bit</li> <li>1 = Baud rate generator is high speed with 4 baud clocks per bit</li> <li>0 = Baud rate generator is normal speed with 16 baud clocks per bit</li> </ul>                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

|---------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| bit 6               | <ul> <li>ABDEN: Auto-baud Detect Enable bit<sup>(3)</sup></li> <li>1 = Auto-baud is enabled. Receiver is waiting for Sync character (0x55)</li> <li>0 = Auto-baud is not enabled or auto-baud is complete</li> </ul>                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

| bit 5               | <ul> <li>TXEN: Transmit Enable Control bit<sup>(2)</sup></li> <li>1 = Transmit is enabled. TX output pin drive is forced on when transmission is active, and controlled by PORT TRIS control when transmission is idle.</li> <li>0 = Transmit is disabled. TX output pin drive is controlled by PORT TRIS control</li> </ul>                                                                                                                                                                                                                                                                                                                                                                 |

| bit 4               | RXEN: Receive Enable Control bit <sup>(2)</sup><br>1 = Receiver is enabled<br>0 = Receiver is disabled                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

| bit 3-0             | MODE<3:0>: UART Mode Select bits <sup>(1)</sup><br>1111 = Reserved<br>1100 = Reserved<br>1101 = Reserved<br>1100 = LIN Master/Slave mode <sup>(4)</sup><br>1011 = LIN Slave-Only mode <sup>(4)</sup><br>1010 = DMX mode <sup>(4)</sup><br>1001 = DALI Control Gear mode <sup>(4)</sup><br>1000 = DALI Control Device mode <sup>(4)</sup><br>1011 = Reserved<br>0110 = Reserved<br>0110 = Reserved<br>0101 = Reserved<br>0101 = Reserved<br>0102 = Asynchronous 9-bit UART Address mode. 9th bit: 1 = address, 0 = data<br>0011 = Asynchronous 8-bit UART mode with 9th bit even parity<br>0010 = Asynchronous 8-bit UART mode with 9th bit odd parity<br>0010 = Asynchronous 8-bit UART mode |

| Note 1:<br>2:<br>3: | Changing the UART MODE while ON = 1 may cause unexpected results.<br>Clearing TXEN or RXEN will not clear the corresponding buffers. Use TXBE or RXBE to clear the buffers.<br>When MODE = 100x, then ABDEN bit is ignored.                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

4: UART1 only.

#### REGISTER 31-8: UxBRGL: UART BAUD RATE GENERATOR LOW REGISTER

| R/W-0/0          | R/W-0/0 | R/W-0/0           | R/W-0/0 | R/W-0/0        | R/W-0/0          | R/W-0/0          | R/W-0/0     |

|------------------|---------|-------------------|---------|----------------|------------------|------------------|-------------|

|                  |         |                   | BRG     | <7:0>          |                  |                  |             |

| bit 7            |         |                   |         |                |                  |                  | bit 0       |

|                  |         |                   |         |                |                  |                  |             |

| Legend:          |         |                   |         |                |                  |                  |             |

| R = Readable     | bit     | W = Writable      | bit     | U = Unimpler   | nented bit, read | as '0'           |             |

| u = Bit is uncha | anged   | x = Bit is unkr   | iown    | -n/n = Value a | at POR and BO    | R/Value at all c | ther Resets |

| '1' = Bit is set |         | '0' = Bit is clea | ared    |                |                  |                  |             |

bit 7-0 BRG<7:0>: Least Significant Byte of Baud Rate Generator

#### REGISTER 31-9: UxBRGH: UART BAUD RATE GENERATOR HIGH REGISTER

| R/W-0/0     | ) R/W-0/0 R/W-0/0 R/W-0/0 R/W-0/0 |  |  |  | R/W-0/0 | R/W-0/0 |  |  |

|-------------|-----------------------------------|--|--|--|---------|---------|--|--|

| BRG<15:8>   |                                   |  |  |  |         |         |  |  |

| bit 7 bit C |                                   |  |  |  |         |         |  |  |

| Legend:              |                      |                                                       |

|----------------------|----------------------|-------------------------------------------------------|

| R = Readable bit     | W = Writable bit     | U = Unimplemented bit, read as '0'                    |

| u = Bit is unchanged | x = Bit is unknown   | -n/n = Value at POR and BOR/Value at all other Resets |

| '1' = Bit is set     | '0' = Bit is cleared |                                                       |

bit 7-0 BRG<15:8>: Most Significant Byte of Baud Rate Generator

**Note 1:** The UxBRG registers should only be written when ON = 0.

**2:** Maximum BRG value when MODE = 100x and BRGS = 1 is 0x7FFE.

3: Maximum BRG value when MODE = '100x' and BRGS = 0 is 0x1FFE.

# PIC18(L)F26/27/45/46/47/55/56/57K42

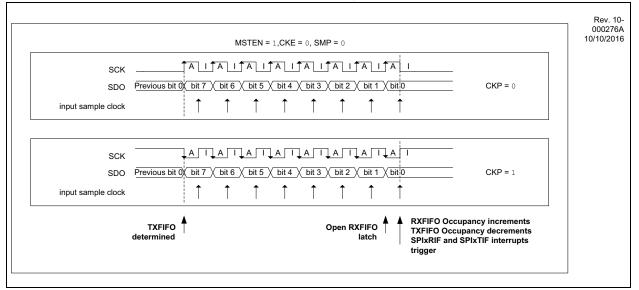

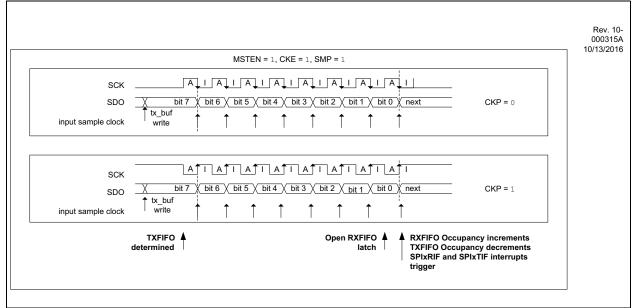

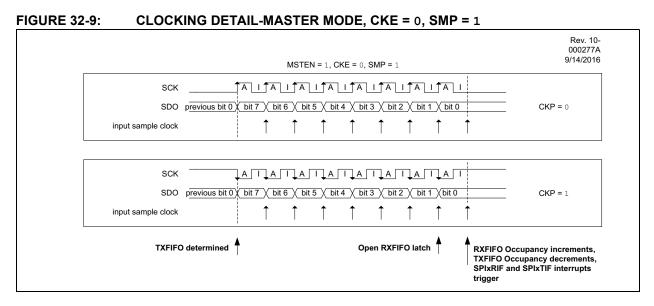

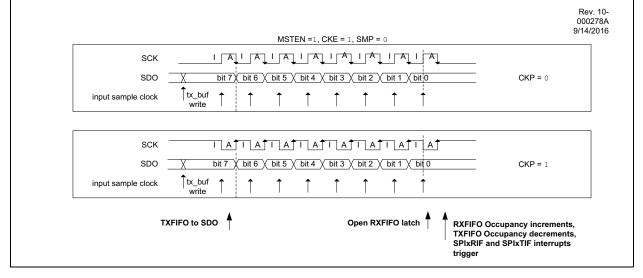

#### FIGURE 32-7: CLOCKING DETAIL-MASTER MODE, CKE/SMP = 0/0

FIGURE 32-10: CLOCKING DETAIL-MASTER MODE, CKE = 1, SMP = 0

#### 32.5.6.3 SCK Start-Up Delay

When starting an SPI data exchange, the master device sets the SS output (either through hardware or software) and then triggers the module to send data. These data triggers are synchronized to the clock selected by the SPIxCLK register before the first SCK pulse appears, usually requiring one or two clocks of the selected clock.

The SPI module includes synchronization delays on SCK generation specifically designed to ensure that the Slave Select output timing is correct, without requiring precision software timing loops.

When the value of the SPIxBAUD register is a small number (indicating higher SCK frequencies), the synchronization delay can be relatively long between setting SS and the first SCK. With larger values of SPIxBAUD (indicating lower SCK frequencies), this delay is much smaller and the first SCK can appear relatively quickly after SS is set.

By default, the SPI module inserts a ½ baud delay (half of the period of the clock selected by the SPIxCLK register) before the first SCK pulse. This allows for systems with a high SPIxBAUD value to have extra setup time before the first clock. Setting the FST bit in SPIxCON1 removes this additional delay, allowing systems with low SPIxBAUD values (and thus, long synchronization delays) to forego this unnecessary extra delay.

# 36.0 ANALOG-TO-DIGITAL CONVERTER WITH COMPUTATION (ADC<sup>2</sup>) MODULE

The Analog-to-Digital Converter with Computation (ADC<sup>2</sup>) allows conversion of an analog input signal to a 12-bit binary representation of that signal. This device uses analog inputs, which are multiplexed into a single sample and hold circuit. The output of the sample and hold is connected to the input of the converter. The converter generates a 12-bit binary result via successive approximation and stores the conversion result into the ADC result registers (ADRESH:ADRESL register pair).

Additionally, the following features are provided within the ADC module:

- 13-bit Acquisition Timer

- Hardware Capacitive Voltage Divider (CVD) support:

- 13-bit Precharge Timer

- Adjustable sample and hold capacitor array

- Guard ring digital output drive

- · Automatic repeat and sequencing:

- Automated double sample conversion for CVD

- Two sets of result registers (Result and Previous result)

- Auto-conversion trigger

- Internal retrigger

- Computation features:

- Averaging and Low-Pass Filter functions

- Reference Comparison

- 2-level Threshold Comparison

- Selectable Interrupts

Figure 36-1 shows the block diagram of the ADC.

The ADC voltage reference is software selectable to be either internally generated or externally supplied.

The ADC can generate an interrupt upon completion of a conversion and upon threshold comparison. These interrupts can be used to wake up the device from Sleep.

| R-0/0            | R-0/0                                                                                   | R-0/0                                                                                                                                                                                              | R/HS/HC-0/0                                                                                                                     | U-0                  | R-0/0            | R-0/0            | R-0/0        |

|------------------|-----------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------|----------------------|------------------|------------------|--------------|

| AOV              | UTHR                                                                                    | LTHR                                                                                                                                                                                               | MATH                                                                                                                            | -                    |                  | STAT<2:0>        | 10.0         |

| bit 7            |                                                                                         |                                                                                                                                                                                                    |                                                                                                                                 |                      |                  |                  | bit          |

|                  |                                                                                         |                                                                                                                                                                                                    |                                                                                                                                 |                      |                  |                  |              |

| Legend:          |                                                                                         |                                                                                                                                                                                                    |                                                                                                                                 |                      |                  |                  |              |

| R = Readable     | e bit                                                                                   | W = Writable                                                                                                                                                                                       | bit                                                                                                                             | U = Unimple          | mented bit, rea  | d as '0'         |              |

| u = Bit is uncl  | hanged                                                                                  | x = Bit is unki                                                                                                                                                                                    | nown                                                                                                                            | -n/n = Value         | at POR and BC    | R/Value at all o | other Resets |

| '1' = Bit is set | :                                                                                       | '0' = Bit is cle                                                                                                                                                                                   | ared                                                                                                                            | HS/HC = Bit          | is set/cleared b | y hardware       |              |

| bit 7            | 1 = ADC acc                                                                             |                                                                                                                                                                                                    | erflow bit<br>C filter or ERR<br>filter and ERR                                                                                 |                      |                  | ed               |              |

| bit 6            | UTHR: ADC Module Greater-than Upper Threshold Flag bit<br>1 = ERR >UTH<br>0 = ERR ≤ UTH |                                                                                                                                                                                                    |                                                                                                                                 |                      |                  |                  |              |

| bit 5            | <b>LTHR</b> : ADC M<br>1 = ERR < LT<br>0 = ERR ≥ LT                                     | ГН                                                                                                                                                                                                 | an Lower Three                                                                                                                  | shold Flag bit       |                  |                  |              |

| bit 4            | 1 = Registers                                                                           | ACC, FLTR, U                                                                                                                                                                                       | itation Status bi<br>JTH, LTH and th<br>s have not chan                                                                         | ne AOV bit are       |                  |                  | lated        |

| bit 3            | Unimplemen                                                                              | ted: Read as '                                                                                                                                                                                     | 0'                                                                                                                              |                      |                  |                  |              |

| bit 2-0          | 111 = ADC n<br>110 = ADC n<br>101 = ADC n<br>100 = Not us<br>011 = ADC n<br>010 = ADC n | nodule is in 2 <sup>nd</sup><br>nodule is in 2 <sup>nd</sup><br>nodule is in 2 <sup>nd</sup><br>ed<br>nodule is in 1 <sup>st</sup><br>nodule is in 1 <sup>st</sup><br>nodule is in 1 <sup>st</sup> | ycle Multistage<br>conversion sta<br>acquisition sta<br>precharge stag<br>conversion stag<br>acquisition stag<br>precharge stag | ge<br>ge<br>ge<br>ge |                  |                  |              |

#### REGISTER 36-5: ADSTAT: ADC STATUS REGISTER

**Note 1:** If CS = 1, and FOSC<FRC, these bits may be invalid.

#### 38.7 Comparator Response Time

The comparator output is indeterminate for a period of time after the change of an input source or the selection of a new reference voltage. This period is referred to as the response time. The response time of the comparator differs from the settling time of the voltage reference. Therefore, both of these times must be considered when determining the total response time to a comparator input change. See the Comparator and Voltage Reference Specifications in Table 44-17 and Table 44-19 for more details.

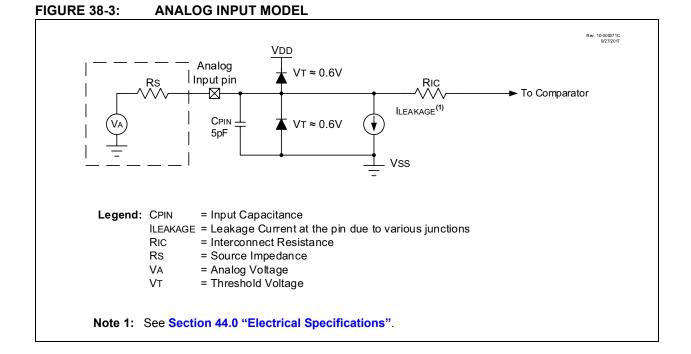

#### 38.8 Analog Input Connection Considerations

A simplified circuit for an analog input is shown in Figure 38-3. Since the analog input pins share their connection with a digital input, they have reverse biased ESD protection diodes to VDD and VSS. The analog input, therefore, must be between VSS and VDD. If the input voltage deviates from this range by more than 0.6V in either direction, one of the diodes is forward biased and a latch-up may occur.

The maximum source impedance for analog sources is mentioned in Parameter AD08 in Table 44-15. Also, any external component connected to an analog input pin, such as a capacitor or a Zener diode, should have very little leakage current to minimize inaccuracies introduced.

- Note 1: When reading a PORT register, all pins configured as analog inputs will read as a '0'. Pins configured as digital inputs will convert as an analog input, according to the input specification.

- 2: Analog levels on any pin defined as a digital input, may cause the input buffer to consume more current than is specified.

© 2017 Microchip Technology Inc.

#### 38.9 CWG1 Auto-Shutdown Source

The output of the comparator module can be used as an auto-shutdown source for the CWG1 module. When the output of the comparator is active and the corresponding WGASxE is enabled, the CWG operation will be suspended immediately (see Section 26.10.1.2 "External Input Source").

#### 38.10 ADC Auto-Trigger Source

The output of the comparator module can be used to trigger an ADC conversion. When the ADACT register is set to trigger on a comparator output, an ADC conversion will trigger when the Comparator output goes high.

#### 38.11 TMR2/4/6 Reset

The output of the comparator module can be used to reset Timer2. When the TxRST register is appropriately set, the timer will reset when the Comparator output goes high.

#### 38.12 Operation in Sleep Mode

The comparator module can operate during Sleep. The comparator clock source is based on the Timer1 clock source. If the Timer1 clock source is either the system clock (FOSC) or the instruction clock (FOSC/4), Timer1 will not operate during Sleep, and synchronized comparator outputs will not operate.

A comparator interrupt will wake the device from Sleep. The CxIE bits of the respective PIE register must be set to enable comparator interrupts.

### 38.13 Register Definitions: Comparator Control

Long bit name prefixes for the Comparators are shown in Table 38-2. Refer to **Section 1.3.2.2 "Long Bit Names"** for more information.

#### TABLE 38-2:

| Peripheral | Bit Name Prefix |

|------------|-----------------|

| C1         | C1              |

| C2         | C2              |

#### REGISTER 38-1: CMxCON0: COMPARATOR x CONTROL REGISTER 0

| R/W-0/0 | R-0/0 | U-0       | R/W-0/0 | U-0 | U-1 | R/W-0/0 | R/W-0/0 |  |

|---------|-------|-----------|---------|-----|-----|---------|---------|--|

| EN      | OUT   | OUT — POL |         | —   | —   | HYS     | SYNC    |  |

| bit 7   |       |           |         |     |     |         | bit 0   |  |

| Legend:           |                  |                                    |                    |  |  |

|-------------------|------------------|------------------------------------|--------------------|--|--|

| R = Readable bit  | W = Writable bit | U = Unimplemented bit, read as '0' |                    |  |  |

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared               | x = Bit is unknown |  |  |

| bit 7 | EN: Comparator Enable bit                                                                            |

|-------|------------------------------------------------------------------------------------------------------|

|       | 1 = Comparator is enabled                                                                            |

|       | 0 = Comparator is disabled and consumes no active power                                              |

| bit 6 | OUT: Comparator Output bit                                                                           |

|       | <u>If POL = 0 (noninverted polarity)</u> :<br>1 = CxVP > CxVN                                        |

|       | 0 = CxVP < CxVN                                                                                      |

|       | If POL = 1 (inverted polarity):                                                                      |

|       | 1 = CxVP < CxVN                                                                                      |

|       | 0 = CxVP > CxVN                                                                                      |

| bit 5 | Unimplemented: Read as '0'                                                                           |

| bit 4 | POL: Comparator Output Polarity Select bit                                                           |

|       | <ul> <li>1 = Comparator output is inverted</li> <li>0 = Comparator output is not inverted</li> </ul> |

| bit 3 | Unimplemented: Read as '0'                                                                           |

| bit 2 | Unimplemented: Read as '1'                                                                           |

| bit 1 | HYS: Comparator Hysteresis Enable bit                                                                |

|       | 1 = Comparator hysteresis enabled                                                                    |

|       | 0 = Comparator hysteresis disabled                                                                   |

| bit 0 | SYNC: Comparator Output Synchronous Mode bit                                                         |

|       | 1 = Comparator output to Timer1/3/5 and I/O pin is synchronous to changes on Timer1 clock source.    |

|       | 0 = Comparator output to Timer1/3/5 and I/O pin is asynchronous                                      |

|       | Output updated on the falling edge of Timer1/3/5 clock source.                                       |

|       |                                                                                                      |

# PIC18(L)F26/27/45/46/47/55/56/57K42

| INCF                                   | Increment f                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | INCFSZ                                                                       | Increment f, skip if 0                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |  |  |

|----------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|

| Syntax:                                | INCF f {,d {,a}}                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | Syntax:                                                                      | INCFSZ f {,d {,a}}                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |  |  |

| Operands:                              | $\begin{array}{l} 0 \leq f \leq 255 \\ d  \in  [0,1] \\ a  \in  [0,1] \end{array}$                                                                                                                                                                                                                                                                                                                                                                                                                                        | Operands:                                                                    | $\begin{array}{l} 0 \leq f \leq 255 \\ d  \in  [0,1] \\ a  \in  [0,1] \end{array}$                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |  |  |

| Operation:                             | (f) + 1 $\rightarrow$ dest                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | Operation:                                                                   | (f) + 1 $\rightarrow$ dest,                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |  |  |

| Status Affected:                       | C, DC, N, OV, Z                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |                                                                              | skip if result = 0                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |  |  |

| Encoding:                              | 0010 10da ffff ff                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | Status Affected:                                                             | None                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |  |  |

| Description:                           | The contents of register 'f' are                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | Encoding:                                                                    | 0011 11da ffff ffff                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |  |  |

| Words:<br>Cycles:<br>Q Cycle Activity: | incremented. If 'd' is '0', the result is<br>placed in W. If 'd' is '1', the result is<br>placed back in register 'f' (default).<br>If 'a' is '0', the Access Bank is select<br>If 'a' is '1', the BSR is used to select<br>GPR bank.<br>If 'a' is '0' and the extended instruct<br>set is enabled, this instruction oper<br>in Indexed Literal Offset Addressing<br>mode whenever $f \le 95$ (5Fh). See S<br>tion 41.2.3 "Byte-Oriented and B<br>Oriented Instructions in Indexed<br>eral Offset Mode" for details.<br>1 | e<br>5<br>-                                                                  | The contents of register 'f' are<br>incremented. If 'd' is '0', the result is<br>placed in W. If 'd' is '1', the result is<br>placed back in register 'f' (default).<br>If the result is '0', the next instruction,<br>which is already fetched, is discarded<br>and a NOP is executed instead, making<br>it a 2-cycle instruction.<br>If 'a' is '0', the Access Bank is selected<br>If 'a' is '1', the BSR is used to select the<br>GPR bank.<br>If 'a' is '0' and the extended instruction<br>set is enabled, this instruction operates<br>in Indexed Literal Offset Addressing<br>mode whenever f ≤ 95 (5Fh). See Sec<br>tion 41.2.3 "Byte-Oriented and Bit-<br>Oriented Instructions in Indexed Lit<br>eral Offset Mode" for details. |  |  |

| Q1<br>Decode                           | Q2 Q3 Q4<br>Read Process Write                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | Words:                                                                       | 1                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |  |  |

| Example:                               | INCF CNT, 1, 0                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | Cycles:                                                                      | 1(2)<br><b>Note:</b> 3 cycles if skip and followed<br>by a 2-word instruction.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |  |  |

| Before Instru                          |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | Q Cycle Activity:                                                            |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |  |  |

| CNT                                    | = FFh                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | Q1                                                                           | Q2 Q3 Q4                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |  |  |

| Z<br>C                                 | = 0<br>= ?                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | Decode                                                                       | Read Process Write to                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |  |  |

| DC                                     | = ?                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |                                                                              | register 'f' Data destination                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |  |  |

| After Instruct<br>CNT                  | ion<br>= 00h                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | If skip:                                                                     | 02 02 04                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |  |  |

| Z                                      | = 1                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | Q1<br>No                                                                     | Q2 Q3 Q4<br>No No No                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |  |  |

| DC                                     | = 1<br>= 1                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |                                                                              | operation operation operation                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |  |  |

|                                        |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |                                                                              | ed by 2-word instruction:                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |  |  |

|                                        |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | Q1                                                                           | Q2 Q3 Q4                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |  |  |

|                                        |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | No                                                                           | No No No                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |  |  |

|                                        |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | operation                                                                    | operation operation operation                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |  |  |

|                                        |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | No<br>operation                                                              | NoNoNooperationoperationoperation                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |  |  |

|                                        |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | Example:                                                                     | HERE INCFSZ CNT, 1, 0<br>NZERO :<br>ZERO :                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |  |  |

|                                        |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | Before Instru<br>PC<br>After Instruct<br>CNT<br>If CNT<br>PC<br>If CNT<br>PC | = Address (HERE)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |  |  |

# 42.0 REGISTER SUMMARY

#### **TABLE 42-1**: REGISTER FILE SUMMARY FOR PIC18(L)F26/27/45/46/47/55/56/57K42 DEVICES