Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

E·XFI

| Product Status             | Active                                                                       |

|----------------------------|------------------------------------------------------------------------------|

| Core Processor             | PIC                                                                          |

| Core Size                  | 8-Bit                                                                        |

| Speed                      | 64MHz                                                                        |

| Connectivity               | I <sup>2</sup> C, LINbus, SPI, UART/USART                                    |

| Peripherals                | Brown-out Detect/Reset, DMA, HLVD, POR, PWM, WDT                             |

| Number of I/O              | 36                                                                           |

| Program Memory Size        | 64KB (32K x 16)                                                              |

| Program Memory Type        | FLASH                                                                        |

| EEPROM Size                | 1K x 8                                                                       |

| RAM Size                   | 4K x 8                                                                       |

| Voltage - Supply (Vcc/Vdd) | 1.8V ~ 3.6V                                                                  |

| Data Converters            | A/D 35x12b; D/A 1x5b                                                         |

| Oscillator Type            | Internal                                                                     |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                            |

| Mounting Type              | Surface Mount                                                                |

| Package / Case             | 44-TQFP                                                                      |

| Supplier Device Package    | 44-TQFP (10x10)                                                              |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/pic18lf46k42t-i-pt |

|                            |                                                                              |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

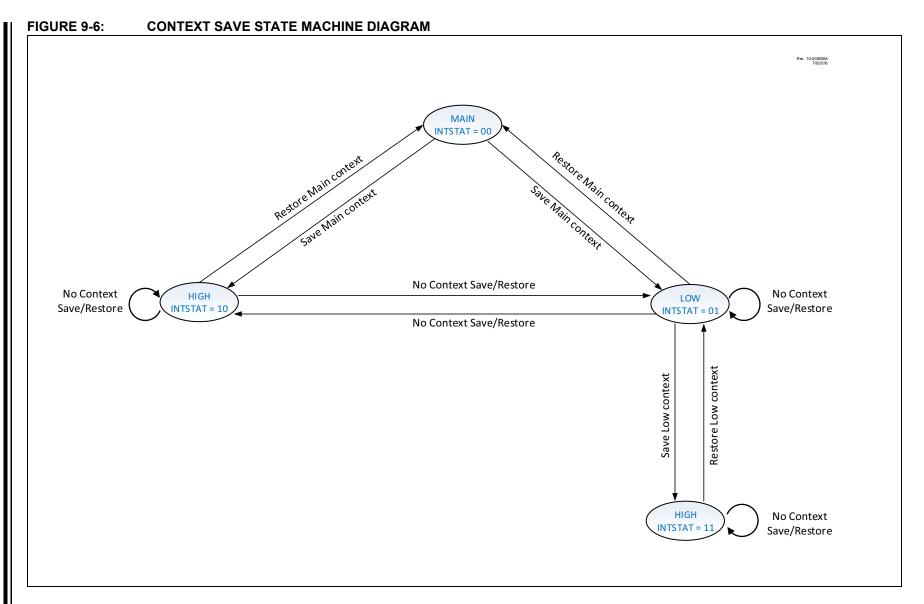

## 9.0 INTERRUPT CONTROLLER

The Vectored Interrupt Controller module reduces the numerous peripheral interrupt request signals to a single interrupt request signal to the CPU. This module includes the following major features:

- Interrupt Vector Table (IVT) with a unique vector for each interrupt source

- · Fixed and ensured interrupt latency

- Programmable base address for Interrupt Vector Table (IVT) with lock

- Two user-selectable priority levels High priority and Low priority

- Two levels of context saving

- Interrupt state status bits to indicate the current execution status of the CPU

The Interrupt Controller module assembles all of the interrupt request signals and resolves the interrupts based on both a fixed natural order priority (i.e., determined by the Interrupt Vector Table), and a user-assigned priority (i.e., determined by the IPRx registers), thereby eliminating scanning of interrupt sources.

### 9.1 Interrupt Control and Status Registers

The devices in this family implement the following registers for the interrupt controller:

- INTCON0, INTCON1 Control Registers

- PIRx Peripheral Interrupt Status Registers

- PIEx Peripheral Interrupt Enable Registers

- IPRx Peripheral Interrupt Priority Registers

- IVTBASE<20:0> Address Registers

- IVTLOCK Register

Global interrupt control functions and external interrupts are controlled from the INTCON0 register. The INTCON1 register contains the status flags for the Interrupt controller.

The PIRx registers contain all of the interrupt request flags. Each source of interrupt has a status bit, which is set by the respective peripherals or an external signal and is cleared via software.

The PIEx registers contain all of the interrupt enable bits. These control bits are used to individually enable interrupts from the peripherals or external signals.

The IPRx registers are used to set the Interrupt Priority Level for each source of interrupt. Each user interrupt source can be assigned to either a high or low priority.

The IVTBASE register is user programmable and is used to determine the start address of the Interrupt Vector Table and the IVTLOCK register is used to prevent any unintended writes to the IVTBASE register. There are two other configuration bits that control the way the interrupt controller can be configured.

- · CONFIG2L<3>, MVECEN bit

- CONFIG2L<4>, IVT1WAY bit

The MVECEN bit in CONFIG2L determines whether the Vector table is used to determine the interrupt priorities.

When the IVT1WAY determines the number of times the IVTLOCKED bit can be cleared and set after a device Reset. See Section

9.2.3 "Interrupt Vector Table (IVT) address calculation" for details.

|                 | J-21. 11L7.                 |                   |            |              |                  |                  |              |  |  |

|-----------------|-----------------------------|-------------------|------------|--------------|------------------|------------------|--------------|--|--|

| U-0             | U-0                         | R/W-0/0           | R/W-0/0    | R/W-0/0      | U-0              | R/W-0/0          | R/W-0/0      |  |  |

| _               | -                           | INT2IE            | CLC2IE     | CWG2IE       | —                | CCP2IE           | TMR4IE       |  |  |

| bit 7           |                             |                   |            |              |                  |                  | bit (        |  |  |

|                 |                             |                   |            |              |                  |                  |              |  |  |

| Legend:         |                             |                   |            |              |                  |                  |              |  |  |

| R = Readab      | ole bit                     | W = Writable      | bit        | U = Unimple  | mented bit, read | l as '0'         |              |  |  |

| u = Bit is un   | changed                     | x = Bit is unkr   | nown       | -n/n = Value | at POR and BO    | R/Value at all o | other Resets |  |  |

| '1' = Bit is se | et                          | '0' = Bit is clea | ared       |              |                  |                  |              |  |  |

|                 |                             |                   |            |              |                  |                  |              |  |  |

| bit 7-6         | Unimplemen                  | nted: Read as '   | 0'         |              |                  |                  |              |  |  |

| bit 5           | INT2IE: Exte                | rnal Interrupt 2  | Enable bit |              |                  |                  |              |  |  |

|                 | 1 = Enabled                 |                   |            |              |                  |                  |              |  |  |

|                 | 0 = Disabled                |                   |            |              |                  |                  |              |  |  |

| bit 4           |                             | C2 Interrupt Ena  | able bit   |              |                  |                  |              |  |  |

|                 | 1 = Enabled                 |                   |            |              |                  |                  |              |  |  |

|                 | 0 = Disabled                |                   |            |              |                  |                  |              |  |  |

| bit 3           |                             | VG2 Interrupt E   | nable bit  |              |                  |                  |              |  |  |

|                 | 1 = Enabled<br>0 = Disabled | I                 |            |              |                  |                  |              |  |  |

| bit 2           |                             | ted: Read as '    | ∩'         |              |                  |                  |              |  |  |

| bit 1           | -                           | P2 Interrupt En   |            |              |                  |                  |              |  |  |

|                 | 1 = Enabled                 | rz menupi En      |            |              |                  |                  |              |  |  |

|                 | 0 = Disabled                | I                 |            |              |                  |                  |              |  |  |

| bit 0           |                             | R4 Interrupt En   | able bit   |              |                  |                  |              |  |  |

|                 | 1 = Enabled                 |                   |            |              |                  |                  |              |  |  |

|                 | 0 = Disabled                |                   |            |              |                  |                  |              |  |  |

#### REGISTER 9-21: PIE7: PERIPHERAL INTERRUPT ENABLE REGISTER 7

#### FIGURE 10-2: WAKE-UP FROM SLEEP THROUGH INTERRUPT

| Q1 Q2 Q3 Q4 Q1 Q2 Q3 Q4 Q1                         | 01/02/03/04         |                    | Q3 Q4 Q1 Q2 Q3 Q4   |

|----------------------------------------------------|---------------------|--------------------|---------------------|

|                                                    |                     |                    |                     |

|                                                    | Tost <sup>(3)</sup> | ·/                 |                     |

| Interrupt flag                                     | / Interrupt Late    | ncy <sup>(4)</sup> |                     |

| GIE bit<br>(INTCON reg.)<br>Sleet                  |                     | <u>.</u>           |                     |

| Instruction Flow<br>PC X PC X PC + 1 X             | PC + 2 X PC + 2     | PC+2 00            | 004h X 0005h        |

| Instruction { Inst(PC) = Sleep Inst(PC + 1)        | Inst(PC + 2)        | Inst               | (0004h) Inst(0005h) |

| Instruction { Inst(PC - 1) Sleep                   | Inst(PC + 1)        | Forced NOP Force   | ed NOP Inst(0004h)  |

| Note 1: External clock. High, Medium, Low mode ass | umed.               |                    |                     |

2: CLKOUT is shown here for timing reference.

3: TOST = 1024 TOSC. This delay does not apply to EC and INTOSC Oscillator modes.

4: GIE = 1 assumed. In this case after wake-up, the processor calls the ISR at 0004h. If GIE = 0, execution will continue in-line.

#### 10.2.3 LOW-POWER SLEEP MODE

The PIC18F26/27/45/46/47/55/56/57K42 device family contains an internal Low Dropout (LDO) voltage regulator, which allows the device I/O pins to operate at voltages up to 5.5V while the internal device logic operates at a lower voltage. The LDO and its associated reference circuitry must remain active when the device is in Sleep mode.

The PIC18F26/27/45/46/47/55/56/57K42 devices allow the user to optimize the operating current in Sleep, depending on the application requirements.

Low-Power Sleep mode can be selected by setting the VREGPM bit of the VREGCON register.

#### 10.2.3.1 Sleep Current vs. Wake-up Time

In the default operating mode, the LDO and reference circuitry remain in the normal configuration while in Sleep. The device is able to exit Sleep mode quickly since all circuits remain active. In Low-Power Sleep mode, when waking-up from Sleep, an extra delay time is required for these circuits to return to the normal configuration and stabilize.

The Low-Power Sleep mode is beneficial for applications that stay in Sleep mode for long periods of time. The Normal mode is beneficial for applications that need to wake from Sleep quickly and frequently.

| TRIGEN | BURSTMD | Scanner Operation                                                                                                                                                                   |

|--------|---------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 0      | 0       | Memory access is requested when the CRC module is ready to accept data; the request is granted if no other higher priority source request is pending.                               |

| 1      | 0       | Memory access is requested when the CRC module is ready to accept data and trigger selection is true; the request is granted if no other higher priority source request is pending. |

| x      | 1       | Memory access is always requested, the request is granted if no other higher priority source request is pending.                                                                    |

#### TABLE 14-1: SCANNER OPERATING MODES<sup>(1)</sup>

Note 1: See Section 3.1 "System Arbitration" for Priority selection and Section 3.2 "Memory Access Scheme" for Memory Access Scheme.

#### REGISTER 14-12: SCANLADRU: SCAN LOW ADDRESS UPPER BYTE REGISTER

| U-0   | U-0 | R/W-0/0 | R/W-0/0 | R/W-0/0 | R/W-0/0             | R/W-0/0 | R/W-0/0 |

|-------|-----|---------|---------|---------|---------------------|---------|---------|

| —     | —   |         |         | LADR<2  | 21:16> <b>(1,2)</b> |         |         |

| bit 7 | •   | •       |         |         |                     |         | bit 0   |

| Legend:              |                      |                                                       |

|----------------------|----------------------|-------------------------------------------------------|

| R = Readable bit     | W = Writable bit     | U = Unimplemented bit, read as '0'                    |

| u = Bit is unchanged | x = Bit is unknown   | -n/n = Value at POR and BOR/Value at all other Resets |

| '1' = Bit is set     | '0' = Bit is cleared |                                                       |

bit 7-6 Unimplemented: Read as '0'

bit 5-0 **LADR<21:16>:** Scan Start/Current Address bits<sup>(1,2)</sup> Upper bits of the current address to be fetched from, value increments on each fetch of memory.

- **Note 1:** Registers SCANLADRU/H/L form a 22-bit value, but are not guarded for atomic or asynchronous access; registers should only be read or written while SGO = 0 (SCANCON0 register).

- 2: While SGO = 1 (SCANCON0 register), writing to this register is ignored.

#### REGISTER 14-13: SCANLADRH: SCAN LOW ADDRESS HIGH BYTE REGISTER

| R/W-0/0                      | R/W-0/0 | R/W-0/0 | R/W-0/0 | R/W-0/0 | R/W-0/0 | R/W-0/0 | R/W-0/0 |  |

|------------------------------|---------|---------|---------|---------|---------|---------|---------|--|

| LADR<15:8> <sup>(1, 2)</sup> |         |         |         |         |         |         |         |  |

| bit 7                        |         |         |         |         |         |         | bit 0   |  |

| Legend:              |                      |                                                       |

|----------------------|----------------------|-------------------------------------------------------|

| R = Readable bit     | W = Writable bit     | U = Unimplemented bit, read as '0'                    |

| u = Bit is unchanged | x = Bit is unknown   | -n/n = Value at POR and BOR/Value at all other Resets |

| '1' = Bit is set     | '0' = Bit is cleared |                                                       |

bit 7-0 LADR<15:8>: Scan Start/Current Address bits<sup>(1, 2)</sup> Most Significant bits of the current address to be fetched from, value increments on each fetch of memory.

- **Note 1:** Registers SCANLADRU/H/L form a 22-bit value, but are not guarded for atomic or asynchronous access; registers should only be read or written while SGO = 0 (SCANCON0 register).

- **2:** While SGO = 1 (SCANCON0 register), writing to this register is ignored.

#### 15.9.5 OVERRUN INTERRUPT

The Overrun Interrupt flag is set if the DMA receives a trigger to start a new message before the current message is completed.

|                              | 1 2 3           | (4)                 | 6 6                                   | ) (8)            | 9 10  | (i) (i)                             | 13 14                               | 15 | 19 f) | 13 | Ray. 10.000275E<br>8/11/2016 |

|------------------------------|-----------------|---------------------|---------------------------------------|------------------|-------|-------------------------------------|-------------------------------------|----|-------|----|------------------------------|

| Instruction<br>Clock         |                 |                     |                                       |                  |       |                                     |                                     |    |       |    |                              |

| EN                           |                 |                     |                                       |                  |       |                                     |                                     |    |       |    |                              |

| SIRQEN                       |                 |                     |                                       |                  |       |                                     |                                     |    |       |    |                              |

| Source Hardware<br>Trigger - |                 |                     |                                       |                  |       |                                     |                                     |    |       |    |                              |

| DGO-                         |                 |                     |                                       |                  |       |                                     |                                     |    |       |    |                              |

| DMAxSPTR                     | (0x100          | )                   | 0x101                                 | X                | 0x100 |                                     | 0x101                               | X  | 0x10  | 0  |                              |

| DMAxDPTR                     | (0x200          | )                   | 0x201                                 | _X               | 0x202 |                                     | 0x203                               | χ  | 0x20  | 0  |                              |

| DMAxSCNT                     | 2               |                     | 1                                     | _X               | 2     |                                     | 1                                   | X  | 2     |    |                              |

| DMAxDCNT                     | 4               |                     | 3                                     | _X               | 2     |                                     | 1                                   | χ  | 4     |    |                              |

| DMA STATE                    | IDLE            | SR <sup>(1)</sup> D | W <sup>(2)</sup> SR <sup>(1)</sup> DW | / <sup>(2)</sup> | IDLE  | SR <sup>(1)</sup> DW <sup>(2)</sup> | SR <sup>(1)</sup> DW <sup>(2)</sup> |    | IDLE  |    |                              |

| DMAxSCNTIF                   |                 |                     |                                       |                  | 1     |                                     |                                     |    |       |    |                              |

| DMAxDCNTIF                   |                 |                     |                                       |                  |       |                                     |                                     |    |       |    |                              |

| DMAxORIF _                   |                 |                     |                                       |                  |       |                                     |                                     | 1  |       |    |                              |

|                              | DMAxCON1bits.SM | A = 01              |                                       |                  |       |                                     |                                     |    |       |    |                              |

|                              | DMAxSSA 0x10    | 00                  | DMAxDSA                               | 0x200            |       |                                     |                                     |    |       |    |                              |

|                              | DMAxSSZ 0x2     | 2                   | DMAxDSZ                               | 0x20             |       |                                     |                                     |    |       |    |                              |

| Note 1:                      | SR - Source Re  | ead                 |                                       |                  |       |                                     |                                     |    |       |    |                              |

| 2:                           | DW - Destinatio | on Write            |                                       |                  |       |                                     |                                     |    |       |    |                              |

#### FIGURE 15-9: OVERRUN INTERRUPT

#### REGISTER 15-9: DMAxSPTRU: DMAx SOURCE POINTER UPPER REGISTER

| U-0   | U-0 | R-0         | R-0 | R-0 | R-0 | R-0 | R-0   |

|-------|-----|-------------|-----|-----|-----|-----|-------|

| —     | —   | SPTR<21:16> |     |     |     |     |       |

| bit 7 |     |             |     |     |     |     | bit 0 |

# Legend: W = Writable bit U = Unimplemented bit, read as '0' -n/n = Value at POR and BOR/Value at all other 1 = bit is set 0 = bit is cleared x = bit is unknown u = bit is unchanged u = bit is unchanged

bit 7-6 Unimplemented: Read as '0'

bit 5-0 SPTR<21:16>: Current Source Address Pointer

#### REGISTER 15-10: DMAxSSZL: DMAx SOURCE SIZE LOW REGISTER

| R/W-0/0 | R/W-0/0 | R/W-0/0 | R/W-0/0 | R/W-0/0  | R/W-0/0 | R/W-0/0 | R/W-0/0 |

|---------|---------|---------|---------|----------|---------|---------|---------|

|         |         |         | SSZ     | <7:0>    |         |         |         |

| bit 7   |         |         |         |          |         |         | bit 0   |

|         |         |         |         |          |         |         |         |

| Legend: |         |         |         |          |         |         |         |

|         | L 14    |         | 1       | 1.1. 1.1 |         | (0)     |         |

| R = Readable bit                                            | W = Writable bit | U = Unimplemented bit, read a | s '0'                                      |

|-------------------------------------------------------------|------------------|-------------------------------|--------------------------------------------|

| -n/n = Value at POR and<br>BOR/Value at all other<br>Resets | 1 = bit is set   |                               | x = bit is unknown<br>u = bit is unchanged |

bit 7-0 SSZ<7:0>: Source Message Size bits

#### REGISTER 15-11: DMAxSSZH: DMAx SOURCE SIZE HIGH REGISTER

| U-0   | U-0 | U-0 | U-0 | R/W-0/0 | R/W-0/0 | R/W-0/0 | R/W-0/0 |

|-------|-----|-----|-----|---------|---------|---------|---------|

| —     | —   | —   | —   |         | SSZ<    | 11:8>   |         |

| bit 7 |     |     |     |         |         |         | bit 0   |

| Legend:                                                     |                  |                        |                                            |  |  |  |  |  |

|-------------------------------------------------------------|------------------|------------------------|--------------------------------------------|--|--|--|--|--|

| R = Readable bit                                            | W = Writable bit | U = Unimplemented bit, | U = Unimplemented bit, read as '0'         |  |  |  |  |  |

| -n/n = Value at POR and<br>BOR/Value at all other<br>Resets | 1 = bit is set   | 0 = bit is cleared     | x = bit is unknown<br>u = bit is unchanged |  |  |  |  |  |

bit 7-4 Unimplemented: Read as '0'

bit 3-0 SSZ<11:8>: Source Message Size bits

| R/W-1/1 |

|---------|---------|---------|---------|---------|---------|---------|---------|

| ANSELx7 | ANSELx6 | ANSELx5 | ANSELx4 | ANSELx3 | ANSELx2 | ANSELx1 | ANSELx0 |

| bit 7   |         |         |         |         |         |         | bit 0   |

|         |         |         |         |         |         |         |         |

#### REGISTER 16-4: ANSELX: ANALOG SELECT REGISTER

Legend:R = Readable bitW = Writable bitU = Unimplemented bit, read as '0''1' = Bit is set'0' = Bit is clearedx = Bit is unknown-n/n = Value at POR and BOR/Value at all other Resets

bit 7-0

- ANSELx<7:0>: Analog Select on Pins Rx<7:0>

- 1 = Digital Input buffers are disabled.

- 0 = ST and TTL input devices are enabled

#### TABLE 16-5: ANALOG SELECT PORT REGISTERS

| Name                  | Bit 7   | Bit 6   | Bit 5   | Bit 4   | Bit 3   | Bit 2   | Bit 1   | Bit 0   |

|-----------------------|---------|---------|---------|---------|---------|---------|---------|---------|

| ANSELA                | ANSELA7 | ANSELA6 | ANSELA5 | ANSELA4 | ANSELA3 | ANSELA2 | ANSELA1 | ANSELA0 |

| ANSELB                | ANSELB7 | ANSELB6 | ANSELB5 | ANSELB4 | ANSELB3 | ANSELB2 | ANSELB1 | ANSELB0 |

| ANSELC                | ANSELC7 | ANSELC6 | ANSELC5 | ANSELC4 | ANSELC3 | ANSELC2 | ANSELC1 | ANSELC0 |

| ANSELD <sup>(1)</sup> | ANSELD7 | ANSELD6 | ANSELD5 | ANSELD4 | ANSELD3 | ANSELD2 | ANSELD1 | ANSELD0 |

| ANSELE <sup>(1)</sup> | _       | _       | _       | —       | _       | ANSELE2 | ANSELE1 | ANSELE0 |

| ANSELF <sup>(2)</sup> | ANSELF7 | ANSELF6 | ANSELF5 | ANSELF4 | ANSELF3 | ANSELF2 | ANSELF1 | ANSELF0 |

Note 1: Unimplemented in PIC18(L)F26/27K42.

2: Unimplemented in PIC18(L)F26/45/46/47K42.

#### REGISTER 21-5: TMRxL: TIMERx LOW BYTE REGISTER

| R/W-x/x          | R/W-x/x | R/W-x/x           | R/W-x/x | R/W-x/x        | R/W-x/x          | R/W-x/x          | R/W-x/x      |

|------------------|---------|-------------------|---------|----------------|------------------|------------------|--------------|

|                  |         |                   | TMR     | «L<7:0>        |                  |                  |              |

| bit 7            |         |                   |         |                |                  |                  | bit 0        |

|                  |         |                   |         |                |                  |                  |              |

| Legend:          |         |                   |         |                |                  |                  |              |

| R = Readable     | bit     | W = Writable I    | bit     | U = Unimpler   | nented bit, read | l as '0'         |              |

| u = Bit is unch  | anged   | x = Bit is unkn   | iown    | -n/n = Value a | at POR and BO    | R/Value at all c | other Resets |

| '1' = Bit is set |         | '0' = Bit is clea | ared    |                |                  |                  |              |

bit 7-0 TMRxL<7:0>:Timerx Low Byte bits

#### **REGISTER 21-6:** TMRxH: TIMERx HIGH BYTE REGISTER

| R/W-x/x    | R/W-x/x | R/W-x/x | R/W-x/x | R/W-x/x | R/W-x/x | R/W-x/x | R/W-x/x |  |

|------------|---------|---------|---------|---------|---------|---------|---------|--|

| TMRxH<7:0> |         |         |         |         |         |         |         |  |

| bit 7 b    |         |         |         |         |         |         |         |  |

| Legend:              |                      |                                                       |

|----------------------|----------------------|-------------------------------------------------------|

| R = Readable bit     | W = Writable bit     | U = Unimplemented bit, read as '0'                    |

| u = Bit is unchanged | x = Bit is unknown   | -n/n = Value at POR and BOR/Value at all other Resets |

| '1' = Bit is set     | '0' = Bit is cleared |                                                       |

bit 7-0 TMRxH<7:0>:Timerx High Byte bits

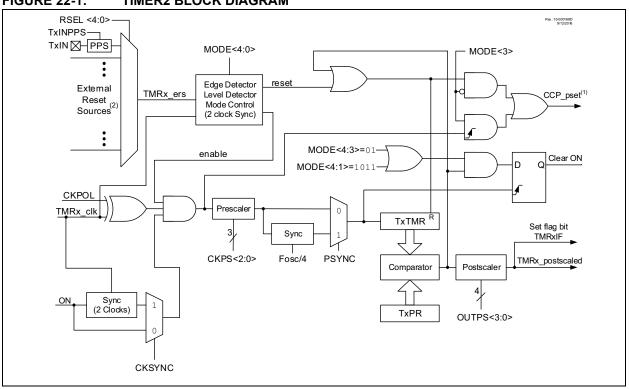

## 22.0 TIMER2/4/6 MODULE

The Timer2/4/6 modules are 8-bit timers that can operate as free-running period counters or in conjunction with external signals that control start, run, freeze, and reset operation in One-Shot and Monostable modes of operation. Sophisticated waveform control such as pulse density modulation are possible by combining the operation of these timers with other internal peripherals such as the comparators and CCP modules. Features of the timer include:

- 8-bit timer register

- 8-bit period register

- Selectable external hardware timer resets

- Programmable prescaler (1:1 to 1:128)

- Programmable postscaler (1:1 to 1:16)

- Selectable synchronous/asynchronous operation

- Alternate clock sources

- Interrupt on period

- Three modes of operation:

- Free Running Period

- One-Shot

- Monostable

See Figure 22-1 for a block diagram of Timer2. See Figure 22-2 for the clock source block diagram.

**Note:** Three identical Timer2 modules are implemented on this device. The timers are named Timer2, Timer4, and Timer6. All references to Timer2 apply as well to Timer4 and Timer6. All references to T2PR apply as well to T4PR and T6PR.

#### FIGURE 22-1: TIMER2 BLOCK DIAGRAM

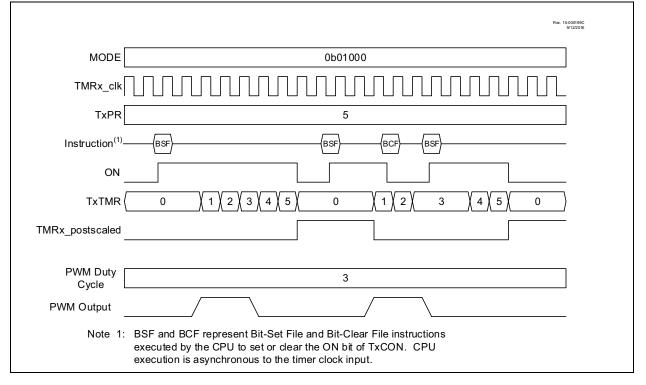

#### 22.5.5 SOFTWARE START ONE-SHOT MODE

In One-Shot mode, the timer resets and the ON bit is cleared when the timer value matches the T2PR period value. The ON bit must be set by software to start another timer cycle. Setting MODE<4:0> = 01000 selects One-Shot mode which is illustrated in Figure 22-8. In the example, ON is controlled by BSF and BCF instructions. In the first case, a BSF instruction sets ON and the counter runs to completion and clears ON. In the second case, a BSF instruction starts the cycle, BCF/BSF instructions turn the counter off and on during the cycle, and then it runs to completion.

When One-Shot mode is used in conjunction with the CCP PWM operation, the PWM pulse drive starts concurrent with setting the ON bit. Clearing the ON bit while the PWM drive is active will extend the PWM drive. The PWM drive will terminate when the timer value matches the CCPRx pulse width value. The PWM drive will remain off until software sets the ON bit to start another cycle. If software clears the ON bit after the CCPRx match but before the T2PR match then the PWM drive will be extended by the length of time the ON bit remains cleared. Another timing cycle can only be initiated by setting the ON bit after it has been cleared by a T2PR period count match.

FIGURE 22-8: SOFTWARE START ONE-SHOT MODE TIMING DIAGRAM (MODE = 01000)

| R/W/HC-0/0       | R/W-0/0                      | R/W-0/0           | R/W-0/0         | R/W-0/0         | R/W-0/0         | R/W-0/0        | R/W-0/0      |  |  |

|------------------|------------------------------|-------------------|-----------------|-----------------|-----------------|----------------|--------------|--|--|

| ON               |                              | CKPS<2:0>         |                 |                 | OUTP            | S<3:0>         |              |  |  |

| bit 7            |                              |                   |                 |                 |                 |                | bit C        |  |  |

| Legend:          |                              |                   |                 |                 |                 |                |              |  |  |

| R = Readable     | bit                          | W = Writable      | bit             | U = Unimpler    | nented bit, rea | d as '0'       |              |  |  |

| u = Bit is unch  | anged                        | x = Bit is unkr   | iown            | -n/n = Value a  | at POR and BC   | R/Value at all | other Resets |  |  |

| '1' = Bit is set |                              | '0' = Bit is clea | ared            | HC = Bit is cle | eared by hardv  | vare           |              |  |  |

| h:+ 7            | <b>ON:</b> Timerx            | On hit(1)         |                 |                 |                 |                |              |  |  |

| bit 7            | 1 = Timerx i                 |                   |                 |                 |                 |                |              |  |  |

|                  |                              | s Off: all counte | rs and state n  | achines are re  | set             |                |              |  |  |

| bit 6-4          |                              | : Timerx-type Cl  |                 |                 |                 |                |              |  |  |

|                  | 111 = 1:128                  |                   |                 |                 |                 |                |              |  |  |

|                  | 110 = 1:64 Prescaler         |                   |                 |                 |                 |                |              |  |  |

|                  | 101 = <b>1:32</b>            | Prescaler         |                 |                 |                 |                |              |  |  |

|                  | 100 = 1:16                   |                   |                 |                 |                 |                |              |  |  |

|                  | 011 = 1:8 P                  | Prescaler         |                 |                 |                 |                |              |  |  |

|                  | 010 = <b>1:4</b> P           |                   |                 |                 |                 |                |              |  |  |

|                  | 001 = 1:2 P                  |                   |                 |                 |                 |                |              |  |  |

|                  | 000 = 1:1 P                  |                   |                 |                 |                 |                |              |  |  |

| bit 3-0          |                              | >: Timerx Output  | It Postscaler S | Select bits     |                 |                |              |  |  |

|                  | 1111 <b>= 1:16</b>           |                   |                 |                 |                 |                |              |  |  |

|                  | 1110 = <b>1</b> : <b>1</b> 5 |                   |                 |                 |                 |                |              |  |  |

|                  | 1101 = 1:14                  |                   |                 |                 |                 |                |              |  |  |

|                  | 1100 = 1:13<br>1011 = 1:12   |                   |                 |                 |                 |                |              |  |  |

|                  | 1011 - 1.12<br>1010 = 1:11   |                   |                 |                 |                 |                |              |  |  |

|                  | 1001 = 1:10                  |                   |                 |                 |                 |                |              |  |  |

|                  | 1000 = 1:9                   |                   |                 |                 |                 |                |              |  |  |

|                  | 0111 = 1:8                   |                   |                 |                 |                 |                |              |  |  |

|                  | 0110 = 1.7 Postscaler        |                   |                 |                 |                 |                |              |  |  |

|                  | 0101 = <b>1:6</b>            | Postscaler        |                 |                 |                 |                |              |  |  |

|                  | 0100 = 1:5                   | Postscaler        |                 |                 |                 |                |              |  |  |

|                  | 0011 = 1:4                   | Postscaler        |                 |                 |                 |                |              |  |  |

|                  | 0010 = 1:3                   |                   |                 |                 |                 |                |              |  |  |

|                  | 0001 = 1:2                   |                   |                 |                 |                 |                |              |  |  |

|                  | 0000 = 1:1                   | Postscaler        |                 |                 |                 |                |              |  |  |

#### REGISTER 22-5: TxCON: TIMERx CONTROL REGISTER

Note 1: In certain modes, the ON bit will be auto-cleared by hardware. See Section 22.1.2 "One-Shot Mode".

#### 25.6.5 WINDOWED MEASURE MODE

This mode measures the window duration of the SMTWINx input of the SMT. It begins incrementing the timer on a rising edge of the SMTWINx input and updates the SMT1CPR register with the value of the timer and resets the timer on a second rising edge. See Figure 25-10 and Figure 25-11.

#### 32.5.3 RECEIVE ONLY MODE

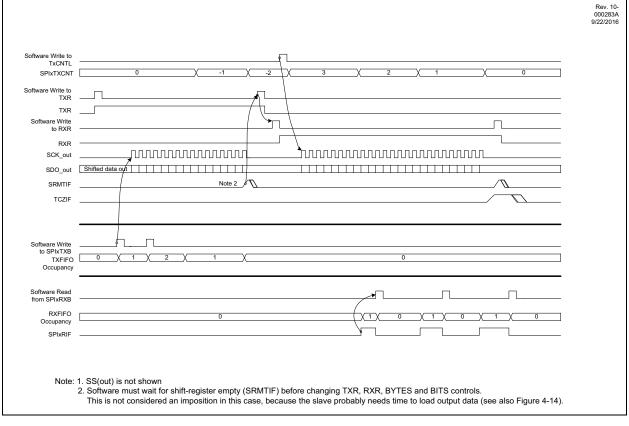

When RXR is set and TXR is clear, the SPI master is in Receive Only mode. In this mode, data transfers when the RXFIFO is not full and the Transfer Counter is nonzero. In this mode, writing a value to SPIxTCNTL will start the clocks for transfer. The clocks will suspend while the RXFIFO is full and cease when the SPIxTCNT reaches zero (see Section 32.4 "Transfer Counter"). If there is any data in the TXFIFO, the first data written to the TXFIFO will be transmitted on each data exchange, although the TXFIFO occupancy will not change, meaning that the same message will be sent on each transmission. If there is no data in the TXFIFO, the most recently received data will instead be transmitted. Figure 32-5 shows an example of sending a command using Section 32.5.2 "Transmit Only Mode" and then receiving a byte of data using this mode.

#### 32.5.4 TRANSFER OFF MODE

When both TXR and RXR are cleared, the SPI master is in Transfer Off mode. In this mode, SCK will not toggle and no data is exchanged. However, writes to SPIxTXB will be transferred to the TXFIFO which will be transmitted if the TXR bit is set.

## 32.9 Register definitions: SPI

|              |                                                                                                              | F: SPI INTER      |                   |               |                    |            |       |  |  |  |  |

|--------------|--------------------------------------------------------------------------------------------------------------|-------------------|-------------------|---------------|--------------------|------------|-------|--|--|--|--|

| R/W/HS-0/0   | R/W/HS-0/0                                                                                                   | R/W/HS-0/0        | R/W/HS-0/0        | U-0           | R/W/HS-0/0         | R/W/HS-0/0 | U-0   |  |  |  |  |

| SRMTIF       | TCZIF                                                                                                        | SOSIF             | EOSIF             |               | RXOIF              | TXUIF      |       |  |  |  |  |

| bit 7        |                                                                                                              |                   |                   |               |                    |            | bit 0 |  |  |  |  |

| Legend:      |                                                                                                              |                   |                   |               |                    |            |       |  |  |  |  |

| R = Readable | bit                                                                                                          | W = Writable b    | t                 |               | plemented bit, re  |            |       |  |  |  |  |

|              |                                                                                                              |                   |                   | HS = Bit c    | an be set by har   | dware      |       |  |  |  |  |

| bit 7        | SRMTIF: Shift                                                                                                | Register Empty    | Interrupt Flag bi | it            |                    |            |       |  |  |  |  |

|              | Slave mode:                                                                                                  |                   |                   |               |                    |            |       |  |  |  |  |

|              | This bit is ignor                                                                                            | ed                |                   |               |                    |            |       |  |  |  |  |

|              | Master mode:                                                                                                 |                   |                   |               |                    |            |       |  |  |  |  |

|              | 1 = The data transfer is complete                                                                            |                   |                   |               |                    |            |       |  |  |  |  |

|              | 0 = Either no da                                                                                             | ata transfers hav | ve occurred or a  | a data transi | fer is in progress | ;          |       |  |  |  |  |

| bit 6        | TCZIF: Transfer Counter is Zero Interrupt Flag bit                                                           |                   |                   |               |                    |            |       |  |  |  |  |

|              | 1 = The transfer counter (as defined by BMODE in Register 32-7, TCNTH/L, and TWIDTH) has decremented to zero |                   |                   |               |                    |            |       |  |  |  |  |

|              | 0= No interrupt pending                                                                                      |                   |                   |               |                    |            |       |  |  |  |  |

| bit 5        | SOSIF: Start of Slave Select Interrupt Flag bit                                                              |                   |                   |               |                    |            |       |  |  |  |  |

|              | 1 = SS(in) transitioned from false to true                                                                   |                   |                   |               |                    |            |       |  |  |  |  |

|              | 0 = No interrupt pending                                                                                     |                   |                   |               |                    |            |       |  |  |  |  |

| bit 4        | EOSIF: End of Slave Select Interrupt Flag bit                                                                |                   |                   |               |                    |            |       |  |  |  |  |

|              | 1 = SS(in) transitioned from true to false                                                                   |                   |                   |               |                    |            |       |  |  |  |  |

|              | 0 = No interrupt pending                                                                                     |                   |                   |               |                    |            |       |  |  |  |  |

| bit 3        | Unimplemente                                                                                                 | ed: Read as '0'   |                   |               |                    |            |       |  |  |  |  |

| bit 2        | RXOIF: Receiv                                                                                                | er Overflow Inte  | rrupt Flag bit    |               |                    |            |       |  |  |  |  |

|              | 1 = Data transf                                                                                              | er completed wh   | en RXBF = $1$ (e  | edge trigger  | red) and RXR =     | 1          |       |  |  |  |  |

|              | 0 = No interrup                                                                                              | t pending         |                   |               |                    |            |       |  |  |  |  |

| bit 1        | TXUIF: Transm                                                                                                | itter Underflow I | nterrupt Flag bi  | t             |                    |            |       |  |  |  |  |

|              | 1 = Slave Data                                                                                               | transfer started  | when TXBE = 2     | and TXR :     | = 1                |            |       |  |  |  |  |

|              | 0 = No interrup                                                                                              | t pending         |                   |               |                    |            |       |  |  |  |  |

| bit 0        | Unimplemente                                                                                                 | ed: Read as '0'   |                   |               |                    |            |       |  |  |  |  |

|              |                                                                                                              |                   |                   |               |                    |            |       |  |  |  |  |

#### REGISTER 32-1: SPIXINTF: SPI INTERRUPT FLAG REGISTER

#### 33.5.11 MASTER TRANSMISSION IN 10-BIT ADDRESSING MODE

This section describes the sequence of events for the  $I^2C$  module configured as an  $I^2C$  master in 10-bit Addressing mode and is transmitting data. Figure 33-21 is used as a visual reference for this description

1. If ABD = 0; i.e., Address buffers are enabled

Master software loads number of bytes to be transmitted in one sequence in I2CxCNT, high address byte of slave address in I2CxADB1 with R/W = 0, low address byte in I2CxADB0 and the first byte of data in I2CxTXB. Master software has to set the Start (S) bit to initiate communication.

If ABD = 1; i.e., Address buffers are disabled

Master software loads the number of bytes to be transmitted in one sequence in I2CxCNT and the high address byte of the slave address with R/W = 0 into the I2CxTXB register. Writing to the I2CxTXB will assert the start condition on the bus and sets the S bit. Software writes to the S bit are ignored in this case.

- 2. Master hardware waits for BFRE bit to be set; then shifts out the start and high address and waits for acknowledge.

- 3. If NACK, master hardware sends Stop.

- 4. If ABD = 0; i.e., Address buffer are enabled

If ACK, master hardware sends the low address byte from I2CxADB0.

If ABD = 1; i.e., Address buffer are disabled

If ACK, master hardware sets TXIF and MDR bits and the software has to write the low address byte into I2CxTXB. Writing to I2CxTXB sends the low address on the bus.

- If TXBE = 1 and I2CxCNT! = 0, I2CxTXIF and MDR bits are set. Clock is stretched on 8th falling SCL edge until master software writes next data byte to I2CxTXB.

- Master hardware sends ninth SCL pulse for ACK from slave and loads the shift register from I2CxTXB. I2CxCNT is decremented.

- 7. If slave sends a NACK, master hardware sends Stop and ends transmission.

- If slave sends an ACK, master hardware outputs data in the shift register on SDA. I2CxCNT value is checked on the 8th falling SCL edge. If I2CxCNT = 0; master hardware sends 9th SCL pulse for ACK and CNTIF is set.

- 9. If I2CxCNT! = 0; go to step 5.

| Name      | Bit 7  | Bit 6                                   | Bit 5   | Bit 4  | Bit 3   | Bit 2 | Bit 1     | Bit 0  | Register<br>on page |

|-----------|--------|-----------------------------------------|---------|--------|---------|-------|-----------|--------|---------------------|

| I2CxBTO   | —      | _                                       | _       | _      |         |       | BTO<2:0>  |        | 582                 |

| I2CxCLK   |        | _                                       | —       | _      | _       |       | CLK<2:0>  |        | 581                 |

| I2CxPIE   | CNTIE  | ACKTIE                                  | _       | WRIE   | ADRIE   | PCIE  | RSCIE     | SCIE   | 588                 |

| I2CxPIR   | CNTIF  | ACKTIF                                  | —       | WRIF   | ADRIF   | PCIF  | RSCIF     | SCIF   | 587                 |

| I2CxERR   | _      | BTOIF                                   | BCLIF   | NACKIF | —       | BTOIE | BCLIE     | NACKIE | 585                 |

| I2CxSTAT0 | BFRE   | SMA                                     | MMA     | R      | D       |       | —         | —      | 583                 |

| I2CxSTAT1 | TXWE   | —                                       | TXBE    |        | RXRE    | CLRBF | —         | RXBF   | 584                 |

| I2CxCON0  | EN     | RSEN                                    | S       | CSTR   | MDR     |       | MODE<2:0> | •      | 577                 |

| I2CxCON1  | ACKCNT | ACKDT                                   | ACKSTAT | ACKT   |         | RXOV  | TXU       | CSD    | 579                 |

| I2CxCON2  | ACNT   | ACNT GCEN FME ADB SDAHT<3:2> BFRET<1:0> |         |        |         |       |           |        | 580                 |

| I2CxADR0  |        | ADR<7:0>                                |         |        |         |       |           |        |                     |

| I2CxADR1  |        | ADR<7:1> —                              |         |        |         |       |           |        |                     |

| I2CxADR2  |        |                                         |         | A      | DR<7:0> |       |           |        | 591                 |

| I2CxADR3  |        |                                         |         | A      | DR<7:1> |       |           | —      | 592                 |

| I2CxADB0  |        |                                         |         | A      | DB<7:0> |       |           |        | 593                 |

| I2CxADB1  |        |                                         |         | A      | DB<7:0> |       |           |        | 594                 |

| I2CxCNT   |        |                                         |         | CI     | NT<7:0> |       |           |        | 586                 |

| I2CxPIR   | CNTIF  | ACKTIF                                  |         | WRIF   | ADRIF   | PCIF  | RSCIF     | SCIF   | 587                 |

| I2CxPIE   | CNTIE  | ACKTIE                                  |         | WRIE   | ADRIE   | PCIE  | RSCIE     | SCIE   | 588                 |

| I2CxADR0  | ADR7   | ADR6                                    | ADR5    | ADR4   | ADR3    | ADR2  | ADR1      | ADR0   | 589                 |

| I2CxADR1  | ADR14  | ADR13                                   | ADR12   | ADR11  | ADR10   | ADR9  | ADR8      |        | 590                 |

| I2CxADR2  | ADR7   | ADR6                                    | ADR5    | ADR4   | ADR3    | ADR2  | ADR1      | ADR0   | 591                 |

| I2CxADR3  | ADR14  | ADR13                                   | ADR12   | ADR11  | ADR10   | ADR9  | ADR8      | —      | 592                 |

| I2CxADB0  | ADB7   | ADB6                                    | ADB5    | ADB4   | ADB3    | ADB2  | ADB1      | ADB0   | 593                 |

| I2CxADB1  | ADB7   | ADB6                                    | ADB5    | ADB4   | ADB3    | ADB2  | ADB1      | ADB0   | 594                 |

## TABLE 33-18: SUMMARY OF REGISTERS FOR I<sup>2</sup>C 8-BIT MACRO

**Legend:** — = unimplemented, read as '0'. Shaded cells are unused by the  $I^2C$  module.

| Standa       | rd Operating            | g Conditions (unless otherwise stated                                           | I)   | \<br>\ | $\langle \rangle$ |       |            |

|--------------|-------------------------|---------------------------------------------------------------------------------|------|--------|-------------------|-------|------------|

| Param<br>No. | Sym.                    | Characteristic                                                                  | Min. | Typt   | , Max.            | Units | Conditions |

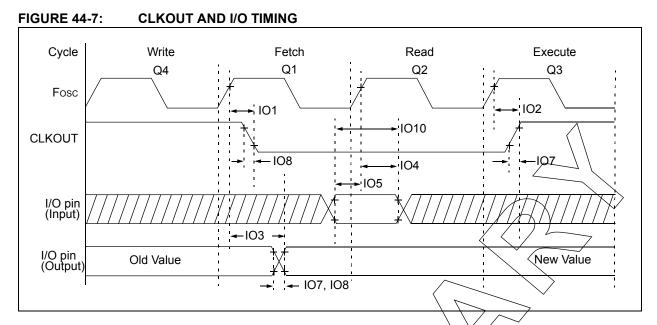

| IO1*         | T <sub>CLKOUTH</sub>    | CLKOUT rising edge delay (rising edge<br>Fosc (Q1 cycle) to falling edge CLKOUT |      |        | 70                | ns    |            |

| IO2*         | T <sub>CLKOUTL</sub>    | CLKOUT falling edge delay (rising edge<br>Fosc (Q3 cycle) to rising edge CLKQUT |      |        | 72                | ns    |            |

| IO3*         | T <sub>IO_VALID</sub>   | Port output valid time (rising edge Fosc<br>(Q1 cycle) to port valid)           |      | 50     | 70                | ns    |            |

| IO4*         | T <sub>IO_SETUP</sub>   | Port input setup time (Setup time before rising edge Fosc – Q2 cxcle)           | 20   |        |                   | ns    |            |

| IO5*         | T <sub>IO_HOLD</sub>    | Port input hold time (Hold time after rising edge Fosc – Q2 cycle)              | 50   |        | _                 | ns    |            |

| IO6*         | T <sub>IOR_SLREN</sub>  | Port I/O rise time, slew rate enabled                                           | —    | 25     | _                 | ns    | VDD = 3.0V |

| 107*         | TIOR_SLRDIS             | Port I/O rise time, slew rate disabled                                          | —    | 5      | _                 | ns    | VDD = 3.0V |

| IO8*         | T <sub>IOF_SLREN</sub>  | Port I/O fall time, slew rate enabled                                           | —    | 25     | _                 | ns    | VDD = 3.0V |

| IO9*         | T <sub>IOF_SLRDIS</sub> | Port I/O fall time, slew rate disabled                                          | _    | 5      |                   | ns    | VDD = 3.0V |

| IO10*        | T <sub>INT</sub>        | INT pin high or low time to trigger an<br>interrupt                             | 25   | _      | _                 | ns    |            |

| IO11*        | TIOC                    | Interrupt-on-Change minimum high or low time to trigger interrupt               | 25   | _      | _                 | ns    |            |

\*These parameters are characterized but not tested.

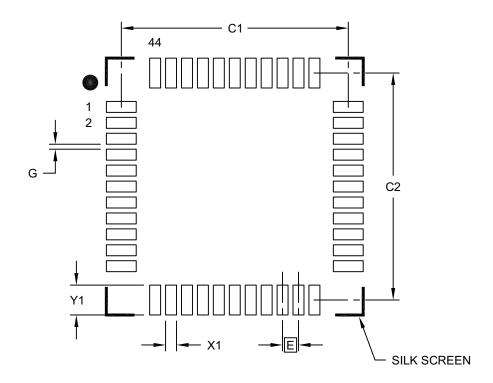

## 44-Lead Plastic Thin Quad Flatpack (PT) - 10X10X1 mm Body, 2.00 mm Footprint [TQFP]

**Note:** For the most current package drawings, please see the Microchip Packaging Specification located at http://www.microchip.com/packaging

## RECOMMENDED LAND PATTERN

| Units                    |    | MILLIMETERS |       |      |

|--------------------------|----|-------------|-------|------|

| Dimension Limits         |    | MIN         | NOM   | MAX  |

| Contact Pitch            | Е  | 0.80 BSC    |       |      |

| Contact Pad Spacing      | C1 |             | 11.40 |      |

| Contact Pad Spacing      | C2 |             | 11.40 |      |

| Contact Pad Width (X44)  | X1 |             |       | 0.55 |

| Contact Pad Length (X44) | Y1 |             |       | 1.50 |

| Distance Between Pads    | G  | 0.25        |       |      |

Notes:

1. Dimensioning and tolerancing per ASME Y14.5M

BSC: Basic Dimension. Theoretically exact value shown without tolerances.

Microchip Technology Drawing No. C04-2076B