Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

#### Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

E·XFl

| Product Status             | Active                                                                      |

|----------------------------|-----------------------------------------------------------------------------|

| Core Processor             | PIC                                                                         |

| Core Size                  | 8-Bit                                                                       |

| Speed                      | 64MHz                                                                       |

| Connectivity               | I <sup>2</sup> C, LINbus, SPI, UART/USART                                   |

| Peripherals                | Brown-out Detect/Reset, DMA, HLVD, POR, PWM, WDT                            |

| Number of I/O              | 36                                                                          |

| Program Memory Size        | 128KB (64K x 16)                                                            |

| Program Memory Type        | FLASH                                                                       |

| EEPROM Size                | 1K x 8                                                                      |

| RAM Size                   | 8K x 8                                                                      |

| Voltage - Supply (Vcc/Vdd) | 1.8V ~ 3.6V                                                                 |

| Data Converters            | A/D 35x12b; D/A 1x5b                                                        |

| Oscillator Type            | Internal                                                                    |

| Operating Temperature      | -40°C ~ 125°C (TA)                                                          |

| Mounting Type              | Surface Mount                                                               |

| Package / Case             | 40-UFQFN Exposed Pad                                                        |

| Supplier Device Package    | 40-UQFN (5x5)                                                               |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/pic18lf47k42-e-mv |

|                            |                                                                             |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

| С          |

|------------|

|            |

| 18         |

| $\tilde{}$ |

|            |

| )F         |

|            |

| 26         |

| S.         |

| N          |

| 7          |

| 4          |

| Ċ          |

| 14         |

| 9          |

| X          |

| 4          |

| 7          |

| ບົ         |

| Ŭ          |

| T          |

| 56         |

| Ň          |

| S          |

| Ζ          |

| X          |

| 4          |

| N          |

Interrupt-on-Change

IOCC3 IOCC4

IOCC5

IOCC6

IOCC7

\_

\_

\_

\_

\_

\_

\_

—

\_

\_

\_

IOCE3

\_

\_

\_

\_

\_

\_

Basic

\_

\_

\_

\_

\_

\_

\_

\_

\_

—

\_

\_

\_ MCLR

VPP

\_

\_

| Ŋ   | 40-Pin PDIP | 44-Pin TQFP | 40-Pin UQFN | 44-Pin QFN | ADC  | Voltage Reference | DAC | Comparators | Zero Cross Detect | I <sup>2</sup> C      | SPI                 | UART                | MSD | Timers/SMT          | CCP and PWM | CWG | CLC | NCO | Clock Reference (CLKR) |

|-----|-------------|-------------|-------------|------------|------|-------------------|-----|-------------|-------------------|-----------------------|---------------------|---------------------|-----|---------------------|-------------|-----|-----|-----|------------------------|

| RC3 | 18          | 37          | 33          | 37         | ANC3 | _                 | _   | _           | _                 | SCL1 <sup>(3,4)</sup> | SCK1 <sup>(1)</sup> | _                   | _   | T2IN <sup>(1)</sup> | _           | _   | _   | _   | _                      |

| RC4 | 23          | 42          | 38          | 42         | ANC4 | _                 | _   | _           | _                 | SDA1 <sup>(3,4)</sup> | SDI1 <sup>(1)</sup> | _                   | _   | _                   | _           | _   | _   | _   | _                      |

| RC5 | 24          | 43          | 39          | 43         | ANC5 | _                 | _   | _           | _                 | _                     | _                   | _                   | _   | T4IN <sup>(1)</sup> | _           | _   | _   | _   | _                      |

| RC6 | 25          | 44          | 40          | 44         | ANC6 | _                 | _   | —           | —                 | —                     | _                   | CTS1 <sup>(1)</sup> | _   | —                   | —           | —   | —   | —   | —                      |

| RC7 | 26          | 1           | 1           | 1          | ANC7 | _                 | _   | _           | _                 | _                     | _                   | RX1 <sup>(1)</sup>  |     | _                   | _           | _   | _   | _   | _                      |

| RD0 | 19          | 38          | 34          | 38         | AND0 | _                 | _   | _           | —                 | (4)                   | _                   | -                   | _   | _                   | _           | _   | _   | _   | _                      |

| RD1 | 20          | 39          | 35          | 39         | AND1 | _                 | _   | _           | _                 | (4)                   | _                   | _                   | _   | _                   | —           | —   | _   | _   | _                      |

| RD2 | 21          | 40          | 36          | 40         | AND2 | -                 | -   | _           | _                 | -                     | -                   | _                   | _   | -                   | -           | -   | _   | -   | _                      |

| RD3 | 22          | 41          | 37          | 41         | AND3 | _                 | _   | _           | -                 | _                     | _                   | _                   | -   | -                   | _           | _   | _   | -   | -                      |

| RD4 | 27          | 2           | 2           | 2          | AND4 | _                 | _   | _           | —                 | _                     | -                   | _                   | _   | -                   | _           | _   | _   | -   | -                      |

| RD5 | 28          | 3           | 3           | 3          | AND5 | _                 | -   | _           | -                 | _                     | _                   |                     | I   | _                   | _           | _   | _   | _   | _                      |

| RD6 | 29          | 4           | 4           | 4          | AND6 | —                 | -   | _           | _                 | -                     | —                   | -                   |     | —                   | -           | -   | —   | —   | _                      |

| RD7 | 30          | 5           | 5           | 5          | AND7 | —                 | —   | _           | _                 | -                     | —                   | -                   |     | —                   | -           | -   | —   | —   | _                      |

| RE0 | 8           | 25          | 23          | 25         | ANE0 | —                 | -   | _           | —                 | _                     | _                   | —                   | -   | —                   | _           | _   | —   | —   | —                      |

| RE1 | 9           | 26          | 24          | 26         | ANE1 | _                 | -   | _           | —                 | _                     | -                   | _                   | _   | _                   | -           | _   | _   | -   | _                      |

| RE2 | 10          | 27          | 25          | 27         | ANE2 | —                 | -   | —           | —                 | _                     | -                   | _                   | _   | —                   | _           | _   | —   | -   | —                      |

| RE3 | 1           | 18          | 16          | 18         | —    | -                 | _   | —           | -                 | —                     | —                   | -                   | _   | —                   | —           | —   | —   | —   | —                      |

| VDD | 11,<br>32   | 7,<br>28    | 7,<br>26    | 7,<br>28   | _    | —                 | —   | _           | -                 | _                     | _                   | _                   | _   | —                   | _           | _   | —   | _   | _                      |

1: This is a PPS remappable input signal. The input function may be moved from the default location shown to one of several other PORTx pins. Note

\_

2: All output signals shown in this row are PPS remappable.

\_

\_

40/44-PIN ALLOCATION TABLE FOR PIC18(L)F4XK42

3: This is a bidirectional signal. For normal module operation, the firmware should map this signal to the same pin in both the PPS input and PPS output registers.

\_

4: These pins can be configured for I<sup>2</sup>C and SMB<sup>TM</sup> 3.0/2.0 logic levels; The SCLx/SDAx signals may be assigned to any of the RB1/RB2/RC3/RC4/RD0/RD1 pins. PPS assignments to the other pins (e.g., RA5) will operate, but input logic levels will be standard TTL/ST as selected by the INLVL register, instead of the I<sup>2</sup>C specific or SMBus input buffer thresholds.

TABLE 2:

12, 31 6, 29 6, 27 6, 30

Vss

## **Table of Contents**

| 1.0 Device Overview                                                                          |     |

|----------------------------------------------------------------------------------------------|-----|

| 2.0 Guidelines for Getting Started with PIC18(L)F26/27/45/46/47/55/56/57K42 Microcontrollers | 22  |

| 3.0 PIC18 CPU                                                                                |     |

| 4.0 Memory Organization                                                                      | 32  |

| 5.0 Device Configuration                                                                     | 63  |

| 6.0 Resets                                                                                   |     |

| 7.0 Oscillator Module (with Fail-Safe Clock Monitor)                                         |     |

| 8.0 Reference Clock Output Module                                                            |     |

| 9.0 Interrupt Controller                                                                     |     |

| 10.0 Power-Saving Operation Modes                                                            | 168 |

| 11.0 Windowed Watchdog Timer (WWDT)                                                          |     |

| 12.0 8x8 Hardware Multiplier                                                                 |     |

| 13.0 Nonvolatile Memory (NVM) Control                                                        |     |

| 14.0 Cyclic Redundancy Check (CRC) Module with Memory Scanner                                |     |

| 15.0 Direct Memory Access (DMA)                                                              |     |

| 16.0 /O Ports                                                                                |     |

| 17.0 Peripheral Pin Select (PPS) Module                                                      |     |

| 18.0 Interrupt-on-Change                                                                     | 283 |

| 19.0 Peripheral Module Disable (PMD)                                                         |     |

| 20.0 Timer0 Module                                                                           | 296 |

| 21.0 Timer1/3/5 Module with Gate Control                                                     | 302 |

| 22.0 Timer2/4/6 Module                                                                       |     |

| 23.0Capture/Compare/PWM Module                                                               |     |

| 24.0 Pulse-Width Modulation (PWM)                                                            |     |

| 25.0Signal Measurement Timer (SMT)                                                           |     |

| 26.0 Complementary Waveform Generator (CWG) Module                                           | 403 |

| 27.0 Configurable Logic Cell (CLC)                                                           |     |

| 28.0 Numerically Controlled Oscillator (NCO) Module                                          |     |

| 29.0 Zero-Cross Detection (ZCD) Module                                                       |     |

| 30.0 Data Signal Modulator (DSM) Module                                                      |     |

| 31.0 Universal Asynchronous Receiver Transmitter (UART) With Protocol Support                | 472 |

| 32.0 Serial Peripheral Interface (SPI) Module                                                |     |

| 33.0 I2C Module                                                                              |     |

| 34.0 Fixed Voltage Reference (FVR)                                                           | 594 |

| 35.0 Temperature Indicator Module                                                            |     |

| 36.0 Analog-to-Digital Converter with Computation (ADC2) Module                              |     |

| 37.0 5-Bit Digital-to-Analog Converter (DAC) Module                                          |     |

| 38.0 Comparator Module                                                                       |     |

| 39.0 High/Low-Voltage Detect (HLVD)                                                          |     |

| 40.0 In-Circuit Serial Programming™ (ICSP™)                                                  |     |

| 41.0 Instruction Set Summary                                                                 |     |

| 42.0 Register Summary                                                                        |     |

| 43.0 Development Support                                                                     |     |

| 44.0 Electrical Specifications                                                               |     |

| 45.0 DC and AC Characteristics Graphs and Tables                                             |     |

| 46.0 Packaging Information                                                                   |     |

## 4.0 MEMORY ORGANIZATION

There are three types of memory in PIC18 microcontroller devices:

- Program Flash Memory

- Data RAM

- Data EEPROM

As Harvard architecture devices, the data and program memories use separate buses; this allows for concurrent access of the two memory spaces. The data EEPROM, for practical purposes, can be regarded as a peripheral device, since it is addressed and accessed through a set of control registers.

Additional detailed information on the operation of the Program Flash Memory and Data EEPROM Memory is provided in Section 13.0 "Nonvolatile Memory (NVM) Control".

## 4.1 Program Flash Memory Organization

PIC18 microcontrollers implement a 21-bit program counter, which is capable of addressing a 2 Mbyte program memory space. Accessing any unimplemented memory will return all '0's (a NOP instruction).

These devices contain the following:

- PIC18(L)F45/55K42: 32 Kbytes of Flash memory, up to 16,384 single-word instructions

- PIC18(L)F26/46/56K42: 64 Kbytes of Flash memory, up to 32,768 single-word instructions

- PIC18(L)F27/47/57K42: 128 Kbytes of Flash memory, up to 65,536 single-word instructions

The Reset vector for the device is at address 00000h. PIC18(L)F26/27/45/46/47/55/56/57K42 devices feature a vectored interrupt controller with a dedicated interrupt vector table in the program memory, see Section 9.0 "Interrupt Controller".

**Note:** For memory information on this family of devices, see Table 4-1 and Table 4-3.

## 4.2 Memory Access Partition (MAP)

Program Flash memory is partitioned into:

- Application Block

- Boot Block, and

- Storage Area Flash (SAF) Block

### 4.2.1 APPLICATION BLOCK

Application block is where the user's program resides by default. Default settings of the configuration bits (BBEN = 1 and  $\overline{SAFEN} = 1$ ) assign all memory in the program Flash memory area to the application block. The WRTAPP configuration bit is used to protect the application block.

#### 4.2.2 BOOT BLOCK

Boot block is an area in program memory that is ideal for storing bootloader code. Code placed in this area can be executed by the CPU. The boot block can be write-protected, independent of the main application block. The Boot Block is enabled by the BBEN bit and size is based on the value of the BBSIZE bits of Configuration word (Register 5-7), see Table 5-1 for boot block sizes. The WRTB Configuration bit is used to write-protect the Boot Block.

### 4.2.3 STORAGE AREA FLASH

Storage Area Flash (SAF) is the area in program memory that can be used as data storage. SAF is enabled by the SAFEN bit of the Configuration word in Register 5-7. If enabled, the code placed in this area cannot be executed by the CPU. The SAF block is placed at the end of memory and spans 128 Words. The WRTSAF Configuration bit is used to write-protect the Storage Area Flash.

**Note:** If write-protected locations are written to, memory is not changed and the WRERR bit defined in Register 13-1 is set.

### TABLE 4-10: SPECIAL FUNCTION REGISTER MAP FOR PIC18(L)F26/27/45/46/47/55/56/57K42 DEVICES BANK 57

| 0          |

|------------|

| 201        |

| 2016-201   |

| 17         |

| Microchip  |

| Technology |

| n          |

| 39FFh | _                      | 39DFh | OSCFRQ                 | 39BFh | _     | 399Fh | _     | 397Fh | _         | 395Fh | WDTU    | 393Fh | _ | 391Fh | _ |

|-------|------------------------|-------|------------------------|-------|-------|-------|-------|-------|-----------|-------|---------|-------|---|-------|---|

| 39FEh | _                      | 39DEh | OSCTUNE                | 39BEh | _     | 399Eh | _     | 397Eh | _         | 395Eh | WDTH    | 393Eh | _ | 391Eh | _ |

| 39FDh |                        | 39DDh | OSCEN                  | 39BDh | _     | 399Dh | _     | 397Dh | SCANTRIG  | 395Dh | WDTL    | 393Dh | _ | 391Dh | — |

| 39FCh | _                      | 39DCh | OSCSTAT                | 39BCh | _     | 399Ch | _     | 397Ch | SCANCON0  | 395Ch | WDTCON1 | 393Ch | _ | 391Ch | — |

| 39FBh | _                      | 39DBh | OSCCON3                | 39BBh | _     | 399Bh | _     | 397Bh | SCANHADRU | 395Bh | WDTCON0 | 393Bh | _ | 391Bh | — |

| 39FAh | —                      | 39DAh | OSCCON2                | 39BAh |       | 399Ah | PIE10 | 397Ah | SCANHADRH | 395Ah | —       | 393Ah |   | 391Ah | — |

| 39F9h | —                      | 39D9h | OSCCON1                | 39B9h | —     | 3999h | PIE9  | 3979h | SCANHADRL | 3959h | —       | 3939h | — | 3919h | — |

| 39F8h | _                      | 39D8h | CPUDOZE                | 39B8h | —     | 3998h | PIE8  | 3978h | SCANLADRU | 3958h | —       | 3938h | — | 3918h | — |

| 39F7h | SCANPR                 | 39D7h | _                      | 39B7h | —     | 3997h | PIE7  | 3977h | SCANLADRH | 3957h | —       | 3937h | — | 3917h | — |

| 39F6h | _                      | 39D6h | _                      | 39B6h | —     | 3996h | PIE6  | 3976h | SCANLADRL | 3956h | —       | 3936h | — | 3916h | — |

| 39F5h |                        | 39D5h |                        | 39B5h | —     | 3995h | PIE5  | 3975h | —         | 3955h | —       | 3935h | _ | 3915h | — |

| 39F4h | DMA2PR                 | 39D4h |                        | 39B4h | —     | 3994h | PIE4  | 3974h | —         | 3954h | —       | 3934h | _ | 3914h | — |

| 39F3h | DMA1PR                 | 39D3h |                        | 39B3h | —     | 3993h | PIE3  | 3973h | —         | 3953h | —       | 3933h | _ | 3913h | — |

| 39F2h | MAINPR                 | 39D2h |                        | 39B2h | —     | 3992h | PIE2  | 3972h | —         | 3952h | —       | 3932h | _ | 3912h | — |

| 39F1h | ISRPR                  | 39D1h | VREGCON <sup>(1)</sup> | 39B1h | —     | 3991h | PIE1  | 3971h | —         | 3951h | —       | 3931h | _ | 3911h | — |

| 39F0h |                        | 39D0h | BORCON                 | 39B0h | —     | 3990h | PIE0  | 3970h | —         | 3950h | —       | 3930h | _ | 3910h | — |

| 39EFh | PRLOCK                 | 39CFh |                        | 39AFh | —     | 398Fh | —     | 396Fh | —         | 394Fh | —       | 392Fh | _ | 390Fh | — |

| 39EEh | _                      | 39CEh | _                      | 39AEh | _     | 398Eh | _     | 396Eh | —         | 394Eh | _       | 392Eh | — | 390Eh | — |

| 39EDh | _                      | 39CDh | _                      | 39ADh | _     | 398Dh | _     | 396Dh | —         | 394Dh | _       | 392Dh | — | 390Dh | — |

| 39ECh | _                      | 39CCh | _                      | 39ACh | _     | 398Ch | _     | 396Ch | —         | 394Ch | _       | 392Ch | — | 390Ch | — |

| 39EBh | _                      | 39CBh | _                      | 39ABh | _     | 398Bh | _     | 396Bh | —         | 394Bh | _       | 392Bh | — | 390Bh | — |

| 39EAh | _                      | 39CAh | _                      | 39AAh | PIR10 | 398Ah | IPR10 | 396Ah | —         | 394Ah | _       | 392Ah | — | 390Ah | — |

| 39E9h | _                      | 39C9h | _                      | 39A9h | PIR9  | 3989h | IPR9  | 3969h | CRCCON1   | 3949h | _       | 3929h | — | 3909h | — |

| 39E8h | _                      | 39C8h | _                      | 39A8h | PIR8  | 3988h | IPR8  | 3968h | CRCCON0   | 3948h | _       | 3928h | — | 3908h | — |

| 39E7h | _                      | 39C7h | PMD7                   | 39A7h | PIR7  | 3987h | IPR7  | 3967h | CRCXORH   | 3947h | _       | 3927h | — | 3907h | — |

| 39E6h | NVMCON2                | 39C6h | PMD6                   | 39A6h | PIR6  | 3986h | IPR6  | 3966h | CRCXORL   | 3946h | —       | 3926h | _ | 3906h | — |

| 39E5h | NVMCON1                | 39C5h | PMD5                   | 39A5h | PIR5  | 3985h | IPR5  | 3965h | CRCSHIFTH | 3945h | _       | 3925h | — | 3905h | — |

| 39E4h | _                      | 39C4h | PMD4                   | 39A4h | PIR4  | 3984h | IPR4  | 3964h | CRCSHIFTL | 3944h | _       | 3924h | _ | 3904h | — |

| 39E3h | NVMDAT                 | 39C3h | PMD3                   | 39A3h | PIR3  | 3983h | IPR3  | 3963h | CRCACCH   | 3943h | _       | 3923h | — | 3903h | — |

| 39E2h | _                      | 39C2h | PMD2                   | 39A2h | PIR2  | 3982h | IPR2  | 3962h | CRCACCL   | 3942h | _       | 3922h | — | 3902h | — |

| 39E1h | NVMADRH <sup>(4)</sup> | 39C1h | PMD1                   | 39A1h | PIR1  | 3981h | IPR1  | 3961h | CRCDATH   | 3941h | _       | 3921h | — | 3901h | — |

| 39E0h | NVMADRL                | 39C0h | PMD0                   | 39A0h | PIR0  | 3980h | IPR0  | 3960h | CRCDATL   | 3940h | —       | 3920h | — | 3900h | — |

Unimplemented data memory locations and registers, read as '0'. Legend:

Note 1: Unimplemented in LF devices.

Unimplemented in PIC18(L)F26/27K42. 2:

Unimplemented in PIC18(L)F26/27/45/46/47K42. 3:

Unimplemented in PIC18(L)F45/55K42. 4:

| REGISIER    | 5-12:         | REVISION ID: REVISION ID REGISTER  |                  |                       |                    |                |                    |                |  |  |  |  |  |

|-------------|---------------|------------------------------------|------------------|-----------------------|--------------------|----------------|--------------------|----------------|--|--|--|--|--|

| R           |               | R                                  | R                | R                     | R                  | R              | R                  | R              |  |  |  |  |  |

| 1           |               | 0                                  | 1                | 0                     |                    | MJR            | REV<5:2>           |                |  |  |  |  |  |

| bit 15      |               |                                    |                  |                       |                    |                |                    | bit 8          |  |  |  |  |  |

|             |               |                                    |                  |                       |                    |                |                    |                |  |  |  |  |  |

| R           |               | R                                  | R                | R                     | R                  | R              | R                  | R              |  |  |  |  |  |

| MJRREV<1:0> |               |                                    |                  |                       | MNRR               | EV<5:0>        |                    |                |  |  |  |  |  |

| bit 7       |               |                                    |                  |                       |                    |                |                    | bit 0          |  |  |  |  |  |

|             |               |                                    |                  |                       |                    |                |                    |                |  |  |  |  |  |

| Legend:     |               |                                    |                  |                       |                    |                |                    |                |  |  |  |  |  |

| R = Readab  | le bit        |                                    | '1' = Bit is set |                       | 0' = Bit is clea   | ared           | x = Bit is unknown |                |  |  |  |  |  |

| bit 15-12   |               | <b>d as</b> '1010<br>se bits are f |                  | <b>e</b> '1010' for a | Ill devices in thi | s family.      |                    |                |  |  |  |  |  |

| bit 11-6    | The:<br>etc.) | se bits are ι                      |                  |                       | sion. A major re   | evision is ind | cated by revisior  | n (A0, B0, C0, |  |  |  |  |  |

| bit 5-0     | MNF           | RREV<5:0>                          | : Minor Revis    | ion ID bits           |                    |                |                    |                |  |  |  |  |  |

## REGISTER 5-12: REVISION ID: REVISION ID REGISTER

These bits are used to identify a minor revision.

**Revision A0 =** 0b00 0000

#### 9.3.2 NATURAL ORDER (HARDWARE) PRIORITY

When more than one interrupt with the same user specified priority level are requested, the priority conflict is resolved by using a method called "Natural Order Priority". Natural order priority is a fixed priority scheme that is based on the Interrupt Vector Table. Table 9-2 shows the natural order priority and the interrupt vector number assigned for each source.

TABLE 9-2:INTERRUPT VECTORPRIORITY TABLE

| Vector<br>NumberInterrupt<br>Source0Software Interrupt1HLVD2OSF3CSW4DMA2CNT4NVM4DMA2OR4NVM4DMA2CR5SCAN4MTO6CRC7IOC8INTO9ZCD10AD11ADT12C113SMT115SMT1PWA16DMA1SCNT17DMA1DCNT18DMA1A20SPI1TX21SPI1TX22SPI123I2C1RX6624I2C1TX6625I2C16626I2C1E6328U1TX70TMR5G30U133TMR1G34TMR235CCP13637NCO38CWG139CLC140INT141C2                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | Martin | later of           |    | Inda f   |

|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------|--------------------|----|----------|

| 1         HLVD           1         HLVD           2         OSF           3         CSW           4         NVM           5         SCAN           4         NVM           6         CRC           7         IOC           8         INTO           9         ZCD           11         ADT           12         C1           5         SMT1           13         SMT1           14         SMT1PRA           15         SMT1PWA           16         DMA1SCNT           17         DMA1DCNT           18         DMA1OR           61         INT2           20         SPI1RX           22         SPI1           23         I2C1RX           64         -           23         I2C1E           64         -           25         I2C1           66         -           24         I2C1E           63         -           25         I2C1           68         -           29         U1E </th <th></th> <th></th> <th></th> <th></th> |        |                    |    |          |

| 2         OSF           3         CSW           4         NVM           4         NVM           5         SCAN           6         CRC           7         IOC           8         INTO           9         ZCD           10         AD           11         ADT           12         C1           13         SMT1           14         SMT1PRA           15         SMT1PWA           16         DMA1SCNT           17         DMA1DCNT           18         DMA10R           60         CLC2           11         SPI1TX           20         SPI1RX           20         SPI1RX           20         SPI1RX           63         -           24         I2C1RX           65         -           24         I2C1RX           66         -           27         U1RX           29         U1E           30         U1           31         TMR0           32         TMR1           34                                                | 0      | Software Interrupt | 42 | DMA2SCNT |

| 3       CSW         4       NVM         4       NVM         5       SCAN         6       CRC         7       IOC         8       INT0         9       ZCD         10       AD         11       ADT         12       C1         13       SMT1         14       SMT1PRA         15       SMT1PWA         16       DMA1SCNT         17       DMA1DCNT         18       DMA1OR         19       DMA1A         20       SPI1TX         20       SPI1TX         20       SPI1TX         21       SPI1TX         22       SPI1         23       I2C1RX         64       -         23       I2C1E         64       -         25       I2C1         66       -         27       U1RX         29       U1E         30       U1         31       TMR0         32       TMR1         33       TMR16         33       TMR1                                                                                                                          | 1      | HLVD               | 43 | DMA2DCNT |

| 4       NVM         4       NVM         5       SCAN         6       CRC         7       IOC         8       INT0         9       ZCD         10       AD         11       ADT         12       C1         13       SMT1         14       SMT1PRA         15       SMT1PWA         16       DMA1SCNT         17       DMA1DCNT         18       DMA1OR         19       DMA1A         20       SPI1RX         20       SPI1RX         22       SPI1         23       I2C1RX         64       -         23       I2C1RX         64       -         23       I2C1RX         64       -         25       I2C1         66       -         25       I2C1         67       -         68       -         27       U1RX         69       -         28       U1TX         70       TMR5         33       TMR1                                                                                                                                   | 2      | OSF                | 44 | DMA2OR   |

| 5       SCAN         6       CRC         7       IOC         8       INTO         9       ZCD         10       AD         11       ADT         12       C1         13       SMT1         15       SMT1PWA         15       SMT1PWA         15       SMT1PWA         15       SMT1PWA         16       DMA1SCNT         17       DMA1OR         18       DMA1OR         19       DMA1A         20       SPI1RX         20       SPI1RX         22       SPI1         63       -         24       I2C1E         65       -         25       I2C1         66       -         25       I2C1         66       -         25       I2C1         66       -         27       U1RX         69       -         28       U1TX         70       TMR5         33       TMR1         75       CLC3         76       -                                                                                                                                | 3      | CSW                | 45 | DMA2A    |

| 6       CRC         7       IOC         8       INTO         9       ZCD         10       AD         11       ADT         12       C1         13       SMT1         15       SMT1PRA         15       SMT1PWA         16       DMA1SCNT         17       DMA1DCNT         18       DMA1OR         19       DMA1A         20       SPI1RX         20       SPI1RX         20       SPI1RX         21       SPI1RX         62       -         21       SPI1RX         63       -         22       SPI1         64       -         23       I2C1RX         64       -         25       I2C1         67       -         26       I2C1E         68       -         29       U1E         31       TMR0         32       TMR1         74       CWG3         75       CLC3         76       -         77       -                                                                                                                               | 4      | NVM                | 46 | I2C2RX   |

| 7       IOC         8       INTO         9       ZCD         10       AD         11       ADT         12       C1         13       SMT1         15       SMT1PRA         15       SMT1PWA         16       DMA1SCNT         17       DMA1OR         18       DMA1OR         20       SPI1RX         21       SPI1TX         20       SPI1RX         21       SPI1X         22       SPI1         23       I2C1         24       I2C1         25       I2C1         66       -         27       U1RX         29       U1E         30       U1         31       TMR0         32       TMR1         33       TMR1G         34       TMR2         35       CCP1         36       -         37       NCO         38       CWG1         39       CLC1         40       INT1                                                                                                                                                                  | 5      | SCAN               | 47 | I2C2TX   |

| 8         INT0           9         ZCD           10         AD           11         ADT           12         C1           13         SMT1           15         SMT1PWA           15         SMT1PWA           16         DMA1SCNT           17         DMA1OR           19         DMA1A           20         SPI1RX           20         SPI1RX           21         SPI1X           62         -           21         SPI1X           63         -           24         I2C1TX           66         -           27         U1RX           29         U1E           30         U1           31         TMR0           32         TMR1           33         TMR1G           34         TMR2           35         CCP1           36         -           37         NCO           38         CWG1           39         CLC1                                                                                                              | 6      | CRC                | 48 | I2C2     |

| 9       ZCD         10       AD         11       ADT         12       C1         13       SMT1         14       SMT1PRA         15       SMT1PWA         16       DMA1SCNT         17       DMA1DCNT         18       DMA1OR         20       SPI1RX         20       SPI1RX         21       SPI1TX         20       SPI1RX         21       SPI1TX         22       SPI1         64       -         23       I2C1RX         64       -         25       I2C1         66       -         25       I2C1         66       -         26       I2C1E         68       -         27       U1RX         29       U1E         30       U1         31       TMR0         32       TMR1         33       TMR1G         34       TMR2         37       NCO         38       CWG1         39       CLC1         40 <t< td=""><td>7</td><td>IOC</td><td>49</td><td>I2C2E</td></t<>                                                                | 7      | IOC                | 49 | I2C2E    |

| 10       AD         11       ADT         12       C1         13       SMT1         14       SMT1PRA         15       SMT1PWA         16       DMA1SCNT         17       DMA1DCNT         18       DMA1OR         20       SPI1RX         20       SPI1RX         20       SPI1RX         21       SPI1TX         20       SPI1RX         21       SPI1TX         63          24       I2C1RX         66       -         25       I2C1         66       -         25       I2C1         66       -         25       I2C1         66       -         26       I2C1E         28       U1TX         70       TMR5         72       U1RX         70       TMR5         71       TMR6         31       TMR0         32       TMR1         33       TMR1G         34       TMR2         35       CCP1         36                                                                                                                              | 8      | INT0               | 50 | U2RX     |

| 11       ADT         12       C1         13       SMT1         13       SMT1PRA         15       SMT1PWA         15       SMT1PWA         16       DMA1SCNT         17       DMA1DCNT         18       DMA1OR         20       SPI1RX         20       SPI1RX         20       SPI1RX         21       SPI1TX         22       SPI1         23       I2C1RX         24       I2C1TX         25       I2C1         66       -         27       U1RX         29       U1E         30       U1         31       TMR0         32       TMR1         33       TMR1G         34       TMR2         37       NCO         38       CWG1         39       CLC1         40       INT1                                                                                                                                                                                                                                                            | 9      | ZCD                | 51 | U2TX     |

| 12       C1         13       SMT1         13       SMT1PRA         15       SMT1PWA         15       SMT1PWA         16       DMA1SCNT         17       DMA1DCNT         18       DMA1OR         19       DMA1A         20       SPI1RX         20       SPI1RX         21       SPI1TX         22       SPI1         23       I2C1RX         24       I2C1TX         26       I2C1E         27       U1RX         29       U1E         30       U1         31       TMR0         32       TMR1G         33       TMR1G         34       TMR2         37       NCO         38       CWG1         39       CLC1         40       INT1                                                                                                                                                                                                                                                                                                   | 10     | AD                 | 52 | U2E      |

| 13       SMT1         14       SMT1PRA         15       SMT1PWA         15       SMT1PWA         16       DMA1SCNT         17       DMA1DCNT         18       DMA1OR         19       DMA1A         20       SPI1RX         20       SPI1RX         20       SPI1RX         21       SPI1TX         22       SPI1         23       I2C1RX         24       I2C1TX         26       I2C1E         27       U1RX         29       U1E         30       U1         31       TMR0         32       TMR1G         33       TMR1G         34       TMR2         37       NCO         38       CWG1         39       CLC1         40       INT1                                                                                                                                                                                                                                                                                               | 11     | ADT                | 53 | U2       |

| 14       SMT1PRA         15       SMT1PWA         15       SMT1PWA         16       DMA1SCNT         17       DMA1DCNT         18       DMA1OR         19       DMA1A         20       SPI1RX         20       SPI1RX         21       SPI1TX         22       SPI1         23       I2C1RX         24       I2C1TX         25       I2C1         26       I2C1E         28       U1TX         29       U1E         30       U1         31       TMR0         32       TMR1G         33       TMR1G         34       TMR2         37       NCO         38       CWG1         39       CLC1         40       INT1                                                                                                                                                                                                                                                                                                                       | 12     | C1                 | 54 | TMR3     |

| 15       SMT1PWA         16       DMA1SCNT         17       DMA1DCNT         18       DMA1OR         19       DMA1A         20       SPI1RX         20       SPI1RX         21       SPI1RX         22       SPI1         23       I2C1RX         24       I2C1TX         25       I2C1         26       I2C1E         27       U1RX         29       U1E         30       U1         31       TMR0         32       TMR1         33       TMR1G         34       TMR2         37       NCO         38       CWG1         39       CLC1         40       INT1                                                                                                                                                                                                                                                                                                                                                                          | 13     | SMT1               | 55 | TMR3G    |

| 16       DMA1SCNT         17       DMA1DCNT         18       DMA1OR         19       DMA1A         20       SPI1RX         20       SPI1RX         21       SPI1TX         22       SPI1         23       I2C1RX         24       I2C1TX         25       I2C1         26       I2C1E         28       U1TX         29       U1E         31       TMR0         32       TMR1         33       TMR1G         34       TMR2         37       NCO         38       CWG1         39       CLC1         40       INT1                                                                                                                                                                                                                                                                                                                                                                                                                       | 14     | SMT1PRA            | 56 | TMR4     |

| 17       DMA1DCNT         18       DMA1OR         19       DMA1A         20       SPI1RX         20       SPI1RX         21       SPI1TX         22       SPI1         23       I2C1RX         24       I2C1TX         25       I2C1         26       I2C1E         28       U1TX         29       U1E         31       TMR0         32       TMR1         33       TMR1G         34       TMR2         37       NCO         38       CWG1         39       CLC1         40       INT1                                                                                                                                                                                                                                                                                                                                                                                                                                                 | 15     | SMT1PWA            | 57 | CCP2     |

| 18       DMA1OR         19       DMA1A         20       SPI1RX         20       SPI1RX         21       SPI1TX         22       SPI1         23       I2C1RX         24       I2C1TX         25       I2C1         26       I2C1E         28       U1TX         29       U1E         31       TMR0         32       TMR1         33       TMR1G         34       TMR2         37       NCO         38       CWG1         39       CLC1         40       INT1                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | 16     | DMA1SCNT           | 58 | —        |

| 19       DMA1A         20       SPI1RX         21       SPI1RX         22       SPI1         23       I2C1RX         24       I2C1TX         25       I2C1         26       I2C1E         27       U1RX         28       U1TX         70       TMR5         29       U1E         31       TMR0         32       TMR1         33       TMR1G         34       TMR2         37       NCO         38       CWG1         39       CLC1         40       INT1                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | 17     | DMA1DCNT           | 59 | CWG2     |

| 20       SPI1RX         20       SPI1RX         21       SPI1TX         22       SPI1         23       I2C1RX         24       I2C1TX         25       I2C1         26       I2C1E         27       U1RX         28       U1TX         29       U1E         31       TMR0         32       TMR1         33       TMR1G         34       TMR2         37       NCO         38       CWG1         39       CLC1         40       INT1                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | 18     | DMA10R             | 60 | CLC2     |

| 21       SPI1TX         22       SPI1         23       I2C1RX         24       I2C1TX         25       I2C1         26       I2C1E         27       U1RX         28       U1TX         70       TMR5         29       U1E         31       TMR0         32       TMR1         33       TMR1G         34       TMR2         35       CCP1         36       -         37       NCO         38       CWG1         39       CLC1         40       INT1                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | 19     | DMA1A              | 61 | INT2     |

| 22       SPI1         23       I2C1RX         24       I2C1TX         25       I2C1         26       I2C1E         27       U1RX         28       U1TX         29       U1E         30       U1         31       TMR0         32       TMR1         33       TMR1G         34       TMR2         37       NCO         38       CWG1         39       CLC1         40       INT1                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | 20     | SPI1RX             | 62 | _        |

| 23       I2C1RX         24       I2C1TX         25       I2C1         26       I2C1E         27       U1RX         28       U1TX         29       U1E         30       U1         31       TMR0         32       TMR1         33       TMR1G         34       TMR2         36       -         37       NCO         38       CWG1         39       CLC1         40       INT1                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | 21     | SPI1TX             | 63 | —        |

| 24       I2C1TX       66          25       I2C1       67          26       I2C1E       68          27       U1RX       69          28       U1TX       70       TMR5         29       U1E       71       TMR5G         30       U1       72       TMR6         31       TMR0       73       CCP3         32       TMR1       74       CWG3         33       TMR1G       75       CLC3         34       TMR2       76       -         35       CCP1       77       -         36       -       78       -         37       NCO       79       -         38       CWG1       80       CCP4         39       CLC1       81       CLC4         40       INT1       -       -                                                                                                                                                                                                                                                                | 22     | SPI1               | 64 | —        |

| 25       I2C1         26       I2C1E         27       U1RX         28       U1TX         29       U1E         30       U1         31       TMR0         32       TMR1         33       TMR1G         34       TMR2         36       -         37       NCO         38       CWG1         39       CLC1         40       INT1                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | 23     | I2C1RX             | 65 | —        |

| 26       I2C1E       68          27       U1RX       69          28       U1TX       70       TMR5         29       U1E       71       TMR5G         30       U1       72       TMR6         31       TMR0       73       CCP3         32       TMR1       74       CWG3         33       TMR2       76       -         35       CCP1       77       -         36       -       78       -         37       NCO       79       -         38       CWG1       80       CCP4         39       CLC1       81       CLC4         40       INT1       -       -                                                                                                                                                                                                                                                                                                                                                                             | 24     | I2C1TX             | 66 | —        |

| 27       U1RX       69       —         28       U1TX       70       TMR5         29       U1E       71       TMR5G         30       U1       72       TMR6         31       TMR0       73       CCP3         32       TMR1       74       CWG3         33       TMR2       76       —         35       CCP1       77       —         36       —       78       —         37       NCO       79       —         38       CWG1       80       CCP4         39       CLC1       81       CLC4         40       INT1       —       —                                                                                                                                                                                                                                                                                                                                                                                                       | 25     | I2C1               | 67 | —        |

| 28       U1TX       70       TMR5         29       U1E       71       TMR5G         30       U1       72       TMR6         31       TMR0       73       CCP3         32       TMR1       74       CWG3         33       TMR1G       75       CLC3         34       TMR2       76       -         35       CCP1       77       -         36       -       78       -         37       NCO       79       -         38       CWG1       80       CCP4         39       CLC1       81       CLC4         40       INT1       -       -                                                                                                                                                                                                                                                                                                                                                                                                   | 26     | I2C1E              | 68 | _        |

| 29       U1E       71       TMR5G         30       U1       72       TMR6         31       TMR0       73       CCP3         32       TMR1       74       CWG3         33       TMR1G       75       CLC3         34       TMR2       76       -         35       CCP1       77       -         36       -       78       -         37       NCO       79       -         38       CWG1       80       CCP4         39       CLC1       81       CLC4                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | 27     | U1RX               | 69 | —        |

| 30       U1         31       TMR0         32       TMR1         33       TMR1G         34       TMR2         35       CCP1         36       -         37       NCO         38       CWG1         39       CLC1         40       INT1                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | 28     | U1TX               | 70 | TMR5     |

| 31       TMR0       73       CCP3         32       TMR1       74       CWG3         33       TMR1G       75       CLC3         34       TMR2       76       -         35       CCP1       77       -         36       -       78       -         37       NCO       79       -         38       CWG1       80       CCP4         39       CLC1       81       CLC4                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | 29     | U1E                | 71 | TMR5G    |

| 32     TMR1       33     TMR1G       34     TMR2       35     CCP1       36     -       37     NCO       38     CWG1       39     CLC1       40     INT1                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | 30     | U1                 | 72 | TMR6     |

| 33       TMR1G       75       CLC3         34       TMR2       76       -         35       CCP1       77       -         36       -       78       -         37       NCO       79       -         38       CWG1       80       CCP4         39       CLC1       81       CLC4         40       INT1       -       -                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | 31     | TMR0               | 73 | CCP3     |

| 34         TMR2         76         —           35         CCP1         77         —           36         —         78         —           37         NCO         79         —           38         CWG1         80         CCP4           39         CLC1         81         CLC4           40         INT1         —         —                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | 32     | TMR1               | 74 | CWG3     |

| 35         CCP1         77         —           36         —         78         —           37         NCO         79         —           38         CWG1         80         CCP4           39         CLC1         81         CLC4           40         INT1         —         —                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | 33     | TMR1G              | 75 | CLC3     |

| 36         —           37         NCO           38         CWG1           39         CLC1           40         INT1                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | 34     | TMR2               | 76 | —        |

| 37         NCO         79         —           38         CWG1         80         CCP4           39         CLC1         81         CLC4           40         INT1                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | 35     | CCP1               | 77 | _        |

| 38         CWG1         80         CCP4           39         CLC1         81         CLC4           40         INT1                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | 36     | —                  | 78 | _        |

| 39         CLC1         81         CLC4           40         INT1                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | 37     | NCO                | 79 | —        |

| 40 INT1                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 38     | CWG1               | 80 | CCP4     |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | 39     | CLC1               | 81 |          |

| 41 C2                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | 40     | INT1               |    | •        |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | 41     | C2                 |    |          |

The natural order priority scheme has vector interrupt 0 as the highest priority and vector interrupt 81 as the lowest priority.

For example, when two concurrently occurring interrupt sources that are both designated high priority using the IPRx register will be resolved using the natural order priority (i.e., the interrupt with a lower corresponding vector number will preempt the interrupt with the higher vector number).

The ability for the user to assign every interrupt source to high or low priority levels means that the user program can give an interrupt with a low natural order priority a higher overall priority level.

## 9.4 Interrupt Operation

All pending interrupts are indicated by the flag bit being equal to a '1' in the PIRx register. All pending interrupts are resolved using the priority scheme explained in Section 9.3 "Interrupt Priority".

Once the interrupt source to be serviced is resolved, the program execution vectors to the resolved interrupt vector addresses, as explained in **Section 9.2** "Interrupt Vector Table (IVT)". The vector number is also stored in the WREG register. Most of the flag bits are required to be cleared by the application software, but in some cases, device hardware clears the interrupt automatically. Some flag bits are read-only in the PIRx registers, these flags are a summary of the source interrupts and the corresponding interrupt flags of the source must be cleared.

A valid interrupt can be either a high or low priority interrupt when in main routine or a high priority interrupt when in low priority Interrupt Service Routine. Depending on order of interrupt requests received and their relative timing, the CPU will be in the state of execution indicated by the STAT bits of the INTCON1 register (Register 9-2).

The State machine shown in Figure 9-1 and the subsequent sections detail the execution of interrupts when received in different orders.

Note: The state of GIEH/L is not changed by the hardware when servicing an interrupt. The internal state machine is used to keep track of execution states. These bits can be manipulated in the user code resulting in transferring execution to the main routine and ignoring existing interrupts.

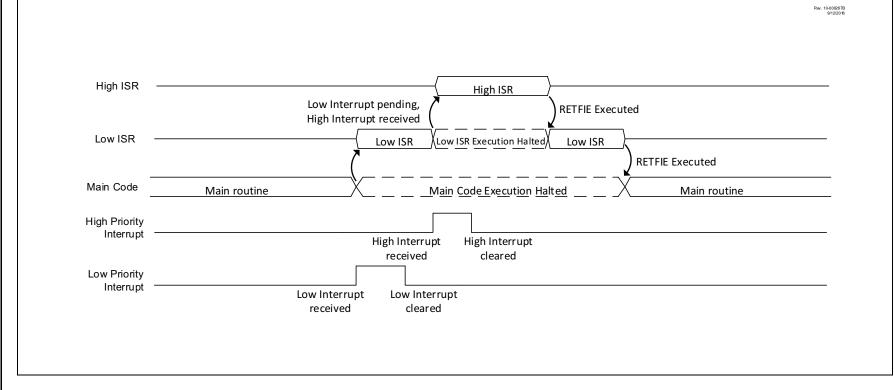

## 9.4.3 PREEMPTING LOW PRIORITY INTERRUPTS

Low-priority interrupts can be preempted by high priority interrupts. While in the low priority ISR, if a high-priority interrupt arrives, the high priority interrupt request is generated and the low priority ISR is suspended, while the high priority ISR is executed, see Figure 9-4.

After the high priority ISR is complete and if any other high priority interrupt requests are not active, the execution returns to the preempted low priority ISR.

**Note 1:** The high priority interrupt flag must be cleared to avoid recursive interrupts.

2: If a low-priority ISR was already serviced halfway before moving on to a high priority ISR, then the low priority ISR is completely serviced even if user code clears GIEL.

## FIGURE 9-4: INTERRUPT EXECUTION: HIGH PRIORITY INTERRUPT PREEMPTING LOW PRIORITY INTERRUPTS

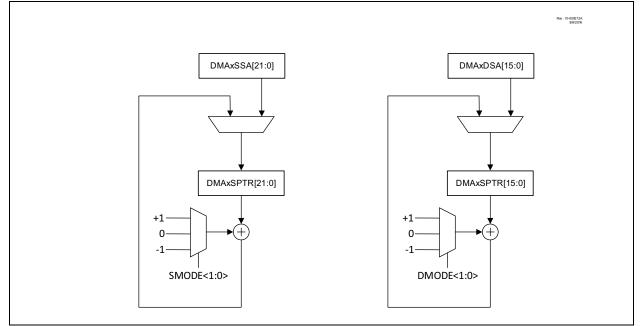

### FIGURE 15-2: DMA POINTERS BLOCK DIAGRAM

The DMA can initiate data transfers from the PFM, Data EEPROM or SFR/GPR Space. The SMR<1:0> bits in the DMAxCON1 register are used to select the type of memory being pointed to by the Source Address Pointer. The SMR<1.0> bits are required because the PFM and SFR/GPR spaces have overlapping addresses that do not allow the specified address to uniquely define the memory location to be accessed.

| Note 1: | For proper memory read access to occur, |  |  |  |  |  |  |  |  |  |

|---------|-----------------------------------------|--|--|--|--|--|--|--|--|--|

|         | the combination of address and space    |  |  |  |  |  |  |  |  |  |

|         | selection must be valid.                |  |  |  |  |  |  |  |  |  |

2: The destination does not have space selection bits because it can only write to the SFR/GPR space.

## 15.4.2 DMA MESSAGE SIZE/COUNTERS

A transaction is the transfer of one byte. A message consists of one or more transactions. A complete DMA process consists of one or more messages. The size registers determine how many transactions are in a message. The DMAxSSZ registers determine the source size and DMAxDSZ registers determine the destination size.

When a DMA transfer is initiated, the size registers are copied to corresponding counter registers that control the duration of the message. The DMAxSCNT registers count the source transactions and the DMAxDCNT registers count the destination transactions. Both are simultaneously decremented by one after each transaction. A message is started by setting the DGO bit of the DMAxCON0 register and terminates when the smaller of the two counters reaches zero.

When either counter reaches zero the DGO bit is cleared and the counter and pointer registers are immediately reloaded with the corresponding size and address data. If the other counter did not reach zero then the next message will continue with the count and address corresponding to that register.

When the source and destination size registers are not equal, then the ratio of the largest to the smallest size determines how many messages are in the DMA process. For example, when the destination size is 6 and the source size is 2, then each message will consist of two transactions and the complete DMA process will consist of three messages. When the larger size is not an even integer of the smaller size, then the last message in the process will terminate early when the larger count reaches zero. In that case, the larger counter will reset and the smaller counter will have a remainder skewing any subsequent messages by that amount.

|                      | PPS Input  | Default Pin         | Register              |       |      |                      |   | In | put Ava | ilable fro | m Selecte            | ed POR | Тх |   |   |   |   |

|----------------------|------------|---------------------|-----------------------|-------|------|----------------------|---|----|---------|------------|----------------------|--------|----|---|---|---|---|

| Peripheral           | Register   | Selection at<br>POR | Reset Value<br>at POR | PIC18 | 7K42 | PIC18(L)F45/46/47K42 |   |    |         |            | PIC18(L)F55/56/57K42 |        |    |   |   |   |   |

| Interrupt 0          | INTOPPS    | RB0                 | 0b0 1000              | А     | В    | _                    | Α | В  | _       | —          | —                    | Α      | В  | — | _ |   | — |

| Interrupt 1          | INT1PPS    | RB1                 | 0b0 1001              | А     | В    | —                    | Α | В  | _       | —          | —                    | _      | В  | — | D | _ | - |

| Interrupt 2          | INT2PPS    | RB2                 | 0b0 1010              | А     | В    | —                    | А | В  | —       | —          | —                    | _      | В  | — | - | — | F |

| Timer0 Clock         | TOCKIPPS   | RA4                 | 0b0 0100              | А     | В    | —                    | Α | В  | _       | —          | —                    | А      | _  | — | _ | _ | F |

| Timer1 Clock         | T1CKIPPS   | RC0                 | 0b1 0000              | А     | _    | С                    | Α |    | С       | —          | —                    | _      | _  | С | _ | E | - |

| Timer1 Gate          | T1GPPS     | RB5                 | 0b0 1101              | _     | В    | С                    | _ | В  | С       | —          | —                    | _      | В  | С | _ | _ | - |