Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

E·XFI

| Product Status             | Active                                                                      |

|----------------------------|-----------------------------------------------------------------------------|

| Core Processor             | PIC                                                                         |

| Core Size                  | 8-Bit                                                                       |

| Speed                      | 64MHz                                                                       |

| Connectivity               | I <sup>2</sup> C, LINbus, SPI, UART/USART                                   |

| Peripherals                | Brown-out Detect/Reset, DMA, HLVD, POR, PWM, WDT                            |

| Number of I/O              | 36                                                                          |

| Program Memory Size        | 128KB (64K x 16)                                                            |

| Program Memory Type        | FLASH                                                                       |

| EEPROM Size                | 1K x 8                                                                      |

| RAM Size                   | 8K x 8                                                                      |

| Voltage - Supply (Vcc/Vdd) | 1.8V ~ 3.6V                                                                 |

| Data Converters            | A/D 35x12b; D/A 1x5b                                                        |

| Oscillator Type            | Internal                                                                    |

| Operating Temperature      | -40°C ~ 125°C (TA)                                                          |

| Mounting Type              | Surface Mount                                                               |

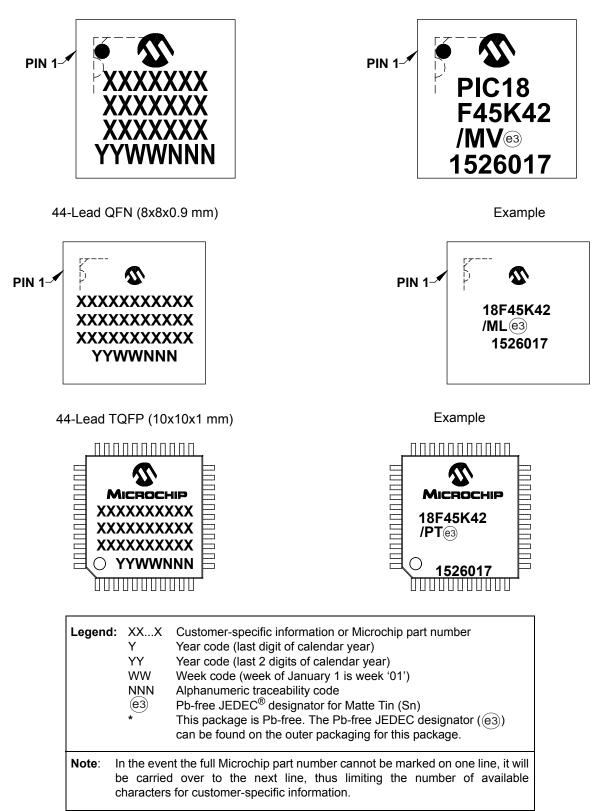

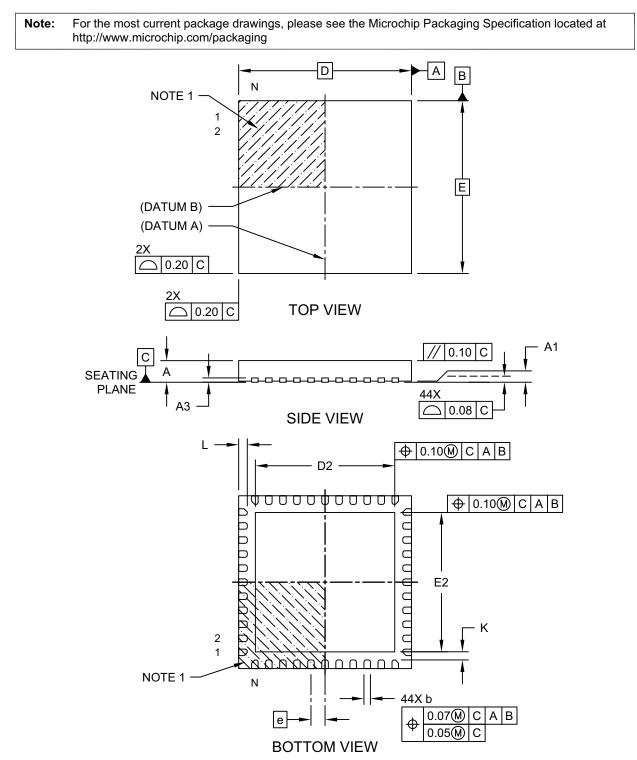

| Package / Case             | 44-TQFP                                                                     |

| Supplier Device Package    | 44-TQFP (10x10)                                                             |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/pic18lf47k42-e-pt |

|                            |                                                                             |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

# 9.0 INTERRUPT CONTROLLER

The Vectored Interrupt Controller module reduces the numerous peripheral interrupt request signals to a single interrupt request signal to the CPU. This module includes the following major features:

- Interrupt Vector Table (IVT) with a unique vector for each interrupt source

- · Fixed and ensured interrupt latency

- Programmable base address for Interrupt Vector Table (IVT) with lock

- Two user-selectable priority levels High priority and Low priority

- Two levels of context saving

- Interrupt state status bits to indicate the current execution status of the CPU

The Interrupt Controller module assembles all of the interrupt request signals and resolves the interrupts based on both a fixed natural order priority (i.e., determined by the Interrupt Vector Table), and a user-assigned priority (i.e., determined by the IPRx registers), thereby eliminating scanning of interrupt sources.

# 9.1 Interrupt Control and Status Registers

The devices in this family implement the following registers for the interrupt controller:

- INTCON0, INTCON1 Control Registers

- PIRx Peripheral Interrupt Status Registers

- PIEx Peripheral Interrupt Enable Registers

- IPRx Peripheral Interrupt Priority Registers

- IVTBASE<20:0> Address Registers

- IVTLOCK Register

Global interrupt control functions and external interrupts are controlled from the INTCON0 register. The INTCON1 register contains the status flags for the Interrupt controller.

The PIRx registers contain all of the interrupt request flags. Each source of interrupt has a status bit, which is set by the respective peripherals or an external signal and is cleared via software.

The PIEx registers contain all of the interrupt enable bits. These control bits are used to individually enable interrupts from the peripherals or external signals.

The IPRx registers are used to set the Interrupt Priority Level for each source of interrupt. Each user interrupt source can be assigned to either a high or low priority.

The IVTBASE register is user programmable and is used to determine the start address of the Interrupt Vector Table and the IVTLOCK register is used to prevent any unintended writes to the IVTBASE register. There are two other configuration bits that control the way the interrupt controller can be configured.

- · CONFIG2L<3>, MVECEN bit

- CONFIG2L<4>, IVT1WAY bit

The MVECEN bit in CONFIG2L determines whether the Vector table is used to determine the interrupt priorities.

When the IVT1WAY determines the number of times the IVTLOCKED bit can be cleared and set after a device Reset. See Section

9.2.3 "Interrupt Vector Table (IVT) address calculation" for details.

#### REGISTER 11-3: WDTPSL: WWDT PRESCALE SELECT LOW BYTE REGISTER (READ-ONLY)

| R-0/0            | R-0/0 | R-0/0                | R-0/0 | R-0/0          | R-0/0            | R-0/0            | R-0/0        |

|------------------|-------|----------------------|-------|----------------|------------------|------------------|--------------|

|                  |       |                      | PSCN  | NT<7:0>        |                  |                  |              |

| bit 7            |       |                      |       |                |                  |                  | bit 0        |

|                  |       |                      |       |                |                  |                  |              |

| Legend:          |       |                      |       |                |                  |                  |              |

| R = Readable     | bit   | W = Writable bit     |       | U = Unimpler   | nented bit, read | 1 as '0'         |              |

| u = Bit is uncha | anged | x = Bit is unknow    | n     | -n/n = Value a | at POR and BO    | R/Value at all o | other Resets |

| '1' = Bit is set |       | '0' = Bit is cleared | b     |                |                  |                  |              |

#### bit 7-0 **PSCNT<7:0>:** Prescale Select Low Byte bits<sup>(1)</sup>

**Note 1:** The 18-bit WDT prescale value, PSCNT<17:0> includes the WDTPSL, WDTPSH and the lower bits of the WDTTMR registers. PSCNT<17:0> is intended for debug operations and should not be read during normal operation.

#### REGISTER 11-4: WDTPSH: WWDT PRESCALE SELECT HIGH BYTE REGISTER (READ-ONLY)

| R-0/0 | R-0/0 | R-0/0 | R-0/0 | R-0/0  | R-0/0 | R-0/0 | R-0/0 |

|-------|-------|-------|-------|--------|-------|-------|-------|

|       |       |       | PSCNT | <15:8> |       |       |       |

| bit 7 |       |       |       |        |       |       | bit 0 |

|       |       |       |       |        |       |       |       |

| Legend:              |                      |                                                       |

|----------------------|----------------------|-------------------------------------------------------|

| R = Readable bit     | W = Writable bit     | U = Unimplemented bit, read as '0'                    |

| u = Bit is unchanged | x = Bit is unknown   | -n/n = Value at POR and BOR/Value at all other Resets |

| '1' = Bit is set     | '0' = Bit is cleared |                                                       |

### bit 7-0 **PSCNT<15:8>:** Prescale Select High Byte bits<sup>(1)</sup>

**Note 1:** The 18-bit WDT prescale value, PSCNT<17:0> includes the WDTPSL, WDTPSH and the lower bits of the WDTTMR registers. PSCNT<17:0> is intended for debug operations and should not be read during normal operation.

### REGISTER 14-9: CRCXORH: CRC XOR HIGH BYTE REGISTER

| R/W-x/x         | R/W-x/x | R/W-x/x            | R/W-x/x | R/W-x/x        | R/W-x/x          | R/W-x/x          | R/W-x/x     |

|-----------------|---------|--------------------|---------|----------------|------------------|------------------|-------------|

|                 |         |                    | X<1     | 5:8>           |                  |                  |             |

| bit 7           |         |                    |         |                |                  |                  | bit 0       |

|                 |         |                    |         |                |                  |                  |             |

| Legend:         |         |                    |         |                |                  |                  |             |

| R = Readable    | bit     | W = Writable       | bit     | U = Unimplen   | nented bit, read | l as '0'         |             |

| u = Bit is unch | anged   | x = Bit is unknown |         | -n/n = Value a | at POR and BO    | R/Value at all o | ther Resets |

bit 7-0 X<15:8>: XOR of Polynomial Term X<sup>n</sup> Enable bits

#### REGISTER 14-10: CRCXORL: CRC XOR LOW BYTE REGISTER

'0' = Bit is cleared

| R/W-x/x | U-1   |

|---------|---------|---------|---------|---------|---------|---------|-------|

|         |         |         | X<7:1>  |         |         |         | —     |

| bit 7   |         |         |         |         |         |         | bit 0 |

| Legend:              |                      |                                                       |

|----------------------|----------------------|-------------------------------------------------------|

| R = Readable bit     | W = Writable bit     | U = Unimplemented bit                                 |

| u = Bit is unchanged | x = Bit is unknown   | -n/n = Value at POR and BOR/Value at all other Resets |

| '1' = Bit is set     | '0' = Bit is cleared |                                                       |

bit 7-1 X<7:1>: XOR of Polynomial Term X<sup>n</sup> Enable bits

bit 0 Unimplemented: Read as '1'

'1' = Bit is set

| bit 7 Legend: R = Readable bit W = Writable bit U = Unimplemented bit, read as '0' u = Bit is unchanged x = Bit is unknown -n/n = Value at POR and BOR/Value at all other R '1' = Bit is set '0' = Bit is cleared HC = Bit is cleared by hardware bit 7 EN: Scanner Enable bit <sup>(1)</sup> 1 = Scanner is enabled 0 = Scanner trigger is disabled bit 6 TRIGEN: Scanner Trigger Isable bit <sup>(2)</sup> 1 = Scanner trigger is disabled Bit 5 SGG: Scanner GO bit <sup>(3, 4)</sup> 1 = When the CRC is ready, the Memory region set by the MREG bit will be accessed and data is to the CRC peripheral. 0 = Scanner operations will not occur bit 4-3 Unimplemented: Read as '0' bit 2 MREG: Scanner Burst Mode bit 1 BURSTMD: Scanner Burst Mode bit 1 BURSTMD: Scanner Burst Mode bit 1 BURSTMD: Scanner Burst Mode bit 1 = Memory access request to the CPU Arbiter is always true 0 = Memory access request to the CPU Arbiter is dependent on the CRC request and Trigger Refer Table 14-1. bit 0 BUSY: Scanner Busy Indicator bit 1 = Scanner cycle is in process 0 = Scanner cycle is oneyte (or never started) Note 1: Setting EN = 1 (SCANCON0 register) does not affect any other register content. 2: Scanner trigger selection can be set using the SCANTRIG register. 3: This bit can be cleared in software. It is cleared in hardware when LADR>HADR (and a data cycle is                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | R/W-0/0        | ) R/W-0/0                                                     | R/W/HC-0/0                                                   | U-0                                       | U-0                                          | R/W-0/0                | R/W-0/0           | R-0/0         |

|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------|---------------------------------------------------------------|--------------------------------------------------------------|-------------------------------------------|----------------------------------------------|------------------------|-------------------|---------------|

| Legend:         R = Readable bit       W = Writable bit       U = Unimplemented bit, read as '0'         u = Bit is unchanged       x = Bit is unknown       -n/n = Value at POR and BOR/Value at all other R         '1' = Bit is set       '0' = Bit is cleared       HC = Bit is cleared by hardware         bit 7       EN: Scanner Enable bit <sup>(1)</sup> 1 = Scanner is enabled         0 = Scanner is enabled       0 = Scanner trigger Enable bit <sup>(2)</sup> 1 = Scanner trigger is disabled       Refer Table 14-1.         bit 5       SGO: Scanner GO bit <sup>(3, 4)</sup> 1 = When the CRC is ready, the Memory region set by the MREG bit will be accessed and data is to the CRC peripheral.         0 = Scanner operations will not occur         bit 4-3       Unimplemented: Read as '0'         bit 2       MREG: Scanner Memory Region Select bit <sup>(2)</sup> 1 = Scanner address points to Drata EEPROM       0 = Scanner address points to Program Flash Memory         bit 1       BURSTMD: Scanner Burst Mode bit         1 = Memory access request to the CPU Arbiter is always true       0 = Memory access request to the CPU Arbiter is dependent on the CRC request and Trigger Refer Table 14-1.         bit 0       BUSY: Scanner Busy Indicator bit       1 = Scanner cycle is in process         0 = Scanner cycle is in process       0 = Scanner cycle is in process         0 = Scanner cycle is in process                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | EN             | TRIGEN                                                        | SGO                                                          |                                           | _                                            | MREG                   | BURSTMD           | BUSY          |

| R = Readable bit       W = Writable bit       U = Unimplemented bit, read as '0'         u = Bit is unchanged       x = Bit is unknown       -n/n = Value at POR and BOR/Value at all other R         '1' = Bit is set       '0' = Bit is cleared       HC = Bit is cleared by hardware         bit 7       EN: Scanner Enable bit <sup>(1)</sup> 1         1 = Scanner is enabled       0 = Scanner trigger Enable bit <sup>(2)</sup> 1 = Scanner trigger is enabled       0 = Scanner trigger is disabled         bit 5       SGO: Scanner Go bit <sup>(3, 4)</sup> 1 = When the CRC is ready, the Memory region set by the MREG bit will be accessed and data is to the CRC peripheral.         0 = Scanner operations will not occur         bit 4-3       Unimplemented: Read as '0'         bit 1       BURSTIND: Scanner Burst Mode bit         1 = Memory access request to the CPU Arbiter is always true         0 = Scanner ddress points to Data EEPROM         0 = Scanner address points to Program Flash Memory         bit 1       BURSTIND: Scanner Burst Mode bit         1 = Memory access request to the CPU Arbiter is always true         0 = Scanner cycle is in process         0 = Scanner cycle is in process         0 = Scanner cycle is in process         0 = Scanner trigger selection can be set using the SCANTRIG register.         3:       This bit can be cleared in software. It i                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | bit 7          | ·                                                             |                                                              |                                           | ·                                            | -                      | •                 | bit           |

| <ul> <li>u = Bit is unchanged x = Bit is unknown -n/n = Value at POR and BOR/Value at all other R<br/>(1' = Bit is set '0' = Bit is cleared HC = Bit is cleared by hardware</li> <li>bit 7 EN: Scanner Enable bit<sup>(1)</sup><br/>1 = Scanner is enabled<br/>0 = Scanner is disabled<br/>bit 6 TRIGEN: Scanner Trigger Enable bit<sup>(2)</sup><br/>1 = Scanner trigger is disabled<br/>0 = Scanner trigger is disabled<br/>Refer Table 14-1.</li> <li>bit 5 SGO: Scanner GO bit<sup>(3, 4)</sup><br/>1 = When the CRC is ready, the Memory region set by the MREG bit will be accessed and data is<br/>to the CRC peripheral.<br/>0 = Scanner operations will not occur</li> <li>bit 4.3 Unimplemented: Read as '0'<br/>bit 2 MREG: Scanner Memory Region Select bit<sup>(2)</sup><br/>1 = Scanner address points to Data EEPROM<br/>0 = Scanner address points to Drogram Flash Memory</li> <li>bit 1 BURSTMD: Scanner Burst Mode bit<br/>1 = Memory access request to the CPU Arbiter is always true<br/>0 = Memory access request to the CPU Arbiter is dependent on the CRC request and Trigger<br/>Refer Table 14-1.</li> <li>bit 0 BUSY: Scanner Busy Indicator bit<br/>1 = Scanner cycle is in process<br/>0 = Scanner cycle is in process<br/>0 = Scanner cycle is compete (or never started)</li> <li>Note 1: Setting EN = 1 (SCANCON0 register) does not affect any other register content.</li> <li>2: Scanner trigger selection can be set using the SCANTRIG register.</li> <li>3: This bit can be cleared in software. It is cleared in hardware when LADR&gt;HADR (and a data cycle is</li> </ul>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | Legend:        |                                                               |                                                              |                                           |                                              |                        |                   |               |

| '1' = Bit is set       '0' = Bit is cleared       HC = Bit is cleared by hardware         bit 7       EN: Scanner Enable bit <sup>(1)</sup> 1 = Scanner is disabled         0 = Scanner is disabled       0 = Scanner Trigger Enable bit <sup>(2)</sup> 1 = Scanner trigger is disabled       0 = Scanner trigger is disabled         0 = Scanner trigger is disabled       Refer Table 14-1.         bit 5       SGO: Scanner GO bit <sup>(3, 4)</sup> 1 = When the CRC is ready, the Memory region set by the MREG bit will be accessed and data is to the CRC peripheral.         0 = Scanner operations will not occur         bit 4-3       Unimplemented: Read as '0'         bit 2       MREG: Scanner Memory Region Select bit <sup>(2)</sup> 1 = Scanner address points to Data EEPROM         0 = Scanner address points to Program Flash Memory         bit 1       BURSTMD: Scanner Burst Mode bit         1 = Memory access request to the CPU Arbiter is always true         0 = Memory access request to the CPU Arbiter is dependent on the CRC request and Trigger         Refer Table 14-1.         bit 0       BUSY: Scanner Busy Indicator bit         1 = Scanner cycle is in process       0 = Scanner cycle is no process         0 = Scanner cycle is compete (or never started)       Note         11:       Setting EN = 1 (SCANCON0 register) does not affect any other register content.         <                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | R = Reada      | ble bit                                                       | W = Writable bi                                              | t                                         | U = Unimple                                  | mented bit, rea        | d as '0'          |               |

| <ul> <li>bit 7 EN: Scanner Enable bit<sup>(1)</sup> <ol> <li>= Scanner is enabled</li> <li>= Scanner is disabled</li> </ol> </li> <li>bit 6 TRIGEN: Scanner Trigger Enable bit<sup>(2)</sup> <ol> <li>= Scanner trigger is enabled</li> <li>= Scanner trigger is disabled</li> <li>Refer Table 14-1.</li> </ol> </li> <li>bit 5 SGO: Scanner GO bit<sup>(3, 4)</sup> <ol> <li>= When the CRC is ready, the Memory region set by the MREG bit will be accessed and data is to the CRC peripheral.</li> <li>= Scanner operations will not occur</li> </ol> </li> <li>bit 4-3 Unimplemented: Read as '0'</li> <li>bit 2 MREG: Scanner Memory Region Select bit<sup>(2)</sup> <ol> <li>= Scanner address points to Data EEPROM</li> <li>= Scanner address points to Program Flash Memory</li> <li>bit 1 BURSTMD: Scanner Burst Mode bit</li> <li>= Memory access request to the CPU Arbiter is always true</li> <li>= Memory access request to the CPU Arbiter is dependent on the CRC request and Trigger Refer Table 14-1.</li> </ol> </li> <li>bit 0 BUSY: Scanner Busy Indicator bit</li> <li>= Scanner cycle is in process <ol> <li>= Scanner cycle is compete (or never started)</li> </ol> </li> <li>Note 1: Setting EN = 1 (SCANCON0 register) does not affect any other register content.</li> <li>2: Scanner trigger selection can be set using the SCANTRIG register.</li> <li>3: This bit can be cleared in software. It is cleared in hardware when LADR&gt;HADR (and a data cycle is compete for the set of the compete of the compete of the compete of the compete of the competer of the</li></ul> | u = Bit is u   | nchanged                                                      | x = Bit is unkno                                             | wn                                        | -n/n = Value                                 | at POR and BC          | R/Value at all ot | her Resets    |

| <ul> <li>1 = Scanner is enabled</li> <li>0 = Scanner is disabled</li> <li>bit 6</li> <li>TRIGEN: Scanner Trigger Enable bit<sup>(2)</sup></li> <li>1 = Scanner trigger is enabled</li> <li>0 = Scanner trigger is disabled</li> <li>Refer Table 14-1.</li> <li>bit 5</li> <li>SGO: Scanner GO bit<sup>(3, 4)</sup></li> <li>1 = When the CRC is ready, the Memory region set by the MREG bit will be accessed and data is to the CRC peripheral.</li> <li>0 = Scanner operations will not occur</li> <li>bit 4-3</li> <li>Unimplemented: Read as '0'</li> <li>bit 2</li> <li>MREG: Scanner Memory Region Select bit<sup>(2)</sup></li> <li>1 = Scanner address points to Data EEPROM</li> <li>0 = Scanner address points to Program Flash Memory</li> <li>bit 1</li> <li>BURSTMD: Scanner Burst Mode bit</li> <li>1 = Memory access request to the CPU Arbiter is always true</li> <li>0 = Memory access request to the CPU Arbiter is dependent on the CRC request and Trigger Refer Table 14-1.</li> <li>bit 0</li> <li>BUSY: Scanner Busy Indicator bit</li> <li>1 = Scanner cycle is in process</li> <li>0 = Scanner cycle is compete (or never started)</li> <li>Note 1: Setting EN = 1 (SCANCON0 register) does not affect any other register content.</li> <li>2: Scanner trigger selection can be set using the SCANTRIG register.</li> <li>3: This bit can be cleared in software. It is cleared in hardware when LADR&gt;HADR (and a data cycle is</li> </ul>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | '1' = Bit is s | set                                                           | '0' = Bit is clear                                           | ed                                        | HC = Bit is c                                | leared by hardv        | vare              |               |

| <ul> <li>1 = Scanner trigger is enabled</li> <li>0 = Scanner trigger is disabled</li> <li>Refer Table 14-1.</li> <li>bit 5</li> <li>SGO: Scanner GO bit<sup>(3, 4)</sup></li> <li>1 = When the CRC is ready, the Memory region set by the MREG bit will be accessed and data is to the CRC peripheral.</li> <li>0 = Scanner operations will not occur</li> <li>bit 4-3</li> <li>Unimplemented: Read as '0'</li> <li>bit 2</li> <li>MREG: Scanner Memory Region Select bit<sup>(2)</sup></li> <li>1 = Scanner address points to Data EEPROM</li> <li>0 = Scanner address points to Program Flash Memory</li> <li>bit 1</li> <li>BURSTMD: Scanner Burst Mode bit</li> <li>1 = Memory access request to the CPU Arbiter is always true</li> <li>0 = Memory access request to the CPU Arbiter is dependent on the CRC request and Trigger Refer Table 14-1.</li> <li>bit 0</li> <li>BUSY: Scanner Busy Indicator bit</li> <li>1 = Scanner cycle is in process</li> <li>0 = Scanner cycle is compete (or never started)</li> </ul> Note 1: Setting EN = 1 (SCANCON0 register) does not affect any other register content. 2: Scanner trigger selection can be set using the SCANTRIG register. 3: This bit can be cleared in software. It is cleared in hardware when LADR>HADR (and a data cycle is                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | bit 7          | 1 = Scanner                                                   | is enabled                                                   |                                           |                                              |                        |                   |               |

| <ul> <li>1 = When the CRC is ready, the Memory region set by the MREG bit will be accessed and data is to the CRC peripheral.</li> <li>0 = Scanner operations will not occur</li> <li>bit 4-3 Unimplemented: Read as '0'</li> <li>bit 2 MREG: Scanner Memory Region Select bit<sup>(2)</sup></li> <li>1 = Scanner address points to Data EEPROM</li> <li>0 = Scanner address points to Program Flash Memory</li> <li>bit 1 BURSTMD: Scanner Burst Mode bit</li> <li>1 = Memory access request to the CPU Arbiter is always true</li> <li>0 = Memory access request to the CPU Arbiter is dependent on the CRC request and Trigger Refer Table 14-1.</li> <li>bit 0 BUSY: Scanner Busy Indicator bit</li> <li>1 = Scanner cycle is in process</li> <li>0 = Scanner cycle is compete (or never started)</li> <li>Note 1: Setting EN = 1 (SCANCON0 register) does not affect any other register content.</li> <li>2: Scanner trigger selection can be set using the SCANTRIG register.</li> <li>3: This bit can be cleared in software. It is cleared in hardware when LADR&gt;HADR (and a data cycle is is</li> </ul>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | bit 6          | 1 = Scanner<br>0 = Scanner                                    | trigger is enabled<br>trigger is disabled                    |                                           |                                              |                        |                   |               |

| <ul> <li>bit 2 MREG: Scanner Memory Region Select bit<sup>(2)</sup> <ol> <li>= Scanner address points to Data EEPROM</li> <li>= Scanner address points to Program Flash Memory</li> </ol> </li> <li>bit 1 BURSTMD: Scanner Burst Mode bit <ol> <li>= Memory access request to the CPU Arbiter is always true</li> <li>= Memory access request to the CPU Arbiter is dependent on the CRC request and Trigger Refer Table 14-1.</li> </ol> </li> <li>bit 0 BUSY: Scanner Busy Indicator bit <ol> <li>= Scanner cycle is in process</li> <li>= Scanner cycle is compete (or never started)</li> </ol> </li> <li>Note 1: Setting EN = 1 (SCANCON0 register) does not affect any other register content.</li> <li>Scanner trigger selection can be set using the SCANTRIG register.</li> <li>This bit can be cleared in software. It is cleared in hardware when LADR&gt;HADR (and a data cycle is in process in the started in the started</li></ul>                            | bit 5          | 1 = When the to the C                                         | e CRC is ready, the<br>RC peripheral.                        |                                           | egion set by the                             | MREG bit will be       | e accessed and o  | lata is passe |

| <ul> <li>1 = Scanner address points to Data EEPROM         <ul> <li>9 = Scanner address points to Program Flash Memory</li> </ul> </li> <li>bit 1 BURSTMD: Scanner Burst Mode bit         <ul> <li>1 = Memory access request to the CPU Arbiter is always true</li> <li>0 = Memory access request to the CPU Arbiter is dependent on the CRC request and Trigger Refer Table 14-1.</li> </ul> </li> <li>bit 0 BUSY: Scanner Busy Indicator bit         <ul> <li>1 = Scanner cycle is in process</li> <li>0 = Scanner cycle is compete (or never started)</li> </ul> </li> <li>Note 1: Setting EN = 1 (SCANCON0 register) does not affect any other register content.</li> <li>2: Scanner trigger selection can be set using the SCANTRIG register.</li> <li>3: This bit can be cleared in software. It is cleared in hardware when LADR&gt;HADR (and a data cycle is in process)</li> </ul>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | bit 4-3        | Unimpleme                                                     | nted: Read as '0'                                            |                                           |                                              |                        |                   |               |

| <ul> <li>1 = Memory access request to the CPU Arbiter is always true         <ul> <li>a Memory access request to the CPU Arbiter is dependent on the CRC request and Trigger Refer Table 14-1.</li> </ul> </li> <li>bit 0 BUSY: Scanner Busy Indicator bit         <ul> <li>1 = Scanner cycle is in process</li> <li>0 = Scanner cycle is compete (or never started)</li> </ul> </li> <li>Note 1: Setting EN = 1 (SCANCON0 register) does not affect any other register content.</li> <li>2: Scanner trigger selection can be set using the SCANTRIG register.</li> <li>3: This bit can be cleared in software. It is cleared in hardware when LADR&gt;HADR (and a data cycle is in process)</li> </ul>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | bit 2          | 1 = Scanner                                                   | address points to                                            | Data EEPP                                 | ROM                                          |                        |                   |               |

| <ol> <li>1 = Scanner cycle is in process         <ul> <li>0 = Scanner cycle is compete (or never started)</li> </ul> </li> <li>Note 1: Setting EN = 1 (SCANCON0 register) does not affect any other register content.         <ul> <li>2: Scanner trigger selection can be set using the SCANTRIG register.</li> <li>3: This bit can be cleared in software. It is cleared in hardware when LADR&gt;HADR (and a data cycle is</li> </ul> </li> </ol>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | bit 1          | 1 = Memory<br>0 = Memory                                      | access request to access request to                          | the CPU A                                 |                                              |                        | request and Tri   | gger          |

| <ol> <li>Scanner trigger selection can be set using the SCANTRIG register.</li> <li>This bit can be cleared in software. It is cleared in hardware when LADR&gt;HADR (and a data cycle is</li> </ol>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | bit 0          | 1 = Scanner                                                   | cycle is in proces                                           | S                                         | tarted)                                      |                        |                   |               |

| occurring) or when CRCGO = 0 (CRCCON0 register).                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 2:<br>3:       | Scanner trigger s<br>This bit can be cle<br>occurring) or whe | election can be se<br>eared in software.<br>en CRCGO = 0 (Cl | t using the<br>It is cleared<br>RCCON0 re | SCANTRIG reg<br>d in hardware w<br>egister). | ister.<br>hen LADR>HAI | DR (and a data c  | ycle is not   |

# REGISTER 14-11: SCANCONO: SCANNER ACCESS CONTROL REGISTER 0

- - 4: CRCEN and CRCGO bits (CRCCON0 register) must be set before setting the SGO bit.

|           |                   |            |       |                                |           |         |        | Register |     |

|-----------|-------------------|------------|-------|--------------------------------|-----------|---------|--------|----------|-----|

| Name      | Bit 7             | Bit 6      | Bit 5 | Bit 5Bit 4Bit 3Bit 2Bit 1Bit 0 |           |         |        |          |     |

| DMAxCON0  | EN                | SIRQEN     | DGO   | —                              | —         | AIRQEN  | _      | XIP      | 248 |

| DMAxCON1  | DMOD              | E<1:0>     | DSTP  | SMR                            | <1:0>     | SMOD    | E<1:0> | SSTP     | 249 |

| DMAxBUF   | DBUF7             | DBUF6      | DBUF5 | DBUF4                          | DBUF3     | DBUF2   | DBUF1  | DBUF0    | 250 |

| DMAxSSAL  | SSA<7:0>          |            |       |                                |           |         |        |          |     |

| DMAxSSAH  |                   |            |       | SSA<                           | :15:8>    |         |        |          | 250 |

| DMAxSSAU  | —                 | _          |       |                                | SSA<      | 21:16>  |        |          | 251 |

| DMAxSPTRL |                   |            |       | SPTR                           | <7:0>     |         |        |          | 251 |

| DMAxSPTRH |                   |            |       | SPTR                           | <15:8>    |         |        |          | 251 |

| DMAxSPTRU | —                 | _          |       |                                | SPTR<     | :21:16> |        |          | 252 |

| DMAxSSZL  |                   | SSZ<7:0>   |       |                                |           |         |        | 252      |     |

| DMAxSSZH  | _                 | SSZ<11:8>  |       |                                |           |         |        | 252      |     |

| DMAxSCNTL |                   | SCNT<7:0>  |       |                                |           |         |        |          | 253 |

| DMAxSCNTH | _                 | _          |       | _                              |           | SCNT    | <11:8> |          | 253 |

| DMAxDSAL  |                   | DSA<7:0>   |       |                                |           |         |        |          | 253 |

| DMAxDSAH  |                   | DSA<15:8>  |       |                                |           |         |        |          | 254 |

| DMAxDPTRL |                   |            |       | DPTR                           | <7:0>     |         |        |          | 254 |

| DMAxDPTRH |                   | DPTR<15:8> |       |                                |           |         |        |          | 254 |

| DMAxDSZL  |                   | DSZ<7:0>   |       |                                |           |         |        | 255      |     |

| DMAxDSZH  | — — — — DSZ<11:8> |            |       |                                |           |         | 255    |          |     |

| DMAxDCNTL | DCNT<7:0>         |            |       |                                |           |         | 255    |          |     |

| DMAxDCNTH | — — — DCNT<11:8>  |            |       |                                |           |         | 256    |          |     |

| DMAxSIRQ  |                   |            |       |                                |           |         | 256    |          |     |

| DMAxAIRQ  |                   |            |       |                                | AIRQ<6:0> |         |        |          | 256 |

# TABLE 15-3: SUMMARY OF REGISTERS ASSOCIATED WITH DMA

Legend: — = unimplemented location, read as '0'. Shaded cells are not used by DMA.

# REGISTER 17-3: PPSLOCK: PPS LOCK REGISTER

| U-0     | U-0 | U-0 | U-0 | U-0 | U-0 | U-0 | R/W-0/0   |

|---------|-----|-----|-----|-----|-----|-----|-----------|

| —       | —   | —   | —   | —   | —   | —   | PPSLOCKED |

| bit 7   | •   |     |     |     | •   |     | bit 0     |

|         |     |     |     |     |     |     |           |

| Legend: |     |     |     |     |     |     |           |

| v                    |                      |                                                       |

|----------------------|----------------------|-------------------------------------------------------|

| R = Readable bit     | W = Writable bit     | U = Unimplemented bit, read as '0'                    |

| u = Bit is unchanged | x = Bit is unknown   | -n/n = Value at POR and BOR/Value at all other Resets |

| '1' = Bit is set     | '0' = Bit is cleared |                                                       |

#### bit 7-1 Unimplemented: Read as '0'

bit 0 **PPSLOCKED:** PPS Locked bit

1 = PPS is locked.

0 = PPS is not locked. PPS selections can be changed.

# 21.3 Timer1/3/5 Prescaler

Timer1/3/5 has four prescaler options allowing 1, 2, 4 or 8 divisions of the clock input. The CKPS bits of the TxCON register control the prescale counter. The prescale counter is not directly readable or writable; however, the prescaler counter is cleared upon a write to TMRxH or TMRxL.

# 21.4 Timer1/3/5 Operation in Asynchronous Counter Mode

If control bit SYNC of the TxCON register is set, the external clock input is not synchronized. The timer increments asynchronously to the internal phase clocks. If external clock source is selected then the timer will continue to run during Sleep and can generate an interrupt on overflow, which will wake up the processor. However, special precautions in software are needed to read/write the timer (see Section 21.4.1 "Reading and Writing Timer1/3/5 in Asynchronous Counter Mode").

Note: When switching from synchronous to asynchronous operation, it is possible to skip an increment. When switching from asynchronous to synchronous operation, it is possible to produce an additional increment.

### 21.4.1 READING AND WRITING TIMER1/3/ 5 IN ASYNCHRONOUS COUNTER MODE

Reading TMRxH or TMRxL while the timer is running from an external asynchronous clock will ensure a valid read (taken care of in hardware). However, the user should keep in mind that reading the 16-bit timer in two 8-bit values itself, poses certain problems, since the timer may overflow between the reads. For writes, it is recommended that the user simply stop the timer and write the desired values. A write contention may occur by writing to the timer registers, while the register is incrementing. This may produce an unpredictable value in the TMRxH:TMRxL register pair.

# 21.5 Timer1/3/5 16-Bit Read/Write Mode

Timer1/3/5 can be configured to read and write all 16 bits of data, to and from, the 8-bit TMRxL and TMRxH registers, simultaneously. The 16-bit read and write operations are enabled by setting the RD16 bit of the TxCON register.

To accomplish this function, the TMRxH register value is mapped to a buffer register called the TMRxH buffer register. While in 16-Bit mode, the TMRxH register is not directly readable or writable and all read and write operations take place through the use of this TMRxH buffer register.

When a read from the TMRxL register is requested, the value of the TMRxH register is simultaneously loaded into the TMRxH buffer register. When a read from the TMRxH register is requested, the value is provided from the TMRxH buffer register instead. This provides the user with the ability to accurately read all 16 bits of the Timer1/3/5 value from a single instance in time. Reference the block diagram in Figure 21-2 for more details.

In contrast, when not in 16-Bit mode, the user must read each register separately and determine if the values have become invalid due to a rollover that may have occurred between the read operations.

When a write request of the TMRxL register is requested, the TMRxH buffer register is simultaneously updated with the contents of the TMRxH register. The value of TMRxH must be preloaded into the TMRxH buffer register prior to the write request for the TMRxL register. This provides the user with the ability to write all 16 bits to the TMRxL:TMRxH register pair at the same time.

Any requests to write to the TMRxH directly does not clear the Timer1/3/5 prescaler value. The prescaler value is only cleared through write requests to the TMRxL register.

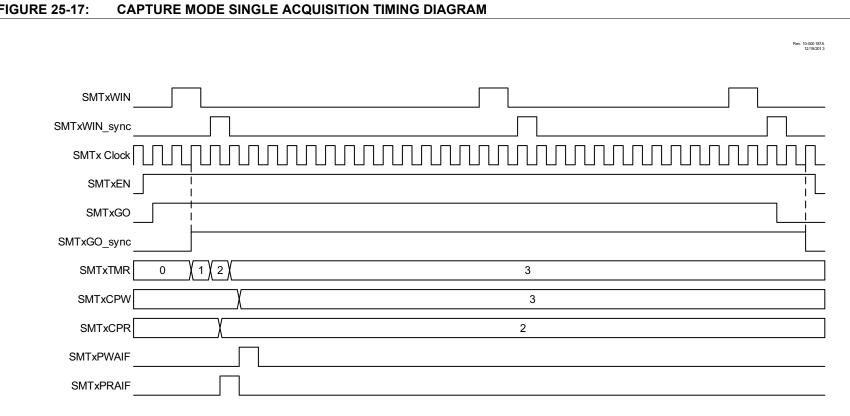

# FIGURE 25-17:

PIC18(L)F26/27/45/46/47/55/56/57K42

# 31.13 Checksum (UART1 only)

This section does not apply to the LIN mode, which handles checksums automatically.

The transmit and receive checksum adders are enabled when the C0EN bit in the UxCON2 register is set. When enabled, the adders accumulate every byte that is transmitted or received. The accumulated sum includes the carry of the addition. Software is responsible for clearing the checksum registers before a transaction and performing the check at the end of the transaction.

The following is an example of how the checksum registers could be used in the asynchronous modes.

### 31.13.1 TRANSMIT CHECKSUM METHOD

- 1. Clear the UxTXCHK register.

- 2. Set the COEN bit.

- 3. Send all bytes of the transaction output.

- 4. Invert UxTXCHK and send the result as the last byte of the transaction.

### 31.13.2 RECEIVE CHECKSUM METHOD

- 1. Clear the UxRXCHK register.

- 2. Set the COEN bit.

- 3. Receive all bytes in the transaction including the checksum byte.

- 4. Set MSb of UxRXCHK if 7-bit mode is selected.

- 5. Add 1 to UxRXCHK.

- 6. If the result is '0', the checksum passes, otherwise it fails.

The CERIF checksum interrupt flag is not active in any mode other than LIN.

# 31.14 Collision Detection

External forces that interfere with the transmit line are detected in all modes of operation with collision detection. Collision detection is always active when RXEN and TXEN are both set.

When the receive input is connected to the transmit output through either the same I/O pin or external circuitry, a character will be received for every character transmitted. The collision detection circuit provides a warning when the word received does not match the word transmitted. The TXCIF flag in the UxERRIR register is used to signal collisions. This signal is only useful when the TX output is looped back to the RX input and everything that is transmitted is expected to be received. If more than one transmitter is active at the same time, it can be assumed that the TX word will not match the RX word. The TXCIF detects this mismatch and flags an interrupt. The TXCIF bit will also be set in DALI mode transmissions when the received bit is missing the expected mid-bit transition.

Collision detection is always active, regardless of whether or not the RX input is connected to the TX output. It is up to the user to disable the TXCIE bit when collision interrupts are not required.

The software overhead of unloading the receive buffer of transmitted data is avoided by setting the RUNOVF bit in UxCON2 and ignoring the receive interrupt and letting the receive buffer overflow. When the transmission is complete, prepare for receiving data by flushing the receive buffer (see Section 31.11.2, FIFO Reset) and clearing the RXFOIF overflow flag in the UxERRIR register.

# 31.15 RX/TX Activity Timeout

The UART works in conjunction with the HLT timers to monitor activity on the RX and TX lines. Use this feature to determine when there has been no activity on the receive or transmit lines for a user specified period of time.

To use this feature, set the HLT to the desired timeout period by a combination of the HLT clock source, timer prescale value, and timer period registers. Configure the HLT to reset on the UART TX or RX line and start the HLT at the same time the UART is started. UART activity will keep resetting the HLT to prevent a full HLT period from elapsing. When there has been no activity on the selected TX or RX line for longer than the HLT period then an HLT interrupt will occur signaling the timeout event.

For example, the following register settings will configure HLT2 for a 5 ms timeout of no activity on U1RX:

- T2PR = 0x9C (156 prescale periods)

- T2CLKCON = 0x05 (500 kHz internal oscillator)

- T2HLT = 0x04 (free running, reset on rising edge)

- T2RST = 0x15 (reset on U1RX)

- T2CON = 0xC0 (Timer2 on with 1:16 prescale)

# 31.16 Clock Accuracy with Asynchronous Operation

The factory calibrates the internal oscillator block output (INTOSC). However, the INTOSC frequency may drift as VDD or temperature changes, and this directly affects the asynchronous baud rate. Two methods may be used to adjust the baud rate clock, but both require a reference clock source of some kind.

The first (preferred) method uses the OSCTUNE register to adjust the INTOSC output. Adjusting the value of the OSCTUNE register allows for fine resolution changes to the system clock source. See **Section 7.2.2.3 "Internal Oscillator Frequency Adjustment"** for more information.

The other method adjusts the value of the Baud Rate Generator. This can be done automatically with the Auto-Baud Detect feature (see Section **31.17.1 "Auto-Baud Detect"**). There may not be fine enough resolution when adjusting the Baud Rate Generator to compensate for a gradual change of the peripheral clock frequency.

# 31.17 UART Baud Rate Generator (BRG)

The Baud Rate Generator (BRG) is a 16-bit timer that is dedicated to the support of the UART operation.

The UxBRGH, UxBRGL register pair determines the period of the free running baud rate timer. The multiplier of the baud rate period is determined by the BRGS bit in the UxCON0 register.

Table 31-1 contains the formulas for determining the baud rate. Example 31-1 provides a sample calculation for determining the baud rate and baud rate error.

The high baud rate range (BRGS = 1) is intended to extend the baud rate range up to a faster rate when the desired baud rate is not possible otherwise. Using the normal baud rate range (BRGS = 0) is recommended when the desired baud rate is achievable with either range.

Writing a new value to the UxBRGH, UxBRGL register pair causes the BRG timer to be reset (or cleared). This ensures that the BRG does not wait for a timer overflow before outputting the new baud rate.

If the system clock is changed during an active receive operation, a receive error or data loss may result. To avoid this problem, check the status of the RXIDL bit to make sure that the receive operation is idle before changing the system clock.

### EXAMPLE 31-1: CALCULATING BAUD RATE ERROR

### TABLE 31-1: BAUD RATE FORMULAS

| BRGS | BRG/UART Mode | Baud Rate Formula |

|------|---------------|-------------------|

| 1    | High Rate     | Fosc/[4 (n+1)]    |

| 0    | Normal Rate   | Fosc/[16(n+1)]    |

**Legend:** n = value of UxBRGH, UxBRGL register pair.

#### **REGISTER 32-12:** SPIxTxB: SPI TRANSMIT BUFFER REGISTER

| W-0   | W-0  | W-0  | W-0  | W-0  | W-0  | W-0  | W-0   |

|-------|------|------|------|------|------|------|-------|

| TXB7  | TXB6 | TXB5 | TXB4 | TXB3 | TXB2 | TXB1 | TXB0  |

| bit 7 |      |      |      |      |      |      | bit 0 |

| Legend:          |                  |                                    |

|------------------|------------------|------------------------------------|

| R = Readable bit | W = Writable bit | U = Unimplemented bit, read as '0' |

bit 7-0 **TXB<7:0>**: Transmit Buffer bits (write only)

If TXFIFO is not full:

Writing to this register adds the data to the top of the TXFIFO and increases the occupancy of the TXFIFO write pointer

If TXFIFO is full:

Writing to this register does not affect the data in the TXFIFO or the write pointer, and the TXWE bit of SPIxSTATUS will be set

### REGISTER 32-13: SPIxCLK: SPI CLOCK SELECTION REGISTER

| U-0   | U-0 | U-0 | U-0 | R/W-0/0 | R/W-0/0 | R/W-0/0 | R/W-0/0 |

|-------|-----|-----|-----|---------|---------|---------|---------|

| _     | —   | —   | -   | CLKSEL3 | CLKSEL2 | CLKSEL1 | CLKSEL0 |

| bit 7 |     |     |     |         |         |         | bit 0   |

| Legend:          |                  |                                    |

|------------------|------------------|------------------------------------|

| R = Readable bit | W = Writable bit | U = Unimplemented bit, read as '0' |

bit 7-4 Unimplemented: Read as '0'

bit 3-0 CLKSEL<3:0>: SPI Clock Source Selection bits

1111-1001 = Reserved

- 1000 = SMT\_match

- 0111 = TMR6\_Postscaled

- 0110 = TMR4\_Postscaled

- 0101 = TMR2\_Postscaled

- 0100 = TMR0\_overflow

- 0011 = CLKREF

- 0010 = MFINTOSC

- 0001 = HFINTOSC

- 0000 **= FOSC**

| TABLE 36           | 6-2: | <b>COMPUTATION MO</b>                        | DES                                                                          |                                                         |                                                                                                                                                 |                   |                   |              |                        |

|--------------------|------|----------------------------------------------|------------------------------------------------------------------------------|---------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------|-------------------|-------------------|--------------|------------------------|

|                    |      | Bit Clear Conditions                         | Value after Trigg                                                            | er completion                                           | Tł                                                                                                                                              | reshold Opera     | tions             | Value at     | ADTIF interrupt        |

| Mode               | ADMD | ACC and CNT                                  | ACC                                                                          | CNT                                                     | Retrigger                                                                                                                                       | Threshold<br>Test | Interrupt         | ADAOV        | FLTR                   |

| Basic              | 0    | ADACLR = 1                                   | Unchanged                                                                    | Unchanged                                               | No                                                                                                                                              | Every Sam-<br>ple | If threshold=true | N/A          | N/A                    |

| Accumulate         | 1    | ADACLR = 1                                   | S + ACC<br>or<br>(S2-S1) + ACC                                               | If (CNT=0xFF): CNT, oth-<br>erwise: CNT+1               | No                                                                                                                                              | Every Sam-<br>ple | If threshold=true | ACC Overflow | ACC/2 <sup>ADCRS</sup> |

| Average            | 2    | ADACLR = 1 or CNT>=RPT<br>at GO or retrigger | S + ACC<br>or<br>(S2-S1) + ACC                                               | If (CNT=0xFF): CNT, oth-<br>erwise: CNT+1               | No                                                                                                                                              | If<br>CNT>=RPT    | If threshold=true | ACC Overflow | ACC/2 <sup>ADCRS</sup> |

| Burst<br>Average   | 3    | ADACLR = 1 or GO set or<br>retrigger         | Each repetition: same as<br>Average<br>End with sum of all<br>samples        | Each repetition: same as<br>Average<br>End with CNT=RPT | Repeat while<br>CNT <rpt< td=""><td>lf<br/>CNT&gt;=RPT</td><td>If threshold=true</td><td>ACC Overflow</td><td>ACC/2<sup>ADCRS</sup></td></rpt<> | lf<br>CNT>=RPT    | If threshold=true | ACC Overflow | ACC/2 <sup>ADCRS</sup> |

| Low-pass<br>Filter | 4    | ADACLR = 1                                   | S+ACC-ACC/<br>2 <sup>ADCRS</sup><br>or<br>(S2-S1)+ACC-ACC/2 <sup>ADCRS</sup> | Count up, stop counting<br>when CNT = 0xFF              | No                                                                                                                                              | lf<br>CNT>=RPT    | If threshold=true | ACC Overflow | Filtered Value         |

S1 and S2 are abbreviations for Sample 1 and Sample 2, respectively. When ADDSEN = 0, S1 = ADRES; When ADDSEN = 1, S1 = PREV and S2 = ADRES. Note:

CNT count

count

count

RPT

count

HC = Bit is cleared by hardware

| U-0                                     | R/W-0/0 | R/W-0/0   | R/W-0/0                            | R/W/HC-0                                              | R/W-0/0 | R/W-0/0  | R/W-0/0 |

|-----------------------------------------|---------|-----------|------------------------------------|-------------------------------------------------------|---------|----------|---------|

| _                                       |         | CALC<2:0> |                                    | SOI                                                   |         | TMD<2:0> |         |

| bit 7                                   | •       |           |                                    |                                                       |         |          | bit 0   |

|                                         |         |           |                                    |                                                       |         |          |         |

| Legend:                                 |         |           |                                    |                                                       |         |          |         |

| R = Readable bit W = Writable bit       |         | bit       | U = Unimplemented bit, read as '0' |                                                       |         |          |         |

| u = Bit is unchanged x = Bit is unknown |         |           | iown                               | -n/n = Value at POR and BOR/Value at all other Resets |         |          |         |

#### REGISTER 36-4: ADCON3: ADC CONTROL REGISTER 3

#### bit 7 Unimplemented: Read as '0'

1' = Bit is set

bit 6-4 CALC<2:0>: ADC Error Calculation Mode Select bits

'0' = Bit is cleared

| CALC | DSEN = 0 Single-<br>Sample Mode | DSEN = 1 CVD Double-<br>Sample Mode <sup>(1)</sup> | Application                                                  |

|------|---------------------------------|----------------------------------------------------|--------------------------------------------------------------|

| 111  | Reserved                        | Reserved                                           | Reserved                                                     |

| 110  | Reserved                        | Reserved                                           | Reserved                                                     |

| 101  | FLTR-STPT                       | FLTR-STPT                                          | Average/filtered value vs. setpoint                          |

| 100  | PREV-FLTR                       | PREV-FLTR                                          | First derivative of filtered value <sup>(3)</sup> (negative) |

| 011  | Reserved                        | Reserved                                           | Reserved                                                     |

| 010  | RES-FLTR                        | (RES-PREV)-FLTR                                    | Actual result vs. averaged/<br>filtered value                |

| 001  | RES-STPT                        | (RES-PREV)-STPT                                    | Actual result vs.setpoint                                    |

| 000  | RES-PREV                        | RES-PREV                                           | First derivative of single measurement <sup>(2)</sup>        |

|      |                                 |                                                    | Actual CVD result in CVD mode <sup>(2)</sup>                 |

| bit 3 | SOI: ADC Stop-on-Interrupt bit                                                                   |  |  |  |  |  |

|-------|--------------------------------------------------------------------------------------------------|--|--|--|--|--|

|       | If CONT = 1:                                                                                     |  |  |  |  |  |

|       | 1 = GO is cleared when the threshold conditions are met, otherwise the conversion is retriggered |  |  |  |  |  |

|       | 0 = GO is not cleared by hardware, must be cleared by software to stop retriggers                |  |  |  |  |  |

#### bit 2-0 TMD<2:0>: Threshold Interrupt Mode Select bits

- 111 = Interrupt regardless of threshold test results

- 110 = Interrupt if ERR>UTH

- 101 = Interrupt if ERR≤UTH

- 100 = Interrupt if ERR<LTH or ERR>UTH

- 011 = Interrupt if ERR>LTH and ERR<UTH

- 010 = Interrupt if ERR≥LTH

- 001 = Interrupt if ERR<LTH

- 000 = Never interrupt

- Note 1: When PSIS = 0, the value of (RES-PREV) is the value of (S2-S1) from Table 36-2.

- 2: When PSIS = 0

- **3:** When PSIS = 1.

## REGISTER 36-27: ADSTPTH: ADC THRESHOLD SETPOINT REGISTER HIGH

| R/W-0/0         | R/W-0/0    | R/W-0/0         | R/W-0/0 | R/W-0/0        | R/W-0/0          | R/W-0/0          | R/W-0/0      |  |  |

|-----------------|------------|-----------------|---------|----------------|------------------|------------------|--------------|--|--|

|                 | STPT<15:8> |                 |         |                |                  |                  |              |  |  |

| bit 7           |            |                 |         |                |                  |                  | bit 0        |  |  |

|                 |            |                 |         |                |                  |                  |              |  |  |

| Legend:         |            |                 |         |                |                  |                  |              |  |  |

| R = Readable    | bit        | W = Writable I  | oit     | U = Unimplen   | nented bit, read | d as '0'         |              |  |  |

| u = Bit is unch | anged      | x = Bit is unkn | own     | -n/n = Value a | at POR and BO    | R/Value at all o | other Resets |  |  |

bit 7-0 **STPT<15:8>**: ADC Threshold Setpoint MSB. Upper byte of ADC threshold setpoint, depending on ADCALC, may be used to determine ERR, see Register 36-29 for more details.

## REGISTER 36-28: ADSTPTL: ADC THRESHOLD SETPOINT REGISTER LOW

'0' = Bit is cleared

| R/W-0/0 |

|---------|---------|---------|---------|---------|---------|---------|---------|

|         |         |         | STPT    | <7:0>   |         |         |         |

| bit 7   |         |         |         |         |         |         | bit 0   |

|         |         |         |         |         |         |         |         |

| Legend:              |                      |                                                       |

|----------------------|----------------------|-------------------------------------------------------|

| R = Readable bit     | W = Writable bit     | U = Unimplemented bit, read as '0'                    |

| u = Bit is unchanged | x = Bit is unknown   | -n/n = Value at POR and BOR/Value at all other Resets |

| '1' = Bit is set     | '0' = Bit is cleared |                                                       |

bit 7-0 **STPT<7:0>**: ADC Threshold Setpoint LSB. Lower byte of ADC threshold setpoint, depending on ADCALC, may be used to determine ERR, see Register 36-30 for more details.

'1' = Bit is set

# 38.2 Comparator Control

Each comparator has two control registers: CMxCON0 and CMxCON1.

The CMxCON0 register (see Register 38-1) contains Control and Status bits for the following:

- Enable

- Output

- Output polarity

- Hysteresis enable

- Timer1 output synchronization

The CMxCON1 register (see Register 38-2) contains Control bits for the following:

• Interrupt on positive/negative edge enables

The CMxPCH and CMxNCH registers are used to select the positive and negative input channels, respectively.

# 38.2.1 COMPARATOR ENABLE

Setting the EN bit of the CMxCON0 register enables the comparator for operation. Clearing the EN bit disables the comparator resulting in minimum current consumption.

# 38.2.2 COMPARATOR OUTPUT

The output of the comparator can be monitored by reading either the CxOUT bit of the CMxCON0 register or the CxOUT bit of the CMOUT register.

The comparator output can also be routed to an external pin through the RxyPPS register (Register 17-2). The corresponding TRIS bit must be clear to enable the pin as an output.

Note 1: The internal output of the comparator is latched with each instruction cycle. Unless otherwise specified, external outputs are not latched.

# 38.2.3 COMPARATOR OUTPUT POLARITY

Inverting the output of the comparator is functionally equivalent to swapping the comparator inputs. The polarity of the comparator output can be inverted by setting the POL bit of the CMxCON0 register. Clearing the POL bit results in a noninverted output.

Table 38-1shows the output state versus inputconditions, including polarity control.

#### TABLE 38-1: COMPARATOR OUTPUT STATE VS. INPUT CONDITIONS

| Input Condition | POL | CxOUT |

|-----------------|-----|-------|

| CxVN > CxVP     | 0   | 0     |

| CxVN < CxVP     | 0   | 1     |

| CxVN > CxVP     | 1   | 1     |

| CxVN < CxVP     | 1   | 0     |