Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

E·XFI

| 2 0 0 0 0 0                |                                                                             |

|----------------------------|-----------------------------------------------------------------------------|

| Product Status             | Active                                                                      |

| Core Processor             | PIC                                                                         |

| Core Size                  | 8-Bit                                                                       |

| Speed                      | 64MHz                                                                       |

| Connectivity               | I <sup>2</sup> C, LINbus, SPI, UART/USART                                   |

| Peripherals                | Brown-out Detect/Reset, DMA, HLVD, POR, PWM, WDT                            |

| Number of I/O              | 36                                                                          |

| Program Memory Size        | 128KB (64K x 16)                                                            |

| Program Memory Type        | FLASH                                                                       |

| EEPROM Size                | 1K x 8                                                                      |

| RAM Size                   | 8K x 8                                                                      |

| Voltage - Supply (Vcc/Vdd) | 1.8V ~ 3.6V                                                                 |

| Data Converters            | A/D 35x12b; D/A 1x5b                                                        |

| Oscillator Type            | Internal                                                                    |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                           |

| Mounting Type              | Surface Mount                                                               |

| Package / Case             | 40-UFQFN Exposed Pad                                                        |

| Supplier Device Package    | 40-UQFN (5x5)                                                               |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/pic18lf47k42-i-mv |

|                            |                                                                             |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

#### 3.1 System Arbitration

The System Arbiter resolves memory access between the System Level Selections (i.e., Main, Interrupt Service Routine) and Peripheral Selection (i.e., DMA and Scanner) based on user-assigned priorities. Each of the system level and peripheral selections has its own priority selection registers. Memory access priority is resolved using the number written to the corresponding Priority registers, 0 being the highest priority and 4 the lowest. The default priorities are listed in Table 3-1.

In case the user wants to change priorities, ensure each Priority register is written with a unique value from 0 to 4.

| Sele         | Priority register<br>Reset value |   |

|--------------|----------------------------------|---|

| System Level | ISR                              | 0 |

|              | MAIN                             | 1 |

| Peripheral   | DMA1                             | 2 |

|              | DMA2                             | 3 |

|              | SCANNER                          | 4 |

TABLE 3-1: DEFAULT PRIORITIES

|                      | PC<21:0>                                                                                               | PC<21:0>                                                                                                                                                         | PC<21:0>                                       | 7                   |

|----------------------|--------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------|---------------------|

|                      | <b>†</b> 1                                                                                             | <b>\$</b>                                                                                                                                                        | ¢ I                                            | _                   |

| Note 1               | Stack (31 levels)                                                                                      | Stack (31 levels)                                                                                                                                                | Stack (31 levels)                              | Note 1              |

|                      | •                                                                                                      |                                                                                                                                                                  | ★                                              | _                   |

| 00 0000h             | Reset Vector                                                                                           | Reset Vector                                                                                                                                                     | Reset Vector                                   | 00 0000h            |

| •••                  | •••                                                                                                    | •••                                                                                                                                                              | •••                                            | •••                 |

| 00 0008h             | Interrupt Vector High <sup>(2)</sup>                                                                   | Interrupt Vector High <sup>(2)</sup>                                                                                                                             | Interrupt Vector High <sup>(2)</sup>           | 00 0008h            |

| •••                  | •••                                                                                                    | • • •                                                                                                                                                            | • • •                                          | •••                 |

| 00 0018h             | Interrupt Vector Low <sup>(2)</sup>                                                                    | Interrupt Vector Low <sup>(2)</sup>                                                                                                                              | Interrupt Vector Low <sup>(2)</sup>            | 00 0018h            |

| 00 001Ah<br>•        | Program Flash Memory (16<br>KW) <sup>(3)</sup>                                                         |                                                                                                                                                                  |                                                | 00 001Ah<br>•       |

| 00 7FFFh             | (WV) <sup></sup>                                                                                       | Program Flash Memory (32<br>KW) <sup>(3)</sup>                                                                                                                   |                                                | 00 7FFF             |

| 00 8000h             |                                                                                                        | KVV). /                                                                                                                                                          | Program Flash Memory (64<br>KW) <sup>(3)</sup> | 00 8000h<br>•       |

| 00 FFFFh             |                                                                                                        |                                                                                                                                                                  |                                                | 00 FFFF             |

| 01 0000h             | Reserved <sup>(4)</sup>                                                                                |                                                                                                                                                                  |                                                | 01 0000h            |

| 01 FFFFh             |                                                                                                        | Reserved <sup>(4)</sup>                                                                                                                                          |                                                | 01 FFFF             |

| 02 0000h<br>1F FFFFh |                                                                                                        |                                                                                                                                                                  | Reserved <sup>(4)</sup>                        | 02 0000h<br>1F FFFF |

| 20 0000              |                                                                                                        | User IDs (8 Words) <sup>(5)</sup>                                                                                                                                |                                                | 20 0000h            |

| 20 000Fh             |                                                                                                        |                                                                                                                                                                  |                                                | 20 000Fh            |

| 20 0010h             |                                                                                                        | Reserved                                                                                                                                                         |                                                | 20 0010h            |

| 2F FFFFh             |                                                                                                        | Reserved                                                                                                                                                         |                                                | 2F FFFF             |

| 30 0000h             |                                                                                                        | Configuration Words (5 Words) <sup>(5</sup>                                                                                                                      | 5)                                             | 30 0000h            |

| 30 0009h             |                                                                                                        | Conliguration words (5 words)                                                                                                                                    | ,                                              | 30 0009h            |

| 30 000Ah             |                                                                                                        | Deserved                                                                                                                                                         |                                                | 30 000Ah            |

| 30 FFFFh             |                                                                                                        | Reserved                                                                                                                                                         |                                                | 30 FFFF             |

| 31 0000h             |                                                                                                        |                                                                                                                                                                  |                                                | 31 0000h            |

| 31 00FFh             | Data EEPROM (256 Bytes)                                                                                |                                                                                                                                                                  |                                                | •••<br>31 00FFh     |

| 31 0100h             |                                                                                                        | Data EEPRO                                                                                                                                                       | M (1024Bytes)                                  | 31 0100h            |

| •••                  |                                                                                                        |                                                                                                                                                                  |                                                | •••                 |

| 31 03FFh             | Reserved                                                                                               |                                                                                                                                                                  |                                                | 31 03FFh            |

| 31 0400h             |                                                                                                        | Rese                                                                                                                                                             | erved                                          | 31 0400h            |

| 3E FFFFh             |                                                                                                        |                                                                                                                                                                  |                                                | 3E FFFF             |

| 3F 0000h             |                                                                                                        | Device Information Area <sup>(5),(7)</sup>                                                                                                                       |                                                | 3F 0000h            |

| 3F 003Fh             |                                                                                                        |                                                                                                                                                                  |                                                | 3F 003Fh            |

| 3F0040h              |                                                                                                        | Reserved                                                                                                                                                         |                                                | 3F0040h             |

| 3F FEFFh             |                                                                                                        |                                                                                                                                                                  |                                                | 3F FEFFI            |

| 3F FF00h             | Device C                                                                                               | onfiguration Information (5 Word                                                                                                                                 | (5),(6),(7)                                    | 3F FF00h            |

| 3F FF09h             |                                                                                                        | <b>.</b> .                                                                                                                                                       |                                                | 3F FF09h            |

| 3F FF0Ah             |                                                                                                        | Reserved                                                                                                                                                         |                                                | 3F FF0Ah            |

| 3F FFFBh             |                                                                                                        | Reserved                                                                                                                                                         |                                                | 3F FFFB             |

| 3F FFFCh             |                                                                                                        | Revision ID (1 Word) <sup>(5),(6),(7)</sup>                                                                                                                      |                                                | 3F FFFCI            |

| 3F FFFDh             |                                                                                                        | Revision ID (1 word)                                                                                                                                             |                                                | 3F FFFD             |

| 3F FFFEh             |                                                                                                        |                                                                                                                                                                  |                                                | 3F FFFEI            |

| 3F FFFFh             |                                                                                                        | Device ID (1 Word) <sup>(5),(6),(7)</sup>                                                                                                                        |                                                | 3F FFFF             |

| Note 1:<br>2:<br>3:  | 00 0008h location is used as the<br>memory by programming the IVT<br>Storage area Flash is implemented | anel, apart from all user memory pa<br>reset default for the IVTBASE regis<br>BASE register.<br>ed as the last 128 Words of user FI<br>he region is read as '0'. | ster, the vector table can be reloca           | ated in the         |

#### TABLE 4-1: PROGRAM AND DATA EEPROM MEMORY MAP

| REGISTER 7- | 5: OSCF | OSCFRQ: HFINTOSC FREQUENCY SELECTION REGISTER |     |          |         |         |         |  |  |

|-------------|---------|-----------------------------------------------|-----|----------|---------|---------|---------|--|--|

| U-0         | U-0     | U-0                                           | U-0 | R/W-q/q  | R/W-q/q | R/W-q/q | R/W-q/q |  |  |

| —           | —       | —                                             | —   | FRQ<3:0> |         |         |         |  |  |

| bit 7       |         |                                               |     |          |         |         | bit 0   |  |  |

|             |         |                                               |     |          |         |         |         |  |  |

Γ

| Logena.              |                      |                                                       |

|----------------------|----------------------|-------------------------------------------------------|

| R = Readable bit     | W = Writable bit     | U = Unimplemented bit, read as '0'                    |

| u = Bit is unchanged | x = Bit is unknown   | -n/n = Value at POR and BOR/Value at all other Resets |

| '1' = Bit is set     | '0' = Bit is cleared | q = Reset value is determined by hardware             |

#### bit 7-4 Unimplemented: Read as '0'

bit 3-0 FRQ<3:0>: HFINTOSC Frequency Selection bits<sup>(1)</sup>

| FRQ<3:0> | Nominal Freq (MHz) |

|----------|--------------------|

| 1001     |                    |

| 1010     |                    |

| 1111     |                    |

| 1110     | Reserved           |

| 1101     | -                  |

| 1100     |                    |

| 1011     |                    |

| 1000     | 64                 |

| 0111     | 48                 |

| 0110     | 32                 |

| 0101     | 16                 |

| 0100     | 12                 |

| 0011     | 8                  |

| 0010     | 4                  |

| 0001     | 2                  |

| 0000     | 1                  |

**Note 1:** Refer to Table 7-2 for more information.

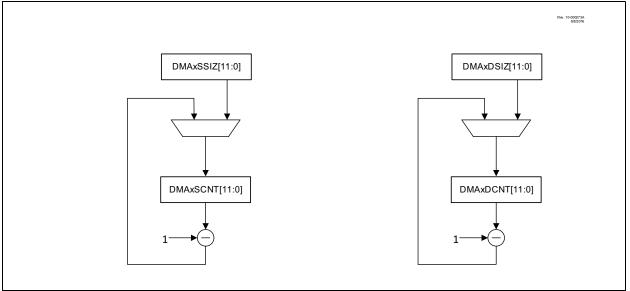

#### FIGURE 15-3: DMA COUNTERS BLOCK DIAGRAM

Table 15-2 has a few examples of configuring DMAMessage sizes.

| TABLE 15-2: | EXAMPLE | E MESSAGE SIZE | TABLE |      |

|-------------|---------|----------------|-------|------|

| Operat      | ion     | Example        | SCNT  | DONT |

| Operation                                | Example           | SCNT | DCNT | Comments                                                                                  |

|------------------------------------------|-------------------|------|------|-------------------------------------------------------------------------------------------|

| Read from single SFR<br>location to RAM  | U1RXB             | 1    | Ν    | N equals the number of bytes desired in the destination buffer. N >= 1.                   |

| Write to single SFR location<br>from RAM | U1TXB             | N    | 1    | N equals the number of bytes desired in the source buffer. N >= 1.                        |

|                                          | ADRES[H:L]        | 2    | 2*N  | N equals the number of ADC results to be stored in memory. N>= 1                          |

| Read from multiple SFR location          | TMR1[H:L]         | 2    | 2*N  | N equals the number of TMR1 Acquisition results to be stored in memory. N>= 1             |

|                                          | SMT1CPR[U:H:L]    | 3    | 3*N  | N equals the number of Capture Pulse Width measurements to be stored in memory. N>= 1     |

| Write to Multiple SFR regis-             | PWMDC[H:L]        | 2*N  | 2    | N equals the number of PWM duty cycle val-<br>ues to be loaded from a memory table. N>= 1 |

| ters                                     | All ADC registers | N*31 | 31   | Using the DMA to transfer a complete ADC context from RAM to the ADC registers.N>= 1      |

m = value depends on default location for that input

#### 17.8 Register Definitions: PPS Input Selection

'1' = Bit is set

'0' = Bit is cleared

#### REGISTER 17-1: xxxPPS: PERIPHERAL xxx INPUT SELECTION

U = Unimplemented bit,

read as '0'

|                  |       | -                        |                                                    |                        | -                      |                        |                        |

|------------------|-------|--------------------------|----------------------------------------------------|------------------------|------------------------|------------------------|------------------------|

| U-0              | U-0   | R/W-m/u <sup>(1,3)</sup> | R/W-m/u <sup>(1)</sup>                             | R/W-m/u <sup>(1)</sup> | R/W-m/u <sup>(1)</sup> | R/W-m/u <sup>(1)</sup> | R/W-m/u <sup>(1)</sup> |

| —                | _     |                          |                                                    | xxxPF                  | PS<5:0>                |                        |                        |

| bit 7            |       |                          |                                                    |                        |                        |                        | bit 0                  |

|                  |       |                          |                                                    |                        |                        |                        |                        |

| Legend:          |       |                          |                                                    |                        |                        |                        |                        |

| R = Readable I   | bit   | W = Writable             | bit                                                | -n/n = Value a         | at POR and BO          | R/Value at all o       | ther Resets            |

| u = Bit is uncha | anged | x = Bit is unkr          | x = Bit is unknown q = value depends on peripheral |                        |                        |                        |                        |

| bit 7-6 | Unimplemented: Read as '0'                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

|---------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| bit 5-3 | xxxPPS<5:3>: Peripheral xxx Input PORTx Pin Selection bits                                                                                                                                                                                                                                                                                                                                                                                                                                 |

|         | See Table 17-1 for the list of available ports and default pin locations.<br>$101 = PORTF^{(2)}$<br>$100 = PORTE^{(3)}$<br>$011 = PORTD^{(3)}$<br>010 = PORTC<br>001 = PORTB<br>000 = PORTA                                                                                                                                                                                                                                                                                                |

| bit 2-0 | xxxPPS<2:0>: Peripheral xxx Input PORTx Pin Selection bits                                                                                                                                                                                                                                                                                                                                                                                                                                 |

|         | <ul> <li>111 = Peripheral input is from PORTx Pin 7 (Rx7)</li> <li>110 = Peripheral input is from PORTx Pin 6 (Rx6)</li> <li>101 = Peripheral input is from PORTx Pin 5 (Rx5)</li> <li>100 = Peripheral input is from PORTx Pin 4 (Rx4)</li> <li>011 = Peripheral input is from PORTx Pin 3 (Rx3)</li> <li>010 = Peripheral input is from PORTx Pin 2 (Rx2)</li> <li>001 = Peripheral input is from PORTx Pin 1 (Rx1)</li> <li>000 = Peripheral input is from PORTx Pin 0 (Rx0)</li> </ul> |

#### Note 1: The Reset value 'm' of this register is determined by device default locations for that input.

#### 2: Reserved on PIC18LF26/27/45/46/57K42 parts.

3: Reserved on PIC18LF26/27K42 parts.

| U-0             | R/W-0/0                                                                                      | R/W-0/0                                                               | U-0          | U-0               | R/W-0/0          | R/W-0/0 | R/W-0/0              |  |  |

|-----------------|----------------------------------------------------------------------------------------------|-----------------------------------------------------------------------|--------------|-------------------|------------------|---------|----------------------|--|--|

| _               | DACMD                                                                                        | ADCMD                                                                 | _            | _                 | CMP2MD           | CMP1MD  | ZCDMD <sup>(1)</sup> |  |  |

| bit 7           |                                                                                              |                                                                       |              |                   | •                |         | bit C                |  |  |

| 1               |                                                                                              |                                                                       |              |                   |                  |         |                      |  |  |

| Legend:         |                                                                                              |                                                                       | .,           |                   |                  |         |                      |  |  |

| R = Readab      |                                                                                              | W = Writable I                                                        |              | •                 | nented bit, read |         |                      |  |  |

| u = Bit is un   | •                                                                                            | x = Bit is unkn                                                       |              |                   | t POR and BO     |         | other Resets         |  |  |

| '1' = Bit is se | et                                                                                           | '0' = Bit is clea                                                     | ared         | q = Value dep     | ends on condit   | ion     |                      |  |  |

|                 |                                                                                              |                                                                       |              |                   |                  |         |                      |  |  |

| bit 7           | •                                                                                            | ted: Read as '0                                                       | )'           |                   |                  |         |                      |  |  |

| bit 6           |                                                                                              | ACMD: Disable DAC bit                                                 |              |                   |                  |         |                      |  |  |

|                 |                                                                                              | 1 = DAC module disabled<br>0 = DAC module enabled                     |              |                   |                  |         |                      |  |  |

|                 |                                                                                              |                                                                       |              |                   |                  |         |                      |  |  |

| bit 5           | -                                                                                            | able ADCC bit                                                         |              |                   |                  |         |                      |  |  |

|                 |                                                                                              | <ul> <li>ADCC module disabled</li> <li>ADCC module enabled</li> </ul> |              |                   |                  |         |                      |  |  |

|                 |                                                                                              |                                                                       | .,           |                   |                  |         |                      |  |  |

| bit 4-3         | -                                                                                            | ted: Read as '0                                                       |              |                   |                  |         |                      |  |  |

| bit 2           |                                                                                              | sable Compara                                                         | tor CMP2 bit |                   |                  |         |                      |  |  |

|                 |                                                                                              | 1 = CMP2 module disabled<br>0 = CMP2 module enabled                   |              |                   |                  |         |                      |  |  |

|                 |                                                                                              |                                                                       |              |                   |                  |         |                      |  |  |

| bit 1           |                                                                                              | CMP1MD: Disable Comparator CMP1 bit                                   |              |                   |                  |         |                      |  |  |

|                 | 1 = CMP1 module disabled<br>0 = CMP1 module enabled                                          |                                                                       |              |                   |                  |         |                      |  |  |

| bit 0           |                                                                                              |                                                                       |              | ь ь: <b>н</b> (1) |                  |         |                      |  |  |

|                 | <b>ZCDMD:</b> Disable Zero-Cross Detect module bit <sup>(1)</sup><br>1 = ZCD module disabled |                                                                       |              |                   |                  |         |                      |  |  |

|                 |                                                                                              |                                                                       |              |                   |                  |         |                      |  |  |

|                 | 0 = ZCD mod                                                                                  | iule enabled                                                          |              |                   |                  |         |                      |  |  |

#### REGISTER 19-3: PMD2: PMD CONTROL REGISTER 2

**Note 1:** Subject to ZCD bit in CONFIG2H.

| Name   | Bit 7                                                    | Bit 6         | Bit 5        | Bit 4         | Bit 3           | Bit 2      | Bit 1      | Bit 0 | Reset<br>Values<br>on<br>Page |

|--------|----------------------------------------------------------|---------------|--------------|---------------|-----------------|------------|------------|-------|-------------------------------|

| TxCON  |                                                          | _             | CKPS         | <1:0>         |                 | SYNC       | RD16       | ON    | 313                           |

| TxGCON | GE                                                       | GPOL          | GTM          | GSPM          | GO/DONE         | GVAL       | _          | _     | 314                           |

| TxCLK  | —                                                        | —             | _            |               | (               | CS<4:0>    |            |       | 315                           |

| TxGATE | —                                                        | _             | _            |               | G               | SS<4:0>    |            |       | 316                           |

| TMRxL  | TMRxL Least Significant Byte of the 16-bit TMR3 Register |               |              |               |                 |            | 317        |       |                               |

| TMRxH  | Ho                                                       | Iding Registe | r for the Mo | ost Significa | ant Byte of the | 16-bit TMR | 3 Register |       | 317                           |

#### TABLE 21-3: SUMMARY OF REGISTERS ASSOCIATED WITH TIMER1/3/5 AS A TIMER/COUNTER

Legend: — = Unimplemented location, read as '0'. Shaded cells are not used by TIMER1/3/5.

#### 25.6.3 PERIOD AND DUTY CYCLE MODE

In Duty Cycle mode, either the duty cycle or period (depending on polarity) of the SMT1\_signal can be acquired relative to the SMT clock. The CPW register is updated on a falling edge of the signal, and the CPR register is updated on a rising edge of the signal, along with the SMT1TMR resetting to 0x0001. In addition, the GO bit is reset on a rising edge when the SMT is in Single Acquisition mode. See Figure 25-6 and Figure 25-7.

#### 26.3 Clock Source

The clock source is used to drive the dead-band timing circuits. The CWG module allows the following clock sources to be selected:

- Fosc (system clock)

- HFINTOSC

When the HFINTOSC is selected, the HFINTOSC will be kept running during Sleep. Therefore, CWG modes requiring dead band can operate in Sleep, provided that the CWG data input is also active during Sleep. The clock sources are selected using the CS bit of the CWGxCLKCON register (Register 26-3). The system clock Fosc, is disabled in Sleep and thus dead-band control cannot be used.

#### 26.4 Selectable Input Sources

The CWG generates the output waveforms from the following input sources:

TABLE 26-1: SELECTABLE INPUT SOURCES

| Source<br>Peripheral | Signal Name                     | ISM<2:0> |

|----------------------|---------------------------------|----------|

| CWGxPPS              | Pin selected by<br>CWGxPPS      | 000      |

| CCP1                 | CCP1 Output                     | 001      |

| CCP2                 | CCP2 Output                     | 010      |

| PWM3                 | PWM3 Output                     | 011      |

| PWM4                 | PWM4 Output                     | 100      |

| CMP1                 | Comparator 1 Output             | 101      |

| CMP2                 | Comparator 2 Output             | 110      |

| DSM                  | Data signal modulator<br>output | 111      |

The input sources are selected using the IS<4:0> bits in the CWGxISM register (Register 26-4).

#### 26.5 Output Control

#### 26.5.1 CWG OUTPUTS

Each CWG output can be routed to a Peripheral Pin Select (PPS) output via the RxyPPS register (see Section 17.0 "Peripheral Pin Select (PPS) Module").

#### 26.5.2 POLARITY CONTROL

The polarity of each CWG output can be selected independently. When the output polarity bit is set, the corresponding output is active-high. Clearing the output polarity bit configures the corresponding output as active-low. However, polarity does not affect the override levels. Output polarity is selected with the POLy bits of the CWGxCON1. Auto-shutdown and steering options are unaffected by polarity.

#### 26.6 Dead-Band Control

The dead-band control provides non-overlapping PWM signals to prevent shoot-through current in PWM switches. Dead-band operation is employed for Half-Bridge and Full-Bridge modes. The CWG contains two 6-bit dead-band counters. One is used for the rising edge of the input source control in Half-Bridge mode or for reverse dead-band Full-Bridge mode. The other is used for the falling edge of the input source control in Half-Bridge mode or for forward dead band in Full-Bridge mode.

Dead band is timed by counting CWG clock periods from zero up to the value in the rising or falling deadband counter registers. See CWGxDBR and CWGxDBF registers, respectively.

### 26.6.1 DEAD-BAND FUNCTIONALITY IN HALF-BRIDGE MODE

In Half-Bridge mode, the dead-band counters dictate the delay between the falling edge of the normal output and the rising edge of the inverted output. This can be seen in Figure 26-2.

### 26.6.2 DEAD-BAND FUNCTIONALITY IN FULL-BRIDGE MODE

In Full-Bridge mode, the dead-band counters are used when undergoing a direction change. The MODE<0> bit of the CWGxCON0 register can be set or cleared while the CWG is running, allowing for changes from Forward to Reverse mode. The CWGxA and CWGxC signals will change immediately upon the first rising input edge following a direction change, but the modulated signals (CWGxB or CWGxD, depending on the direction of the change) will experience a delay dictated by the dead-band counters.

| R/W-0/0          | R/W-0/0           | R/W-0/0           | R/W-0/0          | R/W-0/0             | R/W-0/0             | R/W-0/0             | R/W-0/0             |

|------------------|-------------------|-------------------|------------------|---------------------|---------------------|---------------------|---------------------|

| OVRD             | OVRC              | OVRB              | OVRA             | STRD <sup>(2)</sup> | STRC <sup>(2)</sup> | STRB <sup>(2)</sup> | STRA <sup>(2)</sup> |

| bit 7            |                   |                   |                  |                     |                     |                     | bit (               |

| Legend:          |                   |                   |                  |                     |                     |                     |                     |

| R = Readable     | e bit             | W = Writable      | bit              | U = Unimpler        | nented bit, read    | as '0'              |                     |

| u = Bit is uncl  | hanged            | x = Bit is unkr   | nown             | -n/n = Value a      | at POR and BO       | R/Value at all c    | other Resets        |

| '1' = Bit is set |                   | '0' = Bit is clea | ared             | q = Value dep       | pends on condit     | ion                 |                     |

|                  |                   |                   |                  |                     |                     |                     |                     |

| bit 7            | OVRD: Stee        | ring Data D bit   |                  |                     |                     |                     |                     |

| bit 6            | OVRC: Stee        | ring Data C bit   |                  |                     |                     |                     |                     |

| bit 5            | OVRB: Stee        | ring Data B bit   |                  |                     |                     |                     |                     |

| bit 4            | OVRA: Stee        | ring Data A bit   |                  |                     |                     |                     |                     |

| bit 3            | STRD: Steer       | ring Enable bit D | )(2)             |                     |                     |                     |                     |

|                  | 1 = CWGxD         | output has the    | CWG data inp     | ut waveform wi      | th polarity contr   | ol from POLD        | oit                 |

|                  | 0 = CWGxD         | output is assigr  | ed to value of   | OVRD bit            |                     |                     |                     |

| bit 2            | STRC: Steer       | ring Enable bit C | <sub>)</sub> (2) |                     |                     |                     |                     |

|                  | 1 = CWGxC         | output has the    | CWG data inp     | ut waveform wi      | th polarity contr   | ol from POLC I      | oit                 |

|                  | 0 = CWGxC         | output is assigr  | ed to value of   | OVRC bit            |                     |                     |                     |

| bit 1            | STRB: Steer       | ring Enable bit E | 3(2)             |                     |                     |                     |                     |

|                  |                   | output has the    | •                |                     | th polarity contr   | ol from POLB b      | bit                 |

|                  |                   | output is assign  |                  | OVRB bit            |                     |                     |                     |

| bit 0            |                   | ring Enable bit A |                  |                     |                     |                     |                     |

|                  |                   | output has the    | •                |                     | th polarity contr   | ol from POLA b      | bit                 |

|                  | 0 = CWGxA         | output is assign  | ed to value of   | OVRA bit            |                     |                     |                     |

| Note 1: Th       | e bits in this re | gister apply only | when MODE        | <2:0> = 00x (R      | Register 26-1, St   | eering modes)       |                     |

| <b>9.</b> Th     | in hit in double  | buffered when I   | MODE - 2:05 -    | 001                 |                     |                     |                     |

### **REGISTER 26-5:** CWGxSTR<sup>(1)</sup>: CWG STEERING CONTROL REGISTER

**2:** This bit is double-buffered when MODE<2:0> = 001.

#### 31.5 LIN Modes (UART1 only)

LIN is a protocol used primarily in automotive applications. The LIN network consists of two kinds of software processes: a Master process and a Slave process. Each network has only one Master process and one or more Slave processes.

From a physical layer point of view, the UART on one processor may be driven by both a Master and a Slave process, as long as only one Master process exists on the network.

A LIN transaction consists of a Master process followed by a Slave process. The Slave process may involve more than one Slave where one is transmitting and the other(s) are receiving. The transaction begins by the following Master process transmission sequence:

- 1. Break

- 2. Delimiter bit

- 3. Sync Field

- 4. PID byte

The PID determines which Slave processes are expected to respond to the Master. When the PID byte is complete, the TX output remains in the Idle state. One or more of the Slave processes may respond to the Master process. If no one responds within the interbyte period, the Master is free to start another transmission. The inter-byte period is timed by software using a means other than the UART.

The Slave process follows the Master process. When the Slave software recognizes the PID then that Slave process responds by either transmitting the required response or by receiving the transmitted data. Only Slave processes send data. Therefore, Slave processes receiving data are receiving that of another Slave process.

When a Slave sends data, the Slave UART automatically calculates the checksum for the transmitted bytes as they are sent and appends the inverted checksum byte to the slave response.

When a Slave receives data, the checksum is accumulated on each byte as it is received using the same algorithm as the sending process. The last byte, which is the inverted checksum value calculated by the sending process, is added to the locally calculated checksum by the UART. The check passes when the result is all '1's, otherwise the check fails and the CERIF bit is set.

Two methods for computing the checksum are available: legacy and enhanced. The legacy checksum includes only the data bytes. The enhanced checksum includes the PID and the data. The COEN control bit in the UxCON2 register determines the checksum method. Setting COEN to '1' selects the enhanced method. Software must select the appropriate method before the Start bit of the checksum byte is received.

#### 31.5.1 LIN MASTER/SLAVE MODE

The LIN Master mode includes capabilities to generate Slave processes. The Master process stops at the PID transmission. Any data that is transmitted in Master/ Slave mode is done as a Slave process. LIN Master/ Slave mode is configured by the following settings:

- MODE<3:0> = 1100

- **TXEN =** 1

- RXEN = 1

- UxBRGH:L = Value to achieve desired baud rate

- TXPOL = 0 (for high Idle state)

- STP = desired Stop bits selection

- C0EN = desired checksum mode

- RxyPPS = TX pin selection code

- TX pin TRIS control = 0

- ON = 1

Note: The TXEN bit must be set before the Master process is received and remain set while in LIN mode whether or not the slave process is a transmitter.

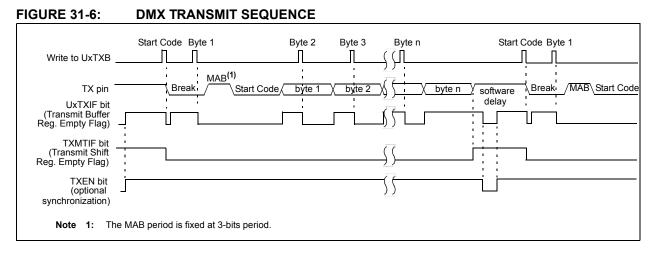

#### 31.9 Stop Bits

The number of Stop bits is user selectable with the STP bits in the UxCON2 register. The STP bits affect all modes of operation.

Stop bits selections include:

- 1 transmit with receive verify on first

- 1.5 transmit with receive verify on first

- · 2 transmit with receive verify on both

- · 2 transmit with receive verify on first only

In all modes, except DALI, the transmitter is idle for the number of Stop bit periods between each consecutively transmitted word. In DALI, the Stop bits are generated after the last bit in the transmitted data stream.

The input is checked for the idle level in the middle of the first Stop bit, when receive verify on first is selected, as well as in the middle of the second Stop bit, when verify on both is selected. If any Stop bit verification indicates a non-idle level, the framing error FERIF bit is set for the received word.

#### 31.9.1 DELAYED UXRXIF

When operating in Half-Duplex mode, where the microcontroller needs to reverse the transceiver direction after a reception, it may be more convenient to hold off the UxRXIF interrupt until the end of the Stop bits to avoid line contention. The user selects when the UxRXIF interrupt occurs with the STPMD bit in the UxFIFO register. When STPMD is '1', the UxRXIF occurs at the end of the last Stop bit. When STPMD is '0', UxRXIF occurs when the received byte is stored in the receive FIFO. When STP < 1:0 > = 10, the store operation is performed in the middle of the second Stop bit, otherwise, it is performed in the middle of the first Stop bit. The FERIF and PERIF interrupts are not delayed with STPMD. Only UxRXIF is delayed when STPMD is set and should be the only indicator for reversing transceiver direction.

#### 31.10 Operation after FIFO overflow

The Receive Shift Register (RSR) can be configured to stop or continue running during a receive FIFO overflow condition. Stopped operation is the Legacy mode.

When the RSR continues to run during an overflow condition, the first word received after clearing the overflow will always be valid.

When the RSR is stopped during an overflow condition, synchronization with the Start bits is lost. Therefore, the first word received after the overflow is cleared may start in the middle of a word.

Operation during overflow is selected with the RUNOVF bit in the UxCON2 register. Setting the RUNOVF bit selects the run during overflow method.

#### 31.11 Receive and Transmit Buffers

The UART uses small buffer areas to transmit and receive data. These are sometimes referred to as FIFOs.

The receiver has a Receive Shift Register (RSR) and two buffer registers. The buffer at the top of the FIFO (earliest byte to enter the FIFO) is by retrieved by reading the UxRXB register.

The transmitter has one Transmit Shift Register (TSR) and one buffer register. Writes to UxTXB go to the transmit buffer then immediately to the TSR, if it is empty. When the TSR is not empty, writes to UxTXB are held then transferred to the TSR when it becomes available.

#### 31.11.1 FIFO STATUS

The UxFIFO register contains several status bits for determining the state of the receive and transmit buffers.

The RXBE bit indicates that the receive FIFO is empty. This bit is essentially the inverse of UxRXIF. The RXBF bit indicates that the receive FIFO is full.

The transmitter has only one buffer register so the status bits are essentially a copy and inverse of the UxTXIF bit. The TXBE bit indicates that the buffer is empty (same as UxTXIF) and the TXBF bit indicates that the buffer is full (UxTXIF inverse). A third transmitter status bit, TXWRE (transmit write error), is set whenever a UxTXB write is performed when the TXBF bit is set. This indicates that the write was unsuccessful.

#### 31.11.2 FIFO RESET

All modes support resetting the receive and transmit buffers.

The receive buffer is flushed and all unread data discarded when the RXBE bit in the UxFIFO register is written to '1'. The MOVWF instruction with the TXBE bit cleared should be used to avoid inadvertently clearing a byte pending in the TSR when UxTXB is empty.

Data written to UxTXB when TXEN is low will be held in the Transmit Shift Register (TSR) then sent when TXEN is set. The transmit buffer and inactive TSR are flushed by setting the TXBE bit in the UxFIFO register. Setting TXBE while a character is actively transmitting from the TSR will complete the transmission without being flushed.

Clearing the ON bit will discard all received data and transmit data pending in the TSR and UxTXB.

#### REGISTER 31-8: UxBRGL: UART BAUD RATE GENERATOR LOW REGISTER

| R/W-0/0          | R/W-0/0 | R/W-0/0            | R/W-0/0 | R/W-0/0                    | R/W-0/0       | R/W-0/0          | R/W-0/0     |

|------------------|---------|--------------------|---------|----------------------------|---------------|------------------|-------------|

|                  |         |                    | BRG     | <7:0>                      |               |                  |             |

| bit 7            |         |                    |         |                            |               |                  | bit 0       |

|                  |         |                    |         |                            |               |                  |             |

| Legend:          |         |                    |         |                            |               |                  |             |

| R = Readable     | bit     | W = Writable       | bit     | U = Unimplemented bit, rea |               | as '0'           |             |

| u = Bit is uncha | anged   | x = Bit is unknown |         | -n/n = Value a             | at POR and BO | R/Value at all c | ther Resets |

| '1' = Bit is set |         | '0' = Bit is clea  | ared    |                            |               |                  |             |

bit 7-0 BRG<7:0>: Least Significant Byte of Baud Rate Generator

#### REGISTER 31-9: UxBRGH: UART BAUD RATE GENERATOR HIGH REGISTER

| R/W-0/0 |

|---------|---------|---------|---------|---------|---------|---------|---------|

|         |         |         | BRG<    | <15:8>  |         |         |         |

| bit 7   |         |         |         |         |         |         | bit 0   |

| Legend:              |                      |                                                       |

|----------------------|----------------------|-------------------------------------------------------|

| R = Readable bit     | W = Writable bit     | U = Unimplemented bit, read as '0'                    |

| u = Bit is unchanged | x = Bit is unknown   | -n/n = Value at POR and BOR/Value at all other Resets |

| '1' = Bit is set     | '0' = Bit is cleared |                                                       |

bit 7-0 BRG<15:8>: Most Significant Byte of Baud Rate Generator

**Note 1:** The UxBRG registers should only be written when ON = 0.

- **2:** Maximum BRG value when MODE = 100x and BRGS = 1 is 0x7FFE.

- 3: Maximum BRG value when MODE = '100x' and BRGS = 0 is 0x1FFE.

| R-0/0      | R-0/0                                 | U-0                                 | U-0                        | U-0                     | R/W-0/0           | R/W-0/0            | R/W-0/0            |

|------------|---------------------------------------|-------------------------------------|----------------------------|-------------------------|-------------------|--------------------|--------------------|

| BUSY       | SSFLT                                 | —                                   | _                          | _                       | SSET              | TXR <sup>(1)</sup> | RXR <sup>(1)</sup> |

| oit 7      |                                       |                                     |                            |                         |                   |                    | bit                |

|            |                                       |                                     |                            |                         |                   |                    |                    |

| Legend:    |                                       |                                     |                            |                         |                   |                    |                    |

| R = Readab | le bit                                | W = Writable                        | bit                        | U = Unimplei            | mented bit, reac  | l as 'O'           |                    |

| bit 7      | BUSY: SPI N                           | /lodule Busy Sta                    | atus bit                   |                         |                   |                    |                    |

|            | 1 = Data exc                          | hange is busy                       |                            |                         |                   |                    |                    |

|            | 0 = Data exc                          | hange is not tal                    | king place                 |                         |                   |                    |                    |

| bit 6      | SSFLT: SS(ir                          | n) Fault Status b                   | bit                        |                         |                   |                    |                    |

|            | <u>If SSET = 0</u>                    |                                     |                            |                         |                   |                    |                    |

|            | 1 = SS(in) er                         | nded the transa                     | ction unexpec              | tedly, and the          | data byte being   | received was l     | ost                |

|            | 0 <b>= SS(in) e</b> r                 | nded normally                       |                            |                         |                   |                    |                    |

|            | If SSET = 1                           |                                     |                            |                         |                   |                    |                    |

|            | This bit is un                        | changed.                            |                            |                         |                   |                    |                    |

| bit 5-3    | Unimpleme                             | n <b>ted</b> : Read as '            | D'                         |                         |                   |                    |                    |

| bit 2      | SSET: Slave                           | Select Enable                       | oit                        |                         |                   |                    |                    |

|            | Master mode                           | <u>e:</u>                           |                            |                         |                   |                    |                    |

|            | 1 = SS(out) i                         | s driven to the a                   | active state co            | ontinuously             |                   |                    |                    |

|            | 0 = SS(out) i                         | s driven to the a                   | active state w             | hile the transm         | it counter is not | zero               |                    |

|            | Slave mode:                           |                                     |                            |                         |                   |                    |                    |

|            | 1 = SS(in) is                         | ignored and da                      | ta is clocked              | on all SCK(in)          | (as though SS =   | TRUE at all ti     | mes)               |

|            |                                       | hables/disables<br>able 32-2 for de |                            | d tri-states SD0        | O if the TRIS bit | associated wit     | h the SDO pi       |

| bit 1      | TXR: Transm                           | nit Data-Require                    | d Control bit <sup>(</sup> | 1)                      |                   |                    |                    |

|            | 1 = TxFIFO                            | data is required                    | for a transfer             |                         |                   |                    |                    |

|            | 0 <b>= TxFIFO</b> 0                   | data is not requi                   | red for a tran             | sfer                    |                   |                    |                    |

| bit 0      | RXR: Receiv                           | e FIFO Space-l                      | Required Con               | trol bit <sup>(1)</sup> |                   |                    |                    |

|            | 1 = Data trar                         | nsfers are suspe                    | ended if the R             | xFIFO is full           |                   |                    |                    |

|            | 0 = Received                          | d data is not sto                   | red in the FIF             | 0                       |                   |                    |                    |

|            | See Table 32-1 a<br>pertaining to TXF |                                     |                            | er mode" and            | Section 32.6 "    | Slave Mode" fo     | or more detai      |

| <b>.</b>   | This register she                     | uld not be writte                   | n to while a t             | ranafar ia in nr        | Daroce (RLIEV h   |                    |                    |

2: This register should not be written to while a transfer is in progress (BUSY bit of SPIxCON2 is set).

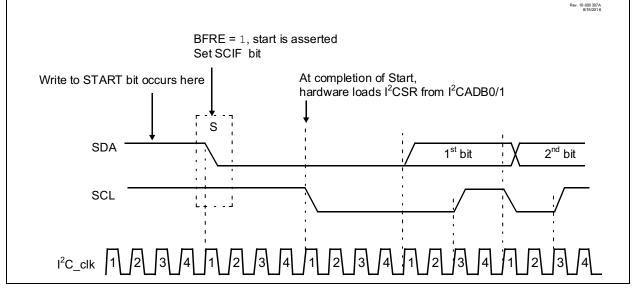

asserting the Start condition. The action of the SDA being driven low while SCL is high is the Start condition,

causing the SCIF bit to be set. One TSCL later the SCL

is asserted low, ending the start sequence. Figure 33-

15 shows the Start condition timing.

#### 33.5.5 I<sup>2</sup>C MASTER MODE START CONDITION TIMING

The user can initiate a Start condition by either writing to the Start bit (S) of the I2CxCON0 register or by writing to the I2CxTXB register based on the ABD bit setting. Master hardware waits for BFRE = 1, before

#### FIGURE 33-15: START CONDITION TIMING

#### 33.5.6 I<sup>2</sup>C MASTER MODE REPEATED START CONDITION TIMING

A Repeated Start condition occurs when the Start bit of the I2CxCON0 register is set and the master module is waiting from a Restart clock stretch event (RSEN = 1 and I2CxCNT = 0).

When the Start bit is set, the SDA pin is released high for TscL/2. Then the SCL pin is released floated high) for TscL/2. If the SDA pin is detected low, bus collision flag (BCLIF) is set and the master goes idle. If SDA is detected high, the SDA pin will be pulled low (Start condition) for TscL. Last, SCL is asserted low and I2CxADB0/1 is loaded into the shift register. As soon as a Restart condition is detected on the SDA and SCL pins, the RSCIF bit is set. Figure 33-16 shows the timings for repeated Start Condition.

### REGISTER 33-4: I2CxCLK: I<sup>2</sup>C CLOCK SELECTION REGISTER

| U-0   | U-0 | U-0 | U-0 | R/W-0/0 | R/W-0/0 | R/W-0/0 | R/W-0/0 |

|-------|-----|-----|-----|---------|---------|---------|---------|

|       | _   | —   | _   |         | CLK     | <3:0>   |         |

| bit 7 |     |     |     |         |         |         | bit 0   |

|       |     |     |     |         |         |         |         |

| Legend:              |                      |                                                       |

|----------------------|----------------------|-------------------------------------------------------|

| R = Readable bit     | W = Writable bit     | U = Unimplemented bit, read as '0'                    |

| u = Bit is unchanged | x = Bit is unknown   | -n/n = Value at POR and BOR/Value at all other Resets |

| '1' = Bit is set     | '0' = Bit is cleared | HS = Hardware set HC = Hardware clear                 |

#### bit 7-4 Unimplemented: Read as '0'

ſ

bit 3-0 **CLK<3:0>:** I<sup>2</sup>C Clock Selection Bits

| CLK<3:0>  | I <sup>2</sup> Cx Clock Selection |

|-----------|-----------------------------------|

| 1010-1111 | Reserved                          |

| 1001      | SMT1 overflow                     |

| 1000      | TMR6 post scaled output           |

| 0111      | TMR4 post scaled output           |

| 0110      | TMR2 post scaled output           |

| 0101      | TMR0 overflow                     |

| 0100      | Clock Reference output            |

| 0011      | MFINTOSC (500 kHz)                |

| 0010      | HFINTOSC                          |

| 0001      | Fosc                              |

| 0000      | Fosc/4                            |

### REGISTER 33-5: I2CxBTO: I<sup>2</sup>C BUS TIMEOUT SELECTION REGISTER

| U-0   | U-0 | U-0 | U-0 | U-0 | R/W-0/0 | R/W-0/0  | R/W-0/0 |

|-------|-----|-----|-----|-----|---------|----------|---------|

|       | —   | —   | —   | _   |         | BTO<2:0> |         |

| bit 7 |     |     |     |     |         |          | bit 0   |

| Legend:              |                      |                                                       |

|----------------------|----------------------|-------------------------------------------------------|

| R = Readable bit     | W = Writable bit     | U = Unimplemented bit, read as '0'                    |

| u = Bit is unchanged | x = Bit is unknown   | -n/n = Value at POR and BOR/Value at all other Resets |

| '1' = Bit is set     | '0' = Bit is cleared | HS = Hardware set HC = Hardware clear                 |

| bit 7-3 | Unimplemented: Read as '0' |

|---------|----------------------------|

|         |                            |

bit 2-0

Г

BTO<2:0>: I<sup>2</sup>C Bus Timeout Selection bits

| BTO<2:0> | I <sup>2</sup> Cx Bus Timeout Selection |  |  |  |

|----------|-----------------------------------------|--|--|--|

| 111      | CLC4OUT                                 |  |  |  |

| 110      | CLC3OUT                                 |  |  |  |

| 101      | CLC2OUT                                 |  |  |  |

| 100      | CLC1OUT                                 |  |  |  |

| 011      | TMR6 post scaled output                 |  |  |  |

| 010      | TMR4 post scaled output                 |  |  |  |

| 001      | TMR2 post scaled output                 |  |  |  |

| 000      | Reserved                                |  |  |  |

#### **36.1 ADC Configuration**

When configuring and using the ADC the following functions must be considered:

- Port configuration

- Channel selection

- ADC voltage reference selection

- ADC conversion clock source

- Interrupt control

- Result formatting

- Conversion Trigger Selection

- ADC Acquisition Time

- ADC Precharge Time

- · Additional Sample and Hold Capacitor

- Single/Double Sample Conversion

- Guard Ring Outputs

#### 36.1.1 PORT CONFIGURATION

The ADC can be used to convert both analog and digital signals. When converting analog signals, the I/O pin should be configured for analog by setting the associated TRIS and ANSEL bits. Refer to **Section 16.0 "I/O Ports"** for more information.

**Note:** Analog voltages on any pin that is defined as a digital input may cause the input buffer to conduct excess current.

#### 36.1.2 CHANNEL SELECTION

There are several channel selections available:

- Eight PORTA pins (RA<7:0>)

- Eight PORTB pins (RB<7:0>)

- Eight PORTC pins (RC<7:0>)

- Eight PORTD pins (RD<7:0>, PIC18(L)F45/46/47/ 55/56/57K42 only)

- Three PORTE pins (RE<2:0>, PIC18(L)F45/46/47/ 55/56/57K42 only)

- Eight PORTF pins (RD<7:0>, PIC18(L)F55/56/ 57K42 only)

- Temperature Indicator

- DAC output

- Fixed Voltage Reference (FVR)

- Vss (ground)

The ADPCH register determines which channel is connected to the sample and hold circuit.

When changing channels, a delay is required before starting the next conversion.

Refer to Section 36.2 "ADC Operation" for more information.

#### 36.1.3 ADC VOLTAGE REFERENCE

The PREF<1:0> bits of the ADREF register provide control of the positive voltage reference. The positive voltage reference can be:

- VREF+ pin

- VDD

- FVR outputs

The NREF bit of the ADREF register provides control of the negative voltage reference. The negative voltage reference can be:

- VREF- pin

- Vss

See **Section 34.0 "Fixed Voltage Reference (FVR)"** for more details on the Fixed Voltage Reference.

#### 36.1.4 CONVERSION CLOCK

The source of the conversion clock is software selectable via the ADCLK register and the CS bits of the ADCON0 register. If Fosc is selected as the ADC clock, there is a prescaler available to divide the clock so that it meets the ADC clock period specification. The ADC clock source options are the following:

- Fosc/(2\*n)(where n is from 1 to 128)

- · FRC (dedicated RC oscillator)

The time to complete one bit conversion is defined as TAD. Refer Figure 36-2 for the complete timing details of the ADC conversion.

For correct conversion, the appropriate TAD specification must be met. Refer to Table 44-16 for more information. Table 36-1 gives examples of appropriate ADC clock selections.

- **Note 1:** Unless using the FRC, any changes in the system clock frequency will change the ADC clock frequency, which may adversely affect the ADC result.

- 2: The internal control logic of the ADC runs off of the clock selected by the CS bit of ADCON0. What this can mean is when the CS bit of ADCON0 is set to '1' (ADC runs on FRC), there may be unexpected delays in operation when setting ADC control bits.

#### TABLE 44-23: SPI MODE REQUIREMENTS (MASTER MODE)

| Standard Operating Conditions (unless otherwise stated) |                       |                                                  |                                            |                   |                                 |       |                       |  |  |

|---------------------------------------------------------|-----------------------|--------------------------------------------------|--------------------------------------------|-------------------|---------------------------------|-------|-----------------------|--|--|

| Param<br>No.                                            | Symbol                | Characteristic                                   | Min.                                       | Тур†              | Max.                            | Units | Conditions            |  |  |

|                                                         | Тѕск                  | SCK Cycle Time (2x Prescaled)                    | 61                                         | _                 | _                               | ns    | Transmit only mode    |  |  |

|                                                         |                       |                                                  | _                                          | 16 <sup>(1)</sup> | _                               | MHz   |                       |  |  |

|                                                         |                       |                                                  | 95                                         |                   | _                               | ns    | Eull duplex mode      |  |  |

|                                                         |                       |                                                  | _                                          | 10 <sup>(1)</sup> | _                               | MHz   |                       |  |  |

| SP70*                                                   | TssL2scH,             | SDO to SCK↓ or SCK↑ input                        | Тѕск                                       | _                 | _                               | ns    | FST = Q               |  |  |

| TssL2scL                                                | TssL2scL              |                                                  | 0                                          |                   | _ /                             | ns    | ) FST = 1             |  |  |

| SP71*                                                   | TscH                  | SCK output high time                             | 0.5 Тѕск - 12                              | _                 | 0.5 Тscк 🛃 12                   | ns    |                       |  |  |

| SP72*                                                   | TscL                  | SCK output low time                              | 0.5 Тѕск - 12                              | _                 | 0.5 Тѕск + 12                   | ns <  |                       |  |  |

| SP73*                                                   | TDIV2scH,<br>TDIV2scL | Setup time of SDI data input to SCK edge         | 85                                         |                   |                                 | ns    |                       |  |  |

|                                                         | TscH2DIL,<br>TscL2DIL | Hold time of SDI data input to SCK edge          | 0                                          | _                 |                                 | 195   |                       |  |  |

|                                                         |                       | Hold time of SDI data input to final SCK         | 0.5 Tscк                                   | _                 | $\square \setminus \forall / /$ | RS    | CKE = 0, SMP = 1      |  |  |

| SP75*                                                   | TDOR                  | SDO data output rise time                        | — /                                        | ~10               | 25                              | ns    | CL = 50 pF            |  |  |