#### Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

#### Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

E·XFI

| Product Status             | Active                                                                      |

|----------------------------|-----------------------------------------------------------------------------|

| Core Processor             | PIC                                                                         |

| Core Size                  | 8-Bit                                                                       |

| Speed                      | 64MHz                                                                       |

| Connectivity               | I <sup>2</sup> C, LINbus, SPI, UART/USART                                   |

| Peripherals                | Brown-out Detect/Reset, DMA, HLVD, POR, PWM, WDT                            |

| Number of I/O              | 36                                                                          |

| Program Memory Size        | 128KB (64K x 16)                                                            |

| Program Memory Type        | FLASH                                                                       |

| EEPROM Size                | 1K x 8                                                                      |

| RAM Size                   | 8K x 8                                                                      |

| Voltage - Supply (Vcc/Vdd) | 1.8V ~ 3.6V                                                                 |

| Data Converters            | A/D 35x12b; D/A 1x5b                                                        |

| Oscillator Type            | Internal                                                                    |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                           |

| Mounting Type              | Surface Mount                                                               |

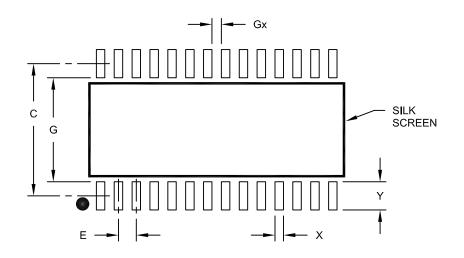

| Package / Case             | 44-TQFP                                                                     |

| Supplier Device Package    | 44-TQFP (10x10)                                                             |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/pic18lf47k42-i-pt |

|                            |                                                                             |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

| Device         | Data Sheet Index | Program Flash Memory (KB) | Data EEPROM (B) | Data SRAM (bytes) | I/O Pins | 12-bit ADC <sup>2</sup><br>(ch) | 5-bit DAC | Comparator | 8-bit/ (with HLT) /16-bit Timer | Window Watchdog Timer<br>(WWDT) | Signal Measurement Timer<br>(SMT) | CCP/10-bit PWM | CWG | NCO | CLC | Zero-Cross Detect | Direct Memory Access (DMA)<br>(ch) | Memory Access Partition | Vectored Interrupts | UART | l²C/SPI | Peripheral Pin Select | Peripheral Module Disable | Debug <sup>(1)</sup> |

|----------------|------------------|---------------------------|-----------------|-------------------|----------|---------------------------------|-----------|------------|---------------------------------|---------------------------------|-----------------------------------|----------------|-----|-----|-----|-------------------|------------------------------------|-------------------------|---------------------|------|---------|-----------------------|---------------------------|----------------------|

| PIC18(L)F24K42 | А                | 16                        | 256             | 1024              | 25       | 24                              | 1         | 2          | 3/4                             | Y                               | Y                                 | 4/4            | 3   | 1   | 4   | Y                 | 2                                  | Y                       | Y                   | 2    | 2/1     | Y                     | Υ                         | I                    |

| PIC18(L)F25K42 | А                | 32                        | 256             | 2048              | 25       | 24                              | 1         | 2          | 3/4                             | Y                               | Y                                 | 4/4            | 3   | 1   | 4   | Υ                 | 2                                  | Y                       | Y                   | 2    | 2/1     | Y                     | Υ                         | I                    |

| PIC18(L)F26K42 | В                | 64                        | 1024            | 4096              | 25       | 24                              | 1         | 2          | 3/4                             | Y                               | Y                                 | 4/4            | 3   | 1   | 4   | Υ                 | 2                                  | Y                       | Y                   | 2    | 2/1     | Y                     | Υ                         | I                    |

| PIC18(L)F27K42 | В                | 128                       | 1024            | 8192              | 25       | 24                              | 1         | 2          | 3/4                             | Y                               | Y                                 | 4/4            | 3   | 1   | 4   | Υ                 | 2                                  | Υ                       | Y                   | 2    | 2/1     | Y                     | Υ                         | I                    |

| PIC18(L)F45K42 | В                | 32                        | 256             | 2048              | 36       | 35                              | 1         | 2          | 3/4                             | Y                               | Y                                 | 4/4            | 3   | 1   | 4   | Y                 | 2                                  | Y                       | Y                   | 2    | 2/1     | Υ                     | Υ                         | 1                    |

| PIC18(L)F46K42 | В                | 64                        | 1024            | 4096              | 36       | 35                              | 1         | 2          | 3/4                             | Y                               | Y                                 | 4/4            | 3   | 1   | 4   | Υ                 | 2                                  | Υ                       | Y                   | 2    | 2/1     | Y                     | Υ                         | I                    |

| PIC18(L)F47K42 | В                | 128                       | 1024            | 8192              | 36       | 35                              | 1         | 2          | 3/4                             | Y                               | Y                                 | 4/4            | 3   | 1   | 4   | Y                 | 2                                  | Y                       | Y                   | 2    | 2/1     | Y                     | Y                         | I                    |

| PIC18(L)F55K42 | В                | 32                        | 256             | 2048              | 44       | 43                              | 1         | 2          | 3/4                             | Y                               | Y                                 | 4/4            | 3   | 1   | 4   | Y                 | 2                                  | Y                       | Y                   | 2    | 2/1     | Y                     | Y                         | I                    |

| PIC18(L)F56K42 | В                | 64                        | 1024            | 4096              | 44       | 43                              | 1         | 2          | 3/4                             | Y                               | Y                                 | 4/4            | 3   | 1   | 4   | Y                 | 2                                  | Y                       | Y                   | 2    | 2/1     | Y                     | Y                         | I                    |

| PIC18(L)F57K42 | В                | 128                       | 1024            | 8192              | 44       | 43                              | 1         | 2          | 3/4                             | Y                               | Y                                 | 4/4            | 3   | 1   | 4   | Y                 | 2                                  | Y                       | Y                   | 2    | 2/1     | Y                     | Υ                         | I                    |

Note 1: I – Debugging integrated on chip.

#### **Data Sheet Index:**

#### Unshaded devices are not described in this document.

DS40001869 PIC18(L)F24/25K42 Data Sheet, 28-Pin **A**:

B:

DS40001919

PIC18(L)F26/27/45/46/47/55/56/57K42 Data Sheet, 28/40/44/48-Pin

For other small form-factor package availability and marking information, visit **http://www.microchip.com/packaging** or contact your local sales office. Note:

# 9.6 Returning from Interrupt Service Routine (ISR)

The "Return from Interrupt" instruction (RETFIE) is used to mark the end of an ISR.

When RETFIE 1 instruction is executed, the PC is loaded with the saved PC value from the top of the PC stack. Saved context is also restored with the execution of this instruction. Thus, execution returns to the previous state of operation that existed before the interrupt occurred.

When RETFIE 0 instruction is executed, the saved context is not restored back to the registers.

# 9.7 Interrupt Latency

By assigning each interrupt with a vector address/ number (MVECEN = 1), scanning of all interrupts is not necessary to determine the source of the interrupt.

When MVECEN = 1, Vectored interrupt controller requires three clock cycles to vector to the ISR from main routine, thereby removing dependency of interrupt timing on compiled code.

There is a fixed latency of three instruction cycles between the completion of the instruction active when the interrupt occurred and the first instruction of the Interrupt Service Routine. Figure 9-7, Figure 9-8 and Figure 9-9 illustrate the sequence of events when a peripheral interrupt is asserted when the last executed instruction is one-cycle, two-cycle and three-cycle respectively, when MVECEN = 1.

After the Interrupt Flag Status bit is set, the current instruction completes executing. In the first latency cycle, the contents of the PC, STATUS, WREG, BSR, FSR0/1/2, PRODL/H and PCLATH/U registers are context saved and the IVTBASE+ Vector number is calculated. In the second latency cycle, the PC is loaded with the calculated vector table address for the interrupt source and the starting address of the ISR is fetched. In the third latency cycle, the PC is loaded with the ISR address. All the latency cycles are executed as a FNOP instruction.

When MVECEN = 0, Vectored interrupt controller requires two clock cycles to vector to the ISR from main routine. There is a latency of two instruction cycles plus the software latency between the completion of the instruction active when the interrupt occurred and the first instruction of the Interrupt Service Routine.

|                 | J-21. 11L7.                 |                                       |           |              |                  |                  |              |  |  |  |

|-----------------|-----------------------------|---------------------------------------|-----------|--------------|------------------|------------------|--------------|--|--|--|

| U-0             | U-0                         | R/W-0/0                               | R/W-0/0   | R/W-0/0      | U-0              | R/W-0/0          | R/W-0/0      |  |  |  |

| _               | -                           | INT2IE                                | CLC2IE    | CWG2IE       | —                | CCP2IE           | TMR4IE       |  |  |  |

| bit 7           |                             |                                       |           |              |                  |                  | bit (        |  |  |  |

|                 |                             |                                       |           |              |                  |                  |              |  |  |  |

| Legend:         |                             |                                       |           |              |                  |                  |              |  |  |  |

| R = Readab      | ole bit                     | W = Writable                          | bit       | U = Unimple  | mented bit, read | l as '0'         |              |  |  |  |

| u = Bit is un   | changed                     | x = Bit is unkr                       | nown      | -n/n = Value | at POR and BO    | R/Value at all o | other Resets |  |  |  |

| '1' = Bit is se | et                          | '0' = Bit is clea                     | ared      |              |                  |                  |              |  |  |  |

|                 |                             |                                       |           |              |                  |                  |              |  |  |  |

| bit 7-6         | Unimplemen                  | nted: Read as '                       | 0'        |              |                  |                  |              |  |  |  |

| bit 5           | INT2IE: Exte                | T2IE: External Interrupt 2 Enable bit |           |              |                  |                  |              |  |  |  |

|                 | 1 = Enabled                 |                                       |           |              |                  |                  |              |  |  |  |

|                 | 0 = Disabled                |                                       |           |              |                  |                  |              |  |  |  |

| bit 4           |                             | C2 Interrupt Ena                      | able bit  |              |                  |                  |              |  |  |  |

|                 | 1 = Enabled                 |                                       |           |              |                  |                  |              |  |  |  |

|                 | 0 = Disabled                |                                       |           |              |                  |                  |              |  |  |  |

| bit 3           |                             | VG2 Interrupt E                       | nable bit |              |                  |                  |              |  |  |  |

|                 | 1 = Enabled<br>0 = Disabled | I                                     |           |              |                  |                  |              |  |  |  |

| bit 2           |                             | ted: Read as '                        | ∩'        |              |                  |                  |              |  |  |  |

| bit 1           | -                           | P2 Interrupt En                       |           |              |                  |                  |              |  |  |  |

|                 | 1 = Enabled                 | rz menupi En                          |           |              |                  |                  |              |  |  |  |

|                 | 0 = Disabled                | I                                     |           |              |                  |                  |              |  |  |  |

| bit 0           |                             | R4 Interrupt En                       | able bit  |              |                  |                  |              |  |  |  |

|                 | 1 = Enabled                 |                                       |           |              |                  |                  |              |  |  |  |

|                 | 0 = Disabled                |                                       |           |              |                  |                  |              |  |  |  |

# REGISTER 9-21: PIE7: PERIPHERAL INTERRUPT ENABLE REGISTER 7

| R/W-1/1         | R/W-1/1                         | R/W-1/1            | U-0              | R/W-1/1 | R/W-1/1        | R/W-1/1           | R/W-1/1     |

|-----------------|---------------------------------|--------------------|------------------|---------|----------------|-------------------|-------------|

| CLC1IP          | CWG1IP                          | NCO1IP             | —                | CCP1IP  | TMR2IP         | TMR1GIP           | TMR1IP      |

| bit 7           |                                 |                    |                  |         |                |                   | bit (       |

| Legend:         |                                 |                    |                  |         |                |                   |             |

| R = Readabl     | o hit                           | W = Writable       | h it             |         | opted bit read |                   |             |

|                 |                                 | x = Bit is unkr    |                  | -       | t DOD and DO   | R/Value at all o  | ther Deceta |

| u = Bit is unc  | •                               |                    |                  |         | ILPOR and BC   | rk/value at all 0 | iner Reseis |

| '1' = Bit is se | t                               | '0' = Bit is cle   | areo             |         |                |                   |             |

| bit 7           | CLC1IP: CLC                     | C1 Interrupt Price | ority bit        |         |                |                   |             |

|                 | 1 = High pric<br>0 = Low price  |                    |                  |         |                |                   |             |

| bit 6           | CWG1IP: CV                      | VG1 Interrupt P    | riority bit      |         |                |                   |             |

|                 | 1 = High pric<br>0 = Low pric   |                    |                  |         |                |                   |             |

| bit 5           | NCO1IP: NC                      | O1 Interrupt Pr    | iority bit       |         |                |                   |             |

|                 | 1 = High prio                   |                    |                  |         |                |                   |             |

| bit 4           | Unimplemen                      | ted: Read as '     | 0'               |         |                |                   |             |

| bit 3           | CCP1IP: CCI                     | P1 Interrupt Pri   | ority bit        |         |                |                   |             |

|                 | 1 = High prio                   |                    |                  |         |                |                   |             |

| bit 2           | •                               | R2 Interrupt Pri   | ority bit        |         |                |                   |             |

|                 | 1 = High price0 = Low price     | •                  | -                |         |                |                   |             |

| bit 1           | TMR1GIP: TI                     | MR1 Gate Inter     | rupt Priority bi | t       |                |                   |             |

|                 | 1 = High price<br>0 = Low price |                    |                  |         |                |                   |             |

| bit 0           | TMR1IP: TM                      | R1 Interrupt Pri   | ority bit        |         |                |                   |             |

|                 | 1 = High prio                   |                    |                  |         |                |                   |             |

|                 | 0 = Low prio                    | rity               |                  |         |                |                   |             |

# REGISTER 9-29: IPR4: PERIPHERAL INTERRUPT PRIORITY REGISTER 4

# 11.6 Operation During Sleep

When the device enters Sleep, the WWDT is cleared. If the WWDT is enabled during Sleep, the WWDT resumes counting. When the device exits Sleep, the WWDT is cleared again.

The WWDT remains clear until the Oscillator Start-up Timer (OST) completes, if enabled. See **Section 7.2.1.3 "Oscillator Start-up Timer (OST)**" for more information on the OST.

When a WWDT time-out occurs while the device is in Sleep, no Reset is generated. Instead, the device wakes up and resumes operation. The  $\overline{TO}$  and  $\overline{PD}$  bits in the STATUS register are changed to indicate the event. The RWDT bit in the PCON0 register can also be used. See Section 4.0 "Memory Organization" for more information.

#### TABLE 11-2: WWDT CLEARING CONDITIONS

| Conditions                                              | WWDT                         |  |  |

|---------------------------------------------------------|------------------------------|--|--|

| WDTE<1:0> = 00                                          |                              |  |  |

| WDTE<1:0> = 01 and SEN = 0                              |                              |  |  |

| WDTE<1:0> = 10 and enter Sleep                          | Cleared                      |  |  |

| CLRWDT Command                                          | Cleared                      |  |  |

| Oscillator Fail Detected                                |                              |  |  |

| Exit Sleep + System Clock = SOSC, EXTRC, INTOSC, EXTCLK |                              |  |  |

| Exit Sleep + System Clock = XT, HS, LP                  | Cleared until the end of OST |  |  |

| Change INTOSC divider (IRCF bits)                       | Unaffected                   |  |  |

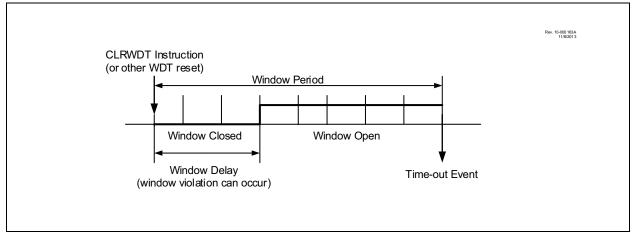

## FIGURE 11-2: WINDOW PERIOD AND DELAY

Depending on the priority of the DMA with respect to CPU execution (Refer to **Section 3.2** "**Memory Access Scheme**" for more information), the DMA Controller can move data through two methods:

- Stalling the CPU execution until it has completed its transfers (DMA has higher priority over the CPU in this mode of operation)

- Utilizing unused CPU cycles for DMA transfers (CPU has higher priority over the DMA in this mode of operation). Unused CPU cycles are referred to as bubbles which are instruction cycles available for use by the DMA to perform read and write operations. In this way, the effective bandwidth for handling data is increased; at the same time, DMA operations can proceed without causing a processor stall.

# 15.4 DMA Interface

The DMA module transfers data from the source to the destination one byte at a time, this smallest data movement is called a DMA data transaction. A DMA Message refers to one or more DMA data transactions.

Each DMA data transaction consists of two separate actions:

- Reading the Source Address Memory and storing the value in the DMA Buffer register

- Writing the contents of the DMA Buffer register to the Destination Address Memory

| Note: | DMA    | data  | movement | is | а | two-cycle |

|-------|--------|-------|----------|----|---|-----------|

|       | operat | tion. |          |    |   |           |

The XIP bit (DMAxCON0 register) is a status bit to indicate whether or not the data in the DMAxBUF register has been written to the destination address. If the bit is set then data is waiting to be written to the destination. If clear, it means that either data has been written to the destination or that no source read has occurred.

The DMA has read access to PFM, Data EEPROM, and SFR/GPR space, and write access to SFR/GPR space. Based on these memory access capabilities, the DMA can support the following memory transactions:

# TABLE 15-1: DMA MEMORY ACCESS

| Read Source          | Write Destination |  |  |  |  |

|----------------------|-------------------|--|--|--|--|

| Program Flash Memory | GPR               |  |  |  |  |

| Program Flash Memory | SFR               |  |  |  |  |

| Data EE              | GPR               |  |  |  |  |

| Data EE              | SFR               |  |  |  |  |

| GPR                  | GPR               |  |  |  |  |

| SFR                  | GPR               |  |  |  |  |

| GPR                  | SFR               |  |  |  |  |

| SFR                  | SFR               |  |  |  |  |

| Note: | Even though the DMA module has access<br>to all memory and peripherals that are<br>also available to the CPU, it is<br>recommended that the DMA does not<br>access any register that is part of the<br>System arbitration. The DMA, as a system<br>arbitration client should not be read or |

|-------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|       | arbitration chefit should not be read of                                                                                                                                                                                                                                                    |

|       | written by itself or by another DMA instantiation.                                                                                                                                                                                                                                          |

|       | instantiation.                                                                                                                                                                                                                                                                              |

The following sections discuss the various control interfaces required for DMA data transfers.

# 15.4.1 DMA ADDRESSING

The start addresses for the source read and destination write operations are set using the DMAxSSA <21:0> and DMAxDSA <15:0> registers, respectively.

When the DMA Message transfers are in progress, the DMAxSPTR <21:0> and DMAxDPTR <15:0> registers contain the current address pointers for each source read and destination write operation, these registers are modified after each transaction based on the Address mode selection bits.

The SMODE and DMODE bits in the DMAxCON1 control register determine the address modes of operation by controlling how the DMAxSPTR <21:0> and DMAxDPTR <15:0> bits are updated after every DMA data transaction combination (Figure 15-2).

Each address can be separately configured to:

- Remain unchanged

- Increment by 1

- Decrement by 1

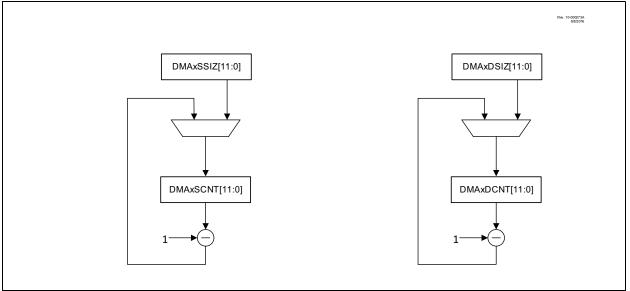

#### FIGURE 15-3: DMA COUNTERS BLOCK DIAGRAM

Table 15-2 has a few examples of configuring DMAMessage sizes.

| TABLE 15-2: | EXAMPLE | E MESSAGE SIZE | TABLE |      |

|-------------|---------|----------------|-------|------|

| Operat      | ion     | Example        | SCNT  | DONT |

| Operation                                | Example           | SCNT | DCNT | Comments                                                                                  |

|------------------------------------------|-------------------|------|------|-------------------------------------------------------------------------------------------|

| Read from single SFR<br>location to RAM  | U1RXB             | 1    | Ν    | N equals the number of bytes desired in the destination buffer. N >= 1.                   |

| Write to single SFR location<br>from RAM | U1TXB             | N    | 1    | N equals the number of bytes desired in the source buffer. N >= 1.                        |

|                                          | ADRES[H:L]        | 2    | 2*N  | N equals the number of ADC results to be stored in memory. N>= 1                          |

| Read from multiple SFR location          | TMR1[H:L]         | 2    | 2*N  | N equals the number of TMR1 Acquisition results to be stored in memory. N>= 1             |

|                                          | SMT1CPR[U:H:L]    | 3    | 3*N  | N equals the number of Capture Pulse Width measurements to be stored in memory. N>= 1     |

| Write to Multiple SFR regis-             | PWMDC[H:L]        | 2*N  | 2    | N equals the number of PWM duty cycle val-<br>ues to be loaded from a memory table. N>= 1 |

| ters                                     | All ADC registers | N*31 | 31   | Using the DMA to transfer a complete ADC context from RAM to the ADC registers.N>= 1      |

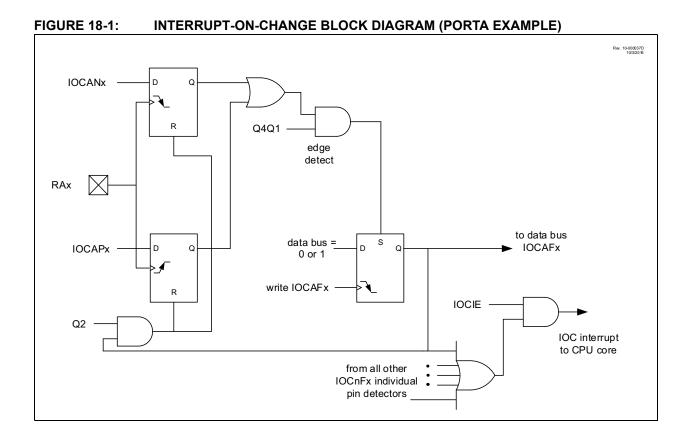

# 18.6 Register Definitions: Interrupt-on-Change Control

|                                         |         |                    |         |                                                       | 0                  |         |         |  |  |

|-----------------------------------------|---------|--------------------|---------|-------------------------------------------------------|--------------------|---------|---------|--|--|

| R/W-0/0                                 | R/W-0/0 | R/W-0/0            | R/W-0/0 | R/W-0/0                                               | R/W-0/0            | R/W-0/0 | R/W-0/0 |  |  |

| IOCxP7                                  | IOCxP6  | IOCxP5             | IOCxP4  | IOCxP3                                                | IOCxP2             | IOCxP1  | IOCxP0  |  |  |

| bit 7                                   |         |                    |         |                                                       |                    |         | bit 0   |  |  |

|                                         |         |                    |         |                                                       |                    |         |         |  |  |

| Legend:                                 |         |                    |         |                                                       |                    |         |         |  |  |

| R = Readable bit                        | t       | W = Writable bi    | it      | U = Unimpleme                                         | ented bit, read as | '0'     |         |  |  |

| u = Bit is unchanged x = Bit is unknown |         |                    |         | -n/n = Value at POR and BOR/Value at all other Resets |                    |         |         |  |  |

| '1' = Bit is set                        |         | '0' = Bit is clear | red     |                                                       |                    |         |         |  |  |

#### REGISTER 18-1: IOCxP: INTERRUPT-ON-CHANGE POSITIVE EDGE REGISTER EXAMPLE

bit 7-0

IOCxP<7:0>: Interrupt-on-Change Positive Edge Enable bits

1 = Interrupt-on-Change enabled on the IOCx pin for a positive-going edge. Associated Status bit and interrupt flag will be set upon detecting an edge.

0 = Interrupt-on-Change disabled for the associated pin.

#### REGISTER 18-2: IOCxN: INTERRUPT-ON-CHANGE NEGATIVE EDGE REGISTER EXAMPLE

| R/W-0/0 |

|---------|---------|---------|---------|---------|---------|---------|---------|

| IOCxN7  | IOCxN6  | IOCxN5  | IOCxN4  | IOCxN3  | IOCxN2  | IOCxN1  | IOCxN0  |

| bit 7   |         |         |         |         |         |         | bit 0   |

| Legend:              |                      |                                                       |

|----------------------|----------------------|-------------------------------------------------------|

| R = Readable bit     | W = Writable bit     | U = Unimplemented bit, read as '0'                    |

| u = Bit is unchanged | x = Bit is unknown   | -n/n = Value at POR and BOR/Value at all other Resets |

| '1' = Bit is set     | '0' = Bit is cleared |                                                       |

bit 7-0

**IOCxN<7:0>:** Interrupt-on-Change Negative Edge Enable bits

1 = Interrupt-on-Change enabled on the IOCx pin for a negative-going edge. Associated Status bit and interrupt flag will be set upon detecting an edge.

0 = Interrupt-on-Change disabled for the associated pin

#### REGISTER 18-3: IOCxF: INTERRUPT-ON-CHANGE FLAG REGISTER EXAMPLE

| R/W/HS-0/0 |

|------------|------------|------------|------------|------------|------------|------------|------------|

| IOCxF7     | IOCxF6     | IOCxF5     | IOCxF4     | IOCxF3     | IOCxF2     | IOCxF1     | IOCxF0     |

| bit 7      |            |            |            |            |            |            | bit 0      |

| Legend:              |                      |                                                       |

|----------------------|----------------------|-------------------------------------------------------|

| R = Readable bit     | W = Writable bit     | U = Unimplemented bit, read as '0'                    |

| u = Bit is unchanged | x = Bit is unknown   | -n/n = Value at POR and BOR/Value at all other Resets |

| '1' = Bit is set     | '0' = Bit is cleared | HS - Bit is set in hardware                           |

bit 7-0

IOCxF<7:0>: Interrupt-on-Change Flag bits

1 = A enabled change was detected on the associated pin. Set when IOCP[n] = 1 and a positive edge was detected on the IOCn pin, or when IOCN[n] = 1 and a negative edge was detected on the IOCn pin

0 = No change was detected, or the user cleared the detected change

| R/W/HC-0/0       | R/W-0/0                                | U-0                                                        | U-0           | R/W-0/0        | R/W-0/0         | R/W-0/0        | R/W-0/0      |  |  |

|------------------|----------------------------------------|------------------------------------------------------------|---------------|----------------|-----------------|----------------|--------------|--|--|

| GO               | REPEAT                                 |                                                            |               |                | MODE            | <3:0>          |              |  |  |

| bit 7            |                                        |                                                            |               |                |                 |                | bit (        |  |  |

| Legend:          |                                        |                                                            |               |                |                 |                |              |  |  |

| HC = Bit is clea | ared by hardv                          | vare                                                       |               | HS = Bit is se | t by hardware   |                |              |  |  |

| R = Readable     | bit                                    | W = Writable                                               | bit           | U = Unimplen   | nented bit, rea | d as '0'       |              |  |  |

| u = Bit is unch  | anged                                  | x = Bit is unkr                                            | iown          | -n/n = Value a | at POR and BC   | R/Value at all | other Resets |  |  |

| '1' = Bit is set |                                        | '0' = Bit is clea                                          | ared          | q = Value dep  | ends on condi   | tion           |              |  |  |

|                  |                                        |                                                            |               |                |                 |                |              |  |  |

| bit 7            | 1 = Increme                            | ta Acquisition bit<br>nting, acquiring<br>nting, acquiring | data is enabl |                |                 |                |              |  |  |

| bit 6            | 1 = Repeat I                           | MT Repeat Acqu<br>Data Acquisition<br>cquisition mode      | mode is ena   |                |                 |                |              |  |  |

| bit 5-4          | Unimpleme                              | nted: Read as '                                            | )'            |                |                 |                |              |  |  |

| bit 3-0          | MODE<3:0>                              | DE<3:0> SMT Operation Mode Select bits                     |               |                |                 |                |              |  |  |

|                  | 1111 <b>= Res</b>                      | erved                                                      |               |                |                 |                |              |  |  |

|                  | •                                      |                                                            |               |                |                 |                |              |  |  |

|                  | •                                      |                                                            |               |                |                 |                |              |  |  |

|                  | 1011 = Reserved                        |                                                            |               |                |                 |                |              |  |  |

|                  | 1010 = Windowed counter                |                                                            |               |                |                 |                |              |  |  |

|                  | 1001 = Gated counter<br>1000 = Counter |                                                            |               |                |                 |                |              |  |  |

|                  | 0111 = Capture                         |                                                            |               |                |                 |                |              |  |  |

|                  | 0110 = Time of flight                  |                                                            |               |                |                 |                |              |  |  |

|                  | 0101 = Gated windowed measure          |                                                            |               |                |                 |                |              |  |  |

|                  |                                        | dowed measure<br>and low time m                            | easurement    |                |                 |                |              |  |  |

|                  |                                        | od and Duty-Cyc                                            |               | n              |                 |                |              |  |  |

|                  | 0001 <b>= Gate</b>                     |                                                            | ·             |                |                 |                |              |  |  |

|                  | 0000 = Time                            |                                                            |               |                |                 |                |              |  |  |

#### REGISTER 25-2: SMT1CON1: SMT CONTROL REGISTER 1

| R/W-x/u          | R/W-x/u                                                                                                                  | R/W-x/u                                                                                                                          | R/W-x/u                                                                      | R/W-x/u        | R/W-x/u          | R/W-x/u          | R/W-x/u     |  |  |

|------------------|--------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------|----------------|------------------|------------------|-------------|--|--|

| G3D4T            | G3D4N                                                                                                                    | G3D3T                                                                                                                            | G3D3N                                                                        | G3D2T          | G3D2N            | G3D1T            | G3D1N       |  |  |

| bit 7            |                                                                                                                          |                                                                                                                                  |                                                                              |                |                  |                  | bit         |  |  |

| Legend:          |                                                                                                                          |                                                                                                                                  |                                                                              |                |                  |                  |             |  |  |

| R = Readable     | bit                                                                                                                      | W = Writable                                                                                                                     | bit                                                                          | U = Unimpler   | nented bit, read | l as '0'         |             |  |  |

| u = Bit is unch  | nanged                                                                                                                   | x = Bit is unkr                                                                                                                  | nown                                                                         | -n/n = Value a | at POR and BO    | R/Value at all c | ther Resets |  |  |

| '1' = Bit is set |                                                                                                                          | '0' = Bit is cle                                                                                                                 | ared                                                                         |                |                  |                  |             |  |  |

|                  |                                                                                                                          |                                                                                                                                  |                                                                              |                |                  |                  |             |  |  |

| bit 7            | G3D4T: Gate                                                                                                              | e 2 Data 4 True                                                                                                                  | (noninverted)                                                                | bit            |                  |                  |             |  |  |

|                  |                                                                                                                          | (true) is gated i                                                                                                                |                                                                              |                |                  |                  |             |  |  |

|                  |                                                                                                                          | (true) is not ga                                                                                                                 |                                                                              |                |                  |                  |             |  |  |

| bit 6            |                                                                                                                          | e 2 Data 4 Neg                                                                                                                   |                                                                              |                |                  |                  |             |  |  |

|                  |                                                                                                                          | · · · ·                                                                                                                          | nverted) is gated into CLCx Gate 2<br>nverted) is not gated into CLCx Gate 2 |                |                  |                  |             |  |  |

| L:1 C            |                                                                                                                          | . ,                                                                                                                              | •                                                                            |                |                  |                  |             |  |  |

| bit 5            |                                                                                                                          | 2 Data 3 True (noninverted) bit                                                                                                  |                                                                              |                |                  |                  |             |  |  |

|                  | <ul> <li>1 = CLCIN2 (true) is gated into CLCx Gate 2</li> <li>0 = CLCIN2 (true) is not gated into CLCx Gate 2</li> </ul> |                                                                                                                                  |                                                                              |                |                  |                  |             |  |  |

| bit 4            |                                                                                                                          | e 2 Data 3 Neg                                                                                                                   |                                                                              |                |                  |                  |             |  |  |

|                  |                                                                                                                          | •                                                                                                                                | (inverted) is gated into CLCx Gate 2                                         |                |                  |                  |             |  |  |

|                  |                                                                                                                          | (inverted) is no                                                                                                                 |                                                                              |                |                  |                  |             |  |  |

| bit 3            | G3D2T: Gate                                                                                                              | e 2 Data 2 True                                                                                                                  | (noninverted)                                                                | bit            |                  |                  |             |  |  |

|                  | 1 = CLCIN1 (true) is gated into CLCx Gate 2                                                                              |                                                                                                                                  |                                                                              |                |                  |                  |             |  |  |

|                  |                                                                                                                          | (true) is not ga                                                                                                                 |                                                                              |                |                  |                  |             |  |  |

| bit 2            |                                                                                                                          | G3D2N: Gate 2 Data 2 Negated (inverted) bit                                                                                      |                                                                              |                |                  |                  |             |  |  |

|                  |                                                                                                                          | <ul> <li>1 = CLCIN1 (inverted) is gated into CLCx Gate 2</li> <li>0 = CLCIN1 (inverted) is not gated into CLCx Gate 2</li> </ul> |                                                                              |                |                  |                  |             |  |  |

| bit 1            |                                                                                                                          | <b>G3D1T:</b> Gate 2 Data 1 True (noninverted) bit                                                                               |                                                                              |                |                  |                  |             |  |  |

|                  |                                                                                                                          | 1 = CLCIN0 (true) is gated into CLCx Gate 2                                                                                      |                                                                              |                |                  |                  |             |  |  |

|                  |                                                                                                                          | (true) is not ga                                                                                                                 |                                                                              |                |                  |                  |             |  |  |

| bit 0            | G3D1N: Gat                                                                                                               | e 2 Data 1 Neg                                                                                                                   | ated (inverted)                                                              | ) bit          |                  |                  |             |  |  |

|                  |                                                                                                                          | (inverted) is ga                                                                                                                 |                                                                              |                |                  |                  |             |  |  |

|                  | 0 = CLCIN0                                                                                                               | (inverted) is no                                                                                                                 | t gated into C                                                               | LCx Gate 2     |                  |                  |             |  |  |

# REGISTER 27-9: CLCxGLS2: GATE 2 LOGIC SELECT REGISTER

| R/W-0/0      | R/W-0/0                                                                                                              | R/W-0/0                           | R/W-0/0         | U-0             | R/W-1/1          | R/W-0/0  | R/W-0/0 |  |  |  |

|--------------|----------------------------------------------------------------------------------------------------------------------|-----------------------------------|-----------------|-----------------|------------------|----------|---------|--|--|--|

| SMP          | CKE                                                                                                                  | CKP                               | FST             |                 | SSP              | SDIP     | SDOP    |  |  |  |

| bit 7        |                                                                                                                      |                                   |                 |                 |                  |          | bit 0   |  |  |  |

| Legend:      |                                                                                                                      |                                   |                 |                 |                  |          |         |  |  |  |

| R = Readable | e bit                                                                                                                | W = Writable                      | bit             | U = Unimple     | mented bit, read | 1 as '0' |         |  |  |  |

|              |                                                                                                                      |                                   | <b>0</b>        |                 |                  |          |         |  |  |  |

| bit 7        |                                                                                                                      | out Sample Pha                    | ase Control bit |                 |                  |          |         |  |  |  |

|              | <u>Slave mode:</u><br>1 = Reserved                                                                                   | 4                                 |                 |                 |                  |          |         |  |  |  |

|              |                                                                                                                      |                                   | the middle of a | lata output tim |                  |          |         |  |  |  |

|              | <ul> <li>0 = SDI input is sampled in the middle of data output time</li> <li>Master mode:</li> </ul>                 |                                   |                 |                 |                  |          |         |  |  |  |

|              | <u>Master mode:</u><br>1 = SDI input is sampled at the end of data output time                                       |                                   |                 |                 |                  |          |         |  |  |  |

|              | 1 = SDI input is sampled at the end of data output time $0 = SDI input is sampled in the middle of data output time$ |                                   |                 |                 |                  |          |         |  |  |  |

| bit 6        | CKE: Clock Edge Select bit                                                                                           |                                   |                 |                 |                  |          |         |  |  |  |

|              | 1 = Output data changes on transition from active to idle clock state                                                |                                   |                 |                 |                  |          |         |  |  |  |

|              | 0 = Output data changes on transition from idle to active clock state                                                |                                   |                 |                 |                  |          |         |  |  |  |

| bit 5        | CKP: Clock Polarity Select bit                                                                                       |                                   |                 |                 |                  |          |         |  |  |  |

|              | 1 = Idle state for SCK is high level                                                                                 |                                   |                 |                 |                  |          |         |  |  |  |

|              | 0 = Idle state for SCK is low level                                                                                  |                                   |                 |                 |                  |          |         |  |  |  |

| bit 4        | FST: Fast Start Enable bit                                                                                           |                                   |                 |                 |                  |          |         |  |  |  |

|              | Slave mode:                                                                                                          |                                   |                 |                 |                  |          |         |  |  |  |

|              | This bit is ignored                                                                                                  |                                   |                 |                 |                  |          |         |  |  |  |

|              | Master mode:                                                                                                         |                                   |                 |                 |                  |          |         |  |  |  |

|              | 1 = Delay to first SCK may be less than $\frac{1}{2}$ baud period                                                    |                                   |                 |                 |                  |          |         |  |  |  |

|              | -                                                                                                                    | first SCK will be                 |                 | ud period       |                  |          |         |  |  |  |

| bit 3        | Unimplemented: Read as '0'                                                                                           |                                   |                 |                 |                  |          |         |  |  |  |

| bit 2        | SSP: SS Input/Output Polarity Control bit                                                                            |                                   |                 |                 |                  |          |         |  |  |  |

|              | 1 = SS is active-low                                                                                                 |                                   |                 |                 |                  |          |         |  |  |  |

| hit 1        | 0 = SS is active-high                                                                                                |                                   |                 |                 |                  |          |         |  |  |  |

| bit 1        | <b>SDIP</b> : SDI Input Polarity Control bit<br>1 = SDI input is active-low                                          |                                   |                 |                 |                  |          |         |  |  |  |

|              | -                                                                                                                    |                                   |                 |                 |                  |          |         |  |  |  |

|              | 0 = SDI input is active-high                                                                                         |                                   |                 |                 |                  |          |         |  |  |  |

| hit 0        | SDOP: SDI Output Polarity Control bit                                                                                |                                   |                 |                 |                  |          |         |  |  |  |

| bit 0        |                                                                                                                      | Dutput Polarity out is active-lov |                 |                 |                  |          |         |  |  |  |

# © 2017 Microchip Technology Inc.

## 33.3.2 BYTE FORMAT

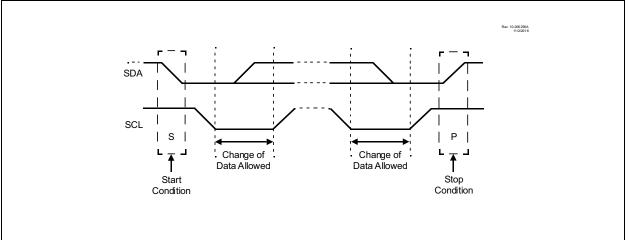

All communication in  $I^2C$  is done in 9-bit segments. A byte is sent from a master to a slave or vice-versa, followed by an Acknowledge bit sent by the receiver. After the 8th falling edge of the SCL line, the device transmitting data on the SDA line releases control of that pin to an input, and reads in an acknowledge value on the next clock pulse. The clock signal is provided by the master. Data is valid to change while the SCL line is low, and sampled on the rising edge of the clock. Changes on the SDA line while the SCL line is high define Start and Stop conditions on the bus which are explained further in the chapter.

#### 33.3.3 SDA AND SCL PINS

The user must configure these pins as open-drain inputs. This is done by clearing the appropriate TRIS bits and setting the appropriate and ODCON bits. The user may also select the input threshold, slew-rate and internal pull-up settings using the Rxyl2C control registers (Register 16-9).

#### 33.3.4 SDA HOLD TIME

The hold time of the SDA pin is selected by the SDAHT<1:0> bits of the I2CxCON2 register. Hold time is the time SDA is held valid after the falling edge of SCL. A longer hold time setting may help on buses with large capacitance.

#### 33.3.5 START CONDITION

The I<sup>2</sup>C specification defines a Start condition as a transition of SDA line from a high to a low state while SCL line is high. A Start condition is always generated by the master and signifies the transition of the bus from an Idle to an Active state. Figure 33-3 shows waveforms for Start conditions. Master hardware waits for the BFRE bit of I2CxSTAT0 to be set, before asserting a Start condition on the SCL and SDA lines. If two masters assert a start at the same time, a collision will occur during the addressing phase.

## 33.3.6 STOP CONDITION

A Stop condition is a transition of the SDA line from low to high while the SCL line is high. Figure 33-3 shows waveforms for Stop conditions.

| Note: | At least one SCL low time must appear    |  |  |  |  |  |  |  |

|-------|------------------------------------------|--|--|--|--|--|--|--|

|       | before a Stop is valid. Therefore if the |  |  |  |  |  |  |  |

|       | SDA line goes low then high again while  |  |  |  |  |  |  |  |

|       | the SCL line is high, only the Start     |  |  |  |  |  |  |  |

|       | condition is detected.                   |  |  |  |  |  |  |  |

## REGISTER 36-27: ADSTPTH: ADC THRESHOLD SETPOINT REGISTER HIGH

| R/W-0/0                           | R/W-0/0 | R/W-0/0                            | R/W-0/0                                     | R/W-0/0 | R/W-0/0          | R/W-0/0      | R/W-0/0 |

|-----------------------------------|---------|------------------------------------|---------------------------------------------|---------|------------------|--------------|---------|

|                                   |         |                                    | STPT                                        | <15:8>  |                  |              |         |

| bit 7                             |         |                                    |                                             |         |                  |              | bit 0   |

|                                   |         |                                    |                                             |         |                  |              |         |

| Legend:                           |         |                                    |                                             |         |                  |              |         |

| R = Readable bit W = Writable bit |         | U = Unimplemented bit, read as '0' |                                             |         |                  |              |         |

| u = Bit is unch                   | anged   | x = Bit is unkn                    | Inknown -n/n = Value at POR and BOR/Value a |         | R/Value at all o | other Resets |         |

bit 7-0 **STPT<15:8>**: ADC Threshold Setpoint MSB. Upper byte of ADC threshold setpoint, depending on ADCALC, may be used to determine ERR, see Register 36-29 for more details.

## REGISTER 36-28: ADSTPTL: ADC THRESHOLD SETPOINT REGISTER LOW

'0' = Bit is cleared

| R/W-0/0   | R/W-0/0 | R/W-0/0 | R/W-0/0 | R/W-0/0 | R/W-0/0 | R/W-0/0 | R/W-0/0 |  |

|-----------|---------|---------|---------|---------|---------|---------|---------|--|

| STPT<7:0> |         |         |         |         |         |         |         |  |

| bit 7     |         |         |         |         |         |         | bit 0   |  |

|           |         |         |         |         |         |         |         |  |

| Legend:              |                      |                                                       |

|----------------------|----------------------|-------------------------------------------------------|

| R = Readable bit     | W = Writable bit     | U = Unimplemented bit, read as '0'                    |

| u = Bit is unchanged | x = Bit is unknown   | -n/n = Value at POR and BOR/Value at all other Resets |

| '1' = Bit is set     | '0' = Bit is cleared |                                                       |

bit 7-0 **STPT<7:0>**: ADC Threshold Setpoint LSB. Lower byte of ADC threshold setpoint, depending on ADCALC, may be used to determine ERR, see Register 36-30 for more details.

'1' = Bit is set

| SUBFWB                                                                                     | Subtract                                                                                                                                                                                                                  | f from W wi                                                                                                                                                                               | th borrow                                                                                                                                         |  |

|--------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------|--|

| Syntax:                                                                                    | SUBFWB                                                                                                                                                                                                                    | f {,d {,a}}                                                                                                                                                                               |                                                                                                                                                   |  |

| Operands:                                                                                  | 0 ≤ f ≤ 255<br>d ∈ [0,1]<br>a ∈ [0,1]                                                                                                                                                                                     |                                                                                                                                                                                           |                                                                                                                                                   |  |

| Operation:                                                                                 |                                                                                                                                                                                                                           | $(\overline{C}) \rightarrow \text{dest}$                                                                                                                                                  |                                                                                                                                                   |  |

| Status Affected:                                                                           | N, OV, C, I                                                                                                                                                                                                               |                                                                                                                                                                                           |                                                                                                                                                   |  |

| Encoding:                                                                                  | 0101                                                                                                                                                                                                                      | 01da ffi                                                                                                                                                                                  | f ffff                                                                                                                                            |  |

| Description:                                                                               | (borrow) fr<br>method). It<br>in W. If 'd'<br>register 'f'<br>If 'a' is '0',<br>selected. I<br>to select th<br>If 'a' is '0' a<br>set is enat<br>operates in<br>Addressing<br>$f \le 95$ (5FH<br>41.2.3 "By<br>ented Inst | the Access Ba<br>f 'a' is '1', the l<br>ne GPR bank.<br>and the extend<br>oled, this instru-<br>n Indexed Liter<br>g mode where<br>n). See Section<br>te-Oriented an<br>ructions in Index | nplement<br>esult is stored<br>it is stored in<br>ank is<br>BSR is used<br>ed instruction<br>action<br>ral Offset<br>ever<br>n<br><b>Bit-Ori-</b> |  |

| Words:                                                                                     | Offset Mo                                                                                                                                                                                                                 | de" for details.                                                                                                                                                                          |                                                                                                                                                   |  |

| Cycles:                                                                                    | 1                                                                                                                                                                                                                         |                                                                                                                                                                                           |                                                                                                                                                   |  |

| Q Cycle Activity:                                                                          | •                                                                                                                                                                                                                         |                                                                                                                                                                                           |                                                                                                                                                   |  |

| Q1                                                                                         | Q2                                                                                                                                                                                                                        | Q3                                                                                                                                                                                        | Q4                                                                                                                                                |  |

| Decode                                                                                     | Read<br>register 'f'                                                                                                                                                                                                      | Read Process Write to                                                                                                                                                                     |                                                                                                                                                   |  |

| Example 1:<br>Before Instructi<br>REG<br>W<br>C<br>After Instruction<br>REG<br>W<br>C<br>Z | = 3<br>= 2<br>= 1<br>n<br>= FF<br>= 2<br>= 0<br>= 0                                                                                                                                                                       | REG, 1, 0                                                                                                                                                                                 |                                                                                                                                                   |  |

| N<br>Everynia 2:                                                                           |                                                                                                                                                                                                                           | sult is negative                                                                                                                                                                          | 9                                                                                                                                                 |  |

| Example 2:<br>Before Instructi                                                             |                                                                                                                                                                                                                           | REG, 0, 0                                                                                                                                                                                 |                                                                                                                                                   |  |