Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

E·XFI

| Product Status             | Active                                                                       |

|----------------------------|------------------------------------------------------------------------------|

| Core Processor             | PIC                                                                          |

| Core Size                  | 8-Bit                                                                        |

| Speed                      | 64MHz                                                                        |

| Connectivity               | I <sup>2</sup> C, LINbus, SPI, UART/USART                                    |

| Peripherals                | Brown-out Detect/Reset, DMA, HLVD, POR, PWM, WDT                             |

| Number of I/O              | 36                                                                           |

| Program Memory Size        | 128KB (64K x 16)                                                             |

| Program Memory Type        | FLASH                                                                        |

| EEPROM Size                | 1K x 8                                                                       |

| RAM Size                   | 8K x 8                                                                       |

| Voltage - Supply (Vcc/Vdd) | 1.8V ~ 3.6V                                                                  |

| Data Converters            | A/D 35x12b; D/A 1x5b                                                         |

| Oscillator Type            | Internal                                                                     |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                            |

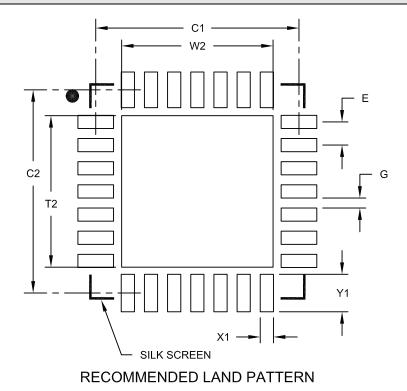

| Mounting Type              | Surface Mount                                                                |

| Package / Case             | 44-TQFP                                                                      |

| Supplier Device Package    | 44-TQFP (10x10)                                                              |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/pic18lf47k42t-i-pt |

|                            |                                                                              |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

| P        |

|----------|

| Ĭ        |

| Q        |

| 18       |

| 3(       |

|          |

| F        |

| Ň        |

| 6        |

| 12       |

| Z        |

| 4        |

| <u>с</u> |

| 14       |

| 9        |

| 4        |

| 71       |

| 3        |

| С<br>С   |

|          |

| 6        |

| X        |

| 2        |

| Σ        |

|          |

| Ň        |

| O/I  | 48-Pin TQFP | 48-Pin UQFN | ADC  | Voltage Reference | DAC | Comparators | Zero Cross Detect | I <sup>2</sup> C      | IdS                 | UART                | WSQ | Timers/SMT           | CCP and PWM         | CWG | CLC | NCO | Clock Reference (CLKR) | Interrupt-on-Change | Basic       |

|------|-------------|-------------|------|-------------------|-----|-------------|-------------------|-----------------------|---------------------|---------------------|-----|----------------------|---------------------|-----|-----|-----|------------------------|---------------------|-------------|

| RC2  | 40          | 40          | ANC2 | —                 | -   | -           | —                 | —                     | —                   | —                   | _   | T5CKI <sup>(1)</sup> | CCP1 <sup>(1)</sup> | _   | —   | —   | —                      | IOCC2               | -           |

| RC3  | 41          | 41          | ANC3 | _                 | -   | —           | —                 | SCL1 <sup>(3,4)</sup> | SCK1 <sup>(1)</sup> | —                   |     | T2IN <sup>(1)</sup>  | -                   | _   | _   | _   | —                      | IOCC3               | —           |

| RC4  | 46          | 46          | ANC4 | _                 | _   | -           | —                 | SDA1 <sup>(3,4)</sup> | SDI1 <sup>(1)</sup> | -                   | _   | -                    | —                   | _   | _   | _   | _                      | IOCC4               | _           |

| RC5  | 47          | 47          | ANC5 | —                 | _   | —           | —                 | _                     | —                   | —                   | _   | T4IN <sup>(1)</sup>  | —                   | _   | —   | —   | —                      | IOCC5               | _           |

| RC6  | 48          | 48          | ANC6 | _                 | _   | —           | _                 | —                     | _                   | CTS1 <sup>(1)</sup> | -   | -                    | —                   |     | _   | _   | _                      | IOCC6               | —           |

| RC7  | 1           | 1           | ANC7 | _                 | _   | —           | _                 | —                     | _                   | RX1 <sup>(1)</sup>  | -   | -                    | —                   | -   | _   | _   | _                      | IOCC7               | _           |

| RD0  | 42          | 42          | AND0 | _                 | _   | —           | —                 | (4)                   | _                   | _                   |     | _                    | —                   | l   | —   | _   | _                      | _                   | _           |

| RD1  | 43          | 43          | AND1 | -                 | -   | -           | —                 | (4)                   | —                   | _                   |     | -                    | _                   |     | —   | -   | —                      | —                   | _           |

| RD2  | 44          | 44          | AND2 | _                 | _   | —           | —                 | —                     | —                   | _                   |     | _                    | —                   | l   | —   | _   | _                      | _                   | _           |

| RD3  | 45          | 45          | AND3 | _                 | _   | _           | _                 | —                     | _                   | _                   |     | _                    | _                   |     | _   | _   | _                      | _                   | _           |

| RD4  | 2           | 2           | AND4 | _                 | _   | —           | —                 | —                     | —                   | —                   |     | _                    | —                   |     | _   | _   | —                      | _                   | —           |

| RD5  | 3           | 3           | AND5 | -                 | _   | —           | -                 | —                     | _                   | —                   |     | -                    | —                   |     | _   | _   | _                      | -                   | _           |

| RD6  | 4           | 4           | AND6 | _                 | _   | —           | _                 | —                     | _                   | _                   | -   | -                    | —                   |     | _   | _   | _                      | _                   | —           |

| RD7  | 5           | 5           | AND7 | _                 | _   | —           | _                 | —                     | _                   | —                   | -   | -                    | —                   | -   | _   | _   | _                      | _                   | _           |

| RE0  | 27          | 27          | ANE0 | _                 | _   | —           | _                 | —                     | _                   | _                   | -   | -                    | —                   |     | _   | _   | _                      | _                   | —           |

| RE1  | 28          | 28          | ANE1 | _                 | _   | —           | _                 | —                     | _                   | —                   | -   | -                    | —                   | -   | _   | _   | _                      | _                   | _           |

| RE2  | 29          | 29          | ANE2 | _                 | _   | —           | _                 | —                     | _                   | _                   | -   | -                    | —                   |     | _   | _   | _                      | _                   | —           |

| RE3  | 20          | 20          | —    | -                 | _   | -           | -                 | -                     | -                   | -                   | —   | -                    | -                   | -   | -   | —   | —                      | IOCE3               | MCLR<br>VPP |

| RF0  | 36          | 36          | ANF0 | _                 | _   | -           | _                 | -                     | _                   | _                   | _   | -                    | _                   | _   | _   | _   | _                      | _                   | —           |

| RF1  | 37          | 37          | ANF1 | _                 | —   | —           | _                 | _                     | _                   | _                   |     | _                    | _                   |     | —   | _   | _                      | _                   | _           |

| RF2  | 38          | 38          | ANF2 | _                 | _   | _           | _                 | _                     | _                   | _                   | _   | _                    | _                   | _   | _   | _   | _                      | _                   | _           |

| RF3  | 39          | 39          | ANF3 | _                 | —   | —           | _                 | —                     |                     | _                   | _   | _                    | _                   | -   | —   | _   | _                      | _                   | _           |

| RF4  | 12          | 12          | ANF4 | _                 | _   | _           | _                 | _                     | —                   | _                   | l   | _                    | _                   | l   | —   | _   | _                      | _                   | _           |

| RF5  | 13          | 13          | ANF5 | _                 | _   | _           | _                 | _                     | _                   | _                   | _   | _                    | _                   | _   | —   | _   | _                      | _                   | _           |

| RF6  | 14          | 14          | ANF6 | _                 | _   | _           | _                 | _                     |                     | _                   |     | _                    | _                   |     | _   | _   | _                      | _                   | _           |

| RF7  | 15          | 15          | ANF7 | —                 | _   | _           | -                 | _                     | —                   | _                   |     | _                    | _                   | l   | —   | _   | —                      | _                   | _           |

| Note | 1:          |             |      |                   |     |             |                   |                       |                     |                     |     | other PORTx pin      |                     |     |     |     |                        |                     |             |

48-PIN ALLOCATION TABLE FOR PIC18(L)F5XK42 (CONTINUED)

2: All output signals shown in this row are PPS remappable.

This is a bidirectional signal. For normal module operation, the firmware should map this signal to the same pin in both the PPS input and PPS output registers. 3:

These pins can be configured for I<sup>2</sup>C and SMB<sup>TM</sup> 3.0/2.0 logic levels; The SCLx/SDAx signals may be assigned to any of the RB1/RB2/RC3/RC4/RD0/RD1 pins. PPS assignments to the other pins (e.g., RA5) will operate, but input logic levels will be standard TTL/ST as selected by the INLVL register, instead of the I<sup>2</sup>C specific or SMBus input buffer thresholds. 4:

TABLE 3:

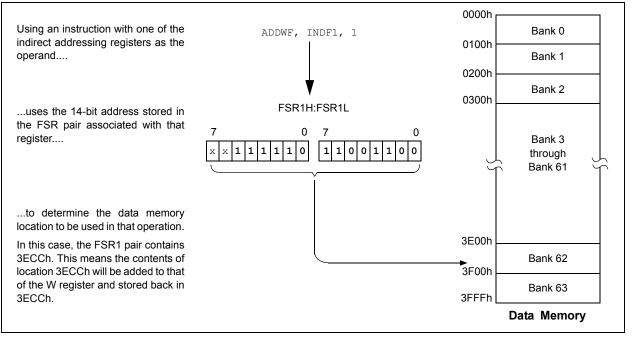

#### 4.7.3.2 FSR Registers, POSTINC, POSTDEC, PREINC and PLUSW

In addition to the INDF operand, each FSR register pair also has four additional indirect operands. Like INDF, these are "virtual" registers which cannot be directly read or written. Accessing these registers actually accesses the location to which the associated FSR register pair points, and also performs a specific action on the FSR value. They are:

- POSTDEC: accesses the location to which the FSR points, then automatically decrements the FSR by 1 afterwards

- POSTINC: accesses the location to which the FSR points, then automatically increments the FSR by 1 afterwards

- PREINC: automatically increments the FSR by 1, then uses the location to which the FSR points in the operation

- PLUSW: adds the signed value of the W register (range of -127 to 128) to that of the FSR and uses the location to which the result points in the operation.

#### FIGURE 4-6: INDIRECT ADDRESSING

In this context, accessing an INDF register uses the value in the associated FSR register without changing it. Similarly, accessing a PLUSW register gives the FSR value an offset by that in the W register; however, neither W nor the FSR is actually changed in the operation. Accessing the other virtual registers changes the value of the FSR register.

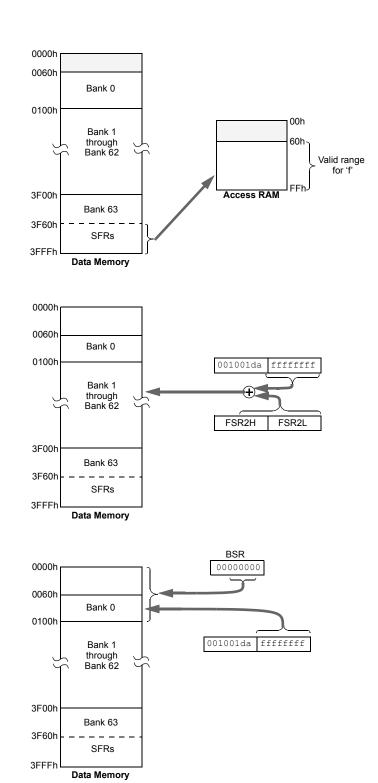

#### FIGURE 4-7: COMPARING ADDRESSING OPTIONS FOR BIT-ORIENTED AND BYTE-ORIENTED INSTRUCTIONS (EXTENDED INSTRUCTION SET ENABLED)

**EXAMPLE INSTRUCTION:** ADDWF, f, d, a (Opcode: 0010 01da ffff ffff)

#### When 'a' = 0 and $f \ge 60h$ :

The instruction executes in Direct Forced mode. 'f' is interpreted as a location in the Access RAM between 060h and 0FFh. This is the same as locations 3F60h to 3FFFh (Bank 63) of data memory.

Locations below 60h are not available in this Addressing mode.

#### When 'a' = 0 and $f \le 5Fh$ :

The instruction executes in Indexed Literal Offset mode. 'f' is interpreted as an offset to the address value in FSR2. The two are added together to obtain the address of the target register for the instruction. The address can be anywhere in the data memory space.

Note that in this mode, the correct syntax is now: ADDWF [k], d where 'k' is the same as 'f'.

#### When 'a' = 1 (all values of f):

The instruction executes in Direct mode (also known as Direct Long mode). 'f' is interpreted as a location in one of the 63 banks of the data memory space. The bank is designated by the Bank Select Register (BSR). The address can be in any implemented bank in the data memory space.

# PIC18(L)F26/27/45/46/47/55/56/57K42

| R-q/q           | R-q/q     | R-q/q                                                                                                                                 | R-q/q           | R-q/q             | R-q/q             | U-0            | R-q/q        |  |  |  |

|-----------------|-----------|---------------------------------------------------------------------------------------------------------------------------------------|-----------------|-------------------|-------------------|----------------|--------------|--|--|--|

| EXTOR           | HFOR      | MFOR                                                                                                                                  | LFOR            | SOR               | ADOR              | —              | PLLR         |  |  |  |

| bit 7           |           |                                                                                                                                       |                 |                   |                   |                | bit (        |  |  |  |

|                 |           |                                                                                                                                       |                 |                   |                   |                |              |  |  |  |

| Legend:         |           |                                                                                                                                       |                 |                   |                   |                |              |  |  |  |

| R = Readabl     |           | W = Writable                                                                                                                          |                 |                   | mented bit, read  |                |              |  |  |  |

| u = Bit is und  | changed   | x = Bit is unk                                                                                                                        | nown            | -n/n = Value      | at POR and BO     | R/Value at all | other Resets |  |  |  |

| '1' = Bit is se | et        | '0' = Bit is cle                                                                                                                      | ared            | q = Reset va      | alue is determine | ed by hardware | 9            |  |  |  |

|                 |           |                                                                                                                                       |                 |                   |                   |                |              |  |  |  |

| bit 7           |           | XTOSC (external<br>oscillator is ready                                                                                                |                 | eady bit          |                   |                |              |  |  |  |

|                 |           | oscillator is not er                                                                                                                  |                 | ot vet ready to l | be used           |                |              |  |  |  |

| bit 6           |           | INTOSC Oscillate                                                                                                                      |                 |                   |                   |                |              |  |  |  |

|                 |           | oscillator is ready                                                                                                                   | •               |                   |                   |                |              |  |  |  |

|                 | 0 = The c | scillator is not er                                                                                                                   | abled, or is no | ot yet ready to l | be used           |                |              |  |  |  |

| bit 5           |           | INTOSC Oscillat                                                                                                                       |                 |                   |                   |                |              |  |  |  |

|                 |           | scillator is ready                                                                                                                    |                 |                   |                   |                |              |  |  |  |

|                 |           | oscillator is not er                                                                                                                  |                 | ot yet ready to l | be used           |                |              |  |  |  |

| bit 4           |           | LFOR: LFINTOSC Oscillator Ready bit                                                                                                   |                 |                   |                   |                |              |  |  |  |

|                 |           | <ul> <li>1 = The oscillator is ready to be used</li> <li>0 = The oscillator is not enabled, or is not yet ready to be used</li> </ul> |                 |                   |                   |                |              |  |  |  |

| bit 3           |           | ondary (Timer1) (                                                                                                                     |                 |                   | Je useu           |                |              |  |  |  |

| JILO            |           | oscillator is ready                                                                                                                   |                 |                   |                   |                |              |  |  |  |

|                 |           | oscillator is not er                                                                                                                  |                 | ot yet ready to   | be used           |                |              |  |  |  |

| bit 2           | ADOR: AD  | C Oscillator Rea                                                                                                                      | dy bit          |                   |                   |                |              |  |  |  |

|                 |           | oscillator is ready                                                                                                                   |                 |                   |                   |                |              |  |  |  |

|                 | 0 = The o | oscillator is not er                                                                                                                  | nabled, or is n | ot yet ready to   | be used           |                |              |  |  |  |

| bit 1           | Unimplem  | ented: Read as                                                                                                                        | 0'              |                   |                   |                |              |  |  |  |

| bit 0           | PLLR: PLL | is Ready bit                                                                                                                          |                 |                   |                   |                |              |  |  |  |

|                 |           | PLL is ready to b                                                                                                                     | e used          |                   |                   |                |              |  |  |  |

|                 | 0 = The F |                                                                                                                                       |                 |                   |                   |                |              |  |  |  |

#### REGISTER 7-4: OSCSTAT: OSCILLATOR STATUS REGISTER 1

#### 11.1 Independent Clock Source

The WWDT can derive its time base from either the 31 kHz LFINTOSC or 31.25 kHz MFINTOSC internal oscillators, depending on the value of WDTE<1:0> Configuration bits.

If WDTE = 0b1x, then the clock source will be enabled depending on the WDTCCS<2:0> Configuration bits.

If WDTE = 0b01, the SEN bit should be set by software to enable WWDT, and the clock source is enabled by the CS bits in the WDTCON1 register.

Time intervals in this chapter are based on a minimum nominal interval of 1 ms. See Section 44.0 "Electrical Specifications" for LFINTOSC and MFINTOSC tolerances.

#### 11.2 WWDT Operating Modes

The Windowed Watchdog Timer module has four operating modes controlled by the WDTE<1:0> bits in Configuration Words. See Table 11-1.

#### 11.2.1 WWDT IS ALWAYS ON

When the WDTE bits of Configuration Words are set to '11', the WWDT is always on.

WWDT protection is active during Sleep.

#### 11.2.2 WWDT IS OFF IN SLEEP

When the WDTE bits of Configuration Words are set to '10', the WWDT is on, except in Sleep.

WWDT protection is not active during Sleep.

#### 11.2.3 WWDT CONTROLLED BY SOFTWARE

When the WDTE bits of Configuration Words are set to '01', the WWDT is controlled by the SEN bit of the WDTCON0 register.

WWDT protection is unchanged by Sleep. See Table 11-1 for more details.

| WDTE<1:0> | SEN | Device<br>Mode | WWDT<br>Mode |

|-----------|-----|----------------|--------------|

| 11        | Х   | Х              | Active       |

| 10        | 37  | Awake          | Active       |

| 10        | Х   | Sleep          | Disabled     |

| 0.1       | 1   | Х              | Active       |

| 01        | 0   | Х              | Disabled     |

| 0 0       | Х   | Х              | Disabled     |

#### TABLE 11-1: WWDT OPERATING MODES

#### 11.3 Time-out Period

If the WDTCPS<4:0> Configuration bits default to 0b11111, then the PS bits of the WDTCON0 register set the time-out period from 1 ms to 256 seconds (nominal). If any value other than the default value is assigned to WDTCPS<4:0> Configuration bits, then the timer period will be based on the WDTCPS<4:0> bits in the CONFIG3L register. After a Reset, the default time-out period is 2s.

#### 11.4 Watchdog Window

The Windowed Watchdog Timer has an optional Windowed mode that is controlled by the WDTCWS<2:0> Configuration bits and WINDOW<2:0> bits of the WDTCON1 register. In the Windowed mode, the CLRWDT instruction must occur within the allowed window of the WDT period. Any CLRWDT instruction that occurs outside of this window will trigger a window violation and will cause a WWDT Reset, similar to a WWDT time out. See Figure 11-2 for an example.

The window size is controlled by the WINDOW<2:0> Configuration bits, or the WINDOW<2:0> bits of WDTCON1, if WDTCWS<2:0> = 111.

The five Most Significant bits of the WDTTMR register are used to determine whether the window is open, as defined by the WINDOW<2:0> bits of the WDTCON1 register.

In the event of a <u>window</u> violation, a Reset will be generated and the WDTWV bit of the PCON0 register will be cleared. This bit is set by a POR or can be set in firmware.

#### 11.5 Clearing the WWDT

The WWDT is cleared when any of the following conditions occur:

- Any Reset

- Valid CLRWDT instruction is executed

- Device enters Sleep

- Exit Sleep by Interrupt

- WWDT is disabled

- Oscillator Start-up Timer (OST) is running

- Any write to the WDTCON0 or WDTCON1

registers

#### 11.5.1 CLRWDT CONSIDERATIONS (WINDOWED MODE)

When in Windowed mode, the WWDT must be armed before a CLRWDT instruction will clear the timer. This is performed by reading the WDTCON0 register. Executing a CLRWDT instruction without performing such an arming action will trigger a window violation regardless of whether the window is open or not.

See Table 11-2 for more information.

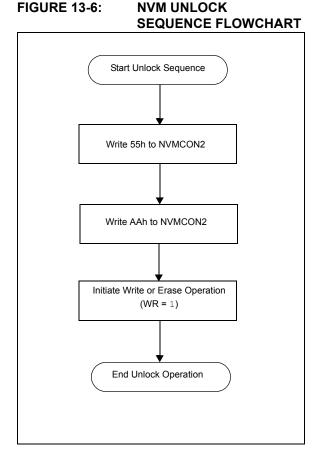

#### 13.1.4 NVM UNLOCK SEQUENCE

The unlock sequence is a mechanism that protects the NVM from unintended self-write programming or erasing. The sequence must be executed and completed without interruption to successfully complete any of the following operations:

- PFM Row Erase

- Write of PFM write latches to PFM memory

- Write of PFM write latches to User IDs

- Write to Data EEPROM Memory

- Write to Configuration Words

The unlock sequence consists of the following steps and must be completed in order:

- Write 55h to NVMCON2

- Write AAh to NMVCON2

- · Set the WR bit of NVMCON1

Once the WR bit is set, the processor will stall internal operations until the operation is complete and then resume with the next instruction.

Since the unlock sequence must not be interrupted, global interrupts should be disabled prior to the unlock sequence and re-enabled after the unlock sequence is completed.

|                |                              | -    |                                                       |

|----------------|------------------------------|------|-------------------------------------------------------|

| BCF            | INTCON0,GIE                  | ;    | Recommended so sequence is not interrupted            |

| BANKSEL        | NVMCON1                      |      |                                                       |

| BSF            | NVMCON1,WREN                 | ;    | Enable write/erase                                    |

| MOVLW          | 55h                          | ;    | Load 55h                                              |

| MOVWF          | NVMCON2                      | ;    | Step 1: Load 55h into NVMCON2                         |

| MOVLW          | AAh                          | ;    | Step 2: Load W with AAh                               |

| MOVWF          | NVMCON2                      | ;    | Step 3: Load AAh into NVMCON2                         |

| BSF            | INTCON1,WR                   | ;    | Step 4: Set WR bit to begin write/erase               |

| BSF            | INTCON0,GIE                  | ;    | Re-enable interrupts                                  |

| Note 1: Sequen | ce begins when NVMCON2 is wr | itte | en; steps 1-4 must occur in the cycle-accurate order  |

|                | 0                            |      | rupted by an interrupt or a debugger Halt, the action |

|                | take place.                  |      |                                                       |

2: Opcodes shown are illustrative; any instruction that has the indicated effect may be used.

#### EXAMPLE 13-2: NVM UNLOCK SEQUENCE

# PIC18(L)F26/27/45/46/47/55/56/57K42

#### REGISTER 15-9: DMAxSPTRU: DMAx SOURCE POINTER UPPER REGISTER

| U-0   | U-0 | R-0 | R-0 | R-0    | R-0    | R-0 | R-0   |

|-------|-----|-----|-----|--------|--------|-----|-------|

| —     | —   |     |     | SPTR<2 | 21:16> |     |       |

| bit 7 |     |     |     |        |        |     | bit 0 |

# Legend: W = Writable bit U = Unimplemented bit, read as '0' -n/n = Value at POR and BOR/Value at all other 1 = bit is set 0 = bit is cleared x = bit is unknown u = bit is unchanged u = bit is unchanged

bit 7-6 Unimplemented: Read as '0'

bit 5-0 SPTR<21:16>: Current Source Address Pointer

#### REGISTER 15-10: DMAxSSZL: DMAx SOURCE SIZE LOW REGISTER

| R/W-0/0 | R/W-0/0 | R/W-0/0 | R/W-0/0 | R/W-0/0  | R/W-0/0 | R/W-0/0 | R/W-0/0 |

|---------|---------|---------|---------|----------|---------|---------|---------|

|         |         |         | SSZ     | <7:0>    |         |         |         |

| bit 7   |         |         |         |          |         |         | bit 0   |

|         |         |         |         |          |         |         |         |

| Legend: |         |         |         |          |         |         |         |

|         | L 14    |         | 1       | 1.1. 1.1 |         | (0)     |         |

| R = Readable bit                                            | W = Writable bit | bit U = Unimplemented bit, read as '0' |                                            |  |  |  |

|-------------------------------------------------------------|------------------|----------------------------------------|--------------------------------------------|--|--|--|

| -n/n = Value at POR and<br>BOR/Value at all other<br>Resets | 1 = bit is set   |                                        | x = bit is unknown<br>u = bit is unchanged |  |  |  |

bit 7-0 SSZ<7:0>: Source Message Size bits

#### REGISTER 15-11: DMAxSSZH: DMAx SOURCE SIZE HIGH REGISTER

| U-0   | U-0 | U-0 | U-0 | R/W-0/0 | R/W-0/0 | R/W-0/0 | R/W-0/0 |

|-------|-----|-----|-----|---------|---------|---------|---------|

| —     | —   | —   | —   |         | SSZ<    | 11:8>   |         |

| bit 7 |     |     |     |         |         |         | bit 0   |

| Legend:                                                     |                  |                        |                                            |

|-------------------------------------------------------------|------------------|------------------------|--------------------------------------------|

| R = Readable bit                                            | W = Writable bit | U = Unimplemented bit, | read as '0'                                |

| -n/n = Value at POR and<br>BOR/Value at all other<br>Resets | 1 = bit is set   | 0 = bit is cleared     | x = bit is unknown<br>u = bit is unchanged |

bit 7-4 Unimplemented: Read as '0'

bit 3-0 SSZ<11:8>: Source Message Size bits

#### REGISTER 25-10: SMT1CPRL: SMT CAPTURED PERIOD REGISTER – LOW BYTE

| R-x/x                                                                        | R-x/x | R-x/x          | R-x/x | R-x/x        | R-x/x            | R-x/x            | R-x/x        |

|------------------------------------------------------------------------------|-------|----------------|-------|--------------|------------------|------------------|--------------|

|                                                                              |       |                | SMT10 | CPR<7:0>     |                  |                  |              |

| bit 7                                                                        |       |                |       |              |                  |                  | bit 0        |

|                                                                              |       |                |       |              |                  |                  |              |

| Legend:                                                                      |       |                |       |              |                  |                  |              |

| R = Readable b                                                               | oit   | W = Writable t | oit   | U = Unimpler | mented bit, read | d as '0'         |              |

| u = Bit is unchanged x = Bit is unknown -n/n = Value at POR and BOR/Value at |       |                |       |              |                  | R/Value at all o | other Resets |

bit 7-0 SMT1CPR<7:0>: Significant bits of the SMT Period Latch – Low Byte

'0' = Bit is cleared

#### REGISTER 25-11: SMT1CPRH: SMT CAPTURED PERIOD REGISTER - HIGH BYTE

| R-x/x            | R-x/x | R-x/x              | R-x/x | R-x/x          | R-x/x            | R-x/x            | R-x/x        |

|------------------|-------|--------------------|-------|----------------|------------------|------------------|--------------|

|                  |       |                    | SMT1C | PR<15:8>       |                  |                  |              |

| bit 7            |       |                    |       |                |                  |                  | bit 0        |

|                  |       |                    |       |                |                  |                  |              |

| Legend:          |       |                    |       |                |                  |                  |              |

| R = Readable b   | oit   | W = Writable bi    | it    | U = Unimpler   | nented bit, read | d as '0'         |              |

| u = Bit is uncha | anged | x = Bit is unkno   | wn    | -n/n = Value a | at POR and BC    | R/Value at all o | other Resets |

| '1' = Bit is set |       | '0' = Bit is clear | ed    |                |                  |                  |              |

bit 7-0 SMT1CPR<15:8>: Significant bits of the SMT Period Latch – High Byte

#### **REGISTER 25-12: SMT1CPRU: SMT CAPTURED PERIOD REGISTER – UPPER BYTE**

| R-x/x          | R-x/x | R-x/x | R-x/x | R-x/x | R-x/x | R-x/x | R-x/x |  |  |

|----------------|-------|-------|-------|-------|-------|-------|-------|--|--|

| SMT1CPR<23:16> |       |       |       |       |       |       |       |  |  |

| bit 7          |       |       |       |       |       |       |       |  |  |

| Legend:              |                      |                                                       |

|----------------------|----------------------|-------------------------------------------------------|

| R = Readable bit     | W = Writable bit     | U = Unimplemented bit, read as '0'                    |

| u = Bit is unchanged | x = Bit is unknown   | -n/n = Value at POR and BOR/Value at all other Resets |

| '1' = Bit is set     | '0' = Bit is cleared |                                                       |

bit 7-0 SMT1CPR<23:16>: Significant bits of the SMT Period Latch – Upper Byte

'1' = Bit is set

## 31.6 DALI Mode (UART1 only)

DALI is a protocol used for intelligent lighting control for building automation. The protocol consists of Control Devices and Control Gear. A Control Device is an application controller that sends out commands to the light fixtures. The light fixture itself is termed as a Control Gear. The communication is done using Manchester encoding, which is performed by the UART hardware.

Manchester encoding consists of the clock and data in a single bit stream. A high-to-low or a low-to-high transition always occurs in the middle of the bit period and is not guaranteed to occur at the bit period boundaries. When the consecutive bits in the bit stream are of the same value i.e. consecutive '1's or consecutive '0's, a transition occurs at the bit boundary. However, when the bit value changes, there is no transition at the bit boundary. According to the standard, a half-bit time is typically 416.7 µs long. A double half-bit time or a single bit is typically 833.3 µs.

The protocol is inherently half-duplex. Communication over the bus occurs in the form of forward and backward frames. Wait times between the frames are defined in the standard to prevent collision between the frames.

A Control Device transmission is termed as the forward frame. In the DALI 2.0 standard, a forward frame can be two or three bytes in length. The two-byte forward frame is used for communication between Control Device and Control Gear whereas the three-byte forward frame is used for communication between Control Devices on the bus. The first byte in the forward frame is the control byte and is followed by either one or two data bytes. The transaction begins when the Control Device starts a transmission. Unlike other protocols, each byte in the frame is transmitted MSB first. Typical frame timing is as shown in Figure 31-8.

During communication between two Control Devices, three bytes are required to be transmitted. In this case, the software must write the third byte to UxTXB as soon as UxTXIF goes True and before the output shifter becomes empty. This ensures that the three bytes of the forward frame are transmitted back-to-back without any interruption.

All Control Gear on the bus receive the forward frame. If the forward frame requires a reply to be sent, one of the Control Gear may respond with a single byte, called the backward frame. The 2.0 standard requires the Control Gear to begin transmission of the backward frame between 5.5 ms to 10.5 ms (~14 to 22 half-bit times) after reception of the forward frame. Once the backward frame is received by the Control Device, it is required to wait a minimum of 2.4 ms (~6 half-bit times). After this wait time, the Control Device is free to transmit another forward frame (see Figure 31-9). A start bit is used to indicate the start of the forward and backward frames. The receiver bit rate is determined by the BRG register. The low period of the start bit is measured and is used as the timing reference for all data bits in the forward and backward frames. The ABDOVF bit is set if the start bit low period causes the measurement counter to overflow. All the bits following the start bit are data bits. The bit stream terminates when no transition is detected in the middle of a bit period (see Figure 31-7).

Forward and backward frames are terminated by two Idle bit periods or Stop bits. Normally, these start in the first bit period of a byte. If both Stop bits are valid, the byte reception is terminated.

If either of the Stop bits is invalid, the frame is tagged as invalid by saving it as a null byte and setting the framing error in the receive FIFO.

A framing error also occurs when no transition is detected on the bus in the middle of a bit period when the byte reception is not complete. In such a scenario, the byte will be saved with the FERIF bit.

#### 31.6.1 CONTROL DEVICE

Control Device mode is configured with the following settings:

- MODE = 0b1000

- TXEN = 1

- RXEN = 1

- UxP1 = Forward frames are held for transmission with this number of half-bit periods after the completion of a forward or backward frame.

- UxP2 = Forward/backward frame threshold delimiter. Any reception that starts this number of half bit periods after the completion of a forward or backward frame is detected as forward frame and sets the PERIF flag of the corresponding received byte.

- UxBRGH:L = Value to achieve 1200 baud rate

- TXPOL = appropriate polarity for interface circuit

- STP = 0b10 for two Stop bits

- RxyPPS = TX pin selection code

- TX pin TRIS control = 0

- ON = 1.

A forward frame is initiated by writing the control byte to the UxTXB register. After sending the control byte, each data byte must be written to the UxTXB register as soon as UxTXIF goes true. It is necessary to perform every write after UxTXIF goes true, to ensure that the transmit buffer is ready to accept the byte. Each write must also occur before the TXMTIF bit goes true, to ensure that the bit stream of forward frame is generated without an interruption.

## 31.9 Stop Bits

The number of Stop bits is user selectable with the STP bits in the UxCON2 register. The STP bits affect all modes of operation.

Stop bits selections include:

- 1 transmit with receive verify on first

- 1.5 transmit with receive verify on first

- · 2 transmit with receive verify on both

- · 2 transmit with receive verify on first only

In all modes, except DALI, the transmitter is idle for the number of Stop bit periods between each consecutively transmitted word. In DALI, the Stop bits are generated after the last bit in the transmitted data stream.

The input is checked for the idle level in the middle of the first Stop bit, when receive verify on first is selected, as well as in the middle of the second Stop bit, when verify on both is selected. If any Stop bit verification indicates a non-idle level, the framing error FERIF bit is set for the received word.

#### 31.9.1 DELAYED UXRXIF

When operating in Half-Duplex mode, where the microcontroller needs to reverse the transceiver direction after a reception, it may be more convenient to hold off the UxRXIF interrupt until the end of the Stop bits to avoid line contention. The user selects when the UxRXIF interrupt occurs with the STPMD bit in the UxFIFO register. When STPMD is '1', the UxRXIF occurs at the end of the last Stop bit. When STPMD is '0', UxRXIF occurs when the received byte is stored in the receive FIFO. When STP < 1:0 > = 10, the store operation is performed in the middle of the second Stop bit, otherwise, it is performed in the middle of the first Stop bit. The FERIF and PERIF interrupts are not delayed with STPMD. Only UxRXIF is delayed when STPMD is set and should be the only indicator for reversing transceiver direction.

#### 31.10 Operation after FIFO overflow

The Receive Shift Register (RSR) can be configured to stop or continue running during a receive FIFO overflow condition. Stopped operation is the Legacy mode.

When the RSR continues to run during an overflow condition, the first word received after clearing the overflow will always be valid.

When the RSR is stopped during an overflow condition, synchronization with the Start bits is lost. Therefore, the first word received after the overflow is cleared may start in the middle of a word.

Operation during overflow is selected with the RUNOVF bit in the UxCON2 register. Setting the RUNOVF bit selects the run during overflow method.

#### 31.11 Receive and Transmit Buffers

The UART uses small buffer areas to transmit and receive data. These are sometimes referred to as FIFOs.

The receiver has a Receive Shift Register (RSR) and two buffer registers. The buffer at the top of the FIFO (earliest byte to enter the FIFO) is by retrieved by reading the UxRXB register.

The transmitter has one Transmit Shift Register (TSR) and one buffer register. Writes to UxTXB go to the transmit buffer then immediately to the TSR, if it is empty. When the TSR is not empty, writes to UxTXB are held then transferred to the TSR when it becomes available.

#### 31.11.1 FIFO STATUS

The UxFIFO register contains several status bits for determining the state of the receive and transmit buffers.

The RXBE bit indicates that the receive FIFO is empty. This bit is essentially the inverse of UxRXIF. The RXBF bit indicates that the receive FIFO is full.

The transmitter has only one buffer register so the status bits are essentially a copy and inverse of the UxTXIF bit. The TXBE bit indicates that the buffer is empty (same as UxTXIF) and the TXBF bit indicates that the buffer is full (UxTXIF inverse). A third transmitter status bit, TXWRE (transmit write error), is set whenever a UxTXB write is performed when the TXBF bit is set. This indicates that the write was unsuccessful.

#### 31.11.2 FIFO RESET

All modes support resetting the receive and transmit buffers.

The receive buffer is flushed and all unread data discarded when the RXBE bit in the UxFIFO register is written to '1'. The MOVWF instruction with the TXBE bit cleared should be used to avoid inadvertently clearing a byte pending in the TSR when UxTXB is empty.

Data written to UxTXB when TXEN is low will be held in the Transmit Shift Register (TSR) then sent when TXEN is set. The transmit buffer and inactive TSR are flushed by setting the TXBE bit in the UxFIFO register. Setting TXBE while a character is actively transmitting from the TSR will complete the transmission without being flushed.

Clearing the ON bit will discard all received data and transmit data pending in the TSR and UxTXB.

#### REGISTER 31-8: UxBRGL: UART BAUD RATE GENERATOR LOW REGISTER

| R/W-0/0          | R/W-0/0 | R/W-0/0           | R/W-0/0 | R/W-0/0        | R/W-0/0          | R/W-0/0          | R/W-0/0     |

|------------------|---------|-------------------|---------|----------------|------------------|------------------|-------------|

|                  |         |                   | BRG     | <7:0>          |                  |                  |             |

| bit 7            |         |                   |         |                |                  |                  | bit 0       |

|                  |         |                   |         |                |                  |                  |             |

| Legend:          |         |                   |         |                |                  |                  |             |

| R = Readable     | bit     | W = Writable      | bit     | U = Unimpler   | nented bit, read | as '0'           |             |

| u = Bit is uncha | anged   | x = Bit is unkr   | iown    | -n/n = Value a | at POR and BO    | R/Value at all c | ther Resets |

| '1' = Bit is set |         | '0' = Bit is clea | ared    |                |                  |                  |             |

bit 7-0 BRG<7:0>: Least Significant Byte of Baud Rate Generator

#### REGISTER 31-9: UxBRGH: UART BAUD RATE GENERATOR HIGH REGISTER

| R/W-0/0 |

|---------|---------|---------|---------|---------|---------|---------|---------|

|         |         |         | BRG<    | <15:8>  |         |         |         |

| bit 7   |         |         |         |         |         |         | bit 0   |

| Legend:              |                      |                                                       |

|----------------------|----------------------|-------------------------------------------------------|

| R = Readable bit     | W = Writable bit     | U = Unimplemented bit, read as '0'                    |

| u = Bit is unchanged | x = Bit is unknown   | -n/n = Value at POR and BOR/Value at all other Resets |

| '1' = Bit is set     | '0' = Bit is cleared |                                                       |

bit 7-0 BRG<15:8>: Most Significant Byte of Baud Rate Generator

**Note 1:** The UxBRG registers should only be written when ON = 0.

**2:** Maximum BRG value when MODE = 100x and BRGS = 1 is 0x7FFE.

**3:** Maximum BRG value when MODE = '100x' and BRGS = 0 is 0x1FFE.

# PIC18(L)F26/27/45/46/47/55/56/57K42

| U-0             | U-0        | U-0               | U-0          | U-0            | U-0              | U-0              | R/W-0/0      |

|-----------------|------------|-------------------|--------------|----------------|------------------|------------------|--------------|

|                 | _          | _                 |              | _              | —                | _                | P2<8>        |

| bit 7           |            |                   |              |                |                  |                  | bit (        |

|                 |            |                   |              |                |                  |                  |              |

| Legend:         |            |                   |              |                |                  |                  |              |

| R = Readabl     | le bit     | W = Writable      | bit          | U = Unimpler   | mented bit, read | as '0'           |              |

| u = Bit is und  | changed    | x = Bit is unkr   | nown         | -n/n = Value a | at POR and BOF   | R/Value at all o | other Resets |

| '1' = Bit is se | et         | '0' = Bit is clea | ared         |                |                  |                  |              |

|                 |            |                   |              |                |                  |                  |              |

| bit 7-6         | Unimplemer | ted: Read as '    | 0'           |                |                  |                  |              |

| hit 0           | P2<8> Most | Significant Rit   | of Parameter | <b>c</b>       |                  |                  |              |

#### REGISTER 31-14: UxP2H: UART PARAMETER 2 HIGH REGISTER

| bit 7-6 | Unimplemented: Read as '0'                                                                           |

|---------|------------------------------------------------------------------------------------------------------|

| bit 0   | P2<8>: Most Significant Bit of Parameter 2                                                           |

|         | DMX mode:                                                                                            |

|         | Most Significant bit of first address of receive block                                               |

|         | DALI mode:                                                                                           |

|         | Most Significant bit of number of half-bit periods of idle time in Forward Frame detection threshold |

|         | Other modes:                                                                                         |

|         | Not used                                                                                             |

#### REGISTER 31-15: UxP2L: UART PARAMETER 2 LOW REGISTER

| R/W-0/0 |

|---------|---------|---------|---------|---------|---------|---------|---------|

|         |         |         | P2<     | 7:0>    |         |         |         |

| bit 7   |         |         |         |         |         |         |         |

|         |         |         |         |         |         |         |         |

| Legend:              |                      |                                                       |

|----------------------|----------------------|-------------------------------------------------------|

| R = Readable bit     | W = Writable bit     | U = Unimplemented bit, read as '0'                    |

| u = Bit is unchanged | x = Bit is unknown   | -n/n = Value at POR and BOR/Value at all other Resets |

| '1' = Bit is set     | '0' = Bit is cleared |                                                       |

bit 7-0

P2<7:0>: Least Significant Bits of Parameter 2

DMX mode:

Least Significant Byte of first address of receive block

LIN Slave mode:

Number of data bytes to transmit

DALI mode:

Least Significant Byte of number of half-bit periods of idle time in Forward Frame detection threshold

Asynchronous Address mode:

Receiver address

Other modes:

Not used

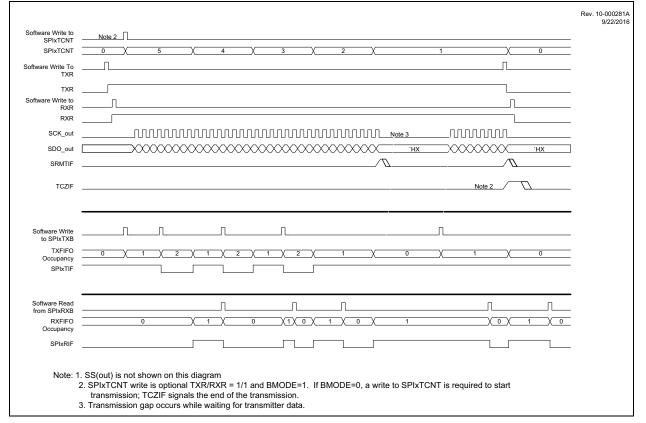

#### 32.5.1 FULL DUPLEX MODE

When both TXR and RXR are set, the SPI master is in Full Duplex mode. In this mode, data transfer triggering is affected by the BMODE bit of SPIxCON0.

When BMODE = 1, data transfers will occur whenever both the RXFIFO is not full and there is data present in the TXFIFO. In practice, as long as the RXFIFO is not full, data will be transmitted/received as soon as the SPIxTxB register is written to, matching functionality of SPI (MSSP) modules on older 8-bit Microchip devices. The SPIxTCNT will decrement with each transfer. However, when SPIxTCNT is zero the next transfer is not inhibited and the corresponding SPIxTCNT decrement will cause the count to roll over to the maximum value. Figure 32-3 shows an example of a communication using this mode.

When BMODE = 0, the transfer counter (SPIxTCNTH/ SPIxTCNTL) must also be written to before transfers will occur, and transfers will cease when the transfer counter reaches '0'. For example, if SPIxTXB is written twice and then SPIxTCTL is written with '3' then the transfer will start with the SPIxTCTL write. The two bytes in the TXFIFO will be sent after which the transfer will suspend until the third and last byte is written to SPIxTXB.

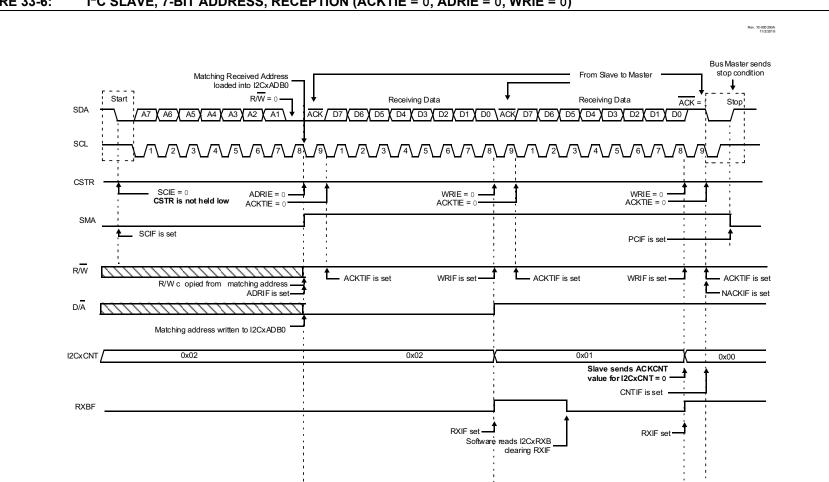

#### FIGURE 33-6: I<sup>2</sup>C SLAVE, 7-BIT ADDRESS, RECEPTION (ACKTIE = 0, ADRIE = 0, WRIE = 0)

PIC18(L)F26/27/45/46/47/55/56/57K42

| Mnemonic,  |                    | Description                             | Qualas | 16-  | Bit Inst | ruction | Word | Status          | Notoo |

|------------|--------------------|-----------------------------------------|--------|------|----------|---------|------|-----------------|-------|

| Opera      | nds                | Description                             | Cycles | MSb  |          |         | LSb  | Affected        | Notes |

| LITERAL IN | ISTRUC             | TIONS                                   |        |      |          |         |      |                 |       |

| ADDLW      | k                  | Add literal and WREG                    | 1      | 0000 | 1111     | kkkk    | kkkk | C, DC, Z, OV, N |       |

| ANDLW      | k                  | AND literal with WREG                   | 1      | 0000 | 1011     | kkkk    | kkkk | Z, N            |       |

| IORLW      | k                  | Inclusive OR literal with WREG          | 1      | 0000 | 1001     | kkkk    | kkkk | Z, N            |       |

| LFSR       | f <sub>n</sub> , k | Load FSR(f <sub>n</sub> ) with a 14-bit | 2      | 1110 | 1110     | 00ff    | kkkk | None            |       |

|            |                    | literal (k)                             |        | 1111 | 00kk     | kkkk    | kkkk |                 |       |

| ADDFSR     | f <sub>n</sub> , k | Add FSR(f <sub>n</sub> ) with (k)       | 1      | 1110 | 1000     | ffkk    | kkkk | None            |       |

| SUBFSR     | f <sub>n</sub> , k | Subtract (k) from FSR(f <sub>n</sub> )  | 1      | 1110 | 1001     | ffkk    | kkkk | None            |       |

| MOVLB      | k                  | Move literal to BSR<5:0>                | 1      | 0000 | 0001     | 00kk    | kkkk | None            |       |

| MOVLW      | k                  | Move literal to WREG                    | 1      | 0000 | 1110     | kkkk    | kkkk | None            |       |

| MULLW      | k                  | Multiply literal with WREG              | 1      | 0000 | 1101     | kkkk    | kkkk | None            |       |

| RETLW      | k                  | Return with literal in WREG             | 2      | 0000 | 1100     | kkkk    | kkkk | None            |       |

| SUBLW      | k                  | Subtract WREG from literal              | 1      | 0000 | 1000     | kkkk    | kkkk | C, DC, Z, OV, N |       |

| XORLW      | k                  | Exclusive OR literal with WREG          | 1      | 0000 | 1010     | kkkk    | kkkk | Z, N            |       |

| DATA MEM   | IORY – P           | ROGRAM MEMORY INSTRUCTIONS              |        |      |          |         |      |                 |       |

| TBLRD*     |                    | Table Read                              | 2 - 5  | 0000 | 0000     | 0000    | 1000 | None            |       |

| TBLRD*+    |                    | Table Read with post-increment          |        | 0000 | 0000     | 0000    | 1001 | None            |       |

| TBLRD*-    |                    | Table Read with post-decrement          |        | 0000 | 0000     | 0000    | 1010 | None            |       |

| TBLRD+*    |                    | Table Read with pre-increment           |        | 0000 | 0000     | 0000    | 1011 | None            |       |

| TBLWT*     |                    | Table Write                             | 2 - 5  | 0000 | 0000     | 0000    | 1100 | None            |       |

| TBLWT*+    |                    | Table Write with post-increment         |        | 0000 | 0000     | 0000    | 1101 | None            |       |

| TBLWT*-    |                    | Table Write with post-decrement         |        | 0000 | 0000     | 0000    | 1110 | None            |       |

| TBLWT+*    |                    | Table Write with pre-increment          |        | 0000 | 0000     | 0000    | 1111 | None            |       |

#### TABLE 41-2: INSTRUCTION SET (CONTINUED)

Note 1: If Program Counter (PC) is modified or a conditional test is true, the instruction requires an additional cycle. The extra cycle is executed as a NOP.

2: Some instructions are multi word instructions. The second/third words of these instructions will be decoded as a NOP, unless the first word of the instruction retrieves the information embedded in these 16-bits. This ensures that all program memory locations have a valid instruction.

3:  $f_s$  and  $f_d$  do not cover the full memory range. 2 MSBs of bank selection are forced to 'b00 to limit the range of these instructions to lower 4k addressing space.

# PIC18(L)F26/27/45/46/47/55/56/57K42

| XORWF                                                  | Exclusive                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | OR W wit              | n f |                       |  |  |  |  |

|--------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------|-----|-----------------------|--|--|--|--|

| Syntax:                                                | XORWF                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | f {,d {,a}}           |     |                       |  |  |  |  |

| Operands:                                              | $\begin{array}{l} 0 \leq f \leq 255 \\ d  \in  [0,1] \\ a  \in  [0,1] \end{array}$                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | d ∈ [0,1]             |     |                       |  |  |  |  |

| Operation:                                             | (W) .XOR. (                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | f) $\rightarrow$ dest |     |                       |  |  |  |  |

| Status Affected:                                       | N, Z                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |                       |     |                       |  |  |  |  |

| Encoding:                                              | 0001                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | 10da f                | ff  | ffff                  |  |  |  |  |

| Description:                                           | Exclusive OR the contents of W with<br>register 'f'. If 'd' is '0', the result is stored<br>in W. If 'd' is '1', the result is stored back<br>in the register 'f' (default).<br>If 'a' is '0', the Access Bank is selected.<br>If 'a' is '1', the BSR is used to select the<br>GPR bank.<br>If 'a' is '0' and the extended instruction<br>set is enabled, this instruction operates<br>in Indexed Literal Offset Addressing<br>mode whenever $f \le 95$ (5Fh). See Sec-<br>tion 41.2.3 "Byte-Oriented and Bit-<br>Oriented Instructions in Indexed Lit-<br>eral Offset Mode" for details. |                       |     |                       |  |  |  |  |

| Words:                                                 | 1                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |                       |     |                       |  |  |  |  |

| Cycles:                                                | 1                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |                       |     |                       |  |  |  |  |

| Q Cycle Activity:                                      |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |                       |     |                       |  |  |  |  |

| Q1                                                     | Q2                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | Q3                    |     | Q4                    |  |  |  |  |

| Decode                                                 | Read<br>register 'f'                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | Process<br>Data       | -   | Vrite to<br>stination |  |  |  |  |

| Example:                                               | XORWF F                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | REG, 1, 0             |     |                       |  |  |  |  |

| Before Instruct<br>REG<br>W<br>After Instructio<br>REG | = AFh<br>= B5h<br>n<br>= 1Ah                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |                       |     |                       |  |  |  |  |

| W                                                      | = B5h                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |                       |     |                       |  |  |  |  |

© 2017 Microchip Technology Inc.

#### 43.6 MPLAB X SIM Software Simulator

The MPLAB X SIM Software Simulator allows code development in a PC-hosted environment by simulating the PIC MCUs and dsPIC DSCs on an instruction level. On any given instruction, the data areas can be examined or modified and stimuli can be applied from a comprehensive stimulus controller. Registers can be logged to files for further run-time analysis. The trace buffer and logic analyzer display extend the power of the simulator to record and track program execution, actions on I/O, most peripherals and internal registers.

The MPLAB X SIM Software Simulator fully supports symbolic debugging using the MPLAB XC Compilers, and the MPASM and MPLAB Assemblers. The software simulator offers the flexibility to develop and debug code outside of the hardware laboratory environment, making it an excellent, economical software development tool.

## 43.7 MPLAB REAL ICE In-Circuit Emulator System

The MPLAB REAL ICE In-Circuit Emulator System is Microchip's next generation high-speed emulator for Microchip Flash DSC and MCU devices. It debugs and programs all 8, 16 and 32-bit MCU, and DSC devices with the easy-to-use, powerful graphical user interface of the MPLAB X IDE.

The emulator is connected to the design engineer's PC using a high-speed USB 2.0 interface and is connected to the target with either a connector compatible with in-circuit debugger systems (RJ-11) or with the new high-speed, noise tolerant, Low-Voltage Differential Signal (LVDS) interconnection (CAT5).

The emulator is field upgradable through future firmware downloads in MPLAB X IDE. MPLAB REAL ICE offers significant advantages over competitive emulators including full-speed emulation, run-time variable watches, trace analysis, complex breakpoints, logic probes, a ruggedized probe interface and long (up to three meters) interconnection cables.

#### 43.8 MPLAB ICD 3 In-Circuit Debugger System

The MPLAB ICD 3 In-Circuit Debugger System is Microchip's most cost-effective, high-speed hardware debugger/programmer for Microchip Flash DSC and MCU devices. It debugs and programs PIC Flash microcontrollers and dsPIC DSCs with the powerful, yet easy-to-use graphical user interface of the MPLAB IDE.

The MPLAB ICD 3 In-Circuit Debugger probe is connected to the design engineer's PC using a highspeed USB 2.0 interface and is connected to the target with a connector compatible with the MPLAB ICD 2 or MPLAB REAL ICE systems (RJ-11). MPLAB ICD 3 supports all MPLAB ICD 2 headers.

## 43.9 PICkit 3 In-Circuit Debugger/ Programmer

The MPLAB PICkit 3 allows debugging and programming of PIC and dsPIC Flash microcontrollers at a most affordable price point using the powerful graphical user interface of the MPLAB IDE. The MPLAB PICkit 3 is connected to the design engineer's PC using a full-speed USB interface and can be connected to the target via a Microchip debug (RJ-11) connector (compatible with MPLAB ICD 3 and MPLAB REAL ICE). The connector uses two device I/O pins and the Reset line to implement in-circuit debugging and In-Circuit Serial Programming<sup>™</sup> (ICSP<sup>™</sup>).

## 43.10 MPLAB PM3 Device Programmer

The MPLAB PM3 Device Programmer is a universal, CE compliant device programmer with programmable voltage verification at VDDMIN and VDDMAX for maximum reliability. It features a large LCD display (128 x 64) for menus and error messages, and a modular, detachable socket assembly to support various package types. The ICSP cable assembly is included as a standard item. In Stand-Alone mode, the MPLAB PM3 Device Programmer can read, verify and program PIC devices without a PC connection. It can also set code protection in this mode. The MPLAB PM3 connects to the host PC via an RS-232 or USB cable. The MPLAB PM3 has high-speed communications and optimized algorithms for quick programming of large memory devices, and incorporates an MMC card for file storage and data applications.

#### TABLE 44-3: SUPPLY CURRENT (IDD)<sup>(1,2,4)</sup>

| PIC18LF27/47/57K42<br>PIC18F27/47/57K42 |                                    |                                               |                     | Standard Operating Conditions (unless otherwise stated) |                              |      |      |                |  |

|-----------------------------------------|------------------------------------|-----------------------------------------------|---------------------|---------------------------------------------------------|------------------------------|------|------|----------------|--|

|                                         |                                    |                                               |                     |                                                         |                              |      |      |                |  |

| No.                                     | Symbol                             | тур.т                                         | o.† Max.            | Units                                                   | VDD                          | Note |      |                |  |

| D100                                    | IDD <sub>XT4</sub>                 | XT = 4 MHz                                    | _                   | 625                                                     | 1200                         | μΑ   | 3.0V | $\wedge$       |  |

| D100                                    | IDD <sub>XT4</sub>                 | XT = 4 MHz                                    |                     | 825                                                     | 1400                         | μΑ   | 3.0V |                |  |

| D100A                                   | IDD <sub>XT4</sub>                 | XT = 4 MHz                                    |                     | 425                                                     | —                            | μΑ   | 3.0V | PMD's all 1's  |  |

| D100A                                   | IDD <sub>XT4</sub>                 | XT = 4 MHz                                    |                     | 665                                                     | _                            | μΑ   | 3.0V | PMD's all 1's  |  |

| D101                                    | IDD <sub>HFO16</sub>               | HFINTOSC = 16 MHz                             |                     | 2.9                                                     | 5                            | mA   | 3.0V |                |  |

| D101                                    | IDD <sub>HFO16</sub>               | HFINTOSC = 16 MHz                             |                     | 3                                                       | 5.1                          | mA   | 3.0V |                |  |

| D101A                                   | IDD <sub>HFO16</sub>               | HFINTOSC = 16 MHz                             |                     | 2.0                                                     | —                            | mA   | 3.0V | P/MD's)all 1's |  |

| D101A                                   | IDD <sub>HFO16</sub>               | HFINTOSC = 16 MHz                             |                     | 2.1                                                     | _                            | mA   | 3.0V | RMD's all 1's  |  |