Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

### Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

E·XF

| Details                    |                                                                              |

|----------------------------|------------------------------------------------------------------------------|

| Product Status             | Active                                                                       |

| Core Processor             | PIC                                                                          |

| Core Size                  | 8-Bit                                                                        |

| Speed                      | 64MHz                                                                        |

| Connectivity               | I <sup>2</sup> C, LINbus, SPI, UART/USART                                    |

| Peripherals                | Brown-out Detect/Reset, LVD, POR, PWM, WDT                                   |

| Number of I/O              | 44                                                                           |

| Program Memory Size        | 64KB (32K x 16)                                                              |

| Program Memory Type        | FLASH                                                                        |

| EEPROM Size                | 1K x 8                                                                       |

| RAM Size                   | 4K x 8                                                                       |

| Voltage - Supply (Vcc/Vdd) | 1.8V ~ 3.6V                                                                  |

| Data Converters            | A/D 43x12b; D/A 1x5b                                                         |

| Oscillator Type            | Internal                                                                     |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                            |

| Mounting Type              | Surface Mount                                                                |

| Package / Case             | 48-TQFP Exposed Pad                                                          |

| Supplier Device Package    | 48-TQFP-EP (7x7)                                                             |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/pic18lf56k42t-i-pt |

|                            |                                                                              |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

|                      | PC<21:0>                                                                                                                                                                                                                                                                                                 | PC<21:0>                                       | PC<21:0>                                       | 7                    |  |

|----------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------|------------------------------------------------|----------------------|--|

|                      | <b>†</b> 1                                                                                                                                                                                                                                                                                               | <b>\$</b>                                      | ¢ I                                            | _                    |  |

| Note 1               | Stack (31 levels)                                                                                                                                                                                                                                                                                        | Stack (31 levels)                              | Stack (31 levels)                              | Note 1               |  |

|                      | •                                                                                                                                                                                                                                                                                                        |                                                | ★                                              | _                    |  |

| 00 0000h             | Reset Vector                                                                                                                                                                                                                                                                                             | Reset Vector                                   | Reset Vector                                   | 00 0000h             |  |

| •••                  | •••                                                                                                                                                                                                                                                                                                      | •••                                            | •••                                            | •••                  |  |

| 00 0008h             | Interrupt Vector High <sup>(2)</sup>                                                                                                                                                                                                                                                                     | Interrupt Vector High <sup>(2)</sup>           | Interrupt Vector High <sup>(2)</sup>           | 00 0008h             |  |

| •••                  | •••                                                                                                                                                                                                                                                                                                      | • • •                                          | • • •                                          | •••                  |  |

| 00 0018h             | Interrupt Vector Low <sup>(2)</sup>                                                                                                                                                                                                                                                                      | Interrupt Vector Low <sup>(2)</sup>            | Interrupt Vector Low <sup>(2)</sup>            | 00 0018h             |  |

| 00 001Ah<br>•        | Program Flash Memory (16<br>KW) <sup>(3)</sup>                                                                                                                                                                                                                                                           |                                                |                                                | 00 001Ah<br>•        |  |

| 00 7FFFh             | (WV) <sup></sup>                                                                                                                                                                                                                                                                                         | Program Flash Memory (32<br>KW) <sup>(3)</sup> |                                                | 00 7FFF              |  |

| 00 8000h             |                                                                                                                                                                                                                                                                                                          | KVV). /                                        | Program Flash Memory (64<br>KW) <sup>(3)</sup> | 00 8000h<br>•        |  |

| 00 FFFFh             |                                                                                                                                                                                                                                                                                                          |                                                |                                                | 00 FFFF              |  |

| 01 0000h             | Reserved <sup>(4)</sup>                                                                                                                                                                                                                                                                                  |                                                |                                                | 01 0000h             |  |

| 01 FFFFh             |                                                                                                                                                                                                                                                                                                          | Reserved <sup>(4)</sup>                        |                                                | 01 FFFF              |  |

| 02 0000h<br>1F FFFFh |                                                                                                                                                                                                                                                                                                          |                                                | Reserved <sup>(4)</sup>                        | 02 0000h<br>1F FFFFh |  |

| 20 0000              |                                                                                                                                                                                                                                                                                                          | User IDs (8 Words) <sup>(5)</sup>              |                                                | 20 0000h             |  |

| 20 000Fh             |                                                                                                                                                                                                                                                                                                          |                                                |                                                | 20 000Fh             |  |

| 20 0010h             |                                                                                                                                                                                                                                                                                                          | Reserved                                       |                                                | 20 0010h             |  |

| 2F FFFFh             |                                                                                                                                                                                                                                                                                                          | Reserved                                       |                                                | 2F FFFF              |  |

| 30 0000h             |                                                                                                                                                                                                                                                                                                          | Configuration Words (5 Words) <sup>(5</sup>    | 5)                                             | 30 0000h             |  |

| 30 0009h             |                                                                                                                                                                                                                                                                                                          | Conliguration words (5 words)                  | ,                                              | 30 0009h             |  |

| 30 000Ah             |                                                                                                                                                                                                                                                                                                          | Deserved                                       |                                                | 30 000Ah             |  |

| 30 FFFFh             |                                                                                                                                                                                                                                                                                                          | Reserved                                       |                                                | 30 FFFF              |  |

| 31 0000h             |                                                                                                                                                                                                                                                                                                          |                                                |                                                | 31 0000h             |  |

| 31 00FFh             | Data EEPROM (256 Bytes)                                                                                                                                                                                                                                                                                  |                                                |                                                | •••<br>31 00FFh      |  |

| 31 0100h             |                                                                                                                                                                                                                                                                                                          | Data EEPRO                                     | M (1024Bytes)                                  | 31 0100h             |  |

| •••                  |                                                                                                                                                                                                                                                                                                          |                                                |                                                | •••                  |  |

| 31 03FFh             | Reserved                                                                                                                                                                                                                                                                                                 |                                                | 31 03FFh                                       |                      |  |

| 31 0400h             |                                                                                                                                                                                                                                                                                                          | Rese                                           | erved                                          | 31 0400h             |  |

| 3E FFFFh             |                                                                                                                                                                                                                                                                                                          |                                                |                                                | 3E FFFF              |  |

| 3F 0000h             |                                                                                                                                                                                                                                                                                                          | Device Information Area <sup>(5),(7)</sup>     |                                                | 3F 0000h             |  |

| 3F 003Fh             |                                                                                                                                                                                                                                                                                                          |                                                |                                                | 3F 003Fh             |  |

| 3F0040h              |                                                                                                                                                                                                                                                                                                          | Reserved                                       |                                                | 3F0040h              |  |

| 3F FEFFh             |                                                                                                                                                                                                                                                                                                          |                                                |                                                | 3F FEFFI             |  |

| 3F FF00h             | Device C                                                                                                                                                                                                                                                                                                 | onfiguration Information (5 Word               | (5),(6),(7)                                    | 3F FF00h             |  |

| 3F FF09h             |                                                                                                                                                                                                                                                                                                          | <b>.</b> .                                     |                                                | 3F FF09h             |  |

| 3F FF0Ah             |                                                                                                                                                                                                                                                                                                          | Reserved                                       |                                                | 3F FF0Ah             |  |

| 3F FFFBh             | Reserved                                                                                                                                                                                                                                                                                                 |                                                |                                                |                      |  |

| 3F FFFCh             | Revision ID (1 Word) <sup>(5),(6),(7)</sup>                                                                                                                                                                                                                                                              |                                                |                                                |                      |  |

| 3F FFFDh             |                                                                                                                                                                                                                                                                                                          | Revision ID (1 word)                           |                                                | 3F FFFD              |  |

| 3F FFFEh             |                                                                                                                                                                                                                                                                                                          |                                                |                                                | 3F FFFEI             |  |

| 3F FFFFh             |                                                                                                                                                                                                                                                                                                          | Device ID (1 Word) <sup>(5),(6),(7)</sup>      |                                                | 3F FFFF              |  |

| Note 1:<br>2:<br>3:  | The stack is a separate SRAM panel, apart from all user memory panels.<br>00 0008h location is used as the reset default for the IVTBASE register, the vector table can be relo<br>memory by programming the IVTBASE register.<br>Storage area Flash is implemented as the last 128 Words of user Flash. |                                                |                                                |                      |  |

### TABLE 4-1: PROGRAM AND DATA EEPROM MEMORY MAP

Operations on the FSRs with POSTDEC, POSTINC and PREINC affect the entire register pair; that is, rollovers of the FSRnL register from FFh to 00h carry over to the FSRnH register. On the other hand, results of these operations do not change the value of any flags in the STATUS register (e.g., Z, N, OV, etc.).

The PLUSW register can be used to implement a form of indexed addressing in the data memory space. By manipulating the value in the W register, users can reach addresses that are fixed offsets from pointer addresses. In some applications, this can be used to implement some powerful program control structure, such as software stacks, inside of data memory.

## 4.7.3.3 Operations by FSRs on FSRs

Indirect addressing operations that target other FSRs or virtual registers represent special cases. For example, using an FSR to point to one of the virtual registers will not result in successful operations. As a specific case, assume that FSR0H:FSR0L contains 3FE7h, the address of INDF1. Attempts to read the value of the INDF1 using INDF0 as an operand will return 00h. Attempts to write to INDF1 using INDF0 as the operand will result in a NOP.

On the other hand, using the virtual registers to write to an FSR pair may not occur as planned. In these cases, the value will be written to the FSR pair but without any incrementing or decrementing. Thus, writing to either the INDF2 or POSTDEC2 register will write the same value to the FSR2H:FSR2L.

Since the FSRs are physical registers mapped in the SFR space, they can be manipulated through all direct operations. Users should proceed cautiously when working on these registers, particularly if their code uses indirect addressing.

Similarly, operations by indirect addressing are generally permitted on all other SFRs. Users should exercise the appropriate caution that they do not inadvertently change settings that might affect the operation of the device.

## 4.8 Data Memory and the Extended Instruction Set

Enabling the PIC18 extended instruction set (XINST Configuration bit = 1) significantly changes certain aspects of data memory and its addressing. Specifically, the use of the Access Bank for many of the core PIC18 instructions is different; this is due to the introduction of a new addressing mode for the data memory space.

What does not change is just as important. The size of the data memory space is unchanged, as well as its linear addressing. The SFR map remains the same. Core PIC18 instructions can still operate in both Direct and Indirect Addressing mode; inherent and literal instructions do not change at all. Indirect addressing with FSR0 and FSR1 also remain unchanged.

## 4.8.1 INDEXED ADDRESSING WITH LITERAL OFFSET

Enabling the PIC18 extended instruction set changes the behavior of indirect addressing using the FSR2 register pair within Access RAM. Under the proper conditions, instructions that use the Access Bank – that is, most bit-oriented and byte-oriented instructions – can invoke a form of indexed addressing using an offset specified in the instruction. This special addressing mode is known as Indexed Addressing with Literal Offset, or Indexed Literal Offset mode.

When using the extended instruction set, this addressing mode requires the following:

- The use of the Access Bank is forced ('a' = 0) and

- The file address argument is less than or equal to 5Fh.

Under these conditions, the file address of the instruction is not interpreted as the lower byte of an address (used with the BSR in direct addressing), or as an 8-bit address in the Access Bank. Instead, the value is interpreted as an offset value to an Address Pointer, specified by FSR2. The offset and the contents of FSR2 are added to obtain the target address of the operation.

## 4.8.2 INSTRUCTIONS AFFECTED BY INDEXED LITERAL OFFSET MODE

Any of the core PIC18 instructions that can use direct addressing are potentially affected by the Indexed Literal Offset Addressing mode. This includes all byte-oriented and bit-oriented instructions, or almost one-half of the standard PIC18 instruction set. Instructions that only use Inherent or Literal Addressing modes are unaffected.

Additionally, byte-oriented and bit-oriented instructions are not affected if they do not use the Access Bank (Access RAM bit is '1'), or include a file address of 60h or above. Instructions meeting these criteria will continue to execute as before. A comparison of the different possible addressing modes when the extended instruction set is enabled is shown in Figure 4-7.

Those who desire to use byte-oriented or bit-oriented instructions in the Indexed Literal Offset mode should note the changes to assembler syntax for this mode. This is described in more detail in **Section 41.2.1 "Extended Instruction Syntax**".

## 11.0 WINDOWED WATCHDOG TIMER (WWDT)

The Watchdog Timer (WDT) is a system timer that generates a Reset if the firmware does not issue a CLRWDT instruction within the time-out period. The Watchdog Timer is typically used to recover the system from unexpected events. The Windowed Watchdog Timer (WWDT) differs in that CLRWDT instructions are only accepted when they are performed within a specific window during the time-out period.

The WWDT has the following features:

- Selectable clock source

- Multiple operating modes

- WWDT is always On

- WWDT is off when in Sleep

- WWDT is controlled by software

- WWDT is always Off

- Configurable time-out period is from 1 ms to 256s (nominal)

- Configurable window size from 12.5% to 100% of the time-out period

- Multiple Reset conditions

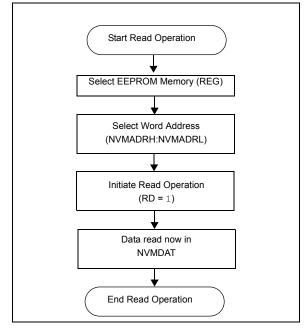

## 13.3.3 READING THE DATA EEPROM MEMORY

To read a data memory location, the user must write the address to the NVMADRL and NVMADRH register pair, clear REG<1:0> control bit in NVMCON1 register to access Data EEPROM locations and then set control bit, RD. The data is available on the very next instruction cycle; therefore, the NVMDAT register can be read by the next instruction. NVMDAT will hold this value until another read operation, or until it is written to by the user (during a write operation).

The basic process is shown in Example 13-5.

### FIGURE 13-11: DATA EEPROM READ FLOWCHART

## 13.3.4 WRITING TO THE DATA EEPROM MEMORY

To write an EEPROM data location, the address must first be written to the NVMADRL and NVMADRH register pair and the data written to the NVMDAT register. The sequence in Example 13-6 must be followed to initiate the write cycle.

The write will not begin if NVM Unlock sequence, described in **Section 13.1.4 "NVM Unlock Sequence"**, is not exactly followed for each byte. It is strongly recommended that interrupts be disabled during this code segment.

Additionally, the WREN bit in NVMCON1 must be set to enable writes. This mechanism prevents accidental writes to data EEPROM due to unexpected code execution (i.e., runaway programs). The WREN bit should be kept clear at all times, except when updating the EEPROM. The WREN bit is not cleared by hardware.

After a write sequence has been initiated, NVMCON1, NVMADRL, NVMADRH and NVMDAT cannot be modified. The WR bit will be inhibited from being set unless the WREN bit is set. Both WR and WREN cannot be set with the same instruction.

After a write sequence has been initiated, clearing the WREN bit will not affect this write cycle. A single Data EEPROM word is written and the operation includes an implicit erase cycle for that word (it is not necessary to set FREE). CPU execution continues in parallel and at the completion of the write cycle, the WR bit is cleared in hardware and the NVM Interrupt Flag bit (NVMIF) is set. The user can either enable this interrupt or poll this bit. NVMIF must be cleared by software.

| R/W-1/1          | R/W-1/1 | R/W-1/1           | R/W-1/1 | R/W-1/1                 | R/W-1/1          | R/W-1/1          | R/W-1/1      |

|------------------|---------|-------------------|---------|-------------------------|------------------|------------------|--------------|

|                  |         |                   | HADR<   | 15:8> <sup>(1, 2)</sup> |                  |                  |              |

| bit 7            |         |                   |         |                         |                  |                  | bit 0        |

|                  |         |                   |         |                         |                  |                  |              |

| Legend:          |         |                   |         |                         |                  |                  |              |

| R = Readable     | bit     | W = Writable      | bit     | U = Unimpler            | mented bit, read | 1 as '0'         |              |

| u = Bit is unch  | anged   | x = Bit is unkr   | nown    | -n/n = Value a          | at POR and BO    | R/Value at all c | other Resets |

| '1' = Bit is set |         | '0' = Bit is clea | ared    |                         |                  |                  |              |

#### REGISTER 14-16: SCANHADRH: SCAN HIGH ADDRESS HIGH BYTE REGISTER

bit 7-0 HADR<15:8>: Scan End Address bits<sup>(1, 2)</sup>

Most Significant bits of the address at the end of the designated scan

**Note 1:** Registers SCANHADRU/H/L form a 22-bit value, but are not guarded for atomic or asynchronous access; registers should only be read or written while SGO = 0 (SCANCON0 register).

2: While SGO = 1 (SCANCON0 register), writing to this register is ignored.

## REGISTER 14-17: SCANHADRL: SCAN HIGH ADDRESS LOW BYTE REGISTER

| R/W-1/1           | R/W-1/1 | R/W-1/1             | R/W-1/1 | R/W-1/1             | R/W-1/1            | R/W-1/1             | R/W-1/1 |

|-------------------|---------|---------------------|---------|---------------------|--------------------|---------------------|---------|

|                   |         |                     | HADR<   | :7:0> <b>(1, 2)</b> |                    |                     |         |

| bit 7             |         |                     |         |                     |                    |                     | bit 0   |

|                   |         |                     |         |                     |                    |                     |         |

| Legend:           |         |                     |         |                     |                    |                     |         |

| R = Readable bi   | t       | W = Writable bit    | t       | U = Unimplem        | ented bit, read as | ʻ0'                 |         |

| u = Bit is unchar | nged    | x = Bit is unkno    | wn      | -n/n = Value at     | POR and BOR/       | alue at all other / | Resets  |

| '1' = Bit is set  |         | '0' = Bit is cleare | ed      |                     |                    |                     |         |

bit 7-0 HADR<7:0>: Scan End Address bits<sup>(1, 2)</sup>

Least Significant bits of the address at the end of the designated scan

- **Note 1:** Registers SCANHADRU/H/L form a 22-bit value, but are not guarded for atomic or asynchronous access; registers should only be read or written while SGO = 0 (SCANCON0 register).

- 2: While SGO = 1 (SCANCON0 register), writing to this register is ignored.

## REGISTER 21-4: TxGATE: TIMERx GATE ISM REGISTER

| U-0   | U-0 | U-0 | R/W-0/u | R/W-0/u | R/W-0/u  | R/W-0/u | R/W-0/u |

|-------|-----|-----|---------|---------|----------|---------|---------|

| _     | _   | _   |         |         | GSS<4:0> |         |         |

| bit 7 |     |     | •       |         |          |         | bit 0   |

|       |     |     |         |         |          |         |         |

| Legend:           |                  |                             |               |  |

|-------------------|------------------|-----------------------------|---------------|--|

| R = Readable bit  | W = Writable bit | U = Unimplemented bit, read | as '0'        |  |

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared        | u = unchanged |  |

### bit 7-5 Unimplemented: Read as '0'

bit 4-0 **GSS<4:0>:** Timerx Gate Source Selection bits

| GSS         | Timer1                 | Timer3                 | Timer5                 |  |

|-------------|------------------------|------------------------|------------------------|--|

| 655         | Gate Source            | Gate Source            | Gate Source            |  |

| 11111-11011 | Reserved               | Reserved               | Reserved               |  |

| 11010       | CLC4_out               | CLC4_out               | CLC4_out               |  |

| 11001       | CLC3_out               | CLC3_out               | CLC3_out               |  |

| 11000       | CLC2_out               | CLC2_out               | CLC2_out               |  |

| 10111       | CLC1_out               | CLC1_out               | CLC1_out               |  |

| 10110       | ZCDOUT                 | ZCDOUT                 | ZCDOUT                 |  |

| 10101       | CMP2OUT                | CMP2OUT                | CMP2OUT                |  |

| 10100       | CMP1OUT                | CMP1OUT                | CMP1OUT                |  |

| 10011       | NC010UT                | NCO10UT                | NCO10UT                |  |

| 10010-10001 | Reserved               | Reserved               | Reserved               |  |

| 10000       | PWM8OUT                | PWM8OUT                | PWM8OUT                |  |

| 01111       | PWM7OUT                | PWM7OUT                | PWM7OUT                |  |

| 01110       | PWM6OUT                | PWM6OUT                | PWM6OUT                |  |

| 01101       | PWM5OUT                | PWM5OUT                | PWM5OUT                |  |

| 01100       | CCP4OUT                | CCP4OUT                | CCP4OUT                |  |

| 01011       | CCP3OUT                | CCP3OUT                | CCP3OUT                |  |

| 01010       | CCP2OUT                | CCP2OUT                | CCP2OUT                |  |

| 01001       | CCP10UT                | CCP10UT                | CCP1OUT                |  |

| 01000       | SMT1_match             | SMT1_match             | SMT1_match             |  |

| 00111       | TMR6OUT (postscaled)   | TMR6OUT (postscaled)   | TMR6OUT (postscaled)   |  |

| 00110       | TMR5 overflow          | TMR5 overflow          | Reserved               |  |

| 00101       | TMR4OUT (postscaled)   | TMR4OUT (postscaled)   | TMR4OUT (postscaled)   |  |

| 00100       | TMR3 overflow          | Reserved               | TMR3 overflow          |  |

| 00011       | TMR2OUT (postscaled)   | TMR2OUT (postscaled)   | TMR2OUT (postscaled)   |  |

| 00010       | Reserved               | TMR1 overflow          | TMR1 overflow          |  |

| 00001       | TMR0 overflow          | TMR0 overflow          | TMR0 overflow          |  |

| 00000       | Pin selected by T1GPPS | Pin selected by T3GPPS | Pin selected by T5GPPS |  |

## 25.6.10 GATED COUNTER MODE

This mode counts pulses on the SMT1\_signal input, gated by the SMT1WIN input. It begins incrementing the timer upon seeing a rising edge of the SMT1WIN input and updates the SMT1CPW register upon a falling edge on the SMT1WIN input. See Figure 25-19 and Figure 25-20.

| U-0                                   | U-0        | U-0             | U-0  | U-0                            | R/W-0/0         | R/W-0/0          | R/W-0/0      |  |

|---------------------------------------|------------|-----------------|------|--------------------------------|-----------------|------------------|--------------|--|

| —                                     | _          | —               | —    | —                              |                 | CSEL<2:0>        |              |  |

| bit 7                                 |            | •               |      |                                |                 |                  | bit 0        |  |

|                                       |            |                 |      |                                |                 |                  |              |  |

| Legend:                               |            |                 |      |                                |                 |                  |              |  |

| R = Readable                          | bit        | W = Writable    | bit  | U = Unimpler                   | nented bit, rea | d as '0'         |              |  |

| u = Bit is unch                       | anged      | x = Bit is unkr | nown | -n/n = Value a                 | at POR and BC   | R/Value at all o | other Resets |  |

| '1' = Bit is set '0' = Bit is cleared |            |                 | ared | q = Value depends on condition |                 |                  |              |  |

|                                       |            |                 |      |                                |                 |                  |              |  |

| bit 7-3                               | Unimplemer | nted: Read as ' | 0'   |                                |                 |                  |              |  |

### REGISTER 25-4: SMT1CLK: SMT CLOCK SELECTION REGISTER

| bit 2-0 | CSEL<2:0>: SMT Clock Selection bits |

|---------|-------------------------------------|

|         | 111 = Reference Clock Output        |

|         | 110 = SOSC                          |

|         | 101 = MFINTOSC/16 (32 kHz)          |

|         | 100 = MFINTOSC (500 kHz)            |

011 = LFINTOSC

010 = HFINTOSC 16 MHz

001 = Fosc

000 = Fosc/4

| GURE 28-2                                    | 2: FDC OUTPUT MODE OPERATION DIAGRAM                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

|----------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| NCOx<br>Clock<br>Source                      |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

| NCOx<br>Increment<br>Value                   | 4000h<br>4000h<br>4000h<br>4000h<br>4000h<br>4000h<br>4000h<br>4000h<br>4000h<br>4000h<br>4000h<br>4000h<br>4000h<br>4000h<br>4000h<br>4000h<br>4000h<br>4000h<br>4000h<br>4000h<br>4000h<br>4000h<br>4000h<br>4000h<br>4000h<br>4000h<br>4000h<br>4000h<br>4000h<br>4000h<br>4000h<br>4000h<br>4000h<br>4000h<br>4000h<br>4000h<br>4000h<br>4000h<br>4000h<br>4000h<br>4000h<br>4000h<br>4000h<br>4000h<br>4000h<br>4000h<br>4000h<br>4000h<br>4000h<br>4000h<br>4000h<br>4000h<br>4000h<br>4000h<br>4000h<br>4000h<br>4000h<br>4000h<br>4000h<br>4000h<br>4000h<br>4000h<br>4000h<br>4000h<br>4000h<br>4000h<br>4000h<br>4000h<br>4000h<br>4000h<br>4000h<br>4000h<br>4000h<br>4000h<br>4000h<br>4000h<br>4000h<br>4000h<br>4000h<br>4000h<br>4000h<br>4000h<br>4000h<br>4000h<br>4000h<br>4000h<br>4000h<br>4000h<br>4000h<br>4000h<br>4000h<br>4000h<br>4000h<br>4000h<br>4000h<br>4000h<br>4000h<br>4000h<br>4000h<br>4000h<br>4000h<br>4000h<br>4000h<br>4000h<br>4000h<br>4000h<br>4000h<br>4000h<br>4000h<br>4000h<br>4000h<br>4000h<br>4000h<br>4000h<br>4000h<br>4000h<br>4000h<br>4000h<br>4000h<br>4000h<br>4000h<br>4000h<br>4000h<br>4000h<br>4000h<br>4000h<br>4000h<br>4000h<br>4000h<br>4000h<br>4000h<br>4000h<br>4000h<br>4000h<br>4000h<br>4000h<br>4000h<br>4000h<br>4000h<br>4000h<br>4000h<br>4000h<br>4000h<br>4000h<br>4000h<br>4000h<br>4000h<br>4000h<br>4000h<br>4000h<br>4000h<br>4000h<br>4000h<br>4000h<br>4000h<br>4000h<br>4000h<br>4000h<br>4000h<br>4000h<br>4000h<br>4000h<br>4000h<br>4000h<br>4000h<br>4000h<br>4000h<br>4000h<br>4000h<br>4000h<br>4000h<br>4000h<br>4000h<br>4000h<br>4000h<br>4000h<br>4000h<br>4000h<br>4000h<br>4000h<br>4000h<br>4000h<br>4000h<br>4000h<br>4000h<br>4000h<br>4000h<br>4000h<br>4000h<br>4000h<br>4000h<br>4000h<br>4000h<br>4000h<br>4000h<br>4000h<br>4000h<br>4000h<br>4000h<br>4000h<br>4000h<br>4000h<br>4000h<br>4000h<br>4000h<br>4000h<br>4000h<br>4000h<br>4000h<br>4000h<br>4000h<br>4000h<br>4000h<br>4000h<br>4000h<br>4000h<br>4000h<br>4000h<br>4000h<br>4000h<br>4000h<br>4000h<br>4000h<br>4000h<br>4000h<br>4000h<br>4000h<br>4000h<br>4000h<br>4000h<br>4000h<br>4000h<br>4000h<br>4000h<br>4000h<br>4000h<br>4000h<br>4000h<br>4000h<br>4000h<br>4000h<br>4000h<br>4000h<br>4000h<br>4000h<br>4000h<br>4000h<br>4000h<br>4000h<br>4000h<br>4000h<br>4000h<br>4000h<br>4000h<br>4000h<br>4000h |

| NCOx<br>Accumulator<br>Value                 | 00000h \ 04000h \ 08000h \ (04000h \ 08000h \ 04000h \ 04000h \ 08000h \ 080000h \ 08000h \ 0                                                                                                                                                                                                                                                               |

| NCO_overflow                                 |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

| NCO_interrupt                                |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

| NCOx Output<br>FDC Mode                      |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

| NCOx Output<br>PF Mode<br>NCOxPWS = -<br>000 |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

| NCOx Output<br>PF Mode<br>NCOxPWS = -<br>001 |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

| R/W-0/0          | R/W-0/0                                                                                                       | R/W-0/0                        | R/W-0/0        | R/W-0/0         | R/W-0/0          | R/W-0/0          | R/W-0/0     |

|------------------|---------------------------------------------------------------------------------------------------------------|--------------------------------|----------------|-----------------|------------------|------------------|-------------|

| TXMTIE           | PERIE                                                                                                         | ABDOVE                         | CERIE          | FERIE           | RXBKIE           | RXFOIE           | TXCIE       |

| bit 7            |                                                                                                               |                                |                |                 |                  |                  | bit (       |

|                  |                                                                                                               |                                |                |                 |                  |                  |             |

| Legend:          |                                                                                                               |                                |                |                 |                  |                  |             |

| R = Readable     |                                                                                                               | W = Writable                   |                | 1               | nented bit, read |                  |             |

| u = Bit is unch  | anged                                                                                                         | x = Bit is unkr                |                | -n/n = Value a  | at POR and BO    | R/Value at all c | ther Resets |

| '1' = Bit is set |                                                                                                               | '0' = Bit is cle               | ared           |                 |                  |                  |             |

| bit 7            | TXMTIE: Tra                                                                                                   | insmit Shift Reg               | ister Empty In | iterrupt Enable | bit              |                  |             |

|                  | 1 = Interrupt<br>0 = Interrupt                                                                                | t enabled                      |                |                 |                  |                  |             |

| bit 6            | PERIE: Parit                                                                                                  | y Error Interrup               | Enable bit     |                 |                  |                  |             |

|                  | 1 = Interrupt<br>0 = Interrupt                                                                                |                                |                |                 |                  |                  |             |

| bit 5            | ABDOVE: Auto-baud Detect Overflow Interrupt Enable bit<br>1 = Interrupt enabled<br>0 = Interrupt not enabled  |                                |                |                 |                  |                  |             |

| bit 4            | CERIE: Chec<br>1 = Interrupt<br>0 = Interrupt                                                                 |                                | errupt Enable  | bit             |                  |                  |             |

| bit 3            | FERIE: Framing Error Interrupt Enable bit<br>1 = Interrupt enabled<br>0 = Interrupt not enabled               |                                |                |                 |                  |                  |             |

| bit 2            | <b>RXBKIE:</b> Break Reception Interrupt Enable bit<br>1 = Interrupt enabled<br>0 = Interrupt not enabled     |                                |                |                 |                  |                  |             |

| bit 1            | <b>RXFOIE:</b> Receive FIFO Overflow Interrupt Enable bit   1 = Interrupt enabled   0 = Interrupt not enabled |                                |                |                 |                  |                  |             |

| bit 0            |                                                                                                               | smit Collision In<br>t enabled | terrupt Enable | e bit           |                  |                  |             |

## REGISTER 31-5: UXERRIE: UART ERROR INTERRUPT ENABLE REGISTER

## 32.4 Transfer Counter

In all master modes, the transfer counter can be used to determine how many data transfers the SPI will send/receive. The transfer counter is comprised of the SPIxTCTH/L set of registers, and is also partially controlled by the SPIxTWIDTH register. The Transfer Counter has two primary modes, determined by the BMODE bit of the SPIxCON0 register. Each mode uses the SPIxTCTH/L and SPIxTWIDTH registers to determine the number and size of the transfers. In both modes, when the transfer counter reaches zero, the TCZIF interrupt flag is set.

- Note: When BMODE=1 in all master modes (and at all times in slave modes), the Transfer Counter will still decrement as transfers occur and can be used to count the number of messages sent/received, as well as to control SS(out) and to trigger TCZIF. Also when BMODE = 1, the SPIxTWIDTH register can be used in Master and Slave modes to determine the size of messages sent and received by the SPI, even if the Transfer Counter is not being actively used to control the number of messages being sent/received by the SPI module.

- 32.4.1 TOTAL BIT COUNT MODE (BMODE = 0)

In this mode, SPIxTCTH/L and SPIxTWIDTH are concatenated to determine the total number of bits to be transferred. These bits will be loaded from/into the transmit/receive FIFOs in 8-bit increments and the transfer counter will be decremented by eight until the total number of remaining bits is less than eight. If there are any remaining bits (SPIxTWIDTH  $\neq$  0), the transmit FIFO will send out one final message with any extra bits greater than the remainder ignored. The SPIxTWIDTH is the remaining bit count but the value does not change as it does for the SPIxTCT value. Similarly, the receiver will load a final byte into the receiver FIFO, and pad the extra bits with zeros. The LSBF bit of SPIxCON0 determines whether the Most Significant or Least Significant bits of this final byte are ignored/ padded. For example, when LSBF = 0 and the final transfer contains only two bits then if the last byte sent was 5Fh then the RXB of the receiver will contain 40h which are the two MSbits of the final byte padded with zeros in the LSbits.

In this mode, the SPI master will only transmit messages when the SPIxTCT value is greater than zero, regardless of TXR and RXR settings. In Master Transmit mode, the transfer starts with the data write to the SPIxTXB register or the count value written to the SPIxTCTL register, which ever occurs last. In Master Receive-only mode, the transfer clocks start when the SPIxTCTL value is written. Transfer clocks are suspended when the receive FIFO is full and resume as the FIFO is read.

### 32.4.2 VARIABLE TRANSFER SIZE MODE (BMODE = 1)

In this mode, SPIxTWIDTH specifies the width of every individual piece of the data transfer in bits. SPIxTCTH/ SPIxTCTL specifies the number of transfers of this bit length. If SPIxTWIDTH = 0, each piece is a full byte of data. If SPIxTWIDTH  $\neq$  0, then only the specified number of bits from the transmit FIFO are shifted out, with the unused bits ignored. Received data is padded with zeros in the unused bit areas when transfered into the receive FIFO. The LSBF bit of SPIxCON0 determines whether the Most Significant or Least Significant bits of the transfers are ignored/padded. In this mode, the transfer counter being zero only stops messages from being sent/received when in "Receive only" mode.

Note: With BMODE = 1, it is possible for the transfer counter (SPIxTCTH/L) to decrement below zero, although when in "Receive only" Master mode, transfer clocks will cease when the transfer counter reaches zero.

## 33.3.2 BYTE FORMAT

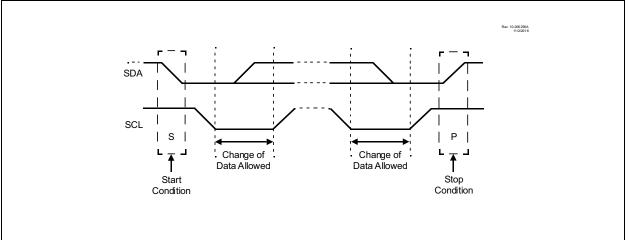

All communication in  $I^2C$  is done in 9-bit segments. A byte is sent from a master to a slave or vice-versa, followed by an Acknowledge bit sent by the receiver. After the 8th falling edge of the SCL line, the device transmitting data on the SDA line releases control of that pin to an input, and reads in an acknowledge value on the next clock pulse. The clock signal is provided by the master. Data is valid to change while the SCL line is low, and sampled on the rising edge of the clock. Changes on the SDA line while the SCL line is high define Start and Stop conditions on the bus which are explained further in the chapter.

## 33.3.3 SDA AND SCL PINS

The user must configure these pins as open-drain inputs. This is done by clearing the appropriate TRIS bits and setting the appropriate and ODCON bits. The user may also select the input threshold, slew-rate and internal pull-up settings using the Rxyl2C control registers (Register 16-9).

## 33.3.4 SDA HOLD TIME

The hold time of the SDA pin is selected by the SDAHT<1:0> bits of the I2CxCON2 register. Hold time is the time SDA is held valid after the falling edge of SCL. A longer hold time setting may help on buses with large capacitance.

## 33.3.5 START CONDITION

The I<sup>2</sup>C specification defines a Start condition as a transition of SDA line from a high to a low state while SCL line is high. A Start condition is always generated by the master and signifies the transition of the bus from an Idle to an Active state. Figure 33-3 shows waveforms for Start conditions. Master hardware waits for the BFRE bit of I2CxSTAT0 to be set, before asserting a Start condition on the SCL and SDA lines. If two masters assert a start at the same time, a collision will occur during the addressing phase.

## 33.3.6 STOP CONDITION

A Stop condition is a transition of the SDA line from low to high while the SCL line is high. Figure 33-3 shows waveforms for Stop conditions.

| Note: | At least one SCL low time must appear    |  |  |  |

|-------|------------------------------------------|--|--|--|

|       | before a Stop is valid. Therefore if the |  |  |  |

|       | SDA line goes low then high again while  |  |  |  |

|       | the SCL line is high, only the Start     |  |  |  |

|       | condition is detected.                   |  |  |  |

© 2017 Microchip Technology Inc.

DS40001919B-page 608

| <b>TABLE 36-6</b> : | SUMMARY OF REGISTERS ASSOCIATED WITH ADC (CONTINUED) |

|---------------------|------------------------------------------------------|

|---------------------|------------------------------------------------------|

| Name   | Bit 7            | Bit 6 | Bit 5 | Bit 4 | Bit 3  | Bit 2 | Bit 1 | Bit 0 | Register<br>on Page |  |

|--------|------------------|-------|-------|-------|--------|-------|-------|-------|---------------------|--|

| ADERRL | ERR<7:0>         |       |       |       |        |       |       |       |                     |  |

| ADERRH |                  |       |       | ERR<  | :15:8> |       |       |       | 633                 |  |

| ADLTHH | LTH<15:8>        |       |       |       |        |       |       |       |                     |  |

| ADLTHL | LTH<7:0>         |       |       |       |        |       |       |       |                     |  |

| ADUTHH | UTH<15:8>        |       |       |       |        |       |       |       |                     |  |

| ADUTHL | UTH<7:0>         |       |       |       |        |       |       |       |                     |  |

| ADERRL | ERR<15:8>        |       |       |       |        |       |       |       |                     |  |

| ADACT  | — — — ADACT<4:0> |       |       |       |        |       |       | 619   |                     |  |

| ADCP   | CPON             | _     | _     | _     | _      | _     | _     | CPRDY | 636                 |  |

**Legend:** – = unimplemented read as '0'. Shaded cells are not used for the ADC module.

## 37.0 5-BIT DIGITAL-TO-ANALOG CONVERTER (DAC) MODULE

The Digital-to-Analog Converter supplies a variable voltage reference, ratiometric with the input source, with 32 selectable output levels.

The positive input source (VSOURCE+) of the DAC can be connected to:

- FVR Buffer

- External VREF+ pin

- VDD supply voltage

The negative input source (VSOURCE-) of the DAC can be connected to:

- External VREF- pin

- Vss

The output of the DAC (DAC1\_output) can be selected as a reference voltage to the following:

- · Comparator positive input

- ADC input channel

- DAC1OUT1 pin

- DAC1OUT2 pin

The Digital-to-Analog Converter (DAC) can be enabled by setting the EN bit of the DAC1CON0 register.

Rev. 10-000026H 10/12/2016 Reserved 11 VSOURCE+ DATA<4:0> FVR Buffer 5 10 R VREF+ 01 AVDD 00 Ş R PSS 5 R R 32-to-1 MUX DACx output 32 • • To Peripherals Steps ΕN  $\leq$ R DACxOUT1<sup>(1)</sup>  $\geq$ R OE1 R DACxOUT2<sup>(1)</sup> VREF-OE2 1 VSOURCE-AVss 0 NSS Note 1: The unbuffered DACx\_output is provided on the DACxOUT pin(s).

## FIGURE 37-1: DIGITAL-TO-ANALOG CONVERTER BLOCK DIAGRAM

|                                                                                  | Branch if Not Overflow                                                    |                                                                                         |                                                      |                               |                                                                          | Branch if Not Zero                                                                  |                                        |  |  |  |

|----------------------------------------------------------------------------------|---------------------------------------------------------------------------|-----------------------------------------------------------------------------------------|------------------------------------------------------|-------------------------------|--------------------------------------------------------------------------|-------------------------------------------------------------------------------------|----------------------------------------|--|--|--|

| Syntax:                                                                          | BNOV n                                                                    |                                                                                         |                                                      | Syntax:                       | BNZ n                                                                    | BNZ n                                                                               |                                        |  |  |  |

| Operands:                                                                        | -128 ≤ n ≤ 1                                                              | 27                                                                                      |                                                      | Operands:                     | -128 ≤ n ≤ 1                                                             | $-128 \le n \le 127$                                                                |                                        |  |  |  |