Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

#### Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

E·XF

| Details                    |                                                                             |

|----------------------------|-----------------------------------------------------------------------------|

| Product Status             | Active                                                                      |

| Core Processor             | PIC                                                                         |

| Core Size                  | 8-Bit                                                                       |

| Speed                      | 64MHz                                                                       |

| Connectivity               | I <sup>2</sup> C, LINbus, SPI, UART/USART                                   |

| Peripherals                | Brown-out Detect/Reset, DMA, HLVD, POR, PWM, WDT                            |

| Number of I/O              | 44                                                                          |

| Program Memory Size        | 128KB (64K x 16)                                                            |

| Program Memory Type        | FLASH                                                                       |

| EEPROM Size                | 1K x 8                                                                      |

| RAM Size                   | 8K x 8                                                                      |

| Voltage - Supply (Vcc/Vdd) | 1.8V ~ 3.6V                                                                 |

| Data Converters            | A/D 43x12b; D/A 1x5b                                                        |

| Oscillator Type            | Internal                                                                    |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                           |

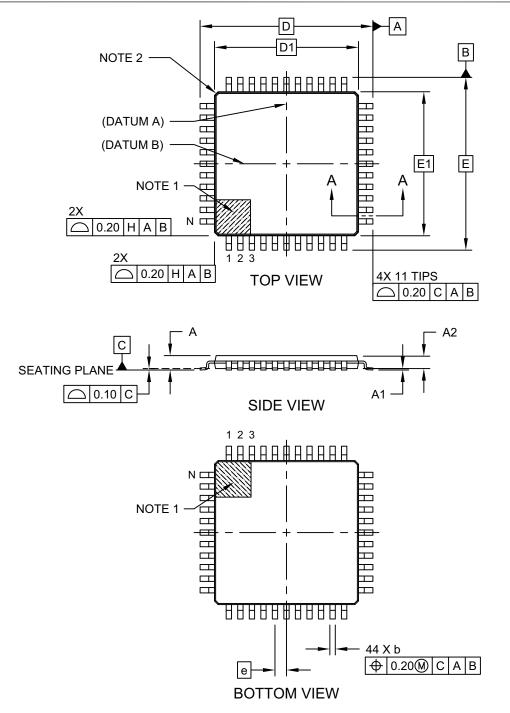

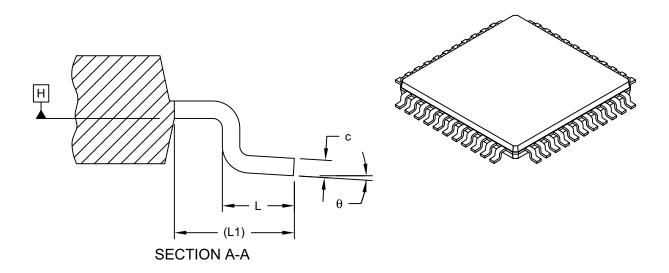

| Mounting Type              | Surface Mount                                                               |

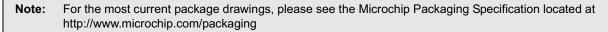

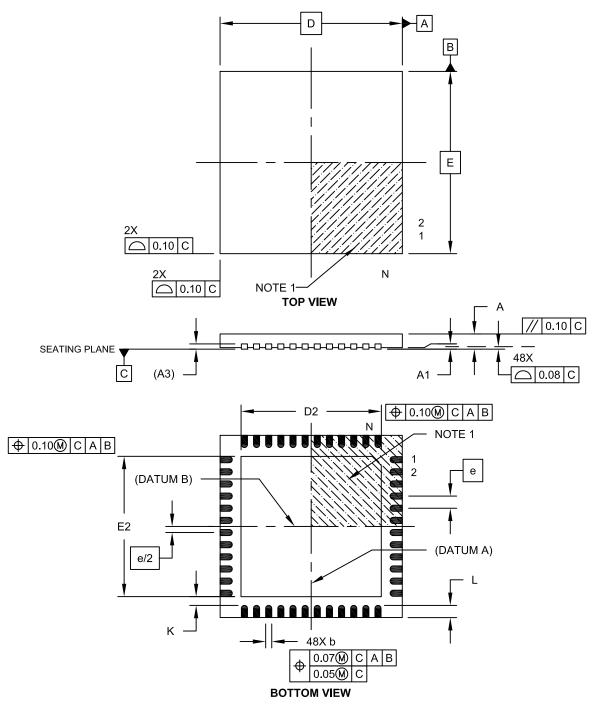

| Package / Case             | 48-TQFP Exposed Pad                                                         |

| Supplier Device Package    | 48-TQFP-EP (7x7)                                                            |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/pic18lf57k42-i-pt |

|                            |                                                                             |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

# 9.3 Interrupt Priority

The final priority level for any pending source of interrupt is determined first by the user-assigned priority of that source in the IPRx register, then by the natural order priority within the IVT. The sections below detail the operation of Interrupt priorities.

### 9.3.1 USER (SOFTWARE) PRIORITY

User-assigned interrupt priority is enabled by setting the IPEN bit in the INTCON0 register (Register 9-1). Each peripheral interrupt source can be assigned a high or low priority level by the user. The userassignable interrupt priority control bits for each interrupt are located in the IPRx registers (Registers 9-25 through 9-35).

The interrupts are serviced based on predefined interrupt priority scheme defined below.

- Interrupts set by the user as high-priority interrupt have higher precedence of execution. High-priority interrupts will override a low-priority request when:

- a) A low priority interrupt has been requested or its request is already pending.

- b) A low- and high-priority interrupt are triggered concurrently, i.e., on the same instruction cycle<sup>(1)</sup>.

- c) A low-priority interrupt was requested and the corresponding Interrupt Service Routine is currently executing. In this case, the lower priority interrupt routine will complete executing after the high-priority interrupt has been serviced<sup>(2)</sup>.

- 2. Interrupts set by the user as a low priority have the lower priority of execution and are preempted by any high-priority interrupt.

- Interrupts defined with the same software priority cannot preempt or interrupt each other. Concurrent pending interrupts with the same user priority are resolved using the natural order priority. (when MVECEN = ON) or in the order the interrupt flag bits are polled in the ISR (when MVECEN = OFF).

- Note 1: When a high priority interrupt preempts a concurrent low priority interrupt, the GIEL bit may be cleared in the high priority Interrupt Service Routine. If the GIEL bit is cleared, the low priority interrupt will NOT be serviced even if it was originally requested. The corresponding interrupt flag needs to be cleared in user code.

- 2: When a high priority interrupt is requested while a low priority Interrupt Service Routine is executing, the GIEL bit may be cleared in the high priority Interrupt Service Routine. The pending low priority interrupt will resume even if the GIEL bit is cleared.

#### 9.8 Interrupt Setup Procedure

1. When using interrupt priority levels, set the IPEN bit in INTCON0 register and then select the user-assigned priority level for the interrupt source by writing the control bits in the appropriate IPRx Control register.

| Note: | At a device Reset, the IPRx registers are |

|-------|-------------------------------------------|

|       | initialized, such that all user interrupt |

|       | sources are assigned to high priority.    |

- 2. Clear the Interrupt Flag Status bit associated with the peripheral in the associated PIRx Status register.

- 3. Enable the interrupt source by setting the interrupt enable control bit associated with the source in the appropriate PIEx Control register.

- If the vector table is used (MVECEN = 1), then setup the start address for the Interrupt Vector Table using the IVTBASE register. See Section 9.2.2 "Interrupt Vector Table Contents".

- 5. Once the IVTBASE is written to, set the Interrupt enable bits in INTCON0 register.

- 6. An example of setting up interrupts and ISRs using assembly and C can be found in Examples 9-3 and 9-4.

### 9.9 External Interrupt Pins

The PIC18(L)F26/27/45/46/47/55/56/57K42 devices have three external interrupt sources which can be assigned to any pin on different ports based on the PPS settings. Refer Section 17.0 "Peripheral Pin Select (PPS) Module" for possible rerouting options. The external interrupt sources are edge-triggered. If the corresponding INTxEDG bit in the INTCON0 register is set (= 1), the interrupt is triggered by a rising edge. If the bit is clear, the trigger is on the falling edge.

When a valid edge appears on the INTx pin, the corresponding flag bit, INTxF in the PIRx registers, is set. This interrupt can be disabled by clearing the corresponding enable bit, INTxE. Flag bit, INTxF, must be cleared by software in the Interrupt Service Routine before re-enabling the interrupt.

All external interrupts (INT0, INT1 and INT2) can wakeup the processor from Idle or Sleep modes if bit INTxE was set prior to going into those modes. If the Global Interrupt Enable bit, GIE/GIEH, is set, the processor will branch to the interrupt vector following wake-up. Interrupt priority is determined by the value contained in the interrupt priority bits, INT0IP, INT1IP and INT2IP of the IPRx registers.

### 9.10 Wake-up from Sleep

The interrupt controller provides a wake-up request to the CPU whenever an interrupt event occurs, if the interrupt event is enabled. This occurs regardless of whether the part is in Run, Idle/Doze or Sleep modes. The status of the GIEH/GIEL bits has no effect on the wake-up request. The wake-up request will be asynchronous to all clocks.

# 9.11 Interrupt Compatibility

When the MVECEN bit in Configuration Word 2L is cleared (Register 5-3), the Interrupt Vector Table feature is disabled and interrupts are compatible with previous high performance 8-bit PIC18 microcontroller devices. In this mode, the Interrupt Vector Table priority has no effect.

When the IPEN bit is also cleared, the interrupt priority feature is disabled and interrupts are compatible with PIC<sup>®</sup>16 microcontroller mid-range devices. All interrupts branch to address 0008h since the interrupt priority is disabled.

| R-0/0                                                                | R-0/0                                                                                                                      | R/W/HS-0/0                        | R/W/HS-0/0                    | R/W/HS-0/0        | R/W/HS-0/0         | R/W/HS-0/0      | R/W/HS-0/0            |

|----------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------|-----------------------------------|-------------------------------|-------------------|--------------------|-----------------|-----------------------|

| I2C2TXIF <sup>(</sup>                                                | <sup>2)</sup> I2C2RXIF <sup>(2)</sup>                                                                                      | DMA2AIF                           | DMA2ORIF                      | DMA2DCNTIF        | DMA2SCNTIF         | C2IF            | INT1IF <sup>(3)</sup> |

| bit 7                                                                |                                                                                                                            |                                   |                               |                   |                    |                 | bit C                 |

|                                                                      |                                                                                                                            |                                   |                               |                   |                    |                 |                       |

| Legend:                                                              |                                                                                                                            |                                   |                               |                   |                    |                 |                       |

| R = Reada                                                            |                                                                                                                            | W = Writable b                    |                               |                   | ented bit, read a  |                 |                       |

| u = Bit is u                                                         | -                                                                                                                          | x = Bit is unkno                  |                               |                   | POR and BOR/       | Value at all ot | her Resets            |

| '1' = Bit is                                                         | set                                                                                                                        | '0' = Bit is clea                 | red                           | HS = Bit is set   | in hardware        |                 |                       |

| bit 7                                                                | <b>I2C2TXIF</b> : I <sup>2</sup>                                                                                           | C2 Transmit Int                   | errupt Flag bit <sup>(2</sup> | 2)                |                    |                 |                       |

|                                                                      |                                                                                                                            | has occurred                      |                               |                   |                    |                 |                       |

|                                                                      | •                                                                                                                          | event has not o                   |                               | ,                 |                    |                 |                       |

| bit 6                                                                |                                                                                                                            | C2 Receive Inte                   | errupt Flag bit <sup>(2</sup> | )                 |                    |                 |                       |

|                                                                      |                                                                                                                            | has occurred                      | agurrad                       |                   |                    |                 |                       |

| bit 5                                                                | •                                                                                                                          | event has not o<br>MA2 Abort Inte |                               |                   |                    |                 |                       |

| DIL O                                                                |                                                                                                                            | has occurred (                    |                               | d by software)    |                    |                 |                       |

|                                                                      |                                                                                                                            | event has not o                   |                               | a by continuity   |                    |                 |                       |

| bit 4                                                                | DMA2ORIF:                                                                                                                  | DMA2 Overrun                      | Interrupt Flag                | bit               |                    |                 |                       |

|                                                                      |                                                                                                                            | has occurred (                    |                               | d by software)    |                    |                 |                       |

|                                                                      | 0 = Interrupt                                                                                                              | event has not o                   | occurred                      |                   |                    |                 |                       |

| bit 3                                                                |                                                                                                                            | IF: DMA2 Desti                    |                               |                   |                    |                 |                       |

|                                                                      |                                                                                                                            | has occurred (<br>event has not o |                               | d by software)    |                    |                 |                       |

| bit 2                                                                | -                                                                                                                          | IF: DMA2 Source                   |                               | upt Flag bit      |                    |                 |                       |

|                                                                      |                                                                                                                            | has occurred (                    |                               |                   |                    |                 |                       |

|                                                                      | 0 = Interrupt                                                                                                              | event has not o                   | occurred                      |                   |                    |                 |                       |

| bit 1                                                                |                                                                                                                            | errupt Flag bit                   |                               |                   |                    |                 |                       |

|                                                                      | <ul> <li>1 = Interrupt has occurred (must be cleared by software)</li> <li>0 = Interrupt event has not occurred</li> </ul> |                                   |                               |                   |                    |                 |                       |

| bit 0 INT1IF: External Interrupt 1 Interrupt Flag bit <sup>(3)</sup> |                                                                                                                            |                                   |                               |                   |                    |                 |                       |

|                                                                      | <ul> <li>1 = Interrupt has occurred (must be cleared by software)</li> <li>0 = Interrupt event has not occurred</li> </ul> |                                   |                               |                   |                    |                 |                       |

| Note 1:                                                              | •                                                                                                                          |                                   |                               |                   |                    |                 |                       |

| 2:                                                                   | I2CxTXIF and I register must be                                                                                            |                                   | ead-only bits. To             | clear the interro | upt condition, the | e CLRBF bit ir  | 12CxSTAT1             |

| 3:                                                                   | The external in                                                                                                            | terrupt GPIO pi                   | n is selected by              | the INTxPPS re    | egister.           |                 |                       |

|                                                                      |                                                                                                                            |                                   |                               |                   |                    |                 |                       |

# REGISTER 9-8: PIR5: PERIPHERAL INTERRUPT REGISTER 5<sup>(1)</sup>

| R/W-0/0         | R/W-0/0                       | R/W-0/0                      | R/W-0/0          | R/W-0/0           | R/W-0/0            | R/W-0/0         | R/W-0/0    |

|-----------------|-------------------------------|------------------------------|------------------|-------------------|--------------------|-----------------|------------|

| I2C2TXIE        | I2C2RXIE                      | DMA2AIE                      | DMA2ORIE         | DMA2DCNTIE        | DMA2SCNTIE         | C2IE            | INT1IE     |

| bit 7           |                               |                              |                  |                   |                    |                 | bit (      |

|                 |                               |                              |                  |                   |                    |                 |            |

| Legend:         |                               |                              |                  |                   |                    |                 |            |

| R = Readab      |                               | W = Writable b               |                  |                   | ented bit, read as |                 |            |

| u = Bit is un   | -                             | x = Bit is unkno             |                  | -n/n = Value at   | POR and BOR/       | /alue at all ot | her Resets |

| '1' = Bit is se | et                            | '0' = Bit is clea            | red              |                   |                    |                 |            |

|                 |                               |                              |                  | .,                |                    |                 |            |

| bit 7           | 1 = Enabled                   | <sup>2</sup> C2 Transmit Int | errupt Enable b  | IT                |                    |                 |            |

|                 | 0 = Disable                   |                              |                  |                   |                    |                 |            |

| bit 6           | I2C2RXIE:                     | <sup>2</sup> C2 Receive Int  | errupt Enable bi | t                 |                    |                 |            |

|                 | 1 = Enabled                   |                              | ·                |                   |                    |                 |            |

|                 | 0 = Disable                   | d                            |                  |                   |                    |                 |            |

| bit 5           |                               | DMA2 Abort Inte              | rrupt Enable bit |                   |                    |                 |            |

|                 | 1 = Enableo                   |                              |                  |                   |                    |                 |            |

| bit 4           |                               | u<br>: DMA2 Overrun          | Interrunt Enabl  | e hit             |                    |                 |            |

| Dit 4           | 1 = Enabled                   |                              |                  | ebit              |                    |                 |            |

|                 | 0 = Disable                   | -                            |                  |                   |                    |                 |            |

| bit 3           | DMA2DCN1                      | TE: DMA2 Dest                | ination Count In | terrupt Enable bi | t                  |                 |            |

|                 | 1 = Enabled                   | -                            |                  |                   |                    |                 |            |

|                 | 0 = Disable                   |                              |                  |                   |                    |                 |            |

| bit 2           |                               | TE: DMA2 Sour                | ce Count Interru | pt Enable bit     |                    |                 |            |

|                 | 1 = Enableo                   |                              |                  |                   |                    |                 |            |

| bit 1           | C2IE: C2 Interrupt Enable bit |                              |                  |                   |                    |                 |            |

|                 | 1 = Enabled                   |                              |                  |                   |                    |                 |            |

|                 | 0 = Disable                   | d                            |                  |                   |                    |                 |            |

| bit 0           | INT1IE: Exte                  | ernal Interrupt 1            | Enable bit       |                   |                    |                 |            |

|                 | 1 = Enabled                   |                              |                  |                   |                    |                 |            |

|                 | 0 = Disable                   | h                            |                  |                   |                    |                 |            |

# REGISTER 9-19: PIE5: PERIPHERAL INTERRUPT ENABLE REGISTER 5

#### 16.2.6 INPUT THRESHOLD CONTROL

The INLVLx register (Register 16-8) controls the input voltage threshold for each of the available PORTx input pins. A selection between the Schmitt Trigger CMOS or the TTL compatible thresholds is available. The input threshold is important in determining the value of a read of the PORTx register and also the level at which an interrupt-on-change occurs, if that feature is enabled. See Table 44-6 for more information on threshold levels.

**Note:** Changing the input threshold selection should be performed while all peripheral modules are disabled. Changing the threshold level during the time a module is active may inadvertently generate a transition associated with an input pin, regardless of the actual voltage level on that pin.

### 16.2.7 WEAK PULL-UP CONTROL

The WPUx register (Register 16-5) controls the individual weak pull-ups for each port pin.

#### 16.2.8 EDGE SELECTABLE INTERRUPT-ON-CHANGE

An interrupt can be generated by detecting a signal at the port pin that has either a rising edge or a falling edge. Any individual pin can be configured to generate an interrupt. The interrupt-on-change module is present on all the pins. For further details about the IOC module refer to Section 18.0 "Interrupt-on-Change".

# 16.2.9 I<sup>2</sup>C PAD CONTROL

For the PIC18(L)F26/27/45/46/47/55/56/57K42 devices, the  $I^2C$  specific pads are available on RB1, RB2, RC3, RC4, RD0<sup>(1)</sup> and RD1<sup>(1)</sup> pins. The  $I^2C$  characteristics of each of these pins is controlled by the RxyI2C registers (see Register 16-9). These characteristics include enabling  $I^2C$  specific slew rate (over standard GPIO slew rate), selecting internal pullups for  $I^2C$  pins, and selecting appropriate input threshold as per SMBus specifications.

# **Note 1:** RD0 and RD1 I<sup>2</sup>C pads are not available in PIC18(L)F26K42 parts.

Any peripheral using the I<sup>2</sup>C pins read the I<sup>2</sup>C ST inputs when enabled via RxyI2C.

# 16.3 PORTE Registers

Depending on the device, PORTE is implemented in two different ways.

#### 16.3.1 PORTE ON 40/44/48-PIN DEVICES

For PIC18(L)F45/46/47/55/56/57K42 devices, PORTE is a 4-bit wide port. Three pins (RE0, RE1 and RE2) are individually configurable as inputs or outputs. These pins have Schmitt Trigger input buffers. When selected as an analog input, these pins will read as '0's. The corresponding data direction register is TRISE. Setting a TRISE bit (= 1) will make the corresponding PORTE pin an input (i.e., disable the output driver).

Clearing a TRISE bit (= 0) will make the corresponding PORTE pin an output (i.e., enable the output driver and put the contents of the output latch on the selected pin). TRISE controls the direction of the REx pins, even when they are being used as analog pins. The user must make sure to keep the pins configured as inputs when using them as analog inputs. RE<2:0> bits have other registers associated with them (i.e., ANSELE, WPUE, INLVLE, SLRCONE and ODCONE). The functionality is similar to the other ports. The Data Latch register (LATE) is also memory-mapped. Readmodify-write operations on the LATE register read and write the latched output value for PORTE.

Note: On a Power-on Reset, RE<2:0> are configured as analog inputs.

The fourth pin of PORTE (MCLR/VPP/RE3) is an input-only pin. Its operation is controlled by the MCLRE Configuration bit. When selected as a port pin, (MCLRE = 0), it functions as a digital input-only pin; as such, it does not have TRIS or LAT bits associated with its operation. Otherwise, it functions as the device's Master Clear input. In either configuration, RE3 also functions as the programming voltage input during programming. RE3 in PORTE register is a read-only bit and will read '1' when MCLRE = 1 (i.e., Master Clear enabled).

Note: On a Power-on Reset, RE3 is enabled as a digital input only if Master Clear functionality is disabled.

| Name       | Bit 7 | Bit 6 | Bit 5 | Bit 4 | Bit 3         | Bit 2      | Bit 1  | Bit 0     | Register<br>on page |

|------------|-------|-------|-------|-------|---------------|------------|--------|-----------|---------------------|

| PPSLOCK    | —     |       | —     | —     | —             | —          | —      | PPSLOCKED | 283                 |

| INT0PPS    | _     | _     | _     |       |               | INT0PPS<4  | 4:0>   |           | 277                 |

| INT1PPS    | _     | _     | _     |       |               | INT1PPS<   | 4:0>   |           | 277                 |

| INT2PPS    | _     | _     | _     |       |               | INT2PPS<4  | 4:0>   |           | 277                 |

| TOCKIPPS   |       | _     | _     |       |               | T0CKIPPS<  | 4:0>   |           | 277                 |

| T1CKIPPS   |       | _     | _     |       |               | T1CKIPPS<  | 4:0>   |           | 277                 |

| T1GPPS     | _     | _     | _     |       |               | T1GPPS<4   | 4:0>   |           | 277                 |

| T3CKIPPS   | _     | _     | _     |       |               | T3CKIPPS<  | :4:0>  |           | 277                 |

| T3GPPS     | _     | _     | _     |       |               | T3GPPS<4   | 4:0>   |           | 277                 |

| T5CKIPPS   | -     | _     | —     |       |               | T5CKIPPS<  | :4:0>  |           | 277                 |

| T5GPPS     | -     | _     | —     |       |               | T5GPPS<4   | 4:0>   |           | 277                 |

| T2INPPS    | _     | _     | _     |       |               | T2INPPS<   | 4:0>   |           | 277                 |

| T4INPPS    | -     | _     | —     |       |               | T4INPPS<   | 4:0>   |           | 277                 |

| T6INPPS    | _     | _     | _     |       |               | T6INPPS<4  | 4:0>   |           | 277                 |

| CCP1PPS    | _     | _     | _     |       |               | CCP1PPS<   | 4:0>   |           | 277                 |

| CCP2PPS    | _     | _     | _     |       |               | CCP2PPS<   | 4:0>   |           | 277                 |

| CCP3PPS    | _     | _     | _     |       |               | CCP3PPS<   | 4:0>   |           | 277                 |

| CCP4PPS    | _     | _     | _     |       |               | CCP4PPS<   | 4:0>   |           | 277                 |

| SMT1WINPPS | _     | _     | _     |       |               | SMT1WINPP  | S<4:0> |           | 277                 |

| SMT1SIGPPS | _     | _     | _     |       |               | SMT1SIGPPS | S<4:0> |           | 277                 |

| CWG1PPS    |       | _     | _     |       |               | CWG1PPS<   | :4:0>  |           | 277                 |

| CWG2PPS    |       | _     | _     |       |               | CWG2PPS<   | :4:0>  |           | 277                 |

| CWG3PPS    |       | _     | _     |       |               | CWG3PPS<   | :4:0>  |           | 277                 |

| MD1CARLPPS | _     | _     | _     |       |               | MDCARLPPS  | 6<4:0> |           | 277                 |

| MD1CARHPPS | _     | _     | _     |       |               | MDCARHPP   | S<4:0> |           | 277                 |

| MD1SRCPPS  | _     | _     | _     |       |               | MDSRCPPS   | <4:0>  |           | 277                 |

| CLCIN0PPS  |       | _     | _     |       |               | CLCIN0PPS  | <4:0>  |           | 277                 |

| CLCIN1PPS  | _     | _     | _     |       |               | CLCIN1PPS  | <4:0>  |           | 277                 |

| CLCIN2PPS  | _     | _     | _     |       |               | CLCIN2PPS  | <4:0>  |           | 277                 |

| CLCIN3PPS  |       | _     | _     |       |               | CLCIN3PPS  | <4:0>  |           | 277                 |

| ADACTPPS   | _     | _     | _     |       |               | ADACTPPS   | <4:0>  |           | 277                 |

| SPI1SCKPPS | _     | _     | _     |       |               | SPI1SCKPPS | S<4:0> |           | 277                 |

| SPI1SDIPPS | _     | _     | _     |       |               | SPI1SDIPPS | <4:0>  |           | 277                 |

| SPI1SSPPS  | _     | _     | _     |       |               | SPI1SSPPS  | <4:0>  |           | 277                 |

| I2C1SCLPPS |       | _     | _     |       |               | I2C1SCLPPS | 6<4:0> |           | 277                 |

| I2C1SDAPPS | _     | _     | _     |       |               | I2C1SDAPPS | 6<4:0> |           | 277                 |

| I2C2SCLPPS | _     | _     | —     |       |               | I2C2SCLPPS | 6<4:0> |           | 277                 |

| I2C2SDAPPS | _     | _     | —     |       |               | I2C2SDAPPS | 6<4:0> |           | 277                 |

| U1RXPPS    | _     | _     | _     |       |               | U1RXPPS<   | 4:0>   |           | 277                 |

| U1CTSPPS   | _     | _     | _     |       | U1CTSPPS<4:0> |            |        |           | 277                 |

| U2RXPPS    | _     | _     | _     |       |               | U2RXPPS<   | 4:0>   |           | 277                 |

| U2CTSPPS   | _     | _     | —     |       |               | U2CTPPS<   | 4:0>   |           | 277                 |

| RxyPPS     | _     | _     | _     |       |               | RxyPPS<4   |        |           | 280                 |

#### TABLE 17-3: SUMMARY OF REGISTERS ASSOCIATED WITH THE PPS MODULE

**Legend:** — = unimplemented, read as '0'. Shaded cells are unused by the PPS module.

#### REGISTER 27-11: CLCDATA: CLC DATA OUTPUT

| U-0   | U-0 | U-0 | U-0 | R-0     | R-0     | R-0     | R-0     |

|-------|-----|-----|-----|---------|---------|---------|---------|

| —     |     |     |     | CLC4OUT | CLC3OUT | CLC2OUT | CLC10UT |

| bit 7 |     |     |     |         |         |         | bit 0   |

| Legend:              |                      |                                                       |

|----------------------|----------------------|-------------------------------------------------------|

| R = Readable bit     | W = Writable bit     | U = Unimplemented bit, read as '0'                    |

| u = Bit is unchanged | x = Bit is unknown   | -n/n = Value at POR and BOR/Value at all other Resets |

| '1' = Bit is set     | '0' = Bit is cleared |                                                       |

| bit 7-4 | Unimplemented: Read as '0'                          |

|---------|-----------------------------------------------------|

| bit 3   | CLC4OUT: Mirror copy of OUT bit of CLC4CON register |

| bit 2   | CLC3OUT: Mirror copy of OUT bit of CLC3CON register |

| bit 1   | CLC2OUT: Mirror copy of OUT bit of CLC2CON register |

| bit 0   | CLC1OUT: Mirror copy of OUT bit of CLC1CON register |

#### TABLE 27-3: SUMMARY OF REGISTERS ASSOCIATED WITH CLCx

| Name     | Bit 7 | Bit 6 | Bit 5 | Bit 4    | Bit 3   | Bit 2   | Bit 1     | Bit 0   | Register on<br>Page |

|----------|-------|-------|-------|----------|---------|---------|-----------|---------|---------------------|

| CLCxCON  | EN    | —     | OUT   | INTP     | INTN    |         | MODE<2:0> |         | 440                 |

| CLCxPOL  | POL   | _     | _     | —        | G4POL   | G3POL   | G2POL     | G1POL   | 441                 |

| CLCxSEL0 | _     | _     |       |          | D1S     | <5:0>   |           |         | 442                 |

| CLCxSEL1 | _     | —     |       | D2S<5:0> |         |         |           |         |                     |

| CLCxSEL2 | _     | _     |       | D3S<5:0> |         |         |           |         |                     |

| CLCxSEL3 | _     | _     |       | D4S<5:0> |         |         |           |         | 442                 |

| CLCxGLS0 | G1D4T | G1D4N | G1D3T | G1D3N    | G1D2T   | G1D2N   | G1D1T     | G1D1N   | 443                 |

| CLCxGLS1 | G2D4T | G2D4N | G2D3T | G2D3N    | G2D2T   | G2D2N   | G2D1T     | G2D1N   | 444                 |

| CLCxGLS2 | G3D4T | G3D4N | G3D3T | G3D3N    | G3D2T   | G3D2N   | G3D1T     | G3D1N   | 445                 |

| CLCxGLS3 | G4D4T | G4D4N | G4D3T | G4D3N    | G4D2T   | G4D2N   | G4D1T     | G4D1N   | 446                 |

| CLCDATA  | _     |       | _     | _        | CLC4OUT | CLC3OUT | CLC2OUT   | CLC10UT | 447                 |

Legend: — = unimplemented, read as '0'. Shaded cells are unused by the CLCx modules.

| <b>TABLE 30-2:</b> | MD1SRC SELECTION MUX |

|--------------------|----------------------|

|                    | CONNECTIONS          |

| MS<4:0> | >   | Connection |

|---------|-----|------------|

| 1 1111  | 31- | Reserved   |

| -       | 23  |            |

| 1 0111  |     |            |

| 1 0110  | 22  | SPI1 SDO   |

| 1 0101  | 21  | Reserved   |

| 1 0100  | 20  | UART2 TX   |

| 1 0011  | 19  | UART1 TX   |

| 1 0010  | 18  | CLC4 OUT   |

| 1 0001  | 17  | CLC3 OUT   |

| 1 0000  | 16  | CLC2 OUT   |

| 0 1111  | 15  | CLC1 OUT   |

| 0 1110  | 14  | CMP2 OUT   |

| 0 1101  | 13  | CMP1 OUT   |

| 0 1100  | 12  | NCO1 OUT   |

| 0 1011  | 11  | Reserved   |

| 0 1010  | 10  | Reserved   |

| 0 1001  | 9   | PWM8 OUT   |

| 0 1000  | 8   | PWM7 OUT   |

| 0 0111  | 7   | PWM6 OUT   |

| 0 0110  | 6   | PWM5 OUT   |

# TABLE 30-2: MD1SRC SELECTION MUX CONNECTIONS

| MS<4:0> | > | Connection               |

|---------|---|--------------------------|

| 0 0101  | 5 | CCP4 OUT                 |

| 0 0100  | 4 | CCP3 OUT                 |

| 0 0011  | 3 | CCP2 OUT                 |

| 0 0010  | 2 | CCP1 OUT                 |

| 0 0001  | 1 | DSM1 BIT                 |

| 0 0000  | 0 | Pin selected by MDSRCPPS |

#### TABLE 30-3: SUMMARY OF REGISTERS ASSOCIATED WITH DATA SIGNAL MODULATOR MODE

| Name    | Bit 7 | Bit 6 | Bit 5 | Bit 4  | Bit 3     | Bit 2    | Bit 1 | Bit 0  | Register<br>on Page |

|---------|-------|-------|-------|--------|-----------|----------|-------|--------|---------------------|

| MD1CON0 | EN    | _     | OUT   | OPOL   | —         | —        | -     | BIT    | 469                 |

| MD1CON1 | —     | _     | CHPOL | CHSYNC | _         | _        | CLPOL | CLSYNC | 470                 |

| MD1CARH | —     | _     | _     | —      | _         | CHS<2:0> |       | 471    |                     |

| MD1CARL | —     | _     | _     | —      | _         | CLS<2:0> |       | 471    |                     |

| MDSRC   | _     | _     | —     | —      | SRCS<3:0> |          |       | 472    |                     |

Legend: — = unimplemented, read as '0'. Shaded cells are not used in the Data Signal Modulator mode.

When TXMTIF goes true, indicating the transmit shift register has completed sending the last byte in the frame, the TX output is held in Idle state for the number of half-bit periods selected by the STP bits in the UxCON2 register.

After the last Stop bit, the TX output is held in Idle state for an additional wait time determined by the half-bit period count in the UxP1 register. For example, a 2450 µs delay (~6 half-bit times) requires a value of 6 in UxP1L.

Any writes to the UxTXB register that occur after TXMTIF goes true, but before the UxP1 wait time expires, are held and then transmitted immediately following the wait time. If a backward frame is received during the wait time, any bytes that may have been written to UxTXB will be transmitted after completion of the backward frame reception plus the UxP1 wait time.

The wait timer is reset by the backward frame and starts over immediately following the reception of the Stop bits of the backward frame. Data pending in the transmit shift register will be sent when the wait time elapses.

To replace or delete any pending forward frame data, the TXBE bit needs to be set to flush the shift register and transmit buffer. A new control byte can then be written to the UxTXB register. The control byte will be held in the buffer and sent at the beginning of the next forward frame following the UxP1 wait time.

In Control Device mode, PERIF is set when a forward frame is received. This helps the software to determine whether the received byte is part of a forward frame from a Control Device (either from the Control Device under consideration or from another Control Device on the bus) or a backward frame from a Control Gear.

# 31.6.2 CONTROL GEAR

The Control Gear mode is configured with the following settings:

- MODE = 0b1001

- TXEN = 1

- RXEN = 1

- UxP1 = Back Frames are held for transmission this number of half-bit periods after the completion of a Forward Frame.

UxP2 = Forward/Back Frame threshold delimiter. Idle periods more than this number of half-bit periods are detected as Forward Frames.

- UxBRGH:L = Value to achieve 1200 baud rate

- TXPOL = appropriate polarity for interface circuit

- RXPOL = same as TXPOL

- STP = 0b10 for two Stop bits

- RxyPPS = TX pin output code

- TX pin TRIS control = 0

- RXPPS = RX pin selection code

- RX pin TRIS control = 1

- Input pin ANSEL bit = 0

- ON = 1

The UART starts listening for a forward frame when the Control Gear mode is entered. Only the frames that follow an Idle period longer than UxP2 half-bit periods are detected as forward frames. Backward frames from other Control Gear are ignored. Only forward frames will be stored in UxRXB. This is necessary because a backward frame can be sent only as a response to a forward frame.

The forward frame is received one byte at a time in the receive FIFO and retrieved by reading the UxRXB register. The end of the forward frame starts a timer to delay the backward frame response by wait time equal to the number of half-bit periods stored in UxP1.

The data received in the forward frame is processed by the application software. If the application decides to send a backward frame in response to the forward frame, the value of the backward frame is written to UxTXB. This value is held for transmission in the transmit shift register until the wait time expires and is then transmitted.

If the backward frame data is written to UxTXB after the wait time has expired, it is held in the UxTXB register until the end of the wait time following the next forward frame. The TXMTIF bit is false when the backward frame data is held in the transmit shift register. Receiving a UxRXIF interrupt before the TXMTIF goes true indicates that the backward frame write was too late and another forward frame. The pending backward frame has to be flushed by setting the TXBE bit, to prevent it from being sent after the next Forward Frame.

| Name      | Bit 7    | Bit 6      | Bit 5                         | Bit 4  | Bit 3   | Bit 2 | Bit 1     | Bit 0  | Register<br>on page |

|-----------|----------|------------|-------------------------------|--------|---------|-------|-----------|--------|---------------------|

| I2CxBTO   | —        | _          | _                             | _      |         |       | BTO<2:0>  |        | 582                 |

| I2CxCLK   |          | _          | —                             | _      | _       |       | CLK<2:0>  |        | 581                 |

| I2CxPIE   | CNTIE    | ACKTIE     | _                             | WRIE   | ADRIE   | PCIE  | RSCIE     | SCIE   | 588                 |

| I2CxPIR   | CNTIF    | ACKTIF     | —                             | WRIF   | ADRIF   | PCIF  | RSCIF     | SCIF   | 587                 |

| I2CxERR   | _        | BTOIF      | BCLIF                         | NACKIF | —       | BTOIE | BCLIE     | NACKIE | 585                 |

| I2CxSTAT0 | BFRE     | SMA        | MMA                           | R      | D       |       | —         | —      | 583                 |

| I2CxSTAT1 | TXWE     | —          | TXBE                          |        | RXRE    | CLRBF | —         | RXBF   | 584                 |

| I2CxCON0  | EN       | RSEN       | S                             | CSTR   | MDR     |       | MODE<2:0> | •      | 577                 |

| I2CxCON1  | ACKCNT   | ACKDT      | ACKSTAT                       | ACKT   |         | RXOV  | TXU       | CSD    | 579                 |

| I2CxCON2  | ACNT     | GCEN       | FME ADB SDAHT<3:2> BFRET<1:0> |        |         |       |           | T<1:0> | 580                 |

| I2CxADR0  | ADR<7:0> |            |                               |        |         |       | 589       |        |                     |

| I2CxADR1  |          | ADR<7:1> — |                               |        |         |       |           | 590    |                     |

| I2CxADR2  | ADR<7:0> |            |                               |        |         |       | 591       |        |                     |

| I2CxADR3  |          | ADR<7:1> — |                               |        |         |       |           | 592    |                     |

| I2CxADB0  |          | ADB<7:0>   |                               |        |         |       |           | 593    |                     |

| I2CxADB1  |          |            |                               | A      | DB<7:0> |       |           |        | 594                 |

| I2CxCNT   |          |            |                               | CI     | NT<7:0> |       |           |        | 586                 |

| I2CxPIR   | CNTIF    | ACKTIF     |                               | WRIF   | ADRIF   | PCIF  | RSCIF     | SCIF   | 587                 |

| I2CxPIE   | CNTIE    | ACKTIE     |                               | WRIE   | ADRIE   | PCIE  | RSCIE     | SCIE   | 588                 |

| I2CxADR0  | ADR7     | ADR6       | ADR5                          | ADR4   | ADR3    | ADR2  | ADR1      | ADR0   | 589                 |

| I2CxADR1  | ADR14    | ADR13      | ADR12                         | ADR11  | ADR10   | ADR9  | ADR8      |        | 590                 |

| I2CxADR2  | ADR7     | ADR6       | ADR5                          | ADR4   | ADR3    | ADR2  | ADR1      | ADR0   | 591                 |

| I2CxADR3  | ADR14    | ADR13      | ADR12                         | ADR11  | ADR10   | ADR9  | ADR8      | —      | 592                 |

| I2CxADB0  | ADB7     | ADB6       | ADB5                          | ADB4   | ADB3    | ADB2  | ADB1      | ADB0   | 593                 |

| I2CxADB1  | ADB7     | ADB6       | ADB5                          | ADB4   | ADB3    | ADB2  | ADB1      | ADB0   | 594                 |

# TABLE 33-18: SUMMARY OF REGISTERS FOR I<sup>2</sup>C 8-BIT MACRO

**Legend:** — = unimplemented, read as '0'. Shaded cells are unused by the  $I^2C$  module.

| U-0             | U-0                                     | R/W-0/0           | R/W-0/0        | R/W-0/0        | R/W-0/0          | R/W-0/0        | R/W-0/0      |

|-----------------|-----------------------------------------|-------------------|----------------|----------------|------------------|----------------|--------------|

| —               | —                                       |                   |                | CS<            | 5:0>             |                |              |

| bit 7           |                                         |                   |                |                |                  |                | bit 0        |

|                 |                                         |                   |                |                |                  |                |              |

| Legend:         |                                         |                   |                |                |                  |                |              |

| R = Readab      | le bit                                  | W = Writable      | bit            | U = Unimplen   | nented bit, read | d as '0'       |              |

| u = Bit is un   | u = Bit is unchanged x = Bit is unknown |                   |                | -n/n = Value a | t POR and BO     | R/Value at all | other Resets |

| '1' = Bit is se | et                                      | '0' = Bit is clea | ared           |                |                  |                |              |

|                 |                                         |                   |                |                |                  |                |              |

| bit 7-6         | Unimplemer                              | nted: Read as '   | )'             |                |                  |                |              |

| bit 5-0         | <b>CS&lt;5:0&gt;</b> : AD               | C Conversion      | Clock Select b | oits           |                  |                |              |

|                 | 111111 <b>= Fc</b>                      | osc/128           |                |                |                  |                |              |

|                 | 111110 <b>= Fc</b>                      | osc/126           |                |                |                  |                |              |

|                 | 111101 <b>= Fc</b>                      | osc/124           |                |                |                  |                |              |

|                 | •                                       |                   |                |                |                  |                |              |

|                 | •                                       |                   |                |                |                  |                |              |

|                 | •                                       |                   |                |                |                  |                |              |

|                 | 000000 <b>= Fc</b>                      | osc/2             |                |                |                  |                |              |

#### REGISTER 36-6: ADCLK: ADC CLOCK SELECTION REGISTER

## REGISTER 36-7: ADREF: ADC REFERENCE SELECTION REGISTER

| U-0   | U-0 | U-0 | R/W-0/0 | U-0 | U-0 | R/W-0/0 | R/W-0/0 |

|-------|-----|-----|---------|-----|-----|---------|---------|

| —     | —   | —   | NREF    | —   | —   | PREF    | <1:0>   |

| bit 7 |     |     |         |     |     |         | bit 0   |

| Legend:              |                      |                                                       |

|----------------------|----------------------|-------------------------------------------------------|

| R = Readable bit     | W = Writable bit     | U = Unimplemented bit, read as '0'                    |

| u = Bit is unchanged | x = Bit is unknown   | -n/n = Value at POR and BOR/Value at all other Resets |

| '1' = Bit is set     | '0' = Bit is cleared |                                                       |

| bit 7-5 | Unimplemented: Read as '0'                                                                                                                                                                                          |

|---------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| bit 4   | NREF: ADC Negative Voltage Reference Selection bit<br>1 = VREF- is connected to external VREF-<br>0 = VREF- is connected to Vss                                                                                     |

| bit 3-2 | Unimplemented: Read as '0'                                                                                                                                                                                          |

| bit 1-0 | PREF: ADC Positive Voltage Reference Selection bits 11 = VREF+ is connected to internal Fixed Voltage Reference (FVR) module 10 = VREF+ is connected to external VREF+ 01 = Reserved 00 = VREF+ is connected to VDD |

| INCF                                   | Increment f                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | INCFSZ                                                                       | Increment f, skip if 0                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

|----------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Syntax:                                | INCF f {,d {,a}}                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | Syntax:                                                                      | INCFSZ f {,d {,a}}                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

| Operands:                              | $\begin{array}{l} 0 \leq f \leq 255 \\ d  \in  [0,1] \\ a  \in  [0,1] \end{array}$                                                                                                                                                                                                                                                                                                                                                                                                                                        | Operands:                                                                    | $\begin{array}{l} 0 \leq f \leq 255 \\ d  \in  [0,1] \\ a  \in  [0,1] \end{array}$                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

| Operation:                             | (f) + 1 $\rightarrow$ dest                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | Operation:                                                                   | (f) + 1 $\rightarrow$ dest,                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

| Status Affected:                       | C, DC, N, OV, Z                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |                                                                              | skip if result = 0                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

| Encoding:                              | 0010 10da ffff ff                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | Status Affected:                                                             | None                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

| Description:                           | The contents of register 'f' are                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | Encoding:                                                                    | 0011 11da ffff ffff                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

| Words:<br>Cycles:<br>Q Cycle Activity: | incremented. If 'd' is '0', the result is<br>placed in W. If 'd' is '1', the result is<br>placed back in register 'f' (default).<br>If 'a' is '0', the Access Bank is select<br>If 'a' is '1', the BSR is used to select<br>GPR bank.<br>If 'a' is '0' and the extended instruct<br>set is enabled, this instruction oper<br>in Indexed Literal Offset Addressing<br>mode whenever $f \le 95$ (5Fh). See S<br>tion 41.2.3 "Byte-Oriented and B<br>Oriented Instructions in Indexed<br>eral Offset Mode" for details.<br>1 | e<br>5<br>-                                                                  | The contents of register 'f' are<br>incremented. If 'd' is '0', the result is<br>placed in W. If 'd' is '1', the result is<br>placed back in register 'f' (default).<br>If the result is '0', the next instruction,<br>which is already fetched, is discarded<br>and a NOP is executed instead, making<br>it a 2-cycle instruction.<br>If 'a' is '0', the Access Bank is selected<br>If 'a' is '0', the ASR is used to select the<br>GPR bank.<br>If 'a' is '1', the BSR is used to select the<br>GPR bank.<br>If 'a' is '0' and the extended instruction<br>set is enabled, this instruction operates<br>in Indexed Literal Offset Addressing<br>mode whenever f $\leq$ 95 (5Fh). See Sec-<br>tion 41.2.3 "Byte-Oriented and Bit-<br>Oriented Instructions in Indexed Lit-<br>eral Offset Mode" for details. |

| Q1<br>Decode                           | Q2 Q3 Q4<br>Read Process Write                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | Words:                                                                       | 1                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

| Example:                               | INCF CNT, 1, 0                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | Cycles:                                                                      | 1(2)<br><b>Note:</b> 3 cycles if skip and followed<br>by a 2-word instruction.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

| Before Instru                          |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | Q Cycle Activity:                                                            |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

| CNT                                    | = FFh                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | Q1                                                                           | Q2 Q3 Q4                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

| Z<br>C                                 | = 0<br>= ?                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | Decode                                                                       | Read Process Write to                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

| DC                                     | = ?                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |                                                                              | register 'f' Data destination                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

| After Instruct<br>CNT                  | ion<br>= 00h                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | If skip:                                                                     | 02 02 04                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

| Z                                      | = 1                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | Q1<br>No                                                                     | Q2 Q3 Q4<br>No No No                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |