Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

#### Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

E·XF

| Details                    |                                                                              |

|----------------------------|------------------------------------------------------------------------------|

| Product Status             | Active                                                                       |

| Core Processor             | PIC                                                                          |

| Core Size                  | 8-Bit                                                                        |

| Speed                      | 64MHz                                                                        |

| Connectivity               | I <sup>2</sup> C, LINbus, SPI, UART/USART                                    |

| Peripherals                | Brown-out Detect/Reset, DMA, HLVD, POR, PWM, WDT                             |

| Number of I/O              | 44                                                                           |

| Program Memory Size        | 128KB (64K x 16)                                                             |

| Program Memory Type        | FLASH                                                                        |

| EEPROM Size                | 1K x 8                                                                       |

| RAM Size                   | 8K x 8                                                                       |

| Voltage - Supply (Vcc/Vdd) | 1.8V ~ 3.6V                                                                  |

| Data Converters            | A/D 43x12b; D/A 1x5b                                                         |

| Oscillator Type            | Internal                                                                     |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                            |

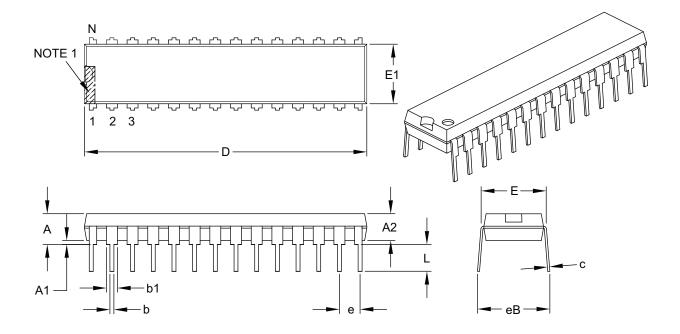

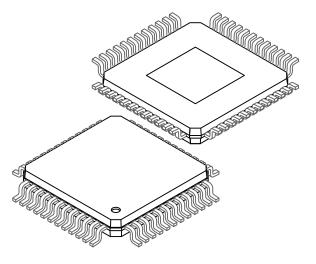

| Mounting Type              | Surface Mount                                                                |

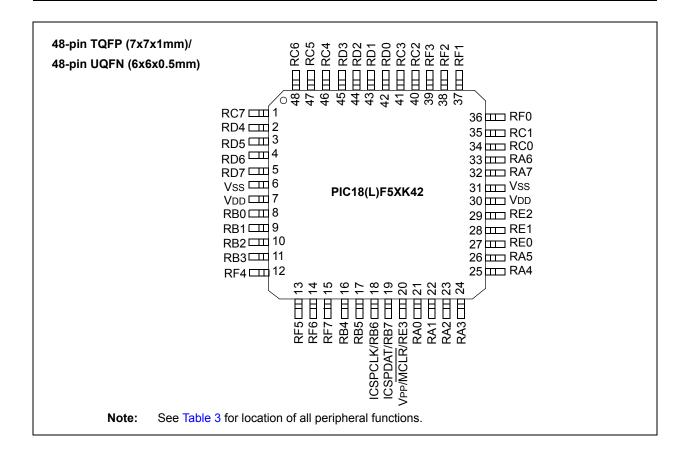

| Package / Case             | 48-TQFP Exposed Pad                                                          |

| Supplier Device Package    | 48-TQFP-EP (7x7)                                                             |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/pic18lf57k42t-i-pt |

|                            |                                                                              |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

#### REGISTER 13-2: NVMCON2: NONVOLATILE MEMORY CONTROL 2 REGISTER

| R/W-0            | R/W-0        | R/W-0               | R/W-0 | R/W-0            | R/W-0            | R/W-0    | R/W-0 |  |  |

|------------------|--------------|---------------------|-------|------------------|------------------|----------|-------|--|--|

|                  | NVMCON2<7:0> |                     |       |                  |                  |          |       |  |  |

| bit 7            |              |                     |       |                  |                  |          | bit 0 |  |  |

|                  |              |                     |       |                  |                  |          |       |  |  |

| Legend:          |              |                     |       |                  |                  |          |       |  |  |

| R = Readable b   | bit          | W = Writable bit    | t     | U = Unimplen     | nented bit, read | 1 as '0' |       |  |  |

| x = Bit is unkno | own          | '0' = Bit is cleare | ed    | '1' = Bit is set |                  |          |       |  |  |

| -n = Value at P  | OR           |                     |       |                  |                  |          |       |  |  |

#### bit 7-0 NVMCON2<7:0>:

#### Refer to Section 13.1.4 "NVM Unlock Sequence".

**Note 1:** This register always reads zeros, regardless of data written.

#### Register 13-3: NVMADRL: Data EEPROM Memory Address Low

| R/W-0/0     | R/W-0/0 | R/W-0/0 | R/W-0/0 | R/W-0/0 | R/W-0/0 | R/W-0/0 | R/W-0/0 |

|-------------|---------|---------|---------|---------|---------|---------|---------|

| ADR<7:0>    |         |         |         |         |         |         |         |

| bit 7 bit 0 |         |         |         |         |         |         |         |

|             |         |         |         |         |         |         |         |

| Legend:            |                      |                                    |  |

|--------------------|----------------------|------------------------------------|--|

| R = Readable bit   | W = Writable bit     | U = Unimplemented bit, read as '0' |  |

| x = Bit is unknown | '0' = Bit is cleared | '1' = Bit is set                   |  |

| -n = Value at POR  |                      |                                    |  |

#### bit 7-0 ADR<7:0>: EEPROM Read Address bits

## REGISTER 13-4: NVMADRH: DATA EEPROM MEMORY ADDRESS HIGH<sup>(1)</sup>

| U-0   | U-0 | U-0 | U-0 | U-0 | U-0 | R/W-0/0 | R/W-0/0 |

|-------|-----|-----|-----|-----|-----|---------|---------|

| —     | —   | —   | —   | _   | _   | ADR     | <9:8>   |

| bit 7 |     |     |     |     |     |         | bit 0   |

| Legend:            |                      |                                    |  |

|--------------------|----------------------|------------------------------------|--|

| R = Readable bit   | W = Writable bit     | U = Unimplemented bit, read as '0' |  |

| x = Bit is unknown | '0' = Bit is cleared | '1' = Bit is set                   |  |

| -n = Value at POR  |                      |                                    |  |

bit 7-2 Unimplemented: Read as '0'

bit 1-0 ADR<9:8>: EEPROM Read Address bits

**Note 1:** The NVMADRH register is not implemented on PIC18(L)F45/55K42.

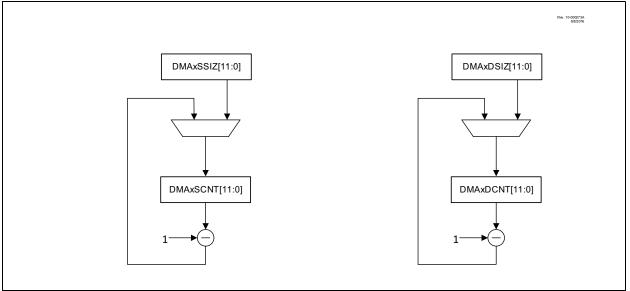

#### FIGURE 15-3: DMA COUNTERS BLOCK DIAGRAM

Table 15-2 has a few examples of configuring DMAMessage sizes.

| TABLE 15-2: | EXAMPLE | E MESSAGE SIZE | TABLE |      |

|-------------|---------|----------------|-------|------|

| Operat      | ion     | Example        | SCNT  | DONT |

| Operation                                | Example           | SCNT | DCNT                                                          | Comments                                                                                  |

|------------------------------------------|-------------------|------|---------------------------------------------------------------|-------------------------------------------------------------------------------------------|

| Read from single SFR<br>location to RAM  | U1RXB             | 1    | Ν                                                             | N equals the number of bytes desired in the destination buffer. N >= 1.                   |

| Write to single SFR location<br>from RAM | U1TXB             | N    | 1 N equals the number of bytes desired source buffer. N >= 1. |                                                                                           |

|                                          | ADRES[H:L]        | 2    | 2*N                                                           | N equals the number of ADC results to be stored in memory. N>= 1                          |

| Read from multiple SFR location          | TMR1[H:L]         | 2    | 2*N                                                           | N equals the number of TMR1 Acquisition results to be stored in memory. N>= 1             |

|                                          | SMT1CPR[U:H:L]    | 3    | 3*N                                                           | N equals the number of Capture Pulse Width measurements to be stored in memory. N>= 1     |

| Write to Multiple SFR regis-             | PWMDC[H:L]        | 2*N  | 2                                                             | N equals the number of PWM duty cycle val-<br>ues to be loaded from a memory table. N>= 1 |

| ters                                     | All ADC registers | N*31 | 31                                                            | Using the DMA to transfer a complete ADC context from RAM to the ADC registers.N>= 1      |

#### REGISTER 15-21: DMAxDCNTH: DMAx DESTINATION COUNT HIGH REGISTER

| U-0   | U-0 | U-0 | U-0 | R-0 | R-0   | R-0   | R-0   |

|-------|-----|-----|-----|-----|-------|-------|-------|

| —     | —   | —   | —   |     | DCNT< | 11:8> |       |

| bit 7 |     |     |     |     |       |       | bit 0 |

## Legend:

| Legenu.                                           |                  |                        |                                            |

|---------------------------------------------------|------------------|------------------------|--------------------------------------------|

| R = Readable bit                                  | W = Writable bit | U = Unimplemented bit, | read as '0'                                |

| -n/n = Value at POR and<br>BOR/Value at all other | 1 = bit is set   | 0 = bit is cleared     | x = bit is unknown<br>u = bit is unchanged |

| Resets                                            |                  |                        | C C                                        |

#### bit 7-4 Unimplemented: Read as '0'

bit 3-0 DCNT<11:8>: Current Destination Byte Count

#### REGISTER 15-22: DMAxSIRQ: DMAx START INTERRUPT REQUEST SOURCE SELECTION REGISTER

| U-0   | R/W-0/0 | R/W-0/0 | R/W-0/0 | R/W-0/0   | R/W-0/0 | R/W-0/0 | R/W-0/0 |

|-------|---------|---------|---------|-----------|---------|---------|---------|

| _     |         |         |         | SIRQ<6:0> |         |         |         |

| bit 7 |         |         |         |           |         |         | bit 0   |

| Legend:                                                     |                  |                        |                                            |

|-------------------------------------------------------------|------------------|------------------------|--------------------------------------------|

| R = Readable bit                                            | W = Writable bit | U = Unimplemented bit, | read as '0'                                |

| -n/n = Value at POR<br>and BOR/Value at all<br>other Resets | 1 = bit is set   | 0 = bit is cleared     | x = bit is unknown<br>u = bit is unchanged |

#### bit 7 Unimplemented: Read as '0'

bit 6-0 **SIRQ<6:0>:** DMAx Start Interrupt Request Source Selection bits Please refer to Table 15-2 for more information.

#### REGISTER 15-23: DMAxAIRQ: DMAx ABORT INTERRUPT REQUEST SOURCE SELECTION REGISTER

| U-0   | R/W-0/0 | R/W-0/0 | R/W-0/0 | R/W-0/0   | R/W-0/0 | R/W-0/0 | R/W-0/0 |

|-------|---------|---------|---------|-----------|---------|---------|---------|

| _     |         |         |         | AIRQ<6:0> |         |         |         |

| bit 7 |         |         |         |           |         |         | bit 0   |

| Legend:                                                     |                  |                                    |                                            |  |  |  |

|-------------------------------------------------------------|------------------|------------------------------------|--------------------------------------------|--|--|--|

| R = Readable bit                                            | W = Writable bit | U = Unimplemented bit, read as '0' |                                            |  |  |  |

| -n/n = Value at POR<br>and BOR/Value at all<br>other Resets | 1 = bit is set   | 0 = bit is cleared                 | x = bit is unknown<br>u = bit is unchanged |  |  |  |

bit 7 Unimplemented: Read as '0'

bit 6-0 **AIRQ<6:0>:** DMAx Interrupt Request Source Selection bits Please refer to Table 15-2 for more information.

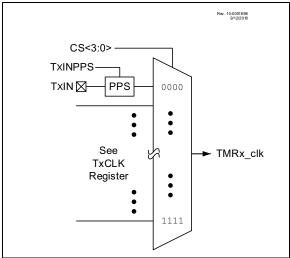

#### FIGURE 22-2: TIMER2 CLOCK SOURCE BLOCK DIAGRAM

## 22.1 Timer2 Operation

Timer2 operates in three major modes:

- Free Running Period

- One-Shot

- Monostable

Within each mode there are several options for starting, stopping, and reset. Table 22-1 lists the options.

In all modes the T2TMR count register is incremented on the rising edge of the clock signal from the programmable prescaler. When T2TMR equals T2PR then a high level is output to the postscaler counter. T2TMR is cleared on the next clock input.

An external signal from hardware can also be configured to gate the timer operation or force a T2TMR count Reset. In gate modes, the counter stops when the gate is disabled and resumes when the gate is enabled. In Reset modes the T2TMR count is reset on either the level or edge from the external source.

The T2TMR and T2PR registers are both directly readable and writable. The T2TMR register is cleared and the T2PR register initializes to FFh on any device Reset. Both the prescaler and postscaler counters are cleared on the following events:

- · a write to the T2TMR register

- · a write to the TxCON register

- any device Reset

- · External Reset Source event that resets the timer.

Note: T2TMR is not cleared when TxCON is written.

## 22.1.1 FREE RUNNING PERIOD MODE

The value of T2TMR is compared to that of the Period register, T2PR, on each clock cycle. When the two values match, the comparator resets the value of T2TMR to 00h on the next cycle and increments the

output postscaler counter. When the postscaler count equals the value in the OUTPS bits of the TxCON register, then a one clock period wide pulse occurs on the T2TMR\_postscaled output, and the postscaler count is cleared.

## 22.1.2 ONE-SHOT MODE

The One-Shot mode is identical to the Free Running Period mode except that the ON bit is cleared and the timer is stopped when T2TMR matches T2PR and will not restart until the T2ON bit is cycled off and on. Postscaler OUTPS values other than 0 are meaningless in this mode because the timer is stopped at the first period event and the postscaler is reset when the timer is restarted.

## 22.1.3 MONOSTABLE MODE

Monostable modes are similar to One-Shot modes except that the ON bit is not cleared and the timer can be restarted by an external Reset event.

## 22.2 Timer2 Output

The Timer2 module's primary output is T2TMR\_postscaled, which pulses for a single T2TMR\_clk period when the postscaler counter matches the value in the OUTPS bits of the TxCON register. The T2PR postscaler is incremented each time the T2TMR value matches the T2PR value. This signal can be selected as an input to several other input modules.

Timer2 is also used by the CCP module for pulse generation in PWM mode. Both the actual T2TMR value as well as other internal signals are sent to the CCP module to properly clock both the period and pulse width of the PWM signal. See Section 23.0 "Capture/Compare/PWM Module" for more details on setting up Timer2 for use with the CCP, as well as the timing diagrams in Section 22.5 "Operation Examples" for examples of how the varying Timer2 modes affect CCP PWM output.

## 22.3 External Reset Sources

In addition to the clock source, the Timer2 also takes in an external Reset source. This external Reset source is selected for Timer2, Timer4, and Timer6 with the T2RST, T4RST, and T6RST registers, respectively. This source can control starting and stopping of the timer, as well as resetting the timer, depending on which mode the timer is in. The mode of the timer is controlled by the MODE bits of the T2HLT register. Edge Triggered modes require six Timer clock periods between external triggers. Level Triggered modes require the triggering level to be at least three Timer clock periods long. External triggers are ignored while in Debug Freeze mode.

## 23.3.1 CCPx PIN CONFIGURATION

The software must configure the CCPx pin as an output by clearing the associated TRIS bit and defining the appropriate output pin through the RxyPPS registers. See **Section 17.0 "Peripheral Pin Select (PPS) Module"** for more details.

Note: Clearing the CCPxCON register will force the CCPx compare output latch to the default low level. This is not the PORT I/O data latch.

#### 23.3.2 TIMER1 MODE RESOURCE

In Compare mode, Timer1 must be running in either Timer mode or Synchronized Counter mode. The compare operation may not work in Asynchronous Counter mode.

See Section 21.0 "Timer1/3/5 Module with Gate Control" for more information on configuring Timer1.

Note: Clocking Timer1 from the system clock (Fosc) should not be used in Compare mode. In order for Compare mode to recognize the trigger event on the CCPx pin, TImer1 must be clocked from the instruction clock (Fosc/4) or from an external clock source.

## 23.3.3 AUTO-CONVERSION TRIGGER

All CCPx modes set the CCP interrupt flag (CCPxIF). When this flag is set and a match occurs, an autoconversion trigger can take place if the CCP module is selected as the conversion trigger source.

Refer to **Section 36.2.5 "Auto-Conversion Trigger"** for more information.

Note: Removing the match condition by changing the contents of the CCPRxH and CCPRxL register pair, between the clock edge that generates the Autoconversion Trigger and the clock edge that generates the Timer1 Reset, will preclude the Reset from occurring

## 23.3.4 COMPARE DURING SLEEP

Since FOSC is shut down during Sleep mode, the Compare mode will not function properly during Sleep, unless the timer is running. The device will wake on interrupt (if enabled).

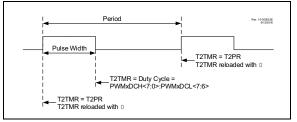

#### 23.4 PWM Overview

Pulse-Width Modulation (PWM) is a scheme that provides power to a load by switching quickly between fully ON and fully OFF states. The PWM signal resembles a square wave where the high portion of the signal is considered the ON state and the low portion of the signal is considered the OFF state. The high portion, also known as the pulse width, can vary in time and is defined in steps. A larger number of steps applied, which lengthens the pulse width, also supplies more power to the load. Lowering the number of steps applied, which shortens the pulse width, supplies less power. The PWM period is defined as the duration of one complete cycle or the total amount of on and off time combined.

PWM resolution defines the maximum number of steps that can be present in a single PWM period. A higher resolution allows for more precise control of the pulsewidth time and in turn the power that is applied to the load.

The term duty cycle describes the proportion of the on time to the off time and is expressed in percentages, where 0% is fully off and 100% is fully on. A lower duty cycle corresponds to less power applied and a higher duty cycle corresponds to more power applied.

Figure 23-3 shows a typical waveform of the PWM signal.

#### 23.4.1 STANDARD PWM OPERATION

The standard PWM mode generates a Pulse-Width Modulation (PWM) signal on the CCPx pin with up to ten bits of resolution. The period, duty cycle, and resolution are controlled by the following registers:

- T2PR registers

- T2CON registers

- CCPRxL and CCPRxH registers

- CCPxCON registers

It is required to have Fosc/4 as the clock input to TMR2/4/6 for correct PWM operation. Figure 23-4 shows a simplified block diagram of PWM operation.

Note: The corresponding TRIS bit must be cleared to enable the PWM output on the CCPx pin.

#### FIGURE 23-3: CCP PWM OUTPUT SIGNAL

## REGISTER 25-7: SMT1TMRL: SMT TIMER REGISTER – LOW BYTE

| R/W-0/0          | R/W-0/0 | R/W-0/0           | R/W-0/0 | R/W-0/0                                               | R/W-0/0          | R/W-0/0  | R/W-0/0 |  |

|------------------|---------|-------------------|---------|-------------------------------------------------------|------------------|----------|---------|--|

|                  |         |                   | SMT1T   | MR<7:0>                                               |                  |          |         |  |

| bit 7            |         |                   |         |                                                       |                  |          | bit 0   |  |

|                  |         |                   |         |                                                       |                  |          |         |  |

| Legend:          |         |                   |         |                                                       |                  |          |         |  |

| R = Readable I   | bit     | W = Writable I    | bit     | U = Unimpler                                          | nented bit, read | d as '0' |         |  |

| u = Bit is uncha | anged   | x = Bit is unkn   | nown    | -n/n = Value at POR and BOR/Value at all other Resets |                  |          |         |  |

| '1' = Bit is set |         | '0' = Bit is clea | ared    |                                                       |                  |          |         |  |

bit 7-0 SMT1TMR<7:0>: Significant bits of the SMT Counter – Low Byte

#### REGISTER 25-8: SMT1TMRH: SMT TIMER REGISTER – HIGH BYTE

| R/W-0/0 |

|---------|---------|---------|---------|---------|---------|---------|---------|

|         |         |         | SMT1TM  | R<15:8> |         |         |         |

| bit 7   |         |         |         |         |         |         | bit 0   |

| Legend:              |                      |                                                       |

|----------------------|----------------------|-------------------------------------------------------|

| R = Readable bit     | W = Writable bit     | U = Unimplemented bit, read as '0'                    |

| u = Bit is unchanged | x = Bit is unknown   | -n/n = Value at POR and BOR/Value at all other Resets |

| '1' = Bit is set     | '0' = Bit is cleared |                                                       |

bit 7-0 SMT1TMR<15:8>: Significant bits of the SMT Counter – High Byte

#### REGISTER 25-9: SMT1TMRU: SMT TIMER REGISTER – UPPER BYTE

| R/W-0/0         | R/W-0/0                         | R/W-0/0         | R/W-0/0 | R/W-0/0                            | R/W-0/0       | R/W-0/0          | R/W-0/0      |  |  |

|-----------------|---------------------------------|-----------------|---------|------------------------------------|---------------|------------------|--------------|--|--|

|                 |                                 |                 | SMT1TM  | R<23:16>                           |               |                  |              |  |  |

| bit 7           |                                 |                 |         |                                    |               |                  | bit 0        |  |  |

|                 |                                 |                 |         |                                    |               |                  |              |  |  |

| Legend:         |                                 |                 |         |                                    |               |                  |              |  |  |

| R = Readable    | = Readable bit W = Writable bit |                 |         | U = Unimplemented bit, read as '0' |               |                  |              |  |  |

| u = Bit is unch | anged                           | x = Bit is unkr | nown    | -n/n = Value a                     | at POR and BC | R/Value at all o | other Resets |  |  |

bit 7-0 SMT1TMR<23:16>: Significant bits of the SMT Counter – Upper Byte

'0' = Bit is cleared

© 2017 Microchip Technology Inc.

'1' = Bit is set

## 31.2.2.4 Receive Framing Error

Each character in the receive FIFO buffer has a corresponding framing error flag bit. A framing error indicates that the Stop bit was not seen at the expected time. The framing error flag is accessed via the FERIF bit in the UxERRIR register. The FERIF bit represents the frame status of the top unread character of the receive FIFO. Therefore, the FERIF bit must be read before reading UxRXB.

The FERIF bit is read-only and only applies to the top unread character of the receive FIFO. A framing error (FERIF = 1) does not preclude reception of additional characters. It is neither necessary nor possible to clear the FERIF bit directly. Reading the next character from the FIFO buffer will advance the FIFO to the next character and the next corresponding framing error.

The FERIF bit is cleared when the character at the top of the FIFO does not have a framing error or when all bytes in the receive FIFO have been read. Clearing the ON bit resets the receive FIFO, thereby also clearing the FERIF bit.

A framing error will generate a summary UxERR interrupt when the FERIE bit in the UxERRIE register is set. The summary error is reset when the FERIF bit of the top of the FIFO is '0' or when all FIFO characters have been retrieved.

When FERIE is set, UxRXIF interrupts are suppressed when FERIF is '1'.

## 31.2.2.5 Receiver Parity Modes

Even and odd parity is automatically detected when the MODE<3:0> bits are set to '0011' and '0010', respectively. Parity modes receive eight data bits and one parity bit for a total of nine bits for each character. The PERIF bit in the UXERRIR register represents the parity error of the top unread character of the receive FIFO rather than the parity bit itself. The parity error must be read before reading the UXRXB register advances the FIFO.

A parity error will generate a summary UxERR interrupt when the PERIE bit in the UxERRIE register is set. The summary error is reset when the PERIF bit of the top of the FIFO is '0' or when all FIFO characters have been retrieved.

When PERIE is set, UxRXIF interrupts are suppressed when PERIF is '1'.

## 31.2.2.6 Receive FIFO Overflow

When more characters are received than the receive FIFO can hold, the RXFOIF bit in the UxERRIR register is set. The character causing the overflow condition is discarded. The RUNOVF bit in the UxCON2 register determines how the receive circuit responds to characters while the overflow condition persists. When RUNOVF is set, the receive shifter stays synchronized to the incoming data stream by responding to Start, data, and Stop bits. However, all received bytes not already in the FIFO are discarded. When RUNOVF is cleared, the receive shifter ceases operation and Start. data, and Stop bits are ignored. The receive overflow condition is cleared by reading the UxRXB register and clearing the RXFOIF bit. If the UxRXB register is not read to open a space in the FIFO, the next character received will be discarded and cause another overflow condition.

A receive overflow error will generate a summary UxEIF interrupt when the RXFOIE bit in the UxERRIE register is set.

31.2.2.7 Asynchronous Reception Setup

- Initialize the UxBRGH, UxBRGL register pair and the BRGS bit to achieve the desired baud rate (see Section 31.17 "UART Baud Rate Generator (BRG)").

- 2. Configure the RXPPS register for the desired RX pin

- 3. Clear the ANSEL bit for the RX pin (if applicable).

- 4. Set the MODE<3:0> bits to the desired asynchronous mode.

- 5. Set the RXPOL bit if the data stream is inverted.

- 6. Enable the serial port by setting the ON bit.

- 7. If interrupts are desired, set the UxRXIE bit in the PIEx register and the GIE bits in the INTCON0 register.

- 8. Enable reception by setting the RXEN bit.

- 9. The UxRXIF interrupt flag bit will be set when a character is transferred from the RSR to the receive buffer. An interrupt will be generated if the UxRXIE interrupt enable bit is also set.

- 10. Read the UxERRIR register to get the error flags.

- 11. Read the UxRXB register to get the received byte.

- 12. If an overrun occurred, clear the RXFOIF bit.

## 32.3.3 TRANSMIT AND RECEIVE FIFOS

The transmission and reception of data from the SPI module is handled by two FIFOs, one for reception and one for transmission (addressed by the SFRs SPIxRXB and SPIxTXB, respectively.). The TXFIFO is written by software and is read by the SPI module to shift the data onto the SDO pin. The RXFIFO is written by the SPI module as it shifts in the data from the SDI pin and is read by software. Setting the CLRBF bit of SPIxSTATUS resets the occupancy for both FIFOs, emptying both buffers. The FIFOs are also reset by disabling the SPI module.

Note: TXFIFO occupancy and RXFIFO occupancy simply refer to the number of bytes that are currently being stored in each FIFO. These values are used in this chapter to illustrate the function of these FIFOs and are not directly accessible through software.

The SPIxRXB register addresses the receive FIFO and is read-only. Reading from this register will read from the first FIFO location that was written to by hardware and decrease the RXFIFO occupancy. If the FIFO is empty, reading from this register will instead return a value of zero and set the RXRE (Receive Buffer Read Error) bit of the SPIxSTATUS register. The RXRE bit must then be cleared in software in order to properly reflect the status of the read error. When RXFIFO is full, the RXBF bit of the SPIxSTATUS register will be set. When the device receives data on the SDI pin, the receive FIFO may be written to by hardware and the occupancy increased, depending on the mode and receiver settings, as summarized in Table 32-1.

The SPIxTXB register addresses the transmit FIFO and is write-only. Writing to the register will write to the first empty FIFO location and increase the occupancy. If the FIFO is full, writing to this register will not affect the data and will set the TXWE bit of the SPIxSTATUS register. When the TXFIFO is empty, the TXBE bit of SPIxSTATUS will be set. When a data transfer occurs, data may be read from the first FIFO location written to and the occupancy decreases, depending on mode and transmitter settings, as summarized in Table 32-1 and Section 32.6.1 "Slave Mode Transmit options".

## 32.3.4 LSB VS. MSB-FIRST OPERATION

Typically, SPI communication is output Most-Significant bit first, but some devices/buses may not conform to this standard. In this case, the LSBF bit may be used to alter the order in which bits are shifted out during the data exchange. In both Master and Slave mode, the LSBF bit of SPIxCON0 controls if data is shifted MSb or LSb first. Clearing the bit (default) configures the data to transfer MSb first, which is traditional SPI operation, while setting the bit configures the data to transfer LSb first.

#### 32.3.5 INPUT AND OUTPUT POLARITY BITS

SPIxCON1 has three bits that control the polarity of the SPI inputs and outputs. The SDIP bit controls the polarity of the SDI input, the SDOP bit controls the polarity of the SDO output, and the SSP bit controls the polarity of both the slave SS input and the master SS output. For all three bits, when the bit is clear, the input or output is active-high, and when the bit is set, the input or output is active-low. When the EN bit of SPIxCON0 is cleared, SS(out) and SCK(out) both revert to the inactive state dictated by their polarity bits. The SDO output state when the EN bit of SPIxCON0 is cleared is determined by several factors.

- When the associated TRIS bit for the SDO pin is cleared, and the SPI goes idle after a transmission, the SDO output will remain at the last bit level. The SDO pin will revert to the Idle state if EN is cleared.

- When the associated TRIS bit for the SDO pin is set, behavior varies in Slave and Master mode.

- In Slave mode, the SDO pin tri-states when:

- Slave Select is inactive,

- the EN bit of SPIxCON0 is cleared, or when

- the TXR bit of SPIxCON2 is cleared.

- In Master mode, the SDO pin tri-states when TXR = 0. When TXR = 1 and the SPI goes idle after a transmission, the SDO output will remain at the last bit level. The SDO pin will revert to the Idle state if EN is cleared.

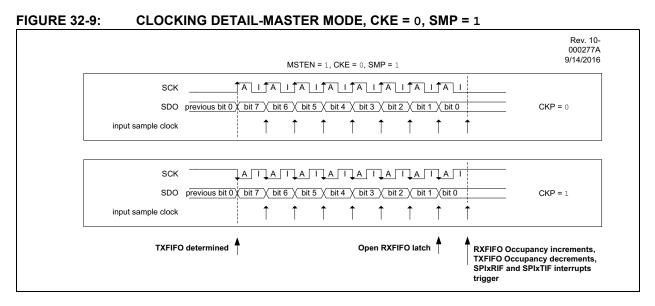

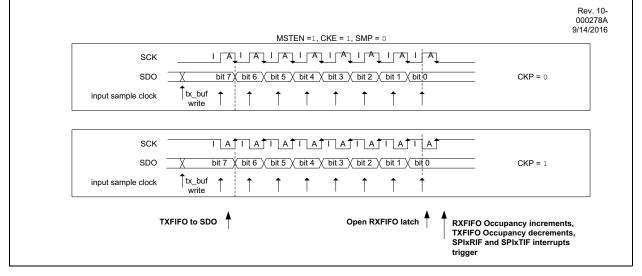

FIGURE 32-10: CLOCKING DETAIL-MASTER MODE, CKE = 1, SMP = 0

## 32.5.6.3 SCK Start-Up Delay

When starting an SPI data exchange, the master device sets the SS output (either through hardware or software) and then triggers the module to send data. These data triggers are synchronized to the clock selected by the SPIxCLK register before the first SCK pulse appears, usually requiring one or two clocks of the selected clock.

The SPI module includes synchronization delays on SCK generation specifically designed to ensure that the Slave Select output timing is correct, without requiring precision software timing loops.

When the value of the SPIxBAUD register is a small number (indicating higher SCK frequencies), the synchronization delay can be relatively long between setting SS and the first SCK. With larger values of SPIxBAUD (indicating lower SCK frequencies), this delay is much smaller and the first SCK can appear relatively quickly after SS is set.

By default, the SPI module inserts a ½ baud delay (half of the period of the clock selected by the SPIxCLK register) before the first SCK pulse. This allows for systems with a high SPIxBAUD value to have extra setup time before the first clock. Setting the FST bit in SPIxCON1 removes this additional delay, allowing systems with low SPIxBAUD values (and thus, long synchronization delays) to forego this unnecessary extra delay.

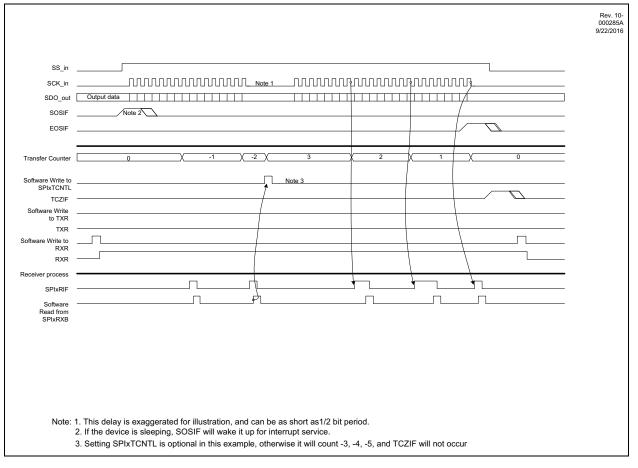

## 32.6.2 SLAVE MODE RECEIVE OPTIONS

The RXR bit controls the nature of receptions in slave mode. When RXR is set, the SDI input data will be stored in the RXFIFO if it is not full. If the RXFIFO is full, the RXOIF bit will be set to indicate an RXFIFO overflow error and the data is discarded. When RXR is cleared, all received data will be ignored and not stored in the RXFIFO (although it may still be used for transmission if TXFIFO is empty). Figure 32-11 shows a typical slave mode communication, showing a case where the master writes two then three bytes, showing interrupts as well as the behavior of the transfer counter in slave mode (see Section 32.4.3 "Transfer Counter in Slave mode" for more details on tSection 32.8 "SPI Interrupts" he transfer counter in slave mode as well as Section X.8 for more information on interrupts).

FIGURE 32-11: SPI SLAVE MODE OPERATION – INTERRUPT-DRIVEN, MASTER WRITES 2+3 BYTES

#### 33.5.11 MASTER TRANSMISSION IN 10-BIT ADDRESSING MODE

This section describes the sequence of events for the  $I^2C$  module configured as an  $I^2C$  master in 10-bit Addressing mode and is transmitting data. Figure 33-21 is used as a visual reference for this description

1. If ABD = 0; i.e., Address buffers are enabled

Master software loads number of bytes to be transmitted in one sequence in I2CxCNT, high address byte of slave address in I2CxADB1 with R/W = 0, low address byte in I2CxADB0 and the first byte of data in I2CxTXB. Master software has to set the Start (S) bit to initiate communication.

If ABD = 1; i.e., Address buffers are disabled

Master software loads the number of bytes to be transmitted in one sequence in I2CxCNT and the high address byte of the slave address with R/W = 0 into the I2CxTXB register. Writing to the I2CxTXB will assert the start condition on the bus and sets the S bit. Software writes to the S bit are ignored in this case.

- 2. Master hardware waits for BFRE bit to be set; then shifts out the start and high address and waits for acknowledge.

- 3. If NACK, master hardware sends Stop.

- 4. If ABD = 0; i.e., Address buffer are enabled

If ACK, master hardware sends the low address byte from I2CxADB0.

If ABD = 1; i.e., Address buffer are disabled

If ACK, master hardware sets TXIF and MDR bits and the software has to write the low address byte into I2CxTXB. Writing to I2CxTXB sends the low address on the bus.

- If TXBE = 1 and I2CxCNT! = 0, I2CxTXIF and MDR bits are set. Clock is stretched on 8th falling SCL edge until master software writes next data byte to I2CxTXB.

- Master hardware sends ninth SCL pulse for ACK from slave and loads the shift register from I2CxTXB. I2CxCNT is decremented.

- 7. If slave sends a NACK, master hardware sends Stop and ends transmission.

- If slave sends an ACK, master hardware outputs data in the shift register on SDA. I2CxCNT value is checked on the 8th falling SCL edge. If I2CxCNT = 0; master hardware sends 9th SCL pulse for ACK and CNTIF is set.

- 9. If I2CxCNT! = 0; go to step 5.

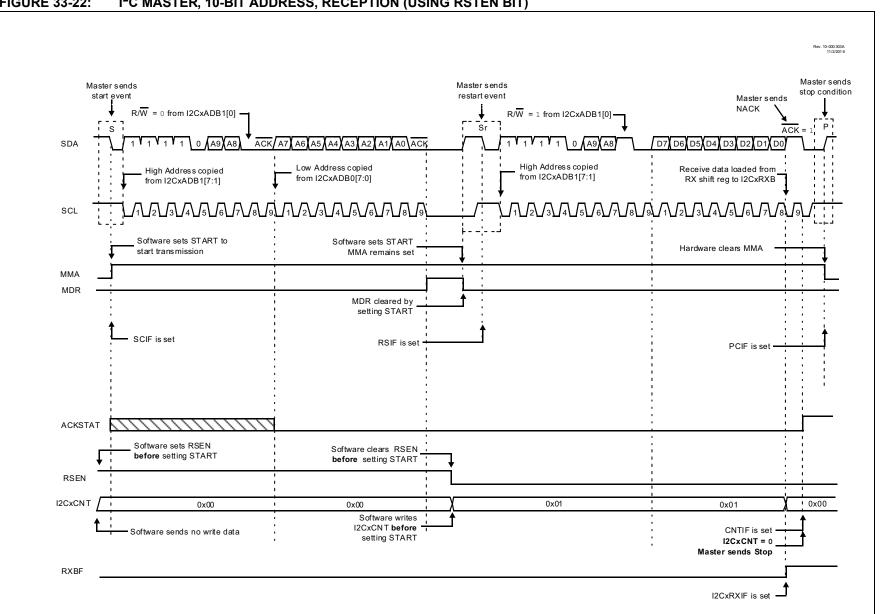

## FIGURE 33-22: I<sup>2</sup>C MASTER, 10-BIT ADDRESS, RECEPTION (USING RSTEN BIT)

© 2016-2017 Microchip Technology Inc

| RLNCF                          | Rotate Le                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | eft f (No Car                                                                                                   | ry)                                                                                                                                                                                                      |  |  |  |  |  |  |  |

|--------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|--|--|--|

| Syntax:                        | RLNCF                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | f {,d {,a}}                                                                                                     |                                                                                                                                                                                                          |  |  |  |  |  |  |  |

| Operands:                      | $\begin{array}{l} 0 \leq f \leq 255 \\ d  \in  [0,1] \\ a  \in  [0,1] \end{array}$                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |                                                                                                                 |                                                                                                                                                                                                          |  |  |  |  |  |  |  |

| Operation:                     |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | $(f < n >) \rightarrow dest < n + 1 >,$<br>$(f < 7 >) \rightarrow dest < 0 >$                                   |                                                                                                                                                                                                          |  |  |  |  |  |  |  |

| Status Affected:               | N, Z                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | N, Z                                                                                                            |                                                                                                                                                                                                          |  |  |  |  |  |  |  |

| Encoding:                      | 0100                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | 0100 01da ffff ffff                                                                                             |                                                                                                                                                                                                          |  |  |  |  |  |  |  |

| Description:                   | one bit to the stored back of the store ba | and the extend<br>led, this instruc-<br>Literal Offset $\lambda$<br>never f $\leq$ 95 (5<br>" <b>Byte-Orien</b> | '0', the result<br>, the result is<br>(default).<br>nk is selected.<br>d to select the<br>led instruction<br>ction operates<br>Addressing<br>(Fh). See Sec-<br>ted and Bit-<br>n Indexed Lit-<br>etails. |  |  |  |  |  |  |  |

| Words:                         | 1                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |                                                                                                                 |                                                                                                                                                                                                          |  |  |  |  |  |  |  |

| Cycles:                        | 1                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |                                                                                                                 |                                                                                                                                                                                                          |  |  |  |  |  |  |  |

| Q Cycle Activity:              |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |                                                                                                                 |                                                                                                                                                                                                          |  |  |  |  |  |  |  |

| Q1                             | Q2                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | Q3                                                                                                              | Q4                                                                                                                                                                                                       |  |  |  |  |  |  |  |

| Decode                         | Read<br>register 'f'                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | Process<br>Data                                                                                                 | Write to destination                                                                                                                                                                                     |  |  |  |  |  |  |  |

| Example:<br>Before Instruct    |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | REG, 1,                                                                                                         | 0                                                                                                                                                                                                        |  |  |  |  |  |  |  |

| REG<br>After Instructio<br>REG | = 1010 1<br>n<br>= 0101 0                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |                                                                                                                 |                                                                                                                                                                                                          |  |  |  |  |  |  |  |

| <u> </u>                                                                | Rotate Ri                                                     | -       | 0         | ,                |

|-------------------------------------------------------------------------|---------------------------------------------------------------|---------|-----------|------------------|

| Syntax:                                                                 | RRCF f{,                                                      | d {,a}} |           |                  |

| Operands:                                                               | $0 \le f \le 255$                                             |         |           |                  |

|                                                                         | d ∈ [0,1]                                                     |         |           |                  |

| <b>.</b>                                                                | a ∈ [0,1]                                                     |         |           |                  |

| Operation:                                                              | $(f < n >) \rightarrow de$                                    |         | >,        |                  |

|                                                                         | $(f<0>) \rightarrow C$<br>$(C) \rightarrow dest$              |         |           |                  |

| o                                                                       |                                                               | ~1~     |           |                  |

| Status Affected:                                                        | C, N, Z                                                       |         |           |                  |

| Encoding:                                                               | 0011                                                          | 00da    | ffff      | fffi             |

| Description:                                                            | The conten                                                    |         |           |                  |

|                                                                         | one bit to th                                                 |         |           |                  |

|                                                                         | flag. If 'd' is                                               |         |           |                  |

|                                                                         | lf 'd' is '1', t<br>register 'f' (                            |         | is placed | а раск іп        |

|                                                                         | If 'a' is '0', t                                              |         | s Bank is | s selecte        |

|                                                                         | lf 'a' is '1', t                                              |         |           |                  |

|                                                                         | GPR bank.                                                     |         |           |                  |

|                                                                         | <b>lf 'a' is '</b> 0' a                                       |         |           |                  |

|                                                                         | set is enabl                                                  | -       |           | •                |

|                                                                         | in Indexed                                                    |         |           |                  |

|                                                                         | mode when<br>tion 41.2.3                                      |         |           |                  |

|                                                                         | Oriented Ir                                                   |         |           |                  |

|                                                                         | eral Offset                                                   |         |           |                  |

|                                                                         | -► C                                                          | ► re    | gister f  | →                |

|                                                                         |                                                               |         | 5         |                  |

| Words:                                                                  | 1                                                             |         |           |                  |

| Cycles:                                                                 | 1                                                             |         |           |                  |

| Q Cycle Activity:                                                       |                                                               |         |           |                  |

| Q1                                                                      | Q2                                                            | Q3      |           | Q4               |

| Decode                                                                  | Read                                                          | Proce   |           | Write to         |

|                                                                         | register 'f'                                                  | Dat     |           |                  |

| Decode                                                                  |                                                               | Data    | a de      | estinatio        |

| Decode                                                                  | regioter i                                                    | Dat     | a de      | estinatio        |

|                                                                         | RRCF                                                          |         | a de      | estinatio        |

| Example:                                                                | RRCF                                                          |         |           | estinatio        |

|                                                                         | RRCF                                                          | REG,    |           | estinatio        |

| Example:<br>Before Instruc<br>REG<br>C                                  | RRCF<br>tion<br>= 1110 (<br>= 0                               | REG,    |           | estinatio        |

| Example:<br>Before Instruct<br>REG<br>C<br>After Instruction            | RRCF<br>tion<br>= 1110 C<br>= 0                               | REG,    |           | <u>estinatio</u> |