#### Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

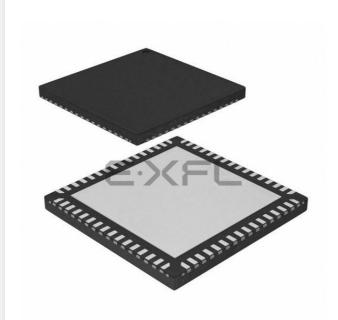

| Product Status             | Active                                                                    |

|----------------------------|---------------------------------------------------------------------------|

| Core Processor             | AVR                                                                       |

| Core Size                  | 8-Bit                                                                     |

| Speed                      | 16MHz                                                                     |

| Connectivity               | CANbus, I <sup>2</sup> C, SPI, UART/USART                                 |

| Peripherals                | Brown-out Detect/Reset, POR, PWM, WDT                                     |

| Number of I/O              | 53                                                                        |

| Program Memory Size        | 128KB (128K x 8)                                                          |

| Program Memory Type        | FLASH                                                                     |

| EEPROM Size                | 4K x 8                                                                    |

| RAM Size                   | 4K x 8                                                                    |

| Voltage - Supply (Vcc/Vdd) | 2.7V ~ 5.5V                                                               |

| Data Converters            | A/D 8x10b                                                                 |

| Oscillator Type            | Internal                                                                  |

| Operating Temperature      | -40°C ~ 125°C (TA)                                                        |

| Mounting Type              | Surface Mount                                                             |

| Package / Case             | 64-VFQFN Exposed Pad                                                      |

| Supplier Device Package    | 64-QFN (9x9)                                                              |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/at90can128-15mz |

|                            |                                                                           |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

# 1. Description

# 1.1 Comparison Between AT90CAN32, AT90CAN64 and AT90CAN128

AT90CAN32, AT90CAN64 and AT90CAN128 are all hardware and software compatible with each other, the only difference is the memory size.

| Device     | Flash      | EEPROM   | RAM      |

|------------|------------|----------|----------|

| AT90CAN32  | 32K Bytes  | 1K Byte  | 2K Bytes |

| AT90CAN64  | 64K Bytes  | 2K Bytes | 4K Bytes |

| AT90CAN128 | 128K Bytes | 4K Byte  | 4K Bytes |

# 1.2 Part Description

The AT90CAN32/64/128 is a low-power CMOS 8-bit microcontroller based on the AVR enhanced RISC architecture. By executing powerful instructions in a single clock cycle, the AT90CAN32/64/128 achieves throughputs approaching 1 MIPS per MHz allowing the system designer to optimize power consumption versus processing speed.

The AVR core combines a rich instruction set with 32 general purpose working registers. All 32 registers are directly connected to the Arithmetic Logic Unit (ALU), allowing two independent registers to be accessed in one single instruction executed in one clock cycle. The resulting architecture is more code efficient while achieving throughputs up to ten times faster than conventional CISC microcontrollers.

The AT90CAN32/64/128 provides the following features: 32K/64K/128K bytes of In-System Programmable Flash with Read-While-Write capabilities, 1K/2K/4K bytes EEPROM, 2K/4K/4K bytes SRAM, 53 general purpose I/O lines, 32 general purpose working registers, a CAN controller, Real Time Counter (RTC), four flexible Timer/Counters with compare modes and PWM, 2 USARTs, a byte oriented Two-wire Serial Interface, an 8-channel 10-bit ADC with optional differential input stage with programmable gain, a programmable Watchdog Timer with Internal Oscillator, an SPI serial port, IEEE std. 1149.1 compliant JTAG test interface, also used for accessing the On-chip Debug system and programming and five software selectable power saving modes.

The Idle mode stops the CPU while allowing the SRAM, Timer/Counters, SPI/CAN ports and interrupt system to continue functioning. The Power-down mode saves the register contents but freezes the Oscillator, disabling all other chip functions until the next interrupt or Hardware Reset. In Power-save mode, the asynchronous timer continues to run, allowing the user to maintain a timer base while the rest of the device is sleeping. The ADC Noise Reduction mode stops the CPU and all I/O modules except Asynchronous Timer and ADC, to minimize switching noise during ADC conversions. In Standby mode, the Crystal/Resonator Oscillator is running while the rest of the device is sleeping. This allows very fast start-up combined with low power consumption.

The device is manufactured using Atmel's high-density nonvolatile memory technology. The Onchip ISP Flash allows the program memory to be reprogrammed in-system through an SPI serial interface, by a conventional nonvolatile memory programmer, or by an On-chip Boot program running on the AVR core. The boot program can use any interface to download the application program in the application Flash memory. Software in the Boot Flash section will continue to run while the Application Flash section is updated, providing true Read-While-Write operation. By

The fast-access Register File contains  $32 \times 8$ -bit general purpose working registers with a single clock cycle access time. This allows single-cycle Arithmetic Logic Unit (ALU) operation. In a typical ALU operation, two operands are output from the Register File, the operation is executed, and the result is stored back in the Register File – in one clock cycle.

Six of the 32 registers can be used as three 16-bit indirect address register pointers for Data Space addressing – enabling efficient address calculations. One of the these address pointers can also be used as an address pointer for look up tables in Flash program memory. These added function registers are the 16-bit X-, Y-, and Z-register, described later in this section.

The ALU supports arithmetic and logic operations between registers or between a constant and a register. Single register operations can also be executed in the ALU. After an arithmetic operation, the Status Register is updated to reflect information about the result of the operation.

Program flow is provided by conditional and unconditional jump and call instructions, able to directly address the whole address space. Most AVR instructions have a single 16-bit word format. Every program memory address contains a 16- or 32-bit instruction.

Program Flash memory space is divided in two sections, the Boot Program section and the Application Program section. Both sections have dedicated Lock bits for write and read/write protection. The SPM (Store Program Memory) instruction that writes into the Application Flash memory section must reside in the Boot Program section.

During interrupts and subroutine calls, the return address Program Counter (PC) is stored on the Stack. The Stack is effectively allocated in the general data SRAM, and consequently the Stack size is only limited by the total SRAM size and the usage of the SRAM. All user programs must initialize the SP in the Reset routine (before subroutines or interrupts are executed). The Stack Pointer (SP) is read/write accessible in the I/O space. The data SRAM can easily be accessed through the five different addressing modes supported in the AVR architecture.

The memory spaces in the AVR architecture are all linear and regular memory maps.

A flexible interrupt module has its control registers in the I/O space with an additional Global Interrupt Enable bit in the Status Register. All interrupts have a separate Interrupt Vector in the Interrupt Vector table. The interrupts have priority in accordance with their Interrupt Vector position. The lower the Interrupt Vector address, the higher is the priority.

The I/O memory space contains 64 addresses for CPU peripheral functions as Control Registers, SPI, and other I/O functions. The I/O Memory can be accessed directly, or as the Data Space locations following those of the Register File, 0x20 - 0x5F. In addition, the AT90CAN32/64/128 has Extended I/O space from 0x60 - 0xFF in SRAM where only the ST/STS/STD and LD/LDS/LDD instructions can be used.

# 3.3 ALU – Arithmetic Logic Unit

The high-performance AVR ALU operates in direct connection with all the 32 general purpose working registers. Within a single clock cycle, arithmetic operations between general purpose registers or between a register and an immediate are executed. The ALU operations are divided into three main categories – arithmetic, logical, and bit-functions. Some implementations of the architecture also provide a powerful multiplier supporting both signed/unsigned multiplication and fractional format. See the "Instruction Set Summary" section for a detailed description.

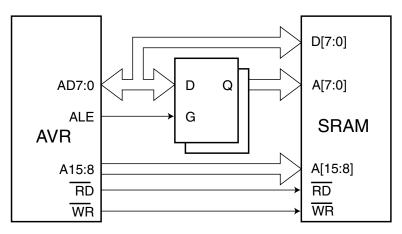

# 4.5.3 Address Latch Requirements

Due to the high-speed operation of the XRAM interface, the address latch must be selected with care for system frequencies above 8 MHz @ 4V and 4 MHz @ 2.7V. When operating at conditions above these frequencies, the typical old style 74HC series latch becomes inadequate. The External Memory Interface is designed in compliance to the 74AHC series latch. However, most latches can be used as long they comply with the main timing parameters. The main parameters for the address latch are:

- D to Q propagation delay  $(t_{PD})$ .

- Data setup time before G low  $(t_{SU})$ .

- Data (address) hold time after G low (<sub>TH</sub>).

The External Memory Interface is designed to guaranty minimum address hold time after G is asserted low of  $t_h = 5$  ns. Refer to  $t_{LAXX\_LD} / t_{LLAXX\_ST}$  in "Memory Programming" Tables 26-7 through Tables 26-14. The D-to-Q propagation delay ( $t_{PD}$ ) must be taken into consideration when calculating the access time requirement of the external component. The data setup time before G low ( $t_{SU}$ ) must not exceed address valid to ALE low ( $t_{AVLLC}$ ) minus PCB wiring delay (dependent on the capacitive load).

#### 4.5.4 Pull-up and Bus-keeper

The pull-ups on the AD7:0 ports may be activated if the corresponding Port register is written to one. To reduce power consumption in sleep mode, it is recommended to disable the pull-ups by writing the Port register to zero before entering sleep.

The XMEM interface also provides a bus-keeper on the AD7:0 lines. The bus-keeper can be disabled and enabled in software as described in "External Memory Control Register B – XMCRB" on page 33. When enabled, the bus-keeper will ensure a defined logic level (zero or one) on the AD7:0 bus when these lines would otherwise be tri-stated by the XMEM interface.

#### 4.5.5 Timing

External Memory devices have different timing requirements. To meet these requirements, the AT90CAN32/64/128 XMEM interface provides four different wait-states as shown in Table 4-4. It is important to consider the timing specification of the External Memory device before selecting the wait-state. The most important parameters are the access time for the external memory compared to the set-up requirement of the AT90CAN32/64/128. The access time for the External Memory is defined to be the time from receiving the chip select/address until the data of this

The following code example shows one assembly and one C function for turning off the WDT. The example assumes that interrupts are controlled (e.g. by disabling interrupts globally) so that no interrupts will occur during execution of these functions.

| Assembly Co    | ode Example <sup>(1)</sup>                         |

|----------------|----------------------------------------------------|

| WDT_off        | :                                                  |

| ; Wri          | te logical one to WDCE and WDE                     |

| ldi            | r16, (1< <wdce) (1<<wde)< th=""></wdce) (1<<wde)<> |

| sts            | WDTCR, r16                                         |

| ; Tur          | n off WDT                                          |

| ldi            | r16, (0< <wde)< th=""></wde)<>                     |

| sts            | WDTCR, r16                                         |

| ret            |                                                    |

| C Code Exa     | mple <sup>(1)</sup>                                |

| <b>void</b> WD | T_off( <b>void</b> )                               |

| {              |                                                    |

| /* Wr          | ite logical one to WDCE and WDE */                 |

| WDTCR          | = (1< <wdce) (1<<wde);<="" th=""  =""></wdce)>     |

| /* Tu          | rn off WDT */                                      |

| WDTCR          | = 0x00;                                            |

| }              |                                                    |

Note: 1. The example code assumes that the part specific header file is included.

# 7.4 Timed Sequences for Changing the Configuration of the Watchdog Timer

The sequence for changing configuration differs slightly between the two safety levels. Separate procedures are described for each level.

# 7.4.1 Safety Level 1

In this mode, the Watchdog Timer is initially disabled, but can be enabled by writing the WDE bit to 1 without any restriction. A timed sequence is needed when changing the Watchdog Time-out period or disabling an enabled Watchdog Timer. To disable an enabled Watchdog Timer, and/or changing the Watchdog Time-out, the following procedure must be followed:

- 1. In the same operation, write a logic one to WDCE and WDE. A logic one must be written to WDE regardless of the previous value of the WDE bit.

- 2. Within the next four clock cycles, in the same operation, write the WDE and WDP bits as desired, but with the WDCE bit cleared.

# 7.4.2 Safety Level 2

In this mode, the Watchdog Timer is always enabled, and the WDE bit will always read as one. A timed sequence is needed when changing the Watchdog Time-out period. To change the Watchdog Time-out, the following procedure must be followed:

- 1. In the same operation, write a logical one to WDCE and WDE. Even though the WDE always is set, the WDE must be written to one to start the timed sequence.

- 2. Within the next four clock cycles, in the same operation, write the WDP bits as desired, but with the WDCE bit cleared. The value written to the WDE bit is irrelevant.

# 8. Interrupts

This section describes the specifics of the interrupt handling as performed in AT90CAN32/64/128. For a general explanation of the AVR interrupt handling, refer to "Reset and Interrupt Handling" on page 15.

# 8.1 Interrupt Vectors in AT90CAN32/64/128

| Vector<br>No. | Program<br>Address <sup>(1)</sup> | Source       | Interrupt Definition                                                                 |

|---------------|-----------------------------------|--------------|--------------------------------------------------------------------------------------|

| 1             | 0x0000 <sup>(2)</sup>             | RESET        | External Pin, Power-on Reset, Brown-out Reset,<br>Watchdog Reset, and JTAG AVR Reset |

| 2             | 0x0002                            | INT0         | External Interrupt Request 0                                                         |

| 3             | 0x0004                            | INT1         | External Interrupt Request 1                                                         |

| 4             | 0x0006                            | INT2         | External Interrupt Request 2                                                         |

| 5             | 0x0008                            | INT3         | External Interrupt Request 3                                                         |

| 6             | 0x000A                            | INT4         | External Interrupt Request 4                                                         |

| 7             | 0x000C                            | INT5         | External Interrupt Request 5                                                         |

| 8             | 0x000E                            | INT6         | External Interrupt Request 6                                                         |

| 9             | 0x0010                            | INT7         | External Interrupt Request 7                                                         |

| 10            | 0x0012                            | TIMER2 COMP  | Timer/Counter2 Compare Match                                                         |

| 11            | 0x0014                            | TIMER2 OVF   | Timer/Counter2 Overflow                                                              |

| 12            | 0x0016                            | TIMER1 CAPT  | Timer/Counter1 Capture Event                                                         |

| 13            | 0x0018                            | TIMER1 COMPA | Timer/Counter1 Compare Match A                                                       |

| 14            | 0x001A                            | TIMER1 COMPB | Timer/Counter1 Compare Match B                                                       |

| 15            | 0x001C                            | TIMER1 COMPC | Timer/Counter1 Compare Match C                                                       |

| 16            | 0x001E                            | TIMER1 OVF   | Timer/Counter1 Overflow                                                              |

| 17            | 0x0020                            | TIMER0 COMP  | Timer/Counter0 Compare Match                                                         |

| 18            | 0x0022                            | TIMER0 OVF   | Timer/Counter0 Overflow                                                              |

| 19            | 0x0024                            | CANIT        | CAN Transfer Complete or Error                                                       |

| 20            | 0x0026                            | OVRIT        | CAN Timer Overrun                                                                    |

| 21            | 0x0028                            | SPI, STC     | SPI Serial Transfer Complete                                                         |

| 22            | 0x002A                            | USART0, RX   | USART0, Rx Complete                                                                  |

| 23            | 0x002C                            | USARTO, UDRE | USART0 Data Register Empty                                                           |

| 24            | 0x002E                            | USARTO, TX   | USART0, Tx Complete                                                                  |

| 25            | 0x0030                            | ANALOG COMP  | Analog Comparator                                                                    |

| 26            | 0x0032                            | ADC          | ADC Conversion Complete                                                              |

| 27            | 0x0034                            | EE READY     | EEPROM Ready                                                                         |

| 28            | 0x0036                            | TIMER3 CAPT  | Timer/Counter3 Capture Event                                                         |

Table 8-1.Reset and Interrupt Vectors

Table 9-19 and Table 9-20 relates the alternate functions of Port F to the overriding signals shown in Figure 9-5 on page 72.

| Signal Name | PF7/ADC7/TDI      | PF6/ADC6/TDO           | PF5/ADC5/TMS      | PF4/ADC4/TCK             |

|-------------|-------------------|------------------------|-------------------|--------------------------|

| PUOE        | JTAGEN            | JTAGEN                 | JTAGEN            | JTAGEN                   |

| PUOV        | JTAGEN            | JTAGEN                 | JTAGEN            | JTAGEN                   |

| DDOE        | JTAGEN            | JTAGEN                 | JTAGEN            | JTAGEN                   |

| DDOV        | 0                 | SHIFT_IR +<br>SHIFT_DR | 0                 | 0                        |

| PVOE        | JTAGEN            | JTAGEN                 | JTAGEN            | JTAGEN                   |

| PVOV        | 0                 | TDO                    | 0                 | 0                        |

| PTOE        | 0                 | 0                      | 0                 | 0                        |

| DIEOE       | JTAGEN +<br>ADC7D | JTAGEN +<br>ADC6D      | JTAGEN +<br>ADC5D | JTAGEN <b>+</b><br>ADC4D |

| DIEOV       | JTAGEN            | 0                      | JTAGEN            | JTAGEN                   |

| DI          | TDI               | -                      | TMS               | тск                      |

| AIO         | ADC7 INPUT        | ADC6 INPUT             | ADC5 INPUT        | ADC4 INPUT               |

Table 9-19.

Overriding Signals for Alternate Functions in PF7..PF4

**Table 9-20.** Overriding Signals for Alternate Functions in PF3..PF0

| Signal Name | PF3/ADC3   | PF2/ADC2   | PF1/ADC1   | PF0/ADC0   |

|-------------|------------|------------|------------|------------|

| PUOE        | 0          | 0          | 0          | 0          |

| PUOV        | 0          | 0          | 0          | 0          |

| DDOE        | 0          | 0          | 0          | 0          |

| DDOV        | 0          | 0          | 0          | 0          |

| PVOE        | 0          | 0          | 0          | 0          |

| PVOV        | 0          | 0          | 0          | 0          |

| PTOE        | 0          | 0          | 0          | 0          |

| DIEOE       | ADC3D      | ADC2D      | ADC1D      | ADC0D      |

| DIEOV       | 0          | 0          | 0          | 0          |

| DI          | _          | -          | -          | -          |

| AIO         | ADC3 INPUT | ADC2 INPUT | ADC1 INPUT | ADC0 INPUT |

# AIMEL

# 9.4.2 Port A Data Direction Register – DDRA

| Bit           | 7    | 6    | 5    | 4    | 3    | 2    | 1    | 0    |      |

|---------------|------|------|------|------|------|------|------|------|------|

|               | DDA7 | DDA6 | DDA5 | DDA4 | DDA3 | DDA2 | DDA1 | DDA0 | DDRA |

| Read/Write    | R/W  |      |

| Initial Value | 0    | 0    | 0    | 0    | 0    | 0    | 0    | 0    |      |

# 9.4.3 Port A Input Pins Address – PINA

| Bit           | 7     | 6     | 5     | 4     | 3     | 2     | 1     | 0     | _    |

|---------------|-------|-------|-------|-------|-------|-------|-------|-------|------|

|               | PINA7 | PINA6 | PINA5 | PINA4 | PINA3 | PINA2 | PINA1 | PINA0 | PINA |

| Read/Write    | R/W   | •    |

| Initial Value | N/A   |      |

#### 9.4.4 Port B Data Register – PORTB

| Bit           | 7      | 6      | 5      | 4      | 3      | 2      | 1      | 0      |       |

|---------------|--------|--------|--------|--------|--------|--------|--------|--------|-------|

|               | PORTB7 | PORTB6 | PORTB5 | PORTB4 | PORTB3 | PORTB2 | PORTB1 | PORTB0 | PORTB |

| Read/Write    | R/W    |       |

| Initial Value | 0      | 0      | 0      | 0      | 0      | 0      | 0      | 0      |       |

# 9.4.5 Port B Data Direction Register – DDRB

| Bit           | 7    | 6    | 5    | 4    | 3    | 2    | 1    | 0    | _    |

|---------------|------|------|------|------|------|------|------|------|------|

|               | DDB7 | DDB6 | DDB5 | DDB4 | DDB3 | DDB2 | DDB1 | DDB0 | DDRB |

| Read/Write    | R/W  |      |

| Initial Value | 0    | 0    | 0    | 0    | 0    | 0    | 0    | 0    |      |

#### 9.4.6 Port B Input Pins Address – PINB

| Bit           | 7     | 6     | 5     | 4     | 3     | 2     | 1     | 0     | _    |

|---------------|-------|-------|-------|-------|-------|-------|-------|-------|------|

|               | PINB7 | PINB6 | PINB5 | PINB4 | PINB3 | PINB2 | PINB1 | PINB0 | PINB |

| Read/Write    | R/W   |      |

| Initial Value | N/A   |      |

#### 9.4.7 Port C Data Register – PORTC

| Bit           | 7      | 6      | 5      | 4      | 3      | 2      | 1      | 0      |       |

|---------------|--------|--------|--------|--------|--------|--------|--------|--------|-------|

|               | PORTC7 | PORTC6 | PORTC5 | PORTC4 | PORTC3 | PORTC2 | PORTC1 | PORTC0 | PORTC |

| Read/Write    | R/W    | I     |

| Initial Value | 0      | 0      | 0      | 0      | 0      | 0      | 0      | 0      |       |

### 9.4.8 Port C Data Direction Register – DDRC

| Bit           | 7    | 6    | 5    | 4    | 3    | 2    | 1    | 0    | _    |

|---------------|------|------|------|------|------|------|------|------|------|

|               | DDC7 | DDC6 | DDC5 | DDC4 | DDC3 | DDC2 | DDC1 | DDC0 | DDRC |

| Read/Write    | R/W  |      |

| Initial Value | 0    | 0    | 0    | 0    | 0    | 0    | 0    | 0    |      |

# 9.4.9 Port C Input Pins Address – PINC

| Bit           | 7     | 6     | 5     | 4     | 3     | 2     | 1     | 0     | _    |

|---------------|-------|-------|-------|-------|-------|-------|-------|-------|------|

|               | PINC7 | PINC6 | PINC5 | PINC4 | PINC3 | PINC2 | PINC1 | PINC0 | PINC |

| Read/Write    | R/W   |      |

| Initial Value | N/A   |      |

# AT90CAN32/64/128

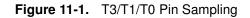

The synchronization and edge detector logic introduces a delay of 2.5 to 3.5 system clock cycles from an edge has been applied to the T3/T1/T0 pin to the counter is updated.

Enabling and disabling of the clock input must be done when T3/T1/T0 has been stable for at least one system clock cycle, otherwise it is a risk that a false Timer/Counter clock pulse is generated.

Each half period of the external clock applied must be longer than one system clock cycle to ensure correct sampling. The external clock must be guaranteed to have less than half the system clock frequency ( $f_{ExtClk} < f_{clk_l/O}/2$ ) given a 50/50 % duty cycle. Since the edge detector uses sampling, the maximum frequency of an external clock it can detect is half the sampling frequency (Nyquist sampling theorem). However, due to variation of the system clock frequency and duty cycle caused by Oscillator source (crystal, resonator, and capacitors) tolerances, it is recommended that maximum frequency of an external clock source is less than  $f_{clk_l/O}/2.5$ .

An external clock source can not be prescaled.

Note: 1. The synchronization logic on the input pins (T0/T1/T3) is shown in Figure 11-1.

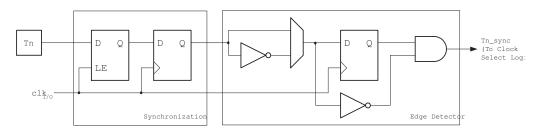

# 11.2 Timer/Counter0/1/3 Prescalers Register Description

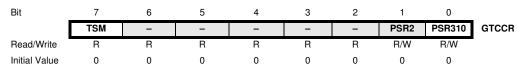

# 11.2.1 General Timer/Counter Control Register – GTCCR

#### • Bit 7 – TSM: Timer/Counter Synchronization Mode

Writing the TSM bit to one activates the Timer/Counter Synchronization mode. In this mode, the value that is written to the PSR2 and PSR310 bits is kept, hence keeping the corresponding prescaler reset signals asserted. This ensures that the corresponding Timer/Counters are halted and can be configured to the same value without the risk of one of them advancing during configuration. When the TSM bit is written to zero, the PSR2 and PSR310 bits are cleared by hardware, and the Timer/Counters start counting simultaneously.

# • Bit 0 – PSR310: Prescaler Reset Timer/Counter3, Timer/Counter1 and Timer/Counter0

When this bit is one, Timer/Counter3, Timer/Counter1 and Timer/Counter0 prescaler will be Reset. This bit is normally cleared immediately by hardware, except if the TSM bit is set. Note that Timer/Counter3, Timer/Counter1 and Timer/Counter0 share the same prescaler and a reset of this prescaler will affect these three timers.

priority, the maximum interrupt response time is dependent on the maximum number of clock cycles it takes to handle any of the other interrupt requests.

Using the Input Capture unit in any mode of operation when the TOP value (resolution) is actively changed during operation, is not recommended.

Measurement of an external signal's duty cycle requires that the trigger edge is changed after each capture. Changing the edge sensing must be done as early as possible after the ICRn Register has been read. After a change of the edge, the Input Capture Flag (ICFn) must be cleared by software (writing a logical one to the I/O bit location). For measuring frequency only, the clearing of the ICFn flag is not required (if an interrupt handler is used).

# 13.7 Output Compare Units

The 16-bit comparator continuously compares TCNTn with the Output Compare Register (OCRnx). If TCNT equals OCRnx the comparator signals a match. A match will set the Output Compare Flag (OCFnx) at the next timer clock cycle. If enabled (OCIEnx = 1), the Output Compare Flag generates an Output Compare interrupt. The OCFnx flag is automatically cleared when the interrupt is executed. Alternatively the OCFnx flag can be cleared by software by writing a logical one to its I/O bit location. The Waveform Generator uses the match signal to generate an output according to operating mode set by the Waveform Generation mode (WGMn3:0) bits and Compare Output mode (COMnx1:0) bits. The TOP and BOTTOM signals are used by the Waveform Generator for handling the special cases of the extreme values in some modes of operation (See "Modes of Operation" on page 126.)

A special feature of Output Compare unit A allows it to define the Timer/Counter TOP value (i.e., counter resolution). In addition to the counter resolution, the TOP value defines the period time for waveforms generated by the Waveform Generator.

Figure 13-4 shows a block diagram of the Output Compare unit. The elements of the block diagram that are not directly a part of the Output Compare unit are gray shaded.

| D<br># (Data + Parity Bit) | R <sub>slow</sub> (%) | R <sub>fast</sub> (%) | Max Total Error (%) | Recommended Max<br>Receiver Error (%) |

|----------------------------|-----------------------|-----------------------|---------------------|---------------------------------------|

| 5                          | 93.20                 | 106.67                | +6.67/-6.8          | ± 3.0                                 |

| 6                          | 94.12                 | 105.79                | +5.79/-5.88         | ± 2.5                                 |

| 7                          | 94.81                 | 105.11                | +5.11/-5.19         | ± 2.0                                 |

| 8                          | 95.36                 | 104.58                | +4.58/-4.54         | ± 2.0                                 |

| 9                          | 95.81                 | 104.14                | +4.14/-4.19         | ± 1.5                                 |

| 10                         | 96.17                 | 103.78                | +3.78/-3.83         | ± 1.5                                 |

**Table 17-2.** Recommended Maximum Receiver Baud Rate Error for Normal Speed Mode(U2Xn = 0)

Table 17-3.Recommended Maximum Receiver Baud Rate Error for Double Speed Mode<br/>(U2Xn = 1)

| D<br># (Data + Parity Bit) | R <sub>slow</sub> (%) | R <sub>fast</sub> (%) | Max Total Error (%) | Recommended Max<br>Receiver Error (%) |

|----------------------------|-----------------------|-----------------------|---------------------|---------------------------------------|

| 5                          | 94.12                 | 105.66                | +5.66/-5.88         | ± 2.5                                 |

| 6                          | 94.92                 | 104.92                | +4.92/-5.08         | ± 2.0                                 |

| 7                          | 95.52                 | 104,35                | +4.35/-4.48         | ± 1.5                                 |

| 8                          | 96.00                 | 103.90                | +3.90/-4.00         | ± 1.5                                 |

| 9                          | 96.39                 | 103.53                | +3.53/-3.61         | ± 1.5                                 |

| 10                         | 96.70                 | 103.23                | +3.23/-3.30         | ± 1.0                                 |

The recommendations of the maximum receiver baud rate error was made under the assumption that the Receiver and Transmitter equally divides the maximum total error.

There are two possible sources for the receivers baud rate error. The Receiver's system clock (XTAL) will always have some minor instability over the supply voltage range and the temperature range. When using a crystal to generate the system clock, this is rarely a problem, but for a resonator the system clock may differ more than 2% depending of the resonators tolerance. The second source for the error is more controllable. The baud rate generator can not always do an exact division of the system frequency to get the baud rate wanted. In this case an UBRRn value that gives an acceptable low error can be used if possible.

# 17.10 Multi-processor Communication Mode

Setting the Multi-processor Communication mode (MPCMn) bit in UCSRnA enables a filtering function of incoming frames received by the USARTn Receiver. Frames that do not contain address information will be ignored and not put into the receive buffer. This effectively reduces the number of incoming frames that has to be handled by the CPU, in a system with multiple MCUs that communicate via the same serial bus. The Transmitter is unaffected by the MPCMn setting, but has to be used differently when it is a part of a system utilizing the Multi-processor Communication mode.

- An algorithm must be implemented allowing only one of the masters to complete the transmission. All other masters should cease transmission when they discover that they have lost the selection process. This selection process is called arbitration. When a contending master discovers that it has lost the arbitration process, it should immediately switch to slave mode to check whether it is being addressed by the winning master. The fact that multiple masters have started transmission at the same time should not be detectable to the slaves, i.e., the data being transferred on the bus must not be corrupted.

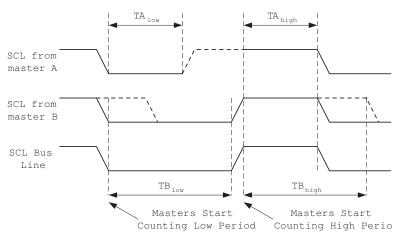

- Different masters may use different SCL frequencies. A scheme must be devised to synchronize the serial clocks from all masters, in order to let the transmission proceed in a lockstep fashion. This will facilitate the arbitration process.

The wired-ANDing of the bus lines is used to solve both these problems. The serial clocks from all masters will be wired-ANDed, yielding a combined clock with a high period equal to the one from the master with the shortest high period. The low period of the combined clock is equal to the low period of the master with the longest low period. Note that all masters listen to the SCL line, effectively starting to count their SCL high and low time-out periods when the combined SCL line goes high or low, respectively.

Arbitration is carried out by all masters continuously monitoring the SDA line after outputting data. If the value read from the SDA line does not match the value the master had output, it has lost the arbitration. Note that a master can only lose arbitration when it outputs a high SDA value while another master outputs a low value. The losing master should immediately go to slave mode, checking if it is being addressed by the winning master. The SDA line should be left high, but losing masters are allowed to generate a clock signal until the end of the current data or address packet. Arbitration will continue until only one master remains, and this may take many bits. If several masters are trying to address the same slave, arbitration will continue into the data packet.

the application has cleared TWINT, the TWI will initiate transmission of the START condition.

- 2. When the START condition has been transmitted, the TWINT flag in TWCR is set, and TWSR is updated with a status code indicating that the START condition has successfully been sent.

- 3. The application software should now examine the value of TWSR, to make sure that the START condition was successfully transmitted. If TWSR indicates otherwise, the application software might take some special action, like calling an error routine. Assuming that the status code is as expected, the application must load SLA+W into TWDR. Remember that TWDR is used both for address and data. After TWDR has been loaded with the desired SLA+W, a specific value must be written to TWCR, instructing the TWI hardware to transmit the SLA+W present in TWDR. Which value to write is described later on. However, it is important that the TWINT bit is set in the value written. Writing a one to TWINT clears the flag. The TWI will not start any operation as long as the TWINT bit in TWCR is set. Immediately after the application has cleared TWINT, the TWI will initiate transmission of the address packet.

- 4. When the address packet has been transmitted, the TWINT flag in TWCR is set, and TWSR is updated with a status code indicating that the address packet has successfully been sent. The status code will also reflect whether a slave acknowledged the packet or not.

- 5. The application software should now examine the value of TWSR, to make sure that the address packet was successfully transmitted, and that the value of the ACK bit was as expected. If TWSR indicates otherwise, the application software might take some special action, like calling an error routine. Assuming that the status code is as expected, the application must load a data packet into TWDR. Subsequently, a specific value must be written to TWCR, instructing the TWI hardware to transmit the data packet present in TWDR. Which value to write is described later on. However, it is important that the TWINT bit is set in the value written. Writing a one to TWINT clears the flag. The TWI will not start any operation as long as the TWINT bit in TWCR is set. Immediately after the application has cleared TWINT, the TWI will initiate transmission of the data packet.

- 6. When the data packet has been transmitted, the TWINT flag in TWCR is set, and TWSR is updated with a status code indicating that the data packet has successfully been sent. The status code will also reflect whether a slave acknowledged the packet or not.

- 7. The application software should now examine the value of TWSR, to make sure that the data packet was successfully transmitted, and that the value of the ACK bit was as expected. If TWSR indicates otherwise, the application software might take some special action, like calling an error routine. Assuming that the status code is as expected, the application must write a specific value to TWCR, instructing the TWI hardware to transmit a STOP condition. Which value to write is described later on. However, it is important that the TWINT bit is set in the value written. Writing a one to TWINT clears the flag. The TWI will not start any operation as long as the TWINT bit in TWCR is set. Immediately after the application has cleared TWINT, the TWI will initiate transmission of the STOP condition. Note that TWINT is NOT set after a STOP condition has been sent.

Even though this example is simple, it shows the principles involved in all TWI transmissions. These can be summarized as follows:

• When the TWI has finished an operation and expects application response, the TWINT flag is set. The SCL line is pulled low until TWINT is cleared.

# AT90CAN32/64/128

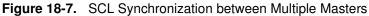

## Figure 19-14. CAN Controller Interrupt Structure

#### 19.8.2 Interrupt Behavior

When an interrupt occurs, an interrupt flag bit is set in the corresponding MOb-CANSTMOB register or in the general CANGIT register. If in the CANIE register, ENRX / ENTX / ENERR bit are set, then the corresponding MOb bit is set in the CANSITn register.

To acknowledge a MOb interrupt, the corresponding bits of CANSTMOB register (RXOK, TXOK,...) must be cleared by the software application. This operation needs a read-modify-write software routine.

To acknowledge a general interrupt, the corresponding bits of CANGIT register (BXOK, BOF-FIT,...) must be cleared by the software application. This operation is made writing a logical one in these interrupt flags (writing a logical zero doesn't change the interrupt flag value).

OVRTIM interrupt flag is reset as the other interrupt sources of CANGIT register and is also reset entering in its dedicated interrupt handler.

When the CAN node is in transmission and detects a Form Error in its frame, a bit Error will also be raised. Consequently, two consecutive interrupts can occur, both due to the same error.

When a MOb error occurs and is set in its own CANSTMOB register, no general error is set in CANGIT register.

# • Bits 1, 0 – ACIS1, ACIS0: Analog Comparator Interrupt Mode Select

These bits determine which comparator events that trigger the Analog Comparator interrupt. The different settings are shown in Table 20-1.

| Table 20-1. | ACIS1/ACIS0 Settings |

|-------------|----------------------|

|-------------|----------------------|

| ACIS1 | ACIS0 | Interrupt Mode                               |

|-------|-------|----------------------------------------------|

| 0     | 0     | Comparator Interrupt on Output Toggle.       |

| 0     | 1     | Reserved                                     |

| 1     | 0     | Comparator Interrupt on Falling Output Edge. |

| 1     | 1     | Comparator Interrupt on Rising Output Edge.  |

When changing the ACIS1/ACIS0 bits, the Analog Comparator Interrupt must be disabled by clearing its Interrupt Enable bit in the ACSR Register. Otherwise an interrupt can occur when the bits are changed.

# 20.3 Analog Comparator Multiplexed Input

It is possible to select any of the ADC7..0 pins to replace the negative input to the Analog Comparator. The ADC multiplexer is used to select this input, and consequently, the ADC must be switched off to utilize this feature. If the Analog Comparator Multiplexer Enable bit (ACME in ADCSRB) is set and the ADC is switched off (ADEN in ADCSRA is zero), MUX2..0 in ADMUX select the input pin to replace the negative input to the Analog Comparator, as shown in Table 20-2. If ACME is cleared or ADEN is set, AIN1 is applied to the negative input to the Analog Comparator.

| ACME | ADEN | MUX20 | Analog Comparator Negative Input |

|------|------|-------|----------------------------------|

| 0    | х    | ХХХ   | AIN1                             |

| 1    | 1    | ХХХ   | AIN1                             |

| 1    | 0    | 000   | ADC0                             |

| 1    | 0    | 001   | ADC1                             |

| 1    | 0    | 010   | ADC2                             |

| 1    | 0    | 011   | ADC3                             |

| 1    | 0    | 100   | ADC4                             |

| 1    | 0    | 101   | ADC5                             |

| 1    | 0    | 110   | ADC6                             |

| 1    | 0    | 111   | ADC7                             |

Table 20-2. Analog Comparator Multiplexed Input

# 21. Analog to Digital Converter - ADC

# 21.1 Features

- 10-bit Resolution

- 0.5 LSB Integral Non-linearity

- ± 2 LSB Absolute Accuracy

- 13 260 µs Conversion Time

- Up to 76 kSPS at Maximum Resolution

- Eight Multiplexed Single Ended Input Channels

- · Seven Differential input channels

- Optional Left Adjustment for ADC Result Readout

- 0 V<sub>CC</sub> ADC Input Voltage Range

- Selectable 2.56 V ADC Reference Voltage

- Free Running or Single Conversion Mode

- ADC Start Conversion by Auto Triggering on Interrupt Sources

- Interrupt on ADC Conversion Complete

- Sleep Mode Noise Canceler

The AT90CAN32/64/128 features a 10-bit successive approximation ADC. The ADC is connected to an 8-channel Analog Multiplexer which allows eight single-ended voltage inputs constructed from the pins of Port F. The single-ended voltage inputs refer to 0V (GND).

The device also supports 16 differential voltage input combinations. Two of the differential inputs (ADC1, ADC0 and ADC3, ADC2) are equipped with a programmable gain stage, providing amplification steps of 0 dB (1x), 20 dB (10x), or 46 dB (200x) on the differential input voltage before the A/D conversion. Seven differential analog input channels share a common negative terminal (ADC1), while any other ADC input can be selected as the positive input terminal. If 1x or 10x gain is used, 8-bit resolution can be expected. If 200x gain is used, 7-bit resolution can be expected.

The ADC contains a Sample and Hold circuit which ensures that the input voltage to the ADC is held at a constant level during conversion. A block diagram of the ADC is shown in Figure 21-1.

The ADC has a separate analog supply voltage pin,  $AV_{CC}$ .  $AV_{CC}$  must not differ more than ± 0.3V from  $V_{CC}$ . See the paragraph "ADC Noise Canceler" on page 279 on how to connect this pin.

Internal reference voltages of nominally 2.56V or  $AV_{CC}$  are provided On-chip. The voltage reference may be externally decoupled at the AREF pin by a capacitor for better noise performance.

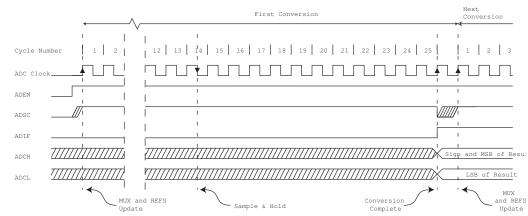

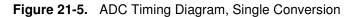

When initiating a single ended conversion by setting the ADSC bit in ADCSRA, the conversion starts at the following rising edge of the ADC clock cycle. See "Differential Channels" on page 277 for details on differential conversion timing.

A normal conversion takes 13 ADC clock cycles. The first conversion after the ADC is switched on (ADEN in ADCSRA is set) takes 25 ADC clock cycles in order to initialize the analog circuitry.

The actual sample-and-hold takes place 1.5 ADC clock cycles after the start of a normal conversion and 13.5 ADC clock cycles after the start of an first conversion. When a conversion is complete, the result is written to the ADC Data Registers, and ADIF is set. In Single Conversion mode, ADSC is cleared simultaneously. The software may then set ADSC again, and a new conversion will be initiated on the first rising ADC clock edge.

When Auto Triggering is used, the prescaler is reset when the trigger event occurs. This assures a fixed delay from the trigger event to the start of conversion. In this mode, the sample-and-hold takes place two ADC clock cycles after the rising edge on the trigger source signal. Three additional CPU clock cycles are used for synchronization logic.

In Free Running mode, a new conversion will be started immediately after the conversion completes, while ADSC remains high. For a summary of conversion times, see Table 21-1.

Figure 21-4. ADC Timing Diagram, First Conversion (Single Conversion Mode)

# 22.8 On-chip Debug Related Register in I/O Memory

## 22.8.1 On-chip Debug Register – OCDR

| Bit           | 7          | 6     | 5     | 4     | 3     | 2     | 1     | 0     |      |

|---------------|------------|-------|-------|-------|-------|-------|-------|-------|------|

|               | IDRD/OCDR7 | OCDR6 | OCDR5 | OCDR4 | OCDR3 | OCDR2 | OCDR1 | OCDR0 | OCDR |

| Read/Write    | R/W        | R/W   | R/W   | R/W   | R/W   | R/W   | R/W   | R/W   |      |

| Initial Value | 0          | 0     | 0     | 0     | 0     | 0     | 0     | 0     |      |

The OCDR Register provides a communication channel from the running program in the microcontroller to the debugger. The CPU can transfer a byte to the debugger by writing to this location. At the same time, an internal flag; I/O Debug Register Dirty – IDRD – is set to indicate to the debugger that the register has been written. When the CPU reads the OCDR Register the 7 LSB will be from the OCDR Register, while the MSB is the IDRD bit. The debugger clears the IDRD bit when it has read the information.

In some AVR devices, this register is shared with a standard I/O location. In this case, the OCDR Register can only be accessed if the OCDEN Fuse is programmed, and the debugger enables access to the OCDR Register. In all other cases, the standard I/O location is accessed.

Refer to the debugger documentation for further information on how to use this register.

# 22.9 Using the JTAG Programming Capabilities

Programming of AVR parts via JTAG is performed via the 4-pin JTAG port, TCK, TMS, TDI, and TDO. These are the only pins that need to be controlled/observed to perform JTAG programming (in addition to power pins). It is not required to apply 12V externally. The JTAGEN Fuse must be programmed and the JTD bit in the MCUCR Register must be cleared to enable the JTAG Test Access Port.

The JTAG programming capability supports:

- Flash programming and verifying.

- EEPROM programming and verifying.

- Fuse programming and verifying.

- Lock bit programming and verifying.

The Lock bit security is exactly as in parallel programming mode. If the Lock bits LB1 or LB2 are programmed, the OCDEN Fuse cannot be programmed unless first doing a chip erase. This is a security feature that ensures no back-door exists for reading out the content of a secured device.

The details on programming through the JTAG interface and programming specific JTAG instructions are given in the section "JTAG Programming Overview" on page 351.

# 22.10 Bibliography

For more information about general Boundary-scan, the following literature can be consulted:

- IEEE: IEEE Std 1149.1-1990. IEEE Standard Test Access Port and Boundary-scan Architecture, IEEE, 1993.

- Colin Maunder: The Board Designers Guide to Testable Logic Circuits, Addison-Wesley, 1992.

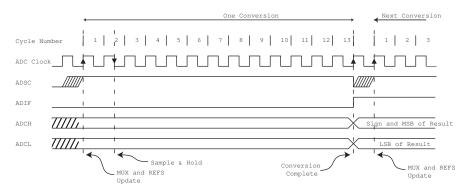

Figure 1. I/O Input Threshold Voltage vs. Vcc (V<sub>IL</sub>, I/O Pin Read as "0")

I/O P IN INP UT THRESHOLD VOLTAGE vs.  $V_{CC}$  VL, IO PIN READ AS '0'

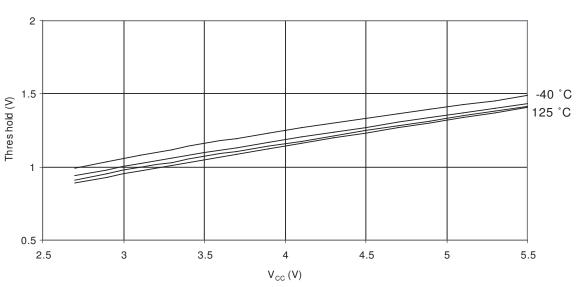

# 29.8 BOD Thresholds and Analog Comparator Offset

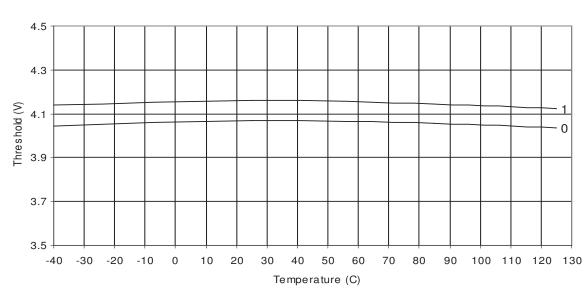

Figure 29-26. BOD Thresholds vs. Temperature (BOD level is 4.1V)

BOD THRESHOLDS vs. TEMPERATURE BOD = 4.1V

# **Atmel Corporation**

2325 Orchard Parkway San Jose, CA 95131, USA Tel: 1(408) 441-0311 Fax: 1(408) 487-2600

# **Regional Headquarters**

#### Europe

Atmel Sarl Route des Arsenaux 41 Case Postale 80 CH-1705 Fribourg Switzerland Tel: (41) 26-426-5555 Fax: (41) 26-426-5500

#### Asia

Room 1219 Chinachem Golden Plaza 77 Mody Road Tsimshatsui East Kowloon Hong Kong Tel: (852) 2721-9778 Fax: (852) 2722-1369

#### Japan

9F, Tonetsu Shinkawa Bldg. 1-24-8 Shinkawa Chuo-ku, Tokyo 104-0033 Japan Tel: (81) 3-3523-3551 Fax: (81) 3-3523-7581

# **Atmel Operations**

Memory

2325 Orchard Parkway San Jose, CA 95131, USA Tel: 1(408) 441-0311 Fax: 1(408) 436-4314

#### **Microcontrollers**

2325 Orchard Parkway San Jose, CA 95131, USA Tel: 1(408) 441-0311 Fax: 1(408) 436-4314

La Chantrerie BP 70602 44306 Nantes Cedex 3, France Tel: (33) 2-40-18-18-18 Fax: (33) 2-40-18-19-60

#### ASIC/ASSP/Smart Cards

Zone Industrielle 13106 Rousset Cedex, France Tel: (33) 4-42-53-60-00 Fax: (33) 4-42-53-60-01

1150 East Cheyenne Mtn. Blvd. Colorado Springs, CO 80906, USA Tel: 1(719) 576-3300 Fax: 1(719) 540-1759

Scottish Enterprise Technology Park Maxwell Building East Kilbride G75 0QR, Scotland Tel: (44) 1355-803-000 Fax: (44) 1355-242-743

#### **RF**/Automotive

Theresienstrasse 2 Postfach 3535 74025 Heilbronn, Germany Tel: (49) 71-31-67-0 Fax: (49) 71-31-67-2340

1150 East Cheyenne Mtn. Blvd. Colorado Springs, CO 80906, USA Tel: 1(719) 576-3300 Fax: 1(719) 540-1759

#### Biometrics/Imaging/Hi-Rel MPU/

High Speed Converters/RF Datacom Avenue de Rochepleine BP 123 38521 Saint-Egreve Cedex, France Tel: (33) 4-76-58-30-00 Fax: (33) 4-76-58-34-80

*Literature Requests* www.atmel.com/literature

Disclaimer: The information in this document is provided in connection with Atmel products. No license, express or implied, by estoppel or otherwise, to any intellectual property right is granted by this document or in connection with the sale of Atmel products. EXCEPT AS SET FORTH IN ATMEL'S TERMS AND CONDI-TIONS OF SALE LOCATED ON ATMEL'S WEB SITE, ATMEL ASSUMES NO LIABILITY WHATSOEVER AND DISCLAIMS ANY EXPRESS, IMPLIED OR STATUTORY WARRANTY RELATING TO ITS PRODUCTS INCLUDING, BUT NOT LIMITED TO, THE IMPLIED WARRANTY OF MERCHANTABILITY, FITNESS FOR A PARTICULAR PURPOSE, OR NON-INFRINGEMENT. IN NO EVENT SHALL ATMEL BE LIABLE FOR ANY DIRECT, INDIRECT, CONSEQUENTIAL, PUNTIVE, SPECIAL OR INCIDEN-TAL DAMAGES (INCLUDING, WITHOUT LIMITATION, DAMAGES FOR LOSS OF PROFITS, BUSINESS INTERRUPTION, OR LOSS OF INFORMATION) ARISING OUT OF THE USE OR INABILITY TO USE THIS DOCUMENT, EVEN IF ATMEL HAS BEEN ADVISED OF THE POSSIBILITY OF SUCH DAMAGES. Atmel makes no representations or warranties with respect to the accuracy or completeness of the contents of this document and reserves the right to make changes to specifications and product descriptions at any time without notice. Atmel does not make any commitment to update the information contained herein. Unless specifically providedotherwise, Atmel products are not suitable for, and shall not be used in, automotive applications. Atmel'sAtmel's products are not intended, authorized, or warranted for use as components in applications intended to support or sustain life.

©2008 Atmel Corporation. All rights reserved. Atmel<sup>®</sup>, logo and combinations thereof, are registered trademarks, and Everywhere You Are<sup>®</sup> are the trademarks of Atmel Corporation or its subsidiaries. Other terms and product names may be trademarks of others.