Welcome to **E-XFL.COM**

# Understanding <u>Embedded - FPGAs (Field Programmable Gate Array)</u>

Embedded - FPGAs, or Field Programmable Gate Arrays, are advanced integrated circuits that offer unparalleled flexibility and performance for digital systems. Unlike traditional fixed-function logic devices, FPGAs can be programmed and reprogrammed to execute a wide array of logical operations, enabling customized functionality tailored to specific applications. This reprogrammability allows developers to iterate designs quickly and implement complex functions without the need for custom hardware.

### **Applications of Embedded - FPGAs**

The versatility of Embedded - FPGAs makes them indispensable in numerous fields. In telecommunications.

| Details                        |                                                              |

|--------------------------------|--------------------------------------------------------------|

| Product Status                 | Obsolete                                                     |

| Number of LABs/CLBs            | 1176                                                         |

| Number of Logic Elements/Cells | 5292                                                         |

| Total RAM Bits                 | 57344                                                        |

| Number of I/O                  | 182                                                          |

| Number of Gates                | 200000                                                       |

| Voltage - Supply               | 1.71V ~ 1.89V                                                |

| Mounting Type                  | Surface Mount                                                |

| Operating Temperature          | -40°C ~ 125°C (TJ)                                           |

| Package / Case                 | 256-LBGA                                                     |

| Supplier Device Package        | 256-FTBGA (17x17)                                            |

| Purchase URL                   | https://www.e-xfl.com/product-detail/xilinx/xa2s200e-6ft256q |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

DS106-1 (v1.7) October 18, 2004

# Spartan-IIE 1.8V FPGA Automotive XA Product Family: Introduction and Ordering

### **Preliminary Product Specification**

### Introduction

The Xilinx Automotive (XA) Spartan<sup>™</sup>-IIE 1.8V Field-Programmable Gate Array family is specifically designed to meet the needs of high-volume, cost-sensitive automotive electronic applications. The family gives users high performance, abundant logic resources, and a rich feature set, all at an exceptionally low price. The five-member family offers densities ranging from 50,000 to 300,000 system gates, as shown in Table 1. System performance is supported beyond 200 MHz.

Spartan-IIE devices deliver more gates, I/Os, and features per dollar than other FPGAs by combining advanced process technology with a streamlined architecture based on the proven Virtex<sup>TM</sup>-E platform. Features include block RAM (to 64K bits), distributed RAM (to 98,304 bits), 19 selectable I/O standards, and four DLLs (Delay-Locked Loops). Fast, predictable interconnect means that successive design iterations continue to meet timing requirements.

XA devices are available in both the extended-temperature Q-grade (-40°C to +125°C) and industrial I-grade (-40°C to +100°C) and are qualified to the industry-recognized AEC-Q100 standard.

The XA Spartan-IIE family is a superior alternative to mask-programmed ASICs. The FPGA avoids the initial cost, lengthy development cycles, and inherent risk of conventional ASICs. Also, FPGA programmability permits design upgrades in the field with no hardware replacement necessary (impossible with ASICs).

### **Features**

AEC-Q100 device qualification and full PPAP support available in both extended temperature Q-grade and I-grade

- Guaranteed to meet full electrical specifications over

T<sub>J</sub> = -40°C to +125°C

- Second generation ASIC replacement technology

- Densities as high as 6,912 logic cells with up to 300,000 system gates

- Very low cost

- System-level features

- SelectRAM+™ hierarchical memory:

- · 16 bits/LUT distributed RAM

- · Configurable 4K-bit true dual-port block RAM

- · Fast interfaces to external RAM

- Dedicated carry logic for high-speed arithmetic

- Efficient multiplier support

- Cascade chain for wide-input functions

- Abundant registers/latches with enable, set, reset

- Four dedicated DLLs for advanced clock control

- Eliminate clock distribution delay

- · Multiply, divide, or phase shift

- Four primary low-skew global clock distribution nets

- IEEE 1149.1 compatible boundary scan logic

- Versatile I/O and packaging

- Low-cost packages available in all densities

- 19 high-performance interface standards

- · LVTTL, LVCMOS, HSTL, SSTL, AGP, CTT, GTL

- LVDS and LVPECL differential I/O

- Up to 120 differential I/O pairs that can be input, output, or bidirectional

- Fully supported by powerful Xilinx ISE development system

- Fully automatic mapping, placement, and routing

- Integrated with design entry and verification tools

- Extensive IP library including DSP functions

Table 1: XA Spartan-IIE FPGA Family Members

| Device   | Logic<br>Cells | Typical<br>System Gate Range<br>(Logic and RAM) | CLB<br>Array<br>(R x C) | Total<br>CLBs | Maximum<br>Available<br>User I/O <sup>(1)</sup> | Maximum<br>Differential<br>I/O Pairs | Distributed<br>RAM Bits | Block<br>RAM Bits |

|----------|----------------|-------------------------------------------------|-------------------------|---------------|-------------------------------------------------|--------------------------------------|-------------------------|-------------------|

| XA2S50E  | 1,728          | 23,000 - 50,000                                 | 16 x 24                 | 384           | 102                                             | 83                                   | 24,576                  | 32K               |

| XA2S100E | 2,700          | 37,000 - 100,000                                | 20 x 30                 | 600           | 102                                             | 86                                   | 38,400                  | 40K               |

| XA2S150E | 3,888          | 52,000 - 150,000                                | 24 x 36                 | 864           | 182                                             | 114                                  | 55,296                  | 48K               |

| XA2S200E | 5,292          | 71,000 - 200,000                                | 28 x 42                 | 1,176         | 182                                             | 120                                  | 75,264                  | 56K               |

| XA2S300E | 6,912          | 93,000 - 300,000                                | 32 x 48                 | 1,536         | 182                                             | 120                                  | 98,304                  | 64K               |

#### Notes

1. User I/O counts include the four global clock/user input pins. See details in Table 3, page 5

© 2003 Xilinx, Inc. All rights reserved. All Xilinx trademarks, registered trademarks, patents, and disclaimers are as listed at <a href="http://www.xilinx.com/legal.htm">http://www.xilinx.com/legal.htm</a>.

All other trademarks and registered trademarks are the property of their respective owners. All specifications are subject to change without notice.

### General Overview

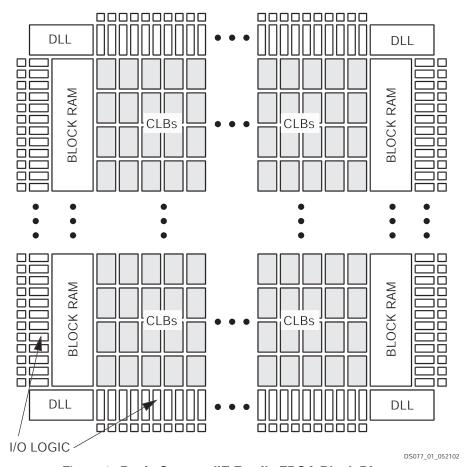

The Spartan-IIE family of FPGAs have a regular, flexible, programmable architecture of Configurable Logic Blocks (CLBs), surrounded by a perimeter of programmable Input/Output Blocks (IOBs). There are four Delay-Locked Loops (DLLs), one at each corner of the die. Two columns of block RAM lie on opposite sides of the die, between the CLBs and the IOB columns. The XC2S400E has four columns of block RAM. These functional elements are interconnected by a powerful hierarchy of versatile routing channels (see Figure 1).

Spartan-IIE FPGAs are customized by loading configuration data into internal static memory cells. Unlimited reprogramming cycles are possible with this approach. Stored values in these cells determine logic functions and interconnections implemented in the FPGA. Configuration data can be read from an external serial PROM (master serial mode), or written into the FPGA in slave serial, slave parallel, or Boundary Scan modes.

Spartan-IIE FPGAs are typically used in high-volume applications where the versatility of a fast programmable solution adds benefits. Spartan-IIE FPGAs are ideal for shortening product development cycles while offering a cost-effective solution for high volume production.

Spartan-IIE FPGAs achieve high-performance, low-cost operation through advanced architecture and semiconductor technology. Spartan-IIE devices provide system clock rates beyond 200 MHz. Spartan-IIE FPGAs offer the most cost-effective solution while maintaining leading edge performance. In addition to the conventional benefits of high-volume programmable logic solutions, Spartan-IIE FPGAs also offer on-chip synchronous single-port and dual-port RAM (block and distributed form), DLL clock drivers, programmable set and reset on all flip-flops, fast carry logic, and many other features.

## Spartan-IIE Family Compared to Spartan-II **Family**

- Higher density and more I/O

- Higher performance

- Unique pinouts in cost-effective packages

- Differential signaling

- LVDS, Bus LVDS, LVPECL

- $V_{CCINT} = 1.8V$

- Lower power

- 5V tolerance with external resistor

- 3V tolerance directly

- LVTTL and LVCMOS2 input buffers powered by V<sub>CCO</sub> instead of V<sub>CCINT</sub>

- Unique larger bitstream

Figure 1: Basic Spartan-IIE Family FPGA Block Diagram

# **DC Specifications**

# Absolute Maximum Ratings<sup>(1)</sup>

| Symbol             | Description                           | Min  | Max  | Units |

|--------------------|---------------------------------------|------|------|-------|

| V <sub>CCINT</sub> | Supply voltage relative to GND        | -0.5 | 2.0  | V     |

| V <sub>CCO</sub>   | Supply voltage relative to GND        | -0.5 | 4.0  | V     |

| V <sub>REF</sub>   | Input reference voltage               | -0.5 | 4.0  | V     |

| V <sub>IN</sub>    | Input voltage relative to GND (2,3)   | -0.5 | 4.05 | V     |

| V <sub>TS</sub>    | Voltage applied to 3-state output (3) | -0.5 | 4.0  | V     |

| T <sub>STG</sub>   | Storage temperature (ambient)         | -65  | +150 | °C    |

| TJ                 | Junction temperature                  | -    | +135 | °C    |

#### Notes:

- Stresses beyond those listed under Absolute Maximum Ratings may cause permanent damage to the device. These are stress ratings only, and functional operation of the device at these or any other conditions beyond those listed under Operating Conditions is not implied. Exposure to Absolute Maximum Ratings conditions for extended periods of time may affect device reliability.

- $V_{IN}$  should not exceed  $V_{CCO}$  by more than 3.6V over extended periods of time (e.g., longer than a day). Maximum DC overshoot must be limited to either  $V_{CCO}$  + 0.5V or 10 mA, and undershoot must be limited to -0.5V or 10 mA, whichever is easier to achieve. The Maximum AC conditions are as follows: The device pins may undershoot to -2.0V or overshoot to  $V_{CCO}$  + 2.0V, provided this over/undershoot lasts no more than 11 ns with a forcing current no greater than 100 mA.

- For soldering guidelines, see the Packaging Information on the Xilinx Web site.

### **Recommended Operating Conditions**

| Symbol             | Description                                   | Min      | Max      | Units |

|--------------------|-----------------------------------------------|----------|----------|-------|

| T <sub>J</sub>     | Junction temperature                          | -40      | 125      | °C    |

| V <sub>CCINT</sub> | Supply voltage relative to GND <sup>(1)</sup> | 1.8 – 5% | 1.8 + 5% | V     |

| V <sub>CCO</sub>   | Supply voltage relative to GND <sup>(2)</sup> | 1.2      | 3.6      | V     |

| T <sub>IN</sub>    | Input signal transition time <sup>(3)</sup>   | -        | 250      | ns    |

### Notes:

- Functional operation is guaranteed down to a minimum  $V_{CCINT}$  of 1.62V (Nominal  $V_{CCINT}$  –10%). For every 50 mV reduction in  $V_{CCINT}$  below 1.71V (nominal  $V_{CCINT}$  –5%), all delay parameters increase by 3%.

- Minimum and maximum values for V<sub>CCO</sub> vary according to the I/O standard selected.

- Input and output measurement threshold is ~50% of V<sub>CCO</sub>.

# **DC Characteristics Over Operating Conditions**

| Symbol              | Description                                                |          | Min | Max | Units |

|---------------------|------------------------------------------------------------|----------|-----|-----|-------|

|                     |                                                            | XA2S50E  | -   | 200 | mA    |

| I <sub>CCINTQ</sub> | Quiescent V <sub>CCINT</sub> supply current <sup>(1)</sup> | XA2S100E | -   | 350 | mA    |

|                     |                                                            | XA2S150E | -   | 450 | mA    |

|                     |                                                            | XA2S200E | -   | 550 | mA    |

|                     |                                                            | XA2S300E | -   | 650 | mA    |

# Spartan-IIE Product Availability

Table 2 shows the package and speed grades available for Spartan-IIE family devices. Table 3 shows the maximum user I/Os available on the device and the number of user I/Os available for each device/package combination.

Table 2: Spartan-IIE Package and Speed Grade Availability

|          | Pins | 144          | 256               |

|----------|------|--------------|-------------------|

|          | Туре | Plastic TQFP | Fine Pitch<br>BGA |

| Device   | Code | TQ144        | FT256             |

| XA2S50E  | -6   | I,Q          |                   |

| XA2S100E | -6   | I,Q          |                   |

| XA2S150E | -6   | -            | I,Q               |

| XA2S200E | -6   | -            | I,Q               |

| XA2S300E | -6   | -            | I,Q               |

### Notes:

- $Q = -40^{\circ} C \text{ to } +125^{\circ} C (T_{J})$

- $I = -40^{\circ} \text{C to } +100^{\circ} \text{C (T_J)}$

<sup>1.</sup> With no output current loads, no active pull-up resistors, and all I/O pins 3-stated and floating.

Table 3: Spartan-IIE User I/O Chart

|          |     |       | e User I/O<br>Package Type |  |

|----------|-----|-------|----------------------------|--|

| Device   | I/O | TQ144 | FT256                      |  |

| XA2S50E  | 102 | 102   | -                          |  |

| XA2S100E | 102 | 102   | -                          |  |

| XA2S150E | 182 | -     | 182                        |  |

| XA2S200E | 182 | -     | 182                        |  |

| XA2S300E | 182 | -     | 182                        |  |

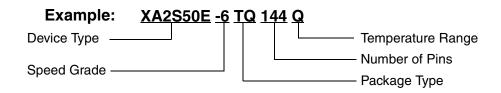

# **Ordering Information**

# **Device Ordering Options**

| Device   |  |

|----------|--|

| XA2S50E  |  |

| XA2S100E |  |

| XA2S150E |  |

| XA2S200E |  |

| XA2S300E |  |

| Speed Grade |                      |  |

|-------------|----------------------|--|

| -6          | Standard Performance |  |

| Package Type / Number of Pins |                          |  |

|-------------------------------|--------------------------|--|

| TQ144                         | 144-pin Plastic Thin QFP |  |

| FT256                         | 256-ball Fine Pitch BGA  |  |

| Temperature Range (T <sub>J</sub> ) |                 |  |

|-------------------------------------|-----------------|--|

| Q = Automotive<br>Extended          | -40°C to +125°C |  |

| I = Automotive<br>Industrial        | -40°C to +100°C |  |

# **Revision History**

| Version No. | Date     | Description                                                                                                                                                                    |

|-------------|----------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 1.0         | 07/17/02 | Initial Xilinx release.                                                                                                                                                        |

| 1.1         | 11/18/02 | Added XC2S400-E and XC2S600-E devices. Added FG676 to package list.                                                                                                            |

| 1.2         | 11/26/02 | Updated Max User I/O and Differential I/O Pairs in Table 1 and Max User I/O in Table 3. Updated notes for Recommended Operating Conditions.                                    |

| 1.3         | 06/04/03 | Changed five-member family to seven-member family in first paragraph.                                                                                                          |

| 1.4         | 06/16/03 | Updated features list. Added <b>DC Characteristics Over Operating Conditions</b> table. Deleted "FG676" from Table 2, Table 3, and the <b>Device Ordering Options</b> section. |

| 1.5         | 07/16/03 | Updated features list, Table 1, DC Characteristics Over Operating Conditions table, and Table 3.                                                                               |

| 1.6         | 09/24/03 | Updated title to read "Product Specification" (removed "Advance")                                                                                                              |

| 1.7         | 10/18/04 | Extensive edits to update family from IQ to XA                                                                                                                                 |