Welcome to **E-XFL.COM**

What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded - Microcontrollers</u>"

| Details                    |                                                                           |

|----------------------------|---------------------------------------------------------------------------|

|                            |                                                                           |

| Product Status             | Active                                                                    |

| Core Processor             | PIC                                                                       |

| Core Size                  | 8-Bit                                                                     |

| Speed                      | 40MHz                                                                     |

| Connectivity               | I <sup>2</sup> C, SPI, UART/USART                                         |

| Peripherals                | Brown-out Detect/Reset, HLVD, POR, PWM, WDT                               |

| Number of I/O              | 25                                                                        |

| Program Memory Size        | 16KB (8K x 16)                                                            |

| Program Memory Type        | FLASH                                                                     |

| EEPROM Size                | 256 x 8                                                                   |

| RAM Size                   | 768 x 8                                                                   |

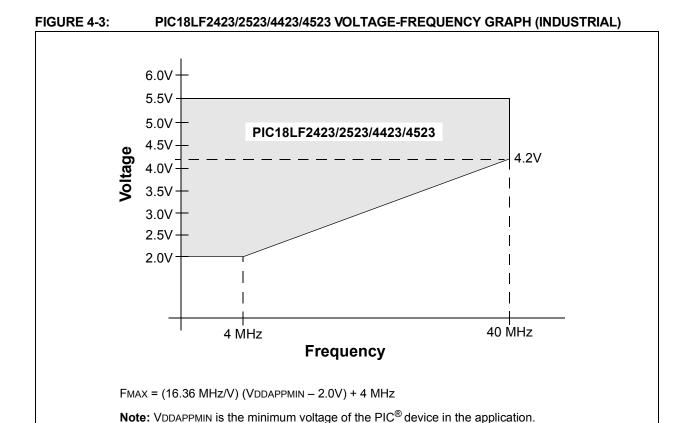

| Voltage - Supply (Vcc/Vdd) | 4.2V ~ 5.5V                                                               |

| Data Converters            | A/D 10x12b                                                                |

| Oscillator Type            | Internal                                                                  |

| Operating Temperature      | -40°C ~ 125°C (TA)                                                        |

| Mounting Type              | Through Hole                                                              |

| Package / Case             | 28-DIP (0.300", 7.62mm)                                                   |

| Supplier Device Package    | 28-SPDIP                                                                  |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/pic18f2423-e-sp |

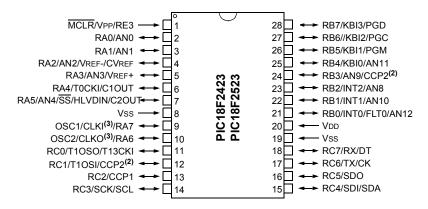

### **Pin Diagrams**

#### 28-Pin PDIP, SOIC

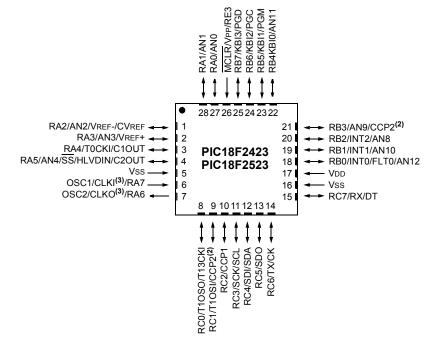

### 28-Pin QFN<sup>(1)</sup>

- Note 1: It is recommended to connect the bottom pad of QFN package parts to Vss.

- 2: RB3 is the alternate pin for CCP2 multiplexing.

- 3: OSC1/CLKI and OSC2/CLKO are only available in select oscillator modes and when these pins are not being used as digital I/O. For additional information, see Section 2.0 "Oscillator Configurations" of the "PIC18F2420/2520/4420/4520 Data Sheet" (DS39631).

#### 1.0 DEVICE OVERVIEW

This document contains device-specific information for the following devices:

PIC18F2423

PIC18F2423

PIC18F2523

PIC18F4423

PIC18F4423

PIC18F4523

PIC18LF4523

Note: This data sheet documents only the devices' features and specifications that are in addition to, or different from, the features and specifications of the PIC18F2420/2520/4420/4520 devices. For information on the features and specifications shared by the PIC18F2423/2523/4423/4523 and PIC18F2420/2520/4420/4520 devices, see the "PIC18F2420/2520/4420/4520 Data Sheet" (DS39631).

This family offers the advantages of all PIC18 microcontrollers – namely, high computational performance at an economical price – with the addition of high-endurance, Enhanced Flash program memory. On top of these features, the PIC18F2423/2523/4423/4523 family introduces design enhancements that make these microcontrollers a logical choice for many high-performance, power-sensitive applications.

#### 1.1 New Core Features

#### 1.1.1 nanoWatt TECHNOLOGY

All of the devices in the PIC18F2423/2523/4423/4523 family incorporate a range of features that can significantly reduce power consumption during operation. Key items include:

- Alternate Run Modes: By clocking the controller from the Timer1 source or the internal oscillator block, power consumption during code execution can be reduced by as much as 90%.

- Multiple Idle Modes: The controller also can run

with its CPU core disabled and the peripherals still

active. In these states, power consumption can be

reduced even further, to as little as 4% of normal

operation requirements.

- On-the-Fly Mode Switching: The power-managed modes are invoked by user code during operation, allowing the user to incorporate power-saving ideas into their application's software design.

- Low Consumption in Key Modules: The power requirements for both Timer1 and the Watchdog Timer are minimized. See Section 4.0 "Electrical Characteristics" for values.

# 1.1.2 MULTIPLE OSCILLATOR OPTIONS AND FEATURES

All of the devices in the PIC18F2423/2523/4423/4523 family offer ten different oscillator options, allowing users a wide range of choices in developing application hardware. These include:

- Four Crystal modes, using crystals or ceramic resonators.

- Two External Clock modes, offering the option of using two pins (oscillator input and a divide-by-4 clock output) or one pin (oscillator input, with the second pin reassigned as general I/O).

- Two External RC Oscillator modes with the same pin options as the External Clock modes.

- An internal oscillator block that offers eight clock frequencies: an 8 MHz clock and an INTRC source (approximately 31 kHz), as well as a range of six user-selectable clock frequencies, between 125 kHz to 4 MHz. This option frees the two oscillator pins for use as additional general purpose I/O.

- A Phase Lock Loop (PLL) frequency multiplier, available to both the High-Speed Crystal and Internal Oscillator modes, allowing clock speeds of up to 40 MHz from the HS clock source. Used with the internal oscillator, the PLL gives users a complete selection of clock speeds, from 31 kHz to 32 MHz, all without using an external crystal or clock circuit.

Besides its availability as a clock source, the internal oscillator block provides a stable reference source that gives the family additional features for robust operation:

- Fail-Safe Clock Monitor: Constantly monitors

the main clock source against a reference signal

provided by the internal oscillator. If a clock failure

occurs, the controller is switched to the internal

oscillator block, allowing for continued operation

or a safe application shutdown.

- Two-Speed Start-up: Allows the internal oscillator to serve as the clock source from Power-on Reset, or wake-up from Sleep mode, until the primary clock source is available.

TABLE 1-1: DEVICE FEATURES

| Features                                | PIC18F2423                                                                                 | PIC18F2523                                                                                 | PIC18F4423                                                                                 | PIC18F4523                                                                                 |

|-----------------------------------------|--------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------|

| Operating Frequency                     | DC – 40 MHz                                                                                |

| Program Memory (Bytes)                  | 16,384                                                                                     | 32,768                                                                                     | 16,384                                                                                     | 32,768                                                                                     |

| Program Memory (Instructions)           | 8,192                                                                                      | 16,384                                                                                     | 8,192                                                                                      | 16,384                                                                                     |

| Data Memory (Bytes)                     | 768                                                                                        | 1,536                                                                                      | 768                                                                                        | 1,536                                                                                      |

| Data EEPROM Memory (Bytes)              | 256                                                                                        | 256                                                                                        | 256                                                                                        | 256                                                                                        |

| Interrupt Sources                       | 19                                                                                         | 19                                                                                         | 20                                                                                         | 20                                                                                         |

| I/O Ports                               | Ports A, B, C, (E)                                                                         | Ports A, B, C, (E)                                                                         | Ports A, B, C, D, E                                                                        | Ports A, B, C, D, E                                                                        |

| Timers                                  | 4                                                                                          | 4                                                                                          | 4                                                                                          | 4                                                                                          |

| Capture/Compare/PWM Modules             | 2                                                                                          | 2                                                                                          | 1                                                                                          | 1                                                                                          |

| Enhanced<br>Capture/Compare/PWM Modules | 0                                                                                          | 0                                                                                          | 1                                                                                          | 1                                                                                          |

| Serial Communications                   | MSSP,<br>Enhanced USART                                                                    | MSSP,<br>Enhanced USART                                                                    | MSSP,<br>Enhanced USART                                                                    | MSSP,<br>Enhanced USART                                                                    |

| Parallel Communications (PSP)           | No                                                                                         | No                                                                                         | Yes                                                                                        | Yes                                                                                        |

| 12-Bit Analog-to-Digital Module         | 10 Input Channels                                                                          | 10 Input Channels                                                                          | 13 Input Channels                                                                          | 13 Input Channels                                                                          |

| Resets (and Delays)                     | POR, BOR, RESET Instruction, Stack Full, Stack Underflow (PWRT, OST), MCLR (optional), WDT | POR, BOR, RESET Instruction, Stack Full, Stack Underflow (PWRT, OST), MCLR (optional), WDT | POR, BOR, RESET Instruction, Stack Full, Stack Underflow (PWRT, OST), MCLR (optional), WDT | POR, BOR, RESET Instruction, Stack Full, Stack Underflow (PWRT, OST), MCLR (optional), WDT |

| Programmable<br>High/Low-Voltage Detect | Yes                                                                                        | Yes                                                                                        | Yes                                                                                        | Yes                                                                                        |

| Programmable Brown-out Reset            | Yes                                                                                        | Yes                                                                                        | Yes                                                                                        | Yes                                                                                        |

| Instruction Set                         | 75 Instructions;<br>83 with Extended<br>Instruction Set enabled                            |

| Packages                                | 28-Pin PDIP<br>28-Pin SOIC<br>28-Pin QFN                                                   | 28-Pin PDIP<br>28-Pin SOIC<br>28-Pin QFN                                                   | 40-Pin PDIP<br>44-Pin QFN<br>44-Pin TQFP                                                   | 40-Pin PDIP<br>44-Pin QFN<br>44-Pin TQFP                                                   |

TABLE 1-2: PIC18F2423/2523 PINOUT I/O DESCRIPTIONS

|               | Pin Number    |     | Pin  | Buffer   |                                                           |

|---------------|---------------|-----|------|----------|-----------------------------------------------------------|

| Pin Name      | PDIP,<br>SOIC | QFN | Туре |          | Description                                               |

| MCLR/VPP/RE3  | 1             | 26  |      |          | Master Clear (input) or programming voltage (input).      |

| MCLR          |               |     | I    | ST       | Master Clear (Reset) input. This pin is an active-low     |

| VPP           |               |     | Р    |          | Reset to the device. Programming voltage input.           |

| RE3           |               |     |      | ST       | Digital input.                                            |

| OSC1/CLKI/RA7 | 9             | 6   |      | <u> </u> | Oscillator crystal or external clock input.               |

| OSC1          |               | Ü   | I    | ST       | Oscillator crystal input or external clock source input.  |

|               |               |     |      |          | ST buffer when configured in RC mode; CMOS otherwise.     |

| CLKI          |               |     | I    | CMOS     |                                                           |

|               |               |     |      |          | function, OSC1. (See related OSC1/CLKI, OSC2/CLKO         |

| RA7           |               |     | I/O  | TTL      | pins.)<br>General purpose I/O pin.                        |

| OSC2/CLKO/RA6 | 10            | 7   |      |          | Oscillator crystal or clock output.                       |

| OSC2          |               | •   | 0    | _        | Oscillator crystal output. Connects to crystal or         |

|               |               |     |      |          | resonator in Crystal Oscillator mode.                     |

| CLKO          |               |     | 0    | _        | In RC mode, OSC2 pin outputs CLKO, which has 1/4 the      |

| RA6           |               |     | I/O  | TTI      | frequency of OSC1 and denotes the instruction cycle rate. |

| r\A0          |               |     | 1/0  | TTL      | General purpose I/O pin.                                  |

**Legend:** TTL = TTL compatible input

CMOS = CMOS compatible input or output

ST = Schmitt Trigger input with CMOS levels

I = Input P = Power

O = Output

$^{2}C = I^{2}C^{\dagger M}/SMBus$

Note 1: Default assignment for CCP2 when Configuration bit, CCP2MX, is set.

2: Alternate assignment for CCP2 when Configuration bit, CCP2MX, is cleared.

TABLE 1-3: PIC18F4423/4523 PINOUT I/O DESCRIPTIONS (CONTINUED)

| Din Nama                                          | Pi   | n Numb | er   | Pin             | Buffer                    | Boo and add and                                                                                               |

|---------------------------------------------------|------|--------|------|-----------------|---------------------------|---------------------------------------------------------------------------------------------------------------|

| Pin Name                                          | PDIP | QFN    | TQFP | Туре            | Type                      | Description                                                                                                   |

|                                                   |      |        |      |                 |                           | PORTB is a bidirectional I/O port. PORTB can be software programmed for internal weak pull-ups on all inputs. |

| RB0/INT0/FLT0/AN12<br>RB0<br>INT0<br>FLT0<br>AN12 | 33   | 9      | 8    | I/O<br>I<br>I   | TTL<br>ST<br>ST<br>Analog | Digital I/O. External Interrupt 0. PWM Fault input for Enhanced CCP1. Analog Input 12.                        |

| RB1/INT1/AN10<br>RB1<br>INT1<br>AN10              | 34   | 10     | 9    | I/O<br>I<br>I   | TTL<br>ST<br>Analog       | Digital I/O.<br>External Interrupt 1.<br>Analog Input 10.                                                     |

| RB2/INT2/AN8<br>RB2<br>INT2<br>AN8                | 35   | 11     | 10   | I/O<br>I<br>I   | TTL<br>ST<br>Analog       | Digital I/O.<br>External Interrupt 2.<br>Analog Input 8.                                                      |

| RB3/AN9/CCP2<br>RB3<br>AN9<br>CCP2 <sup>(1)</sup> | 36   | 12     | 11   | I/O<br>I<br>I/O | TTL<br>Analog<br>ST       | Digital I/O. Analog Input 9. Capture 2 input/Compare 2 output/PWM2 output.                                    |

| RB4/KBI0/AN11<br>RB4<br>KBI0<br>AN11              | 37   | 14     | 14   | I/O<br>I<br>I   | TTL<br>TTL<br>Analog      | Digital I/O.<br>Interrupt-on-change pin.<br>Analog Input 11.                                                  |

| RB5/KBI1/PGM<br>RB5<br>KBI1<br>PGM                | 38   | 15     | 15   | I/O<br>I<br>I/O | TTL<br>TTL<br>ST          | Digital I/O.<br>Interrupt-on-change pin.<br>Low-Voltage ICSP™ Programming enable pin.                         |

| RB6/KBI2/PGC<br>RB6<br>KBI2<br>PGC                | 39   | 16     | 16   | I/O<br>I<br>I/O | TTL<br>TTL<br>ST          | Digital I/O. Interrupt-on-change pin. In-Circuit Debugger and ICSP programming clock pin.                     |

| RB7/KBI3/PGD<br>RB7<br>KBI3<br>PGD                | 40   | 17     | 17   | I/O<br>I<br>I/O | TTL<br>TTL<br>ST          | Digital I/O. Interrupt-on-change pin. In-Circuit Debugger and ICSP programming data pin.                      |

Legend: TTL = TTL compatible input

ST = Schmitt Trigger input with CMOS levels

O = Output

$I^2C = I^2C^{TM}/SMBus$

CMOS = CMOS compatible input or output

I = Input

P = Power

Note 1: Default assignment for CCP2 when Configuration bit, CCP2MX, is set.

2: Alternate assignment for CCP2 when Configuration bit, CCP2MX, is cleared.

TABLE 1-3: PIC18F4423/4523 PINOUT I/O DESCRIPTIONS (CONTINUED)

| Pin Name                           | Piı  | n Numb | er   | Pin             | Buffer         | Description                                                                                                                                                                  |

|------------------------------------|------|--------|------|-----------------|----------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Pin Name                           | PDIP | QFN    | TQFP | Туре            | Type           | Description                                                                                                                                                                  |

|                                    |      |        |      |                 |                | PORTD is a bidirectional I/O port or a Parallel Slave Port (PSP) for interfacing to a microprocessor port. These pins have TTL input buffers when the PSP module is enabled. |

| RD0/PSP0<br>RD0<br>PSP0            | 19   | 38     | 38   | I/O<br>I/O      | ST<br>TTL      | Digital I/O.<br>Parallel Slave Port data.                                                                                                                                    |

| RD1/PSP1<br>RD1<br>PSP1            | 20   | 39     | 39   | I/O<br>I/O      | ST<br>TTL      | Digital I/O.<br>Parallel Slave Port data.                                                                                                                                    |

| RD2/PSP2<br>RD2<br>PSP2            | 21   | 40     | 40   | I/O<br>I/O      | ST<br>TTL      | Digital I/O.<br>Parallel Slave Port data.                                                                                                                                    |

| RD3/PSP3<br>RD3<br>PSP3            | 22   | 41     | 41   | I/O<br>I/O      | ST<br>TTL      | Digital I/O.<br>Parallel Slave Port data.                                                                                                                                    |

| RD4/PSP4<br>RD4<br>PSP4            | 27   | 2      | 2    | I/O<br>I/O      | ST<br>TTL      | Digital I/O.<br>Parallel Slave Port data.                                                                                                                                    |

| RD5/PSP5/P1B<br>RD5<br>PSP5<br>P1B | 28   | 3      | 3    | I/O<br>I/O<br>O | ST<br>TTL      | Digital I/O.<br>Parallel Slave Port data.<br>Enhanced CCP1 output.                                                                                                           |

| RD6/PSP6/P1C<br>RD6<br>PSP6<br>P1C | 29   | 4      | 4    | I/O<br>I/O<br>O | ST<br>TTL<br>— | Digital I/O.<br>Parallel Slave Port data.<br>Enhanced CCP1 output.                                                                                                           |

| RD7/PSP7/P1D<br>RD7<br>PSP7<br>P1D | 30   | 5      | 5    | I/O<br>I/O<br>O | ST<br>TTL<br>— | Digital I/O.<br>Parallel Slave Port data.<br>Enhanced CCP1 output.                                                                                                           |

**Legend:** TTL = TTL compatible input

ST = Schmitt Trigger input with CMOS levels

O = Output

$I^2C = I^2C^{TM}/SMBus$

CMOS = CMOS compatible input or output

I = Input P = Power

... ------

Note 1: Default assignment for CCP2 when Configuration bit, CCP2MX, is set.

2: Alternate assignment for CCP2 when Configuration bit, CCP2MX, is cleared.

NOTES:

#### 2.0 12-BIT ANALOG-TO-DIGITAL **CONVERTER (A/D) MODULE**

The Analog-to-Digital (A/D) Converter module has 10 inputs for the PIC18F2423/2523 devices and 13 for the PIC18F4423/4523 devices. This module allows conversion of an analog input signal to a corresponding 12-bit digital number.

The module has five registers:

- A/D Result High Register (ADRESH)

- A/D Result Low Register (ADRESL)

- A/D Control Register 0 (ADCON0)

- A/D Control Register 1 (ADCON1)

- A/D Control Register 2 (ADCON2)

Of the ADCONx registers:

- ADCON0 (shown in Register 2-1) Controls the module's operation

- · ADCON1 (Register 2-2) Configures the functions of the port pins

- ADCON2 (Register 2-3) Configures the A/D clock source, programmed acquisition time and justification

#### **REGISTER 2-1:** ADCON0: A/D CONTROL REGISTER 0

| U-0   | U-0        | R/W-0 | R/W-0 | R/W-0 | R/W-0 | R/W-0   | R/W-0 |  |

|-------|------------|-------|-------|-------|-------|---------|-------|--|

| _     | — — CHS3 C |       | CHS2  | CHS1  | CHS0  | GO/DONE | ADON  |  |

| bit 7 |            |       |       |       |       |         | bit 0 |  |

| Legend:           |                  |                       |                    |

|-------------------|------------------|-----------------------|--------------------|

| R = Readable bit  | W = Writable bit | U = Unimplemented bit | , read as '0'      |

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared  | x = Bit is unknown |

bit 7-6 Unimplemented: Read as '0'

bit 5-2 CHS<3:0>: Analog Channel Select bits

0000 = Channel 0 (AN0)

0001 = Channel 1 (AN1)

0010 = Channel 2 (AN2)

0011 = Channel 3 (AN3)

0100 = Channel 4 (AN4)

0101 = Channel 5 (AN5)(1,2) 0110 = Channel 6 (AN6)(1,2)

0111 = Channel 7 (AN7)(1,2)

1000 = Channel 8 (AN8)

1001 = Channel 9 (AN9)

1010 = Channel 10 (AN10)

1011 = Channel 11 (AN11)

1100 = Channel 12 (AN12

1101 = Unimplemented<sup>(2)</sup>

1110 = Unimplemented<sup>(2)</sup> 1111 = Unimplemented<sup>(2)</sup>

bit 1 GO/DONE: A/D Conversion Status bit

When ADON = 1:

1 = A/D conversion in progress

0 = A/D Idle

bit 0 ADON: A/D On bit

1 = A/D Converter module is enabled

0 = A/D Converter module is disabled

**Note 1:** These channels are not implemented on PIC18F2423/2523 devices.

Performing a conversion on unimplemented channels will return a floating input measurement.

#### REGISTER 2-2: ADCON1: A/D CONTROL REGISTER 1

| U-0   | U-0 | R/W-0 | R/W-0 | R/W-0 <sup>(1)</sup> | R/W <sup>(1)</sup> | R/W <sup>(1)</sup> | R/W <sup>(1)</sup> |

|-------|-----|-------|-------|----------------------|--------------------|--------------------|--------------------|

| _     | _   | VCFG1 | VCFG0 | PCFG3                | PCFG2              | PCFG1              | PCFG0              |

| bit 7 |     |       |       |                      |                    |                    | bit 0              |

Legend:

R = Readable bit W = Writable bit U = Unimplemented bit, read as '0'

-n = Value at POR '1' = Bit is set '0' = Bit is cleared x = Bit is unknown

bit 7-6 Unimplemented: Read as '0'

bit 5 VCFG1: Voltage Reference Configuration bit (VREF- source)

1 = VREF- (AN2)

0 **= V**ss

bit 4 VCFG0: Voltage Reference Configuration bit (VREF+ source)

1 = VREF+ (AN3)

0 = VDD

bit 3-0 **PCFG<3:0>:** A/D Port Configuration Control bits:

| PCFG<3:0> | AN12 | AN11 | AN10 | 6NA | AN8 | AN7 <sup>(2)</sup> | AN6 <sup>(2)</sup> | AN5 <sup>(2)</sup> | AN4 | AN3 | AN2 | AN1 | ANO |

|-----------|------|------|------|-----|-----|--------------------|--------------------|--------------------|-----|-----|-----|-----|-----|

|           | ٧    | ∢    | ٧    | ⋖   | 4   | ⋖                  | ⋖                  | ٧                  | ٧   | ٧   | ٧   | ٧   | ٧   |

| 0000(1)   | Α    | Α    | Α    | Α   | Α   | Α                  | Α                  | Α                  | Α   | Α   | Α   | Α   | Α   |

| 0001      | Α    | Α    | Α    | Α   | Α   | Α                  | Α                  | Α                  | Α   | Α   | Α   | Α   | Α   |

| 0010      | Α    | Α    | Α    | Α   | Α   | Α                  | Α                  | Α                  | Α   | Α   | Α   | Α   | Α   |

| 0011      | D    | Α    | Α    | Α   | Α   | Α                  | Α                  | Α                  | Α   | Α   | Α   | Α   | Α   |

| 0100      | D    | D    | Α    | Α   | Α   | Α                  | Α                  | Α                  | Α   | Α   | Α   | Α   | Α   |

| 0101      | D    | D    | D    | Α   | Α   | Α                  | Α                  | Α                  | Α   | Α   | Α   | Α   | Α   |

| 0110      | D    | D    | D    | D   | Α   | Α                  | Α                  | Α                  | Α   | Α   | Α   | Α   | Α   |

| 0111(1)   | D    | D    | D    | D   | D   | Α                  | Α                  | Α                  | Α   | Α   | Α   | Α   | Α   |

| 1000      | D    | D    | D    | D   | D   | D                  | Α                  | Α                  | Α   | Α   | Α   | Α   | Α   |

| 1001      | D    | D    | D    | D   | D   | D                  | D                  | Α                  | Α   | Α   | Α   | Α   | Α   |

| 1010      | D    | D    | D    | D   | D   | D                  | D                  | D                  | Α   | Α   | Α   | Α   | Α   |

| 1011      | D    | D    | D    | D   | D   | D                  | D                  | D                  | D   | Α   | Α   | Α   | Α   |

| 1100      | D    | D    | D    | D   | D   | D                  | D                  | D                  | D   | D   | Α   | Α   | Α   |

| 1101      | D    | D    | D    | D   | D   | D                  | D                  | D                  | D   | D   | D   | Α   | Α   |

| 1110      | D    | D    | D    | D   | D   | D                  | D                  | D                  | D   | D   | D   | D   | Α   |

| 1111      | D    | D    | D    | D   | D   | D                  | D                  | D                  | D   | D   | D   | D   | D   |

A = Analog input

D = Digital I/O

**Note 1:** The POR value of the PCFG bits depends on the value of the PBADEN Configuration bit. When PBADEN = 1, PCFG<3:0> = 0000; when PBADEN = 0, PCFG<3:0> = 0111.

2: AN5 through AN7 are only available on PIC18F4423/4523 devices.

### 2.1 A/D Acquisition Requirements

For the A/D Converter to meet its specified accuracy, the charge holding capacitor (CHOLD) must be allowed to fully charge to the input channel voltage level. The analog input model is shown in Figure 2-3.

The source impedance (Rs) and the internal sampling switch (Rss) impedance directly affect the time required to charge the capacitor, CHOLD. The sampling switch (Rss) impedance varies over the device voltage (VDD). The source impedance affects the offset voltage at the analog input (due to pin leakage current). The maximum recommended impedance for analog sources is 2.5 k $\Omega$ .

After the analog input channel is selected (changed), the channel must be sampled for at least the minimum acquisition time before starting a conversion.

**Note:** When the conversion is started, the holding capacitor is disconnected from the input pin.

To calculate the minimum acquisition time, Equation 2-1 may be used. This equation assumes that 1/2 LSb error is used (4,096 steps for the A/D). The 1/2 LSb error is the maximum error allowed for the A/D to meet its specified resolution.

Example 2-3 shows the calculation of the minimum required acquisition time, TACQ. This calculation is based on the application system assumptions shown in Table 2-1:

TABLE 2-1: TACQ ASSUMPTIONS

| CHOLD            | = | 25 pF                                    |

|------------------|---|------------------------------------------|

| Rs               | = | 2.5 kΩ                                   |

| Conversion Error | ≤ | 1/2 LSb                                  |

| VDD              | = | $3V \rightarrow Rss = 4 \text{ k}\Omega$ |

| Temperature      | = | 85°C (system maximum)                    |

#### **EQUATION 2-1: ACQUISITION TIME**

```

TACQ = Amplifier Settling Time + Holding Capacitor Charging Time + Temperature Coefficient

= TAMP + TC + TCOFF

```

### **EQUATION 2-2: A/D MINIMUM CHARGING TIME**

```

V_{HOLD} = (V_{REF} - (V_{REF}/4096)) \cdot (1 - e^{(-T_{C}/C_{HOLD}(R_{IC} + R_{SS} + R_{S}))})

or

T_{C} = -(C_{HOLD})(R_{IC} + R_{SS} + R_{S}) \ln(1/4096)

```

#### **EQUATION 2-3: CALCULATING THE MINIMUM REQUIRED ACQUISITION TIME**

```

TACQ = TAMP + TC + TCOFF

TAMP = 0.2 \,\mu s

TCOFF = (Temp - 25°C)(0.02 \,\mu s/°C)

(85^{\circ}C - 25^{\circ}C)(0.02 \,\mu s/°C)

1.2 \,\mu s

Temperature coefficient is only required for temperatures > 25°C. Below 25°C, TCOFF = 0 ms.

TC = -(CHOLD)(RIC + RSS + RS) ln(1/4095) \mu s

-(25 \,p F) (1 \,k \Omega + 4 \,k \Omega + 2.5 \,k \Omega) ln(0.0004883) \,\mu s

1.56 \,\mu s

TACQ = 0.2 \,\mu s + 1.56 \,\mu s + 1.2 \,\mu s

2.96 \,\mu s

```

### 2.8 Use of the CCP2 Trigger

An A/D conversion can be started by the Special Event Trigger of the CCP2 module. This requires that the CCP2M<3:0> bits (CCP2CON<3:0>) be programmed as '1011' and that the A/D module is enabled (ADON bit is set). When the trigger occurs, the GO/DONE bit will be set, starting the A/D acquisition and conversion, and the Timer1 (or Timer3) counter will be reset to zero. Timer1 (or Timer3) is reset to automatically repeat the A/D acquisition period with minimal software overhead (moving ADRESH:ADRESL to the desired location).

The appropriate analog input channel must be selected and the minimum acquisition period is either timed by the user or an appropriate TACQ time is selected before the Special Event Trigger sets the GO/DONE bit (starts a conversion).

If the A/D module is not enabled (ADON is cleared), the Special Event Trigger will be ignored by the A/D module, but will still reset the Timer1 (or Timer3) counter.

TABLE 2-3: REGISTERS ASSOCIATED WITH A/D OPERATION

| Name                 | Bit 7                         | Bit 6                 | Bit 5       | Bit 4         | Bit 3              | Bit 2   | Bit 1        | Bit 0  | Reset<br>Values on<br>page |  |  |

|----------------------|-------------------------------|-----------------------|-------------|---------------|--------------------|---------|--------------|--------|----------------------------|--|--|

| INTCON               | GIE/GIEH                      | PEIE/GIEL             | TMR0IE      | INT0IE        | RBIE               | TMR0IF  | INT0IF       | RBIF   | (Note 4)                   |  |  |

| PIR1                 | PSPIF <sup>(1)</sup>          | ADIF                  | RCIF        | TXIF          | SSPIF              | CCP1IF  | TMR2IF       | TMR1IF | (Note 4)                   |  |  |

| PIE1                 | PSPIE <sup>(1)</sup>          | ADIE                  | RCIE        | TXIE          | SSPIE              | CCP1IE  | TMR2IE       | TMR1IE | (Note 4)                   |  |  |

| IPR1                 | PSPIP <sup>(1)</sup>          | ADIP                  | RCIP        | TXIP          | SSPIP              | CCP1IP  | TMR2IP       | TMR1IP | (Note 4)                   |  |  |

| PIR2                 | OSCFIF                        | CMIF                  | _           | EEIF          | BCLIF              | HLVDIF  | TMR3IF       | CCP2IF | (Note 4)                   |  |  |

| PIE2                 | OSCFIE                        | CMIE                  | _           | EEIE          | BCLIE              | HLVDIE  | TMR3IE       | CCP2IE | (Note 4)                   |  |  |

| IPR2                 | OSCFIP                        | CMIP                  | _           | EEIP          | BCLIP              | HLVDIP  | TMR3IP       | CCP2IP | (Note 4)                   |  |  |

| ADRESH               | A/D Result Register High Byte |                       |             |               |                    |         |              |        |                            |  |  |

| ADRESL               | A/D Result Register Low Byte  |                       |             |               |                    |         |              |        |                            |  |  |

| ADCON0               | _                             | _                     | CHS3        | CHS2          | CHS1               | CHS0    | GO/DONE      | ADON   | (Note 4)                   |  |  |

| ADCON1               | _                             | _                     | VCFG1       | VCFG0         | PCFG3              | PCFG2   | PCFG1        | PCFG0  | (Note 4)                   |  |  |

| ADCON2               | ADFM                          | _                     | ACQT2       | ACQT1         | ACQT0              | ADCS2   | ADCS1        | ADCS0  | (Note 4)                   |  |  |

| PORTA                | RA7 <sup>(2)</sup>            | RA6 <sup>(2)</sup>    | RA5         | RA4           | RA3                | RA2     | RA1          | RA0    | (Note 4)                   |  |  |

| TRISA                | TRISA7 <sup>(2)</sup>         | TRISA6 <sup>(2)</sup> | PORTA Da    | ata Direction | Control Re         | gister  |              |        | (Note 4)                   |  |  |

| PORTB                | RB7                           | RB6                   | RB5         | RB4           | RB3                | RB2     | RB1          | RB0    | (Note 4)                   |  |  |

| TRISB                | PORTB Dat                     | a Direction (         | Control Reg | ister         |                    |         |              |        | (Note 4)                   |  |  |

| LATB                 | PORTB Dat                     | a Latch Reg           | ister (Read | and Write to  | Data Latc          | h)      |              |        | (Note 4)                   |  |  |

| PORTE <sup>(1)</sup> | _                             | _                     | _           | _             | RE3 <sup>(3)</sup> | RE2     | RE1          | RE0    | (Note 4)                   |  |  |

| TRISE <sup>(1)</sup> | IBF                           | OBF                   | IBOV        | PSPMODE       | _                  | TRISE2  | TRISE1       | TRISE0 | (Note 4)                   |  |  |

| LATE <sup>(1)</sup>  | _                             | _                     |             | _             | _                  | PORTE D | ata Latch Re | gister | (Note 4)                   |  |  |

**Legend:** — = unimplemented, read as '0'. Shaded cells are not used for A/D conversion.

- Note 1: These registers and/or bits are not implemented on PIC18F2423/2523 devices and are read as '0'.

- 2: PORTA<7:6> and their direction bits are individually configured as port pins based on various primary oscillator modes. When disabled, these bits read as '0'.

- 3: RE3 port bit is available only as an input pin when the MCLRE Configuration bit is '0'.

- **4:** For these Reset values, see **Section 4.0 "Reset"** of the "*PIC18F2420/2520/4420/4520 Data Sheet"* (DS39631).

# 3.0 SPECIAL FEATURES OF THE CPU

# Note: For additional details on the Configuration bits, refer to Section 23.1 "Configuration

**Bits"** in the "PIC18F2420/2520/4420/4520 Data Sheet" (DS39631). Device ID information presented in this section is for the PIC18F2423/2523/4423/4523 devices only.

### 3.1 Device ID Registers

The Device ID registers are read-only registers. They identify the device type and revision for device programmers and can be read by firmware using table reads.

#### TABLE 3-1: DEVICE IDs

| File    | Name                  | Bit 7 | Bit 6 | Bit 5 | Bit 4 | Bit 3 | Bit 2 | Bit 1 | Bit 0 | Default/<br>Unprogrammed<br>Value |

|---------|-----------------------|-------|-------|-------|-------|-------|-------|-------|-------|-----------------------------------|

| 3FFFEh  | DEVID1 <sup>(1)</sup> | DEV3  | DEV2  | DEV1  | DEV0  | REV3  | REV2  | REV1  | REV0  | XXXX XXXX(2)                      |

| 3FFFFFh | DEVID2 <sup>(1)</sup> | DEV11 | DEV10 | DEV9  | DEV8  | DEV7  | DEV6  | DEV5  | DEV4  | ×××× ××××(2)                      |

**Legend:** x = unknown, u = unchanged, — = unimplemented. Shaded cells are unimplemented, read as '0'.

Note 1: DEVID registers are read-only and cannot be programmed by the user.

2: See Register 3-1 and Register 3-2 for DEVID1 and DEVID2 values.

### REGISTER 3-1: DEVID1: DEVICE ID REGISTER 1 FOR PIC18F2423/2523/4423/4523

| R     | R    | R    | R    | R    | R    | R    | R     |

|-------|------|------|------|------|------|------|-------|

| DEV3  | DEV2 | DEV1 | DEV0 | REV3 | REV2 | REV1 | REV0  |

| bit 7 |      |      |      |      |      |      | bit 0 |

### Legend:

R = Read-only bit P = Programmable bit U = Unimplemented bit, read as '0'

-n = Value when device is unprogrammed u = Unchanged from programmed state

bit 7-4 **DEV<3:0>:** Device ID bits

1101 = PIC18F4423 1001 = PIC18F4523 0101 = PIC18F2423 0001 = PIC18F2523

bit 3-0 REV<3:0>: Revision ID bits

These bits are used to indicate the device revision.

### REGISTER 3-2: DEVID2: DEVICE ID REGISTER 2 FOR PIC18F2423/2523/4423/4523

| R                    | R                    | R                   | R                   | R                   | R                   | R                   | R                   |

|----------------------|----------------------|---------------------|---------------------|---------------------|---------------------|---------------------|---------------------|

| DEV11 <sup>(1)</sup> | DEV10 <sup>(1)</sup> | DEV9 <sup>(1)</sup> | DEV8 <sup>(1)</sup> | DEV7 <sup>(1)</sup> | DEV6 <sup>(1)</sup> | DEV5 <sup>(1)</sup> | DEV4 <sup>(1)</sup> |

| bit 7                |                      |                     |                     |                     |                     |                     | bit 0               |

Legend:

R = Read-only bit P = Programmable bit U = Unimplemented bit, read as '0'

-n = Value when device is unprogrammed u = Unchanged from programmed state

bit 7-0 **DEV<11:4>:** Device ID bits<sup>(1)</sup>

These bits are used with the DEV<3:0> bits in Device ID Register 1 to identify the part number.

0001 0001 = PIC18F2423/2523 devices 0001 0000 = PIC18F4423/4523 devices

**Note 1:** These values for DEV<11:4> may be shared with other devices. The specific device is always identified by using the entire DEV<11:0> bit sequence.

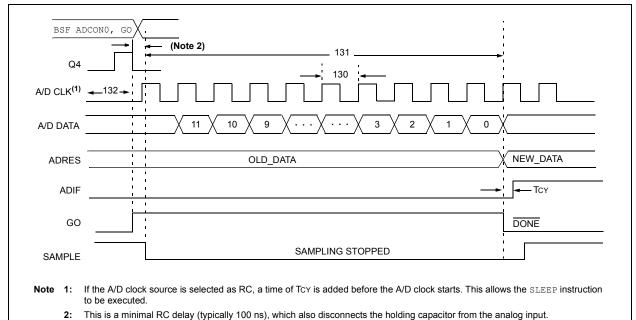

FIGURE 4-4: A/D CONVERSION TIMING

TABLE 4-2: A/D CONVERSION REQUIREMENTS

| Param<br>No. | Symbol | Characteristic                             |                      | Min      | Max                 | Units | Conditions                                                         |

|--------------|--------|--------------------------------------------|----------------------|----------|---------------------|-------|--------------------------------------------------------------------|

| 130          | TAD    | A/D Clock Period                           | PIC18FXXXX           | 8.0      | 12.5 <sup>(1)</sup> | μS    | Tosc based, VREF ≥ 3.0V                                            |

|              |        |                                            | PIC18 <b>LF</b> XXXX | 1.4      | 25.0 <sup>(1)</sup> | μS    | V <sub>DD</sub> = 3.0V;<br>Tosc based, V <sub>REF</sub> full range |

|              |        |                                            | PIC18FXXXX           | _        | 1                   | μS    | A/D RC mode                                                        |

|              |        |                                            | PIC18 <b>LF</b> XXXX | _        | 3                   | μS    | VDD = 3.0V; A/D RC mode                                            |

| 131          | TCNV   | Conversion Time (not including acquisition | 13                   | 14       | TAD                 |       |                                                                    |

| 132          | TACQ   | Acquisition Time <sup>(3)</sup>            | 1.4                  | _        | μS                  |       |                                                                    |

| 135          | Tswc   | Switching Time from C                      | _                    | (Note 4) |                     |       |                                                                    |

| 137          | TDIS   | Discharge Time                             | 0.2                  | _        | μS                  |       |                                                                    |

Note 1: The time of the A/D clock period is dependent on the device frequency and the TAD clock divider.

- 2: ADRES registers may be read on the following TcY cycle.

- 3: The time for the holding capacitor to acquire the "New" input voltage when the voltage changes full scale after the conversion (VDD to Vss or Vss to VDD). The source impedance (Rs) on the input channels is 50Ω.

- 4: On the following cycle of the device clock.

NOTES:

### **APPENDIX A: REVISION HISTORY**

### Revision A (June 2006)

Original data sheet for PIC18F2423/2523/4423/4523 devices.

### **Revision B (January 2007)**

This revision includes updates to the packaging diagrams.

### Revision C (September 2009)

Electrical specifications updated. Preliminary condition status removed. Converted document to the "mini data sheet" format.

# APPENDIX B: DEVICE DIFFERENCES

The differences between the devices listed in this data sheet are shown in Table B-1.

TABLE B-1: DEVICE DIFFERENCES

| Features                             | PIC18F2423                               | PIC18F2523                               | PIC18F4423                               | PIC18F4523                               |

|--------------------------------------|------------------------------------------|------------------------------------------|------------------------------------------|------------------------------------------|

| Program Memory (Bytes)               | 16384                                    | 32768                                    | 16384                                    | 32768                                    |

| Program Memory (Instructions)        | 8192                                     | 16384                                    | 8192                                     | 16384                                    |

| Interrupt Sources                    | 19                                       | 19                                       | 20                                       | 20                                       |

| I/O Ports                            | Ports A, B, C, (E)                       | Ports A, B, C, (E)                       | Ports A, B, C, D, E                      | Ports A, B, C, D, E                      |

| Capture/Compare/PWM Modules          | 2                                        | 2                                        | 1                                        | 1                                        |

| Enhanced Capture/Compare/PWM Modules | 0                                        | 0                                        | 1                                        | 1                                        |

| Parallel Communications (PSP)        | No                                       | No                                       | Yes                                      | Yes                                      |

| 12-Bit Analog-to-Digital Module      | 10 Input Channels                        | 10 Input Channels                        | 13 Input Channels                        | 13 Input Channels                        |

| Packages                             | 28-Pin PDIP<br>28-Pin SOIC<br>28-Pin QFN | 28-Pin PDIP<br>28-Pin SOIC<br>28-Pin QFN | 40-Pin PDIP<br>44-Pin TQFP<br>44-Pin QFN | 40-Pin PDIP<br>44-Pin TQFP<br>44-Pin QFN |

# APPENDIX C: CONVERSION CONSIDERATIONS

This appendix discusses the considerations for converting from previous versions of a device to the ones listed in this data sheet. Typically, these changes are due to the differences in the process technology used. An example of this type of conversion is from a PIC16C74A to a PIC16C74B.

**Not Applicable**

# APPENDIX D: MIGRATION FROM BASELINE TO ENHANCED DEVICES

This section discusses how to migrate from a Baseline device (i.e., PIC16C5X) to an Enhanced MCU device (i.e., PIC18FXXX).

The following are the list of modifications over the PIC16C5X microcontroller family:

**Not Currently Available**

### PRODUCT IDENTIFICATION SYSTEM

To order or obtain information, e.g., on pricing or delivery, refer to the factory or the listed sales office.

| PART NO.<br>Device | X /XX XXX<br>     <br>Temperature Package Pattern<br>Range                                                                                                                                                                                                                        | Examples:  a) PIC18F4523-I/P 301 = Industrial temp., PDIP package, Extended VDD limits, QTP pattern #301.  b) PIC18F4523-I/PT = Industrial temp., TQFP |

|--------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------|

| Device             | PIC18F2423 <sup>(1)</sup> , PIC18F2523 <sup>(1)</sup> , PIC18F4423T <sup>(2)</sup> , PIC18F4523T <sup>(2)</sup> ; VDD range 4.2V to 5.5V PIC18F2423 <sup>(1)</sup> , PIC18F2523 <sup>(1)</sup> , PIC18F4423T <sup>(2)</sup> , PIC18F4523T <sup>(2)</sup> ; VDD range 2.0V to 5.5V | package, Extended VDD limits.  c) PIC18F4523-E/P = Extended temp., PDIP package, normal VDD limits.                                                    |

| Temperature Range  | I = -40°C to +85°C (Industrial)<br>E = -40°C to +125°C (Extended)                                                                                                                                                                                                                 |                                                                                                                                                        |

| Package            | PT = TQFP (Thin Quad Flat pack) ML = QFN SO = SOIC SP = Skinny Plastic DIP P = PDIP                                                                                                                                                                                               | Note 1: F = Standard Voltage Range  LF = Wide Voltage Range  2: T = In tape and reel PLCC, and TQFP packages only.                                     |

| Pattern            | QTP, SQTP, Code or Special Requirements (blank otherwise)                                                                                                                                                                                                                         |                                                                                                                                                        |

### WORLDWIDE SALES AND SERVICE

#### **AMERICAS**

Corporate Office

2355 West Chandler Blvd. Chandler, AZ 85224-6199 Tel: 480-792-7200

Fax: 480-792-7277 Technical Support:

http://support.microchip.com

Web Address: www.microchip.com

Atlanta

Duluth, GA Tel: 678-957-9614 Fax: 678-957-1455

**Boston**

Westborough, MA Tel: 774-760-0087 Fax: 774-760-0088

Chicago

Itasca, IL Tel: 630-285-0071 Fax: 630-285-0075

Cleveland

Independence, OH Tel: 216-447-0464 Fax: 216-447-0643

**Dallas**

Addison, TX Tel: 972-818-7423 Fax: 972-818-2924

Detroit

Farmington Hills, MI Tel: 248-538-2250 Fax: 248-538-2260

Kokomo

Kokomo, IN Tel: 765-864-8360 Fax: 765-864-8387

Los Angeles

Mission Viejo, CA Tel: 949-462-9523 Fax: 949-462-9608

Santa Clara

Santa Clara, CA Tel: 408-961-6444 Fax: 408-961-6445

Toronto

Mississauga, Ontario,

Canada

Tel: 905-673-0699 Fax: 905-673-6509

#### ASIA/PACIFIC

**Asia Pacific Office**

Suites 3707-14, 37th Floor Tower 6, The Gateway Harbour City, Kowloon

Hong Kong Tel: 852-2401-1200 Fax: 852-2401-3431

Australia - Sydney

Tel: 61-2-9868-6733 Fax: 61-2-9868-6755

China - Beijing

Tel: 86-10-8528-2100 Fax: 86-10-8528-2104

China - Chengdu

Tel: 86-28-8665-5511 Fax: 86-28-8665-7889

China - Hong Kong SAR

Tel: 852-2401-1200 Fax: 852-2401-3431

China - Nanjing

Tel: 86-25-8473-2460 Fax: 86-25-8473-2470

China - Qingdao

Tel: 86-532-8502-7355 Fax: 86-532-8502-7205

China - Shanghai

Tel: 86-21-5407-5533 Fax: 86-21-5407-5066

China - Shenyang

Tel: 86-24-2334-2829 Fax: 86-24-2334-2393

China - Shenzhen

Tel: 86-755-8203-2660 Fax: 86-755-8203-1760

China - Wuhan

Tel: 86-27-5980-5300 Fax: 86-27-5980-5118

China - Xiamen

Tel: 86-592-2388138 Fax: 86-592-2388130

China - Xian

Tel: 86-29-8833-7252 Fax: 86-29-8833-7256

China - Zhuhai

Tel: 86-756-3210040 Fax: 86-756-3210049

#### ASIA/PACIFIC

India - Bangalore

Tel: 91-80-3090-4444 Fax: 91-80-3090-4080

India - New Delhi

Tel: 91-11-4160-8631 Fax: 91-11-4160-8632

India - Pune

Tel: 91-20-2566-1512 Fax: 91-20-2566-1513

Japan - Yokohama

Tel: 81-45-471- 6166 Fax: 81-45-471-6122

Korea - Daegu

Tel: 82-53-744-4301 Fax: 82-53-744-4302

Korea - Seoul

Tel: 82-2-554-7200 Fax: 82-2-558-5932 or 82-2-558-5934

Malaysia - Kuala Lumpur

Tel: 60-3-6201-9857 Fax: 60-3-6201-9859

Malaysia - Penang

Tel: 60-4-227-8870 Fax: 60-4-227-4068

Philippines - Manila

Tel: 63-2-634-9065 Fax: 63-2-634-9069

Singapore

Tel: 65-6334-8870 Fax: 65-6334-8850

Taiwan - Hsin Chu

Tel: 886-3-6578-300 Fax: 886-3-6578-370

Taiwan - Kaohsiung

Tel: 886-7-536-4818 Fax: 886-7-536-4803

Taiwan - Taipei

Tel: 886-2-2500-6610 Fax: 886-2-2508-0102

Thailand - Bangkok

Tel: 66-2-694-1351 Fax: 66-2-694-1350

#### **EUROPE**

Austria - Wels

Tel: 43-7242-2244-39 Fax: 43-7242-2244-393

Denmark - Copenhagen

Tel: 45-4450-2828 Fax: 45-4485-2829

France - Paris

Tel: 33-1-69-53-63-20 Fax: 33-1-69-30-90-79

**Germany - Munich**

Tel: 49-89-627-144-0 Fax: 49-89-627-144-44

Italy - Milan

Tel: 39-0331-742611 Fax: 39-0331-466781

Netherlands - Drunen

Tel: 31-416-690399 Fax: 31-416-690340

Spain - Madrid

Tel: 34-91-708-08-90 Fax: 34-91-708-08-91

**UK - Wokingham** Tel: 44-118-921-5869

Tel: 44-118-921-5869 Fax: 44-118-921-5820

03/26/09