Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Details                    |                                                                            |

|----------------------------|----------------------------------------------------------------------------|

| Product Status             | Active                                                                     |

| Core Processor             | PIC                                                                        |

| Core Size                  | 8-Bit                                                                      |

| Speed                      | 40MHz                                                                      |

| Connectivity               | I <sup>2</sup> C, SPI, UART/USART                                          |

| Peripherals                | Brown-out Detect/Reset, HLVD, POR, PWM, WDT                                |

| Number of I/O              | 25                                                                         |

| Program Memory Size        | 32KB (16K x 16)                                                            |

| Program Memory Type        | FLASH                                                                      |

| EEPROM Size                | 256 x 8                                                                    |

| RAM Size                   | 1.5К х 8                                                                   |

| Voltage - Supply (Vcc/Vdd) | 2V ~ 5.5V                                                                  |

| Data Converters            | A/D 10x12b                                                                 |

| Oscillator Type            | Internal                                                                   |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                          |

| Mounting Type              | Through Hole                                                               |

| Package / Case             | 28-DIP (0.300", 7.62mm)                                                    |

| Supplier Device Package    | 28-SPDIP                                                                   |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/pic18lf2523-i-sp |

|                            |                                                                            |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

#### Note the following details of the code protection feature on Microchip devices:

- Microchip products meet the specification contained in their particular Microchip Data Sheet.

- Microchip believes that its family of products is one of the most secure families of its kind on the market today, when used in the intended manner and under normal conditions.

- There are dishonest and possibly illegal methods used to breach the code protection feature. All of these methods, to our knowledge, require using the Microchip products in a manner outside the operating specifications contained in Microchip's Data Sheets. Most likely, the person doing so is engaged in theft of intellectual property.

- Microchip is willing to work with the customer who is concerned about the integrity of their code.

- Neither Microchip nor any other semiconductor manufacturer can guarantee the security of their code. Code protection does not mean that we are guaranteeing the product as "unbreakable."

Code protection is constantly evolving. We at Microchip are committed to continuously improving the code protection features of our products. Attempts to break Microchip's code protection feature may be a violation of the Digital Millennium Copyright Act. If such acts allow unauthorized access to your software or other copyrighted work, you may have a right to sue for relief under that Act.

Information contained in this publication regarding device applications and the like is provided only for your convenience and may be superseded by updates. It is your responsibility to ensure that your application meets with your specifications. MICROCHIP MAKES NO REPRESENTATIONS OR WARRANTIES OF ANY KIND WHETHER EXPRESS OR IMPLIED, WRITTEN OR ORAL, STATUTORY OR OTHERWISE, RELATED TO THE INFORMATION, INCLUDING BUT NOT LIMITED TO ITS CONDITION. QUALITY, PERFORMANCE, MERCHANTABILITY OR FITNESS FOR PURPOSE. Microchip disclaims all liability arising from this information and its use. Use of Microchip devices in life support and/or safety applications is entirely at the buyer's risk, and the buyer agrees to defend, indemnify and hold harmless Microchip from any and all damages, claims, suits, or expenses resulting from such use. No licenses are conveyed, implicitly or otherwise, under any Microchip intellectual property rights.

#### Trademarks

The Microchip name and logo, the Microchip logo, dsPIC, KEELOQ, KEELOQ logo, MPLAB, PIC, PICmicro, PICSTART, rfPIC and UNI/O are registered trademarks of Microchip Technology Incorporated in the U.S.A. and other countries.

FilterLab, Hampshire, HI-TECH C, Linear Active Thermistor, MXDEV, MXLAB, SEEVAL and The Embedded Control Solutions Company are registered trademarks of Microchip Technology Incorporated in the U.S.A.

Analog-for-the-Digital Age, Application Maestro, CodeGuard, dsPICDEM, dsPICDEM.net, dsPICworks, dsSPEAK, ECAN, ECONOMONITOR, FanSense, HI-TIDE, In-Circuit Serial Programming, ICSP, Mindi, MiWi, MPASM, MPLAB Certified logo, MPLIB, MPLINK, mTouch, Octopus, Omniscient Code Generation, PICC, PICC-18, PICDEM, PICDEM.net, PICkit, PICtail, PIC<sup>32</sup> logo, REAL ICE, rfLAB, Select Mode, Total Endurance, TSHARC, UniWinDriver, WiperLock and ZENA are trademarks of Microchip Technology Incorporated in the U.S.A. and other countries.

$\ensuremath{\mathsf{SQTP}}$  is a service mark of Microchip Technology Incorporated in the U.S.A.

All other trademarks mentioned herein are property of their respective companies.

© 2009, Microchip Technology Incorporated, Printed in the U.S.A., All Rights Reserved.

# QUALITY MANAGEMENT SYSTEM CERTIFIED BY DNV ISO/TS 16949:2002

Microchip received ISO/TS-16949:2002 certification for its worldwide headquarters, design and wafer fabrication facilities in Chandler and Tempe, Arizona; Gresham, Oregon and design centers in California and India. The Company's quality system processes and procedures are for its PIC® MCUs and dsPIC® DSCs, KEELOQ® code hopping devices, Serial EEPROMs, microperipherals, nonvolatile memory and analog products. In addition, Microchip's quality system for the design and manufacture of development systems is ISO 9001:2000 certified.

# TO OUR VALUED CUSTOMERS

It is our intention to provide our valued customers with the best documentation possible to ensure successful use of your Microchip products. To this end, we will continue to improve our publications to better suit your needs. Our publications will be refined and enhanced as new volumes and updates are introduced.

If you have any questions or comments regarding this publication, please contact the Marketing Communications Department via E-mail at **docerrors@microchip.com** or fax the **Reader Response Form** in the back of this data sheet to (480) 792-4150. We welcome your feedback.

### Most Current Data Sheet

To obtain the most up-to-date version of this data sheet, please register at our Worldwide Web site at:

http://www.microchip.com

You can determine the version of a data sheet by examining its literature number found on the bottom outside corner of any page. The last character of the literature number is the version number, (e.g., DS30000A is version A of document DS30000).

### Errata

An errata sheet, describing minor operational differences from the data sheet and recommended workarounds, may exist for current devices. As device/documentation issues become known to us, we will publish an errata sheet. The errata will specify the revision of silicon and revision of document to which it applies.

To determine if an errata sheet exists for a particular device, please check with one of the following:

- Microchip's Worldwide Web site; http://www.microchip.com

- Your local Microchip sales office (see last page)

When contacting a sales office, please specify which device, revision of silicon and data sheet (include literature number) you are using.

### **Customer Notification System**

Register on our web site at www.microchip.com to receive the most current information on all of our products.

- **2:** RE3 is only available when MCLR functionality is disabled.

- 3: OSC1/CLKI and OSC2/CLKO are only available in select oscillator modes and when these pins are not being used as digital I/O. For additional information, see Section 2.0 "Oscillator Configurations" of the "PIC18F2420/2520/4420/4520 Data Sheet" (DS39631).

|                                  | Pin Number    |          | Pin         | Buffer        |                                                          |  |  |  |

|----------------------------------|---------------|----------|-------------|---------------|----------------------------------------------------------|--|--|--|

| Pin Name                         | PDIP,<br>SOIC | QFN      | Ріп<br>Туре | винег<br>Туре | Description                                              |  |  |  |

|                                  |               |          |             |               | PORTA is a bidirectional I/O port.                       |  |  |  |

| RA0/AN0                          | 2             | 27       |             |               |                                                          |  |  |  |

| RA0                              |               |          | I/O         | TTL           | Digital I/O.                                             |  |  |  |

| AN0                              |               |          | I           | Analog        | Analog Input 0.                                          |  |  |  |

| RA1/AN1                          | 3             | 28       |             |               |                                                          |  |  |  |

| RA1                              |               |          | I/O         | TTL           | Digital I/O.                                             |  |  |  |

| AN1                              |               |          | I           | Analog        | Analog Input 1.                                          |  |  |  |

| RA2/AN2/VREF-/CVREF              | 4             | 1        |             |               |                                                          |  |  |  |

| RA2                              |               |          | I/O         | TTL           | Digital I/O.                                             |  |  |  |

| AN2                              |               |          | I           | Analog        |                                                          |  |  |  |

| VREF-                            |               |          |             | Analog        |                                                          |  |  |  |

| CVREF                            |               |          | 0           | Analog        | Comparator reference voltage output.                     |  |  |  |

| RA3/AN3/VREF+                    | 5             | 2        |             |               |                                                          |  |  |  |

| RA3                              |               |          | I/O         | TTL           | Digital I/O.                                             |  |  |  |

| AN3                              |               |          |             | Analog        |                                                          |  |  |  |

| VREF+                            |               |          | I           | Analog        | A/D reference voltage (high) input.                      |  |  |  |

| RA4/T0CKI/C1OUT                  | 6             | 3        |             |               |                                                          |  |  |  |

| RA4                              |               |          | I/O         | ST            | Digital I/O.                                             |  |  |  |

| TOCKI                            |               |          |             | ST            | Timer0 external clock input.                             |  |  |  |

| C1OUT                            |               |          | 0           |               | Comparator 1 output.                                     |  |  |  |

| RA5/AN4/SS/HLVDIN/               | 7             | 4        |             |               |                                                          |  |  |  |

| C2OUT                            |               |          | 1/0         |               |                                                          |  |  |  |

| RA5<br>AN4                       |               |          | I/O         |               | Digital I/O.<br>Analog Input 4.                          |  |  |  |

| AN4<br>SS                        |               |          |             | Analog<br>TTL | SPI slave select input.                                  |  |  |  |

| HLVDIN                           |               |          |             | Analog        |                                                          |  |  |  |

| C2OUT                            | 1             |          | Ö           |               | Comparator 2 output.                                     |  |  |  |

| RA6                              |               |          | -           |               | See the OSC2/CLKO/RA6 pin.                               |  |  |  |

| RA7                              |               |          |             |               | See the OSC1/CLKI/RA7 pin.                               |  |  |  |

|                                  |               | ام<br>ام | <u> </u>    |               |                                                          |  |  |  |

| Legend: TTL = TTL c<br>ST = Schm |               |          |             |               | CMOS = CMOS compatible input or output<br>vels I = Input |  |  |  |

| O = Outpu                        |               |          | with C      | INICS IE      | P = Power                                                |  |  |  |

|                                  |               |          |             |               |                                                          |  |  |  |

| TABLE 1-2: | PIC18F2423/2523 PINOUT I/O DESCRIPTIONS |  |

|------------|-----------------------------------------|--|

|            |                                         |  |

$$O = Output$$

$$I^2C = I^2C^{\text{TM}}/\text{SMBus}$$

Note 1: Default assignment for CCP2 when Configuration bit, CCP2MX, is set.

|                                                       | Pin Number                    |               | Pin Buffe          |                              |                                                                                                                                                                          |  |  |  |  |

|-------------------------------------------------------|-------------------------------|---------------|--------------------|------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|

| Pin Name                                              | PDIP,<br>SOIC                 | QFN           | Туре               | Buffer<br>Type               | Description                                                                                                                                                              |  |  |  |  |

|                                                       |                               |               |                    |                              | PORTC is a bidirectional I/O port.                                                                                                                                       |  |  |  |  |

| RC0/T1OSO/T13CKI<br>RC0<br>T1OSO<br>T13CKI            | 11                            | 8             | I/O<br>O<br>I      | ST<br>—<br>ST                | Digital I/O.<br>Timer1 oscillator output.<br>Timer1/Timer3 external clock input.                                                                                         |  |  |  |  |

| RC1/T1OSI/CCP2<br>RC1<br>T1OSI<br>CCP2 <sup>(2)</sup> | 12                            | 9             | I/O<br>I<br>I/O    | ST<br>Analog<br>ST           | Digital I/O.<br>Timer1 oscillator input.<br>Capture 2 input/Compare 2 output/PWM2 output.                                                                                |  |  |  |  |

| RC2/CCP1<br>RC2<br>CCP1                               | 13                            | 10            | I/O<br>I/O         | ST<br>ST                     | Digital I/O.<br>Capture 1 input/Compare 1 output/PWM1 output.                                                                                                            |  |  |  |  |

| RC3/SCK/SCL<br>RC3<br>SCK<br>SCL                      | 14                            | 11            | I/O<br>I/O<br>I/O  | ST<br>ST<br>I <sup>2</sup> C | Digital I/O.<br>Synchronous serial clock input/output for SPI mode.<br>Synchronous serial clock input/output for I <sup>2</sup> C™ mode.                                 |  |  |  |  |

| RC4/SDI/SDA<br>RC4<br>SDI<br>SDA                      | 15                            | 12            | I/O<br>I<br>I/O    | ST<br>ST<br>I <sup>2</sup> C | Digital I/O.<br>SPI data in.<br>I <sup>2</sup> C data I/O.                                                                                                               |  |  |  |  |

| RC5/SDO<br>RC5<br>SDO                                 | 16                            | 13            | I/O<br>O           | ST<br>—                      | Digital I/O.<br>SPI data out.                                                                                                                                            |  |  |  |  |

| RC6/TX/CK<br>RC6<br>TX<br>CK                          | 17                            | 14            | I/O<br>O<br>I/O    | ST<br>—<br>ST                | Digital I/O.<br>EUSART asynchronous transmit.<br>EUSART synchronous clock (see related RX/DT).                                                                           |  |  |  |  |

| RC7/RX/DT<br>RC7<br>RX<br>DT                          | 18                            | 15            | I/O<br>I<br>I/O    | ST<br>ST<br>ST               | Digital I/O.<br>EUSART asynchronous receive.<br>EUSART synchronous data (see related TX/CK).                                                                             |  |  |  |  |

| RE3                                                   |                               | _             |                    | _                            | See MCLR/VPP/RE3 pin.                                                                                                                                                    |  |  |  |  |

| Vss                                                   | 8, 19 క                       | 5, 16         | Р                  | _                            | Ground reference for logic and I/O pins.                                                                                                                                 |  |  |  |  |

| VDD                                                   | 20                            | 17            | Р                  |                              | Positive supply for logic and I/O pins.                                                                                                                                  |  |  |  |  |

| DT<br>RE3<br>Vss                                      | 20<br>ompatible<br>tt Trigger | 17<br>e input | I/O<br>—<br>P<br>P | ST<br>—<br>—                 | EUSART synchronous data (see re<br>See MCLR/VPP/RE3 pin.<br>Ground reference for logic and I/O pins<br>Positive supply for logic and I/O pins.<br>CMOS = CMOS compatible |  |  |  |  |

Р

= Power

| <b>TABLE 1-2</b> : | PIC18F2423/2523 PINOUT I/O DESCRIPTIONS (CONTINUED) |

|--------------------|-----------------------------------------------------|

|--------------------|-----------------------------------------------------|

O = Output  $I^2C$  =  $I^2C^{TM}/SMBus$ Note 1: Default assignment for CCP2 when Configuration bit, CCP2MX, is set.

| Pin Name              | Pi                                      | n Numb   | per  | Pin   | Buffer | Description                                                                                                                                      |  |  |

|-----------------------|-----------------------------------------|----------|------|-------|--------|--------------------------------------------------------------------------------------------------------------------------------------------------|--|--|

| Pin Name              | PDIP                                    | QFN      | TQFP | Туре  | Туре   | Description                                                                                                                                      |  |  |

| MCLR/VPP/RE3<br>MCLR  | 1                                       | 18       | 18   | I     | ST     | Master Clear (input) or programming voltage (input).<br>Master Clear (Reset) input. This pin is an active-low<br>Reset to the device.            |  |  |

| VPP                   |                                         |          |      | Р     |        | Programming voltage input.                                                                                                                       |  |  |

| RE3                   |                                         |          |      |       | ST     | Digital input.                                                                                                                                   |  |  |

| OSC1/CLKI/RA7<br>OSC1 | 13                                      | 32       | 30   | I     | ST     | Oscillator crystal or external clock input.<br>Oscillator crystal input or external clock source input.<br>ST buffer when configured in RC mode; |  |  |

| CLKI                  |                                         |          |      | I     | CMOS   | analog otherwise.<br>External clock source input. Always associated with<br>pin function, OSC1. (See related OSC1/CLKI,<br>OSC2/CLKO pins.)      |  |  |

| RA7                   |                                         |          |      | I/O   | TTL    | General purpose I/O pin.                                                                                                                         |  |  |

| OSC2/CLKO/RA6<br>OSC2 | 14                                      | 33       | 31   | 0     | _      | Oscillator crystal or clock output.<br>Oscillator crystal output. Connects to crystal<br>or resonator in Crystal Oscillator mode.                |  |  |

| CLKO                  |                                         |          |      | 0     | _      | In RC mode, OSC2 pin outputs CLKO, which<br>has 1/4 the frequency of OSC1 and denotes<br>the instruction cycle rate.                             |  |  |

| RA6                   |                                         |          |      | I/O   | TTL    | General purpose I/O pin.                                                                                                                         |  |  |

| ST = Sch<br>O = Ou    | _ compat<br>nmitt Trig<br>put<br>™/SMΒι | ger inpi |      | CMOSI | evels  | CMOS = CMOS compatible input or output<br>I = Input<br>P = Power                                                                                 |  |  |

# TABLE 1-3: PIC18F4423/4523 PINOUT I/O DESCRIPTIONS

Note 1: Default assignment for CCP2 when Configuration bit, CCP2MX, is set.

| Pin Name                                          | Pi                         | n Numb          | ber       | Pin             | Buffer                    | Description                                                                                                       |  |  |

|---------------------------------------------------|----------------------------|-----------------|-----------|-----------------|---------------------------|-------------------------------------------------------------------------------------------------------------------|--|--|

| Pin Name                                          | PDIP                       | QFN             | TQFP      | Туре            | Туре                      | Description                                                                                                       |  |  |

|                                                   |                            |                 |           |                 |                           | PORTB is a bidirectional I/O port. PORTB can be<br>software programmed for internal weak pull-ups on a<br>inputs. |  |  |

| RB0/INT0/FLT0/AN12<br>RB0<br>INT0<br>FLT0<br>AN12 | 33                         | 9               | 8         | I/O<br>I<br>I   | TTL<br>ST<br>ST<br>Analog | Digital I/O.<br>External Interrupt 0.<br>PWM Fault input for Enhanced CCP1.<br>Analog Input 12.                   |  |  |

| RB1/INT1/AN10<br>RB1<br>INT1<br>AN10              | 34                         | 10              | 9         | I/O<br>I<br>I   | TTL<br>ST<br>Analog       | Digital I/O.<br>External Interrupt 1.<br>Analog Input 10.                                                         |  |  |

| RB2/INT2/AN8<br>RB2<br>INT2<br>AN8                | 35                         | 11              | 10        | I/O<br>I<br>I   | TTL<br>ST<br>Analog       | Digital I/O.<br>External Interrupt 2.<br>Analog Input 8.                                                          |  |  |

| RB3/AN9/CCP2<br>RB3<br>AN9<br>CCP2 <sup>(1)</sup> | 36                         | 12              | 11        | I/O<br>I<br>I/O | TTL<br>Analog<br>ST       | Digital I/O.<br>Analog Input 9.<br>Capture 2 input/Compare 2 output/PWM2 output.                                  |  |  |

| RB4/KBI0/AN11<br>RB4<br>KBI0<br>AN11              | 37                         | 14              | 14        | I/O<br>I<br>I   | TTL<br>TTL<br>Analog      | Digital I/O.<br>Interrupt-on-change pin.<br>Analog Input 11.                                                      |  |  |

| RB5/KBI1/PGM<br>RB5<br>KBI1<br>PGM                | 38                         | 15              | 15        | I/O<br>I<br>I/O | TTL<br>TTL<br>ST          | Digital I/O.<br>Interrupt-on-change pin.<br>Low-Voltage ICSP™ Programming enable pin.                             |  |  |

| RB6/KBI2/PGC<br>RB6<br>KBI2<br>PGC                | 39                         | 16              | 16        | I/O<br>I<br>I/O | TTL<br>TTL<br>ST          | Digital I/O.<br>Interrupt-on-change pin.<br>In-Circuit Debugger and ICSP programming<br>clock pin.                |  |  |

| RB7/KBI3/PGD<br>RB7<br>KBI3<br>PGD                | 40                         | 17              | 17        | I/O<br>I<br>I/O | TTL<br>TTL<br>ST          | Digital I/O.<br>Interrupt-on-change pin.<br>In-Circuit Debugger and ICSP programming<br>data pin.                 |  |  |

| O = Out                                           | mitt Trig<br>put<br>™/SMBเ | iger inpi<br>is | ut with C |                 |                           | CMOS = CMOS compatible input or output<br>I = Input<br>P = Power<br>it CCD2MX is set                              |  |  |

# TABLE 1-3: PIC18F4423/4523 PINOUT I/O DESCRIPTIONS (CONTINUED)

**Note 1:** Default assignment for CCP2 when Configuration bit, CCP2MX, is set.

| Din Nama            | Pin Number              |         |           | Pin         | Buffer           | Description                                                                 |  |  |

|---------------------|-------------------------|---------|-----------|-------------|------------------|-----------------------------------------------------------------------------|--|--|

| Pin Name            | PDIP QFN TQFP Type Type |         | Туре      | Description |                  |                                                                             |  |  |

|                     |                         |         |           |             |                  | PORTC is a bidirectional I/O port.                                          |  |  |

| RC0/T1OSO/T13CKI    | 15                      | 34      | 32        |             |                  |                                                                             |  |  |

| RC0                 |                         |         |           | I/O         | ST               | Digital I/O.                                                                |  |  |

| T1OSO               |                         |         |           | 0           | —                | Timer1 oscillator output.                                                   |  |  |

| T13CKI              |                         |         |           | Ι           | ST               | Timer1/Timer3 external clock input.                                         |  |  |

| RC1/T1OSI/CCP2      | 16                      | 35      | 35        |             |                  |                                                                             |  |  |

| RC1                 |                         |         |           | I/O         | ST               | Digital I/O.                                                                |  |  |

| T1OSI               |                         |         |           | I           | CMOS             | Timer1 oscillator input.                                                    |  |  |

| CCP2 <sup>(2)</sup> |                         |         |           | I/O         | ST               | Capture 2 input/Compare 2 output/PWM2 output.                               |  |  |

| RC2/CCP1/P1A        | 17                      | 36      | 36        |             |                  |                                                                             |  |  |

| RC2                 |                         |         |           | I/O         | ST               | Digital I/O.                                                                |  |  |

| CCP1                |                         |         |           | I/O         | ST               | Capture 1 input/Compare 1 output/PWM1 output.                               |  |  |

| P1A                 |                         |         |           | 0           |                  | Enhanced CCP1 output.                                                       |  |  |

| RC3/SCK/SCL         | 18                      | 37      | 37        |             |                  |                                                                             |  |  |

| RC3                 |                         |         |           | I/O         | ST               | Digital I/O.                                                                |  |  |

| SCK                 |                         |         |           | I/O         | ST               | Synchronous serial clock input/output for<br>SPI mode.                      |  |  |

| SCL                 |                         |         |           | I/O         | l <sup>2</sup> C | Synchronous serial clock input/output for I <sup>2</sup> C <sup>™</sup> mod |  |  |

|                     | 22                      | 42      | 42        | 1/0         | 10               |                                                                             |  |  |

| RC4/SDI/SDA<br>RC4  | 23                      | 42      | 42        | I/O         | ST               | Digital I/O.                                                                |  |  |

| SDI                 |                         |         |           | 10          | ST               | SPI data in.                                                                |  |  |

| SDA                 |                         |         |           | I/O         | I <sup>2</sup> C | $I^2C$ data I/O.                                                            |  |  |

| RC5/SDO             | 24                      | 43      | 43        |             |                  |                                                                             |  |  |

| RC5                 | 27                      | 40      |           | I/O         | ST               | Digital I/O.                                                                |  |  |

| SDO                 |                         |         |           | 0           | _                | SPI data out.                                                               |  |  |

| RC6/TX/CK           | 25                      | 44      | 44        |             |                  |                                                                             |  |  |

| RC6                 | 20                      |         |           | I/O         | ST               | Digital I/O.                                                                |  |  |

| ТХ                  |                         |         |           | 0           |                  | EUSART asynchronous transmit.                                               |  |  |

| CK                  |                         |         |           | I/O         | ST               | EUSART synchronous clock (see related RX/DT).                               |  |  |

| RC7/RX/DT           | 26                      | 1       | 1         |             |                  |                                                                             |  |  |

| RC7                 |                         |         |           | I/O         | ST               | Digital I/O.                                                                |  |  |

| RX                  |                         |         |           | I           | ST               | EUSART asynchronous receive.                                                |  |  |

| DT                  |                         |         |           | I/O         | ST               | EUSART synchronous data (see related TX/CK).                                |  |  |

| Legend: TTL = TTL   |                         |         |           |             |                  | CMOS = CMOS compatible input or output                                      |  |  |

|                     | mitt Trig               | ger inp | ut with C | CMOSI       | evels            | I = Input                                                                   |  |  |

| O = Out             |                         |         |           |             |                  | P = Power                                                                   |  |  |

| $I^2C = I^2C$       | ™/SMBเ                  | IS      |           |             |                  |                                                                             |  |  |

#### **TABLE 1-3**: PIC18F4423/4523 PINOUT I/O DESCRIPTIONS (CONTINUED)

Note 1: Default assignment for CCP2 when Configuration bit, CCP2MX, is set.

# PIC18F2423/2523/4423/4523

| R/W-0         | U-0                                | R/W-0            | R/W-0         | R/W-0                     | R/W-0           | R/W-0           | R/W-0 |

|---------------|------------------------------------|------------------|---------------|---------------------------|-----------------|-----------------|-------|

| ADFM          |                                    | ACQT2            | ACQT1         | ACQT0                     | ADCS2           | ADCS1           | ADCS0 |

| bit 7         |                                    |                  |               |                           |                 |                 | bit ( |

| Legend:       |                                    |                  |               |                           |                 |                 |       |

| R = Readabl   | e bit                              | W = Writable     | bit           | U = Unimplen              | nented bit, rea | d as '0'        |       |

| -n = Value at | POR                                | '1' = Bit is set |               | '0' = Bit is cle          |                 | x = Bit is unki | nown  |

| bit 7         | ADFM: A/D F                        | Result Format S  | Select bit    |                           |                 |                 |       |

|               | 1 = Right just<br>0 = Left justifi |                  |               |                           |                 |                 |       |

| bit 6         | •                                  | ted: Read as '   | 0'            |                           |                 |                 |       |

| bit 5-3       | ACQT<2:0>:                         | A/D Acquisitio   | n Time Select | t bits                    |                 |                 |       |

|               | 111 <b>= 20 T</b> AD               | )                |               |                           |                 |                 |       |

|               | 110 <b>= 16 Tad</b>                | )                |               |                           |                 |                 |       |

|               | 101 = <b>12 TAD</b>                | )                |               |                           |                 |                 |       |

|               | 100 <b>= 8 T</b> AD                |                  |               |                           |                 |                 |       |

|               | 011 = 6 TAD<br>010 = 4 TAD         |                  |               |                           |                 |                 |       |

|               | 010 = 4 TAD<br>001 = 2 TAD         |                  |               |                           |                 |                 |       |

|               | 000 = 0 TAD <sup>(*</sup>          | 1)               |               |                           |                 |                 |       |

| bit 2-0       | ADCS<2:0>:                         | A/D Conversio    | n Clock Sele  | ct bits                   |                 |                 |       |

|               | 111 = FRC (c                       | lock derived fro | om A/D RC os  | scillator) <sup>(1)</sup> |                 |                 |       |

|               | 110 = Fosc/6                       |                  |               | ,                         |                 |                 |       |

|               | 101 = Fosc/*                       | 16               |               |                           |                 |                 |       |

|               | 100 = Fosc/4                       |                  |               | (4)                       |                 |                 |       |

|               |                                    | lock derived fro | om A/D RC os  | scillator) <sup>(1)</sup> |                 |                 |       |

|               | 010 = Fosc/3                       |                  |               |                           |                 |                 |       |

|               | 001 = Fosc/8<br>000 = Fosc/2       | 5                |               |                           |                 |                 |       |

#### REGISTER 2-3: ADCON2: A/D CONTROL REGISTER 2

**Note 1:** If the A/D FRC clock source is selected, a delay of one TcY (instruction cycle) is added before the A/D clock starts. This allows the SLEEP instruction to be executed before starting a conversion.

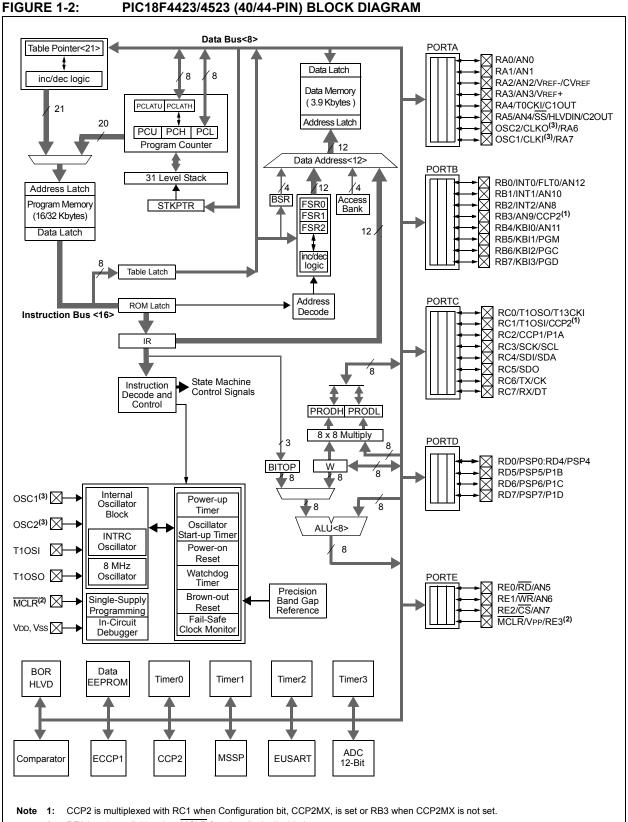

The analog reference voltage is software selectable to either the device's positive and negative supply voltage (VDD and Vss), or the voltage level on the RA3/AN3/ VREF+ and RA2/AN2/VREF-/CVREF pins.

The A/D Converter has a unique feature of being able to operate while the device is in Sleep mode. To operate in Sleep, the A/D conversion clock must be derived from the A/D's internal RC oscillator.

The output of the sample and hold is the input into the converter, which generates the result via successive approximation.

A device Reset forces all registers to their Reset state. This forces the A/D module to be turned off and any conversion in progress is aborted.

Each port pin associated with the A/D Converter can be configured as an analog input or as a digital I/O. The ADRESH and ADRESL registers contain the result of the A/D conversion. When the A/D conversion is complete, the result is <u>loaded</u> into the ADRESH:ADRESL register pair, the GO/DONE bit (ADCON0<1>) is cleared and A/D Interrupt Flag bit, ADIF, is set.

The block diagram of the A/D module is shown in Figure 2-1.

# FIGURE 2-1: A/D BLOCK DIAGRAM

# 2.2 Selecting and Configuring Acquisition Time

The ADCON2 register allows the user to select an acquisition time that occurs each time the GO/DONE bit is set. It also gives users the option of having an automatically determined acquisition time.

Acquisition time may be set with the ACQT<2:0> bits (ADCON2<5:3>), which provide a range of 2 to 20 TAD. When the GO/DONE bit is set, the A/D module continues to sample the input for the selected acquisition time, then automatically begins a conversion. Since the acquisition time is programmed, there may be no need to wait for an acquisition time between selecting a channel and setting the GO/DONE bit.

Manual acquisition time is <u>selected</u> when ACQT<2:0> = 0.00. When the GO/DONE bit is set, sampling is stopped and a conversion begins. The user is responsible for ensuring the required acquisition time has passed between selecting the desired input channel and setting the GO/DONE bit. This option is also the default Reset state of the ACQT<2:0> bits and is compatible with devices that do not offer programmable acquisition times.

In either case, when the conversion is completed, the GO/DONE bit is cleared, the ADIF flag is set and the A/D begins sampling the currently selected channel again. If an acquisition time is programmed, there is nothing to indicate if the acquisition time has ended or if the conversion has begun.

# 2.3 Selecting the A/D Conversion Clock

The A/D conversion time per bit is defined as TAD. The A/D conversion requires 13 TAD per 12-bit conversion. The source of the A/D conversion clock is software selectable.

There are seven possible options for TAD:

- 2 Tosc

- 32 Tosc

64 Tosc

- 4 Tosc

- Internal RC Oscillator

- 8 Tosc 16 Tosc

- )SC

For correct A/D conversions, the A/D conversion clock (TAD) must be as short as possible, but greater than the minimum TAD. (For more information, see parameter 130 on page 41.)

Table 2-2 shows the resultant TAD times derived from the device operating frequencies and the A/D clock source selected.

| A/D Clock So      | Assumes TAD Min. = 0.8 $\mu s$ |                         |

|-------------------|--------------------------------|-------------------------|

| Operation         | Operation ADCS<2:0>            |                         |

| 2 Tosc            | 000                            | 2.50 MHz                |

| 4 Tosc            | 100                            | 5.00 MHz                |

| 8 Tosc            | 001                            | 10.00 MHz               |

| 16 Tosc           | 101                            | 20.00 MHz               |

| 32 Tosc           | 010                            | 40.00 MHz               |

| 64 Tosc           | 110                            | 40.00 MHz               |

| RC <sup>(2)</sup> | x11                            | 1.00 MHz <sup>(1)</sup> |

# TABLE 2-2:TAD vs. DEVICE OPERATING FREQUENCIES

Note 1: The RC source has a typical TAD time of 2.5  $\mu$ s.

2: For device frequencies above 1 MHz, the device must be in Sleep for the entire conversion or a Fosc divider should be used instead; otherwise, the A/D accuracy specification may not be met.

# 2.8 Use of the CCP2 Trigger

An A/D conversion can be started by the Special Event Trigger of the CCP2 module. This requires that the CCP2M<3:0> bits (CCP2CON<3:0>) be programmed as '1011' and that the A/D module is enabled (ADON bit is set). When the trigger occurs, the GO/DONE bit will be set, starting the A/D acquisition and conversion, and the Timer1 (or Timer3) counter will be reset to zero. Timer1 (or Timer3) is reset to automatically repeat the A/D acquisition period with minimal software overhead (moving ADRESH:ADRESL to the desired location). The appropriate analog input channel must be selected and the minimum acquisition period is either timed by the user or an appropriate TACQ time is selected before the Special Event Trigger sets the GO/DONE bit (starts a conversion).

If the A/D module is not enabled (ADON is cleared), the Special Event Trigger will be ignored by the A/D module, but will still reset the Timer1 (or Timer3) counter.

| Name                 | Bit 7                 | Bit 6                         | Bit 5       | Bit 4         | Bit 3              | Bit 2   | Bit 1        | Bit 0   | Reset<br>Values on<br>page |  |  |

|----------------------|-----------------------|-------------------------------|-------------|---------------|--------------------|---------|--------------|---------|----------------------------|--|--|

| INTCON               | GIE/GIEH              | PEIE/GIEL                     | TMR0IE      | INT0IE        | RBIE               | TMR0IF  | INT0IF       | RBIF    | (Note 4)                   |  |  |

| PIR1                 | PSPIF <sup>(1)</sup>  | ADIF                          | RCIF        | TXIF          | SSPIF              | CCP1IF  | TMR2IF       | TMR1IF  | (Note 4)                   |  |  |

| PIE1                 | PSPIE <sup>(1)</sup>  | ADIE                          | RCIE        | TXIE          | SSPIE              | CCP1IE  | TMR2IE       | TMR1IE  | (Note 4)                   |  |  |

| IPR1                 | PSPIP <sup>(1)</sup>  | ADIP                          | RCIP        | TXIP          | SSPIP              | CCP1IP  | TMR2IP       | TMR1IP  | (Note 4)                   |  |  |

| PIR2                 | OSCFIF                | CMIF                          | _           | EEIF          | BCLIF              | HLVDIF  | TMR3IF       | CCP2IF  | (Note 4)                   |  |  |

| PIE2                 | OSCFIE                | CMIE                          | _           | EEIE          | BCLIE              | HLVDIE  | TMR3IE       | CCP2IE  | (Note 4)                   |  |  |

| IPR2                 | OSCFIP                | CMIP                          | _           | EEIP          | BCLIP              | HLVDIP  | TMR3IP       | CCP2IP  | (Note 4)                   |  |  |

| ADRESH               | A/D Result            | A/D Result Register High Byte |             |               |                    |         |              |         |                            |  |  |

| ADRESL               | A/D Result            | Register Lov                  | w Byte      |               |                    |         |              |         | (Note 4)                   |  |  |

| ADCON0               | —                     | —                             | CHS3        | CHS2          | CHS1               | CHS0    | GO/DONE      | ADON    | (Note 4)                   |  |  |

| ADCON1               | _                     | _                             | VCFG1       | VCFG0         | PCFG3              | PCFG2   | PCFG1        | PCFG0   | (Note 4)                   |  |  |

| ADCON2               | ADFM                  | —                             | ACQT2       | ACQT1         | ACQT0              | ADCS2   | ADCS1        | ADCS0   | (Note 4)                   |  |  |

| PORTA                | RA7 <sup>(2)</sup>    | RA6 <sup>(2)</sup>            | RA5         | RA4           | RA3                | RA2     | RA1          | RA0     | (Note 4)                   |  |  |

| TRISA                | TRISA7 <sup>(2)</sup> | TRISA6 <sup>(2)</sup>         | PORTA Da    | ata Direction | Control Re         | gister  |              |         | (Note 4)                   |  |  |

| PORTB                | RB7                   | RB6                           | RB5         | RB4           | RB3                | RB2     | RB1          | RB0     | (Note 4)                   |  |  |

| TRISB                | PORTB Dat             | a Direction (                 | Control Reg | ister         |                    |         |              |         | (Note 4)                   |  |  |

| LATB                 | PORTB Dat             | a Latch Reg                   | ister (Read | and Write to  | Data Latc          | h)      |              |         | (Note 4)                   |  |  |

| PORTE <sup>(1)</sup> | —                     | —                             | _           | _             | RE3 <sup>(3)</sup> | RE2     | RE1          | RE0     | (Note 4)                   |  |  |

| TRISE <sup>(1)</sup> | IBF                   | OBF                           | IBOV        | PSPMODE       | —                  | TRISE2  | TRISE1       | TRISE0  | (Note 4)                   |  |  |

| LATE <sup>(1)</sup>  | _                     | _                             | _           | _             |                    | PORTE D | ata Latch Re | egister | (Note 4)                   |  |  |

TABLE 2-3:

REGISTERS ASSOCIATED WITH A/D OPERATION

Legend: — = unimplemented, read as '0'. Shaded cells are not used for A/D conversion.

Note 1: These registers and/or bits are not implemented on PIC18F2423/2523 devices and are read as '0'.

**2:** PORTA<7:6> and their direction bits are individually configured as port pins based on various primary oscillator modes. When disabled, these bits read as '0'.

3: RE3 port bit is available only as an input pin when the MCLRE Configuration bit is '0'.

4: For these Reset values, see Section 4.0 "Reset" of the "PIC18F2420/2520/4420/4520 Data Sheet" (DS39631).

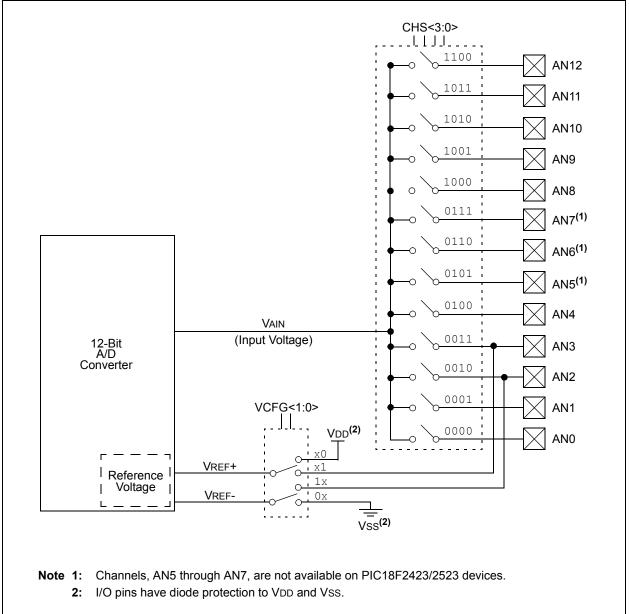

# 4.0 ELECTRICAL CHARACTERISTICS

**Note:** Other than some basic data, this section documents only the PIC18F2423/2523/4423/4523 devices' specifications that differ from those of the PIC18F2420/2520/4420/4520 devices. For detailed information on the electrical specifications shared by the PIC18F2423/2523/4423/4523 and PIC18F2420/2520/4420/4520 devices, see the *"PIC18F2420/2520/4420/4520 Data Sheet"* (DS39631).

# Absolute Maximum Ratings<sup>(†)</sup>

| Ambient temperature under bias                               | 40°C to +125°C       |

|--------------------------------------------------------------|----------------------|

| Storage temperature                                          | 65°C to +150°C       |

| Voltage on any pin with respect to Vss (except VDD and MCLR) | 0.3V to (VDD + 0.3V) |

| Voltage on VDD with respect to Vss                           | 0.3V to +7.5V        |

| Voltage on MCLR with respect to Vss (Note 2)                 | 0V to +13.25V        |

| Total power dissipation (Note 1)                             | 1.0W                 |

| Maximum current out of Vss pin                               |                      |

| Maximum current into VDD pin                                 | 250 mA               |

| Input clamp current, Iк (Vi < 0 or Vi > VDD)                 | ±20 mA               |

| Output clamp current, loк (Vo < 0 or Vo > VDD)               | ±20 mA               |

| Maximum output current sunk by any I/O pin                   | 25 mA                |

| Maximum output current sourced by any I/O pin                | 25 mA                |

| Maximum current sunk by all ports                            | 200 mA               |

| Maximum current sourced by all ports                         | 200 mA               |

- **Note 1:** Power dissipation is calculated as follows: Pdis = VDD x {IDD  $-\sum$  IOH} +  $\sum$  {(VDD - VOH) x IOH} +  $\sum$ (VOL x IOL)

- 2: Voltage spikes below Vss at the MCLR/VPP/RE3 pin, inducing currents greater than 80 mA, may cause latch-up. Thus, a series resistor of 50-100Ω should be used when applying a "low" level to the MCLR/VPP/ RE3 pin, rather than pulling this pin directly to Vss.

**† NOTICE:** Stresses above those listed under "Absolute Maximum Ratings" may cause permanent damage to the device. This is a stress rating only and functional operation of the device at those or any other conditions above those indicated in the operation listings of this specification is not implied. Exposure to maximum rating conditions for extended periods may affect device reliability.

# PIC18F2423/2523/4423/4523

NOTES:

# APPENDIX C: CONVERSION CONSIDERATIONS

This appendix discusses the considerations for converting from previous versions of a device to the ones listed in this data sheet. Typically, these changes are due to the differences in the process technology used. An example of this type of conversion is from a PIC16C74A to a PIC16C74B.

#### Not Applicable

# APPENDIX D: MIGRATION FROM BASELINE TO ENHANCED DEVICES

This section discusses how to migrate from a Baseline device (i.e., PIC16C5X) to an Enhanced MCU device (i.e., PIC18FXXX).

The following are the list of modifications over the PIC16C5X microcontroller family:

Not Currently Available

# APPENDIX E: MIGRATION FROM MID-RANGE TO ENHANCED DEVICES

A detailed discussion of the differences between the mid-range MCU devices (i.e., PIC16CXXX) and the enhanced devices (i.e., PIC18FXXX) is provided in *AN716, "Migrating Designs from PIC16C74A/74B to PIC18C442"*. The changes discussed, while device specific, are generally applicable to all mid-range to enhanced device migrations.

This Application Note is available as Literature Number DS00716.

# APPENDIX F: MIGRATION FROM HIGH-END TO ENHANCED DEVICES

A detailed discussion of the migration pathway and differences between the high-end MCU devices (i.e., PIC17CXXX) and the enhanced devices (i.e., PIC18FXXX) is provided in *AN726, "PIC17CXXX to PIC18CXXX Migration*". This Application Note is available as Literature Number DS00726.

# R

| Reader Response               | 52 |  |  |

|-------------------------------|----|--|--|

| Registers                     |    |  |  |

| ADCON0 (A/D Control 0)        | 25 |  |  |

| ADCON1 (A/D Control 1)        | 26 |  |  |

| ADCON2 (A/D Control 2)        | 27 |  |  |

| DEVID1 (Device ID 1)          | 35 |  |  |

| DEVID2                        |    |  |  |

| (Device ID 2)                 | 36 |  |  |

| Revision History              |    |  |  |

| S                             |    |  |  |

| Special Features of the CPU35 |    |  |  |

# Т

| Timing Diagrams<br>A/D Conversion       | 41 |

|-----------------------------------------|----|

| Timing Diagrams and Specifications      | 44 |

| A/D Conversion Requirements             | 41 |

| V                                       |    |

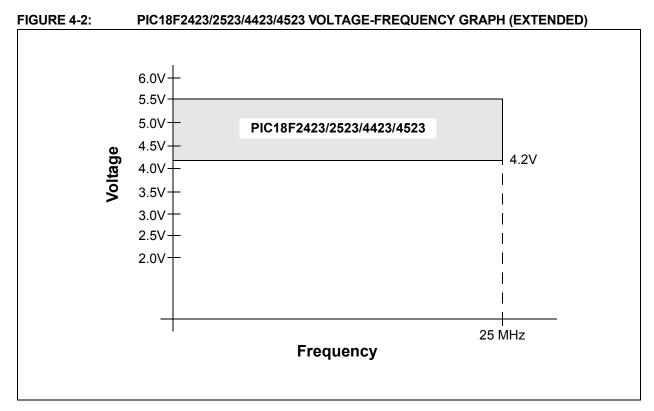

| Voltage-Frequency Graphics              |    |

| PIC18F2423/2523/4423/4523 (Extended)    | 38 |

| PIC18F2423/2523/4423/4523 (Industrial)  | 38 |

| PIC18LF2423/2523/4423/4523 (Industrial) | 39 |

|                                         |    |

# W

| WWW Address          | 51  |

|----------------------|-----|

| WWW, On-Line Support | . 8 |

# READER RESPONSE

It is our intention to provide you with the best documentation possible to ensure successful use of your Microchip product. If you wish to provide your comments on organization, clarity, subject matter, and ways in which our documentation can better serve you, please FAX your comments to the Technical Publications Manager at (480) 792-4150.

Please list the following information, and use this outline to provide us with your comments about this document.

| To:  | Technical Publications Manager                                                              | Total Pages Sent                                  |  |

|------|---------------------------------------------------------------------------------------------|---------------------------------------------------|--|

| RE:  | Reader Response                                                                             |                                                   |  |

| Fron | n: Name                                                                                     |                                                   |  |

|      | Company                                                                                     |                                                   |  |

|      | Address                                                                                     | <u>.</u>                                          |  |

|      | City / State / ZIP / Country                                                                |                                                   |  |

|      | Telephone: ()                                                                               | FAX: ()                                           |  |

| Appl | ication (optional):                                                                         |                                                   |  |

| Wou  | ld you like a reply?YN                                                                      |                                                   |  |

| Devi | ce: PIC18F2423/2523/4423/4523                                                               | Literature Number: DS39755C                       |  |

| Que  | stions:                                                                                     |                                                   |  |

| 1. \ | What are the best features of this doc                                                      | ument?                                            |  |

| -    |                                                                                             |                                                   |  |

| -    |                                                                                             |                                                   |  |

| 2. I | How does this document meet your h                                                          | ardware and software development needs?           |  |

| -    |                                                                                             |                                                   |  |

| -    |                                                                                             |                                                   |  |

| 3. I | 3. Do you find the organization of this document easy to follow? If not, why?               |                                                   |  |

| -    |                                                                                             |                                                   |  |

| -    | Meet additions to the desument days                                                         | withink would appear the structure and subject?   |  |

| 4. \ | what additions to the document do yo                                                        | ou think would enhance the structure and subject? |  |

| -    |                                                                                             |                                                   |  |

| 5. \ | 5. What deletions from the document could be made without affecting the overall usefulness? |                                                   |  |

| 0.   |                                                                                             |                                                   |  |

| -    |                                                                                             |                                                   |  |

| 6. I | Is there any incorrect or misleading information (what and where)?                          |                                                   |  |

|      |                                                                                             |                                                   |  |

| -    |                                                                                             |                                                   |  |

| 7. I | How would you improve this documer                                                          | nt?                                               |  |

| -    |                                                                                             |                                                   |  |

| _    |                                                                                             |                                                   |  |

|      |                                                                                             |                                                   |  |

# WORLDWIDE SALES AND SERVICE

#### AMERICAS

Corporate Office 2355 West Chandler Blvd. Chandler, AZ 85224-6199 Tel: 480-792-7200 Fax: 480-792-7277 Technical Support: http://support.microchip.com Web Address: www.microchip.com

Atlanta Duluth, GA Tel: 678-957-9614 Fax: 678-957-1455

Boston Westborough, MA Tel: 774-760-0087 Fax: 774-760-0088

Chicago Itasca, IL Tel: 630-285-0071 Fax: 630-285-0075

**Cleveland** Independence, OH Tel: 216-447-0464 Fax: 216-447-0643

**Dallas** Addison, TX Tel: 972-818-7423 Fax: 972-818-2924

Detroit Farmington Hills, MI Tel: 248-538-2250 Fax: 248-538-2260

Kokomo Kokomo, IN Tel: 765-864-8360 Fax: 765-864-8387

Los Angeles Mission Viejo, CA Tel: 949-462-9523 Fax: 949-462-9608

Santa Clara Santa Clara, CA Tel: 408-961-6444 Fax: 408-961-6445

Toronto Mississauga, Ontario, Canada Tel: 905-673-0699 Fax: 905-673-6509

#### ASIA/PACIFIC

Asia Pacific Office Suites 3707-14, 37th Floor Tower 6, The Gateway Harbour City, Kowloon Hong Kong Tel: 852-2401-1200 Fax: 852-2401-3431

Australia - Sydney Tel: 61-2-9868-6733 Fax: 61-2-9868-6755

**China - Beijing** Tel: 86-10-8528-2100 Fax: 86-10-8528-2104

**China - Chengdu** Tel: 86-28-8665-5511 Fax: 86-28-8665-7889

**China - Hong Kong SAR** Tel: 852-2401-1200 Fax: 852-2401-3431

China - Nanjing Tel: 86-25-8473-2460

Fax: 86-25-8473-2470 China - Qingdao

Tel: 86-532-8502-7355 Fax: 86-532-8502-7205

**China - Shanghai** Tel: 86-21-5407-5533 Fax: 86-21-5407-5066

China - Shenyang Tel: 86-24-2334-2829 Fax: 86-24-2334-2393

**China - Shenzhen** Tel: 86-755-8203-2660 Fax: 86-755-8203-1760

**China - Wuhan** Tel: 86-27-5980-5300 Fax: 86-27-5980-5118

**China - Xiamen** Tel: 86-592-2388138 Fax: 86-592-2388130

**China - Xian** Tel: 86-29-8833-7252 Fax: 86-29-8833-7256

**China - Zhuhai** Tel: 86-756-3210040 Fax: 86-756-3210049

# ASIA/PACIFIC

India - Bangalore Tel: 91-80-3090-4444 Fax: 91-80-3090-4080

India - New Delhi Tel: 91-11-4160-8631 Fax: 91-11-4160-8632

India - Pune Tel: 91-20-2566-1512 Fax: 91-20-2566-1513

**Japan - Yokohama** Tel: 81-45-471- 6166 Fax: 81-45-471-6122

**Korea - Daegu** Tel: 82-53-744-4301 Fax: 82-53-744-4302

Korea - Seoul Tel: 82-2-554-7200 Fax: 82-2-558-5932 or 82-2-558-5934

Malaysia - Kuala Lumpur Tel: 60-3-6201-9857 Fax: 60-3-6201-9859

**Malaysia - Penang** Tel: 60-4-227-8870 Fax: 60-4-227-4068

Philippines - Manila Tel: 63-2-634-9065 Fax: 63-2-634-9069

Singapore Tel: 65-6334-8870 Fax: 65-6334-8850

**Taiwan - Hsin Chu** Tel: 886-3-6578-300 Fax: 886-3-6578-370

**Taiwan - Kaohsiung** Tel: 886-7-536-4818 Fax: 886-7-536-4803

Taiwan - Taipei Tel: 886-2-2500-6610 Fax: 886-2-2508-0102

**Thailand - Bangkok** Tel: 66-2-694-1351 Fax: 66-2-694-1350

#### EUROPE

Austria - Wels Tel: 43-7242-2244-39 Fax: 43-7242-2244-393 Denmark - Copenhagen Tel: 45-4450-2828 Fax: 45-4485-2829

France - Paris Tel: 33-1-69-53-63-20 Fax: 33-1-69-30-90-79

**Germany - Munich** Tel: 49-89-627-144-0 Fax: 49-89-627-144-44

**Italy - Milan** Tel: 39-0331-742611 Fax: 39-0331-466781

Netherlands - Drunen Tel: 31-416-690399 Fax: 31-416-690340

**Spain - Madrid** Tel: 34-91-708-08-90 Fax: 34-91-708-08-91

**UK - Wokingham** Tel: 44-118-921-5869 Fax: 44-118-921-5820

03/26/09