#### Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Details                    |                                                                           |

|----------------------------|---------------------------------------------------------------------------|

| Product Status             | Active                                                                    |

| Core Processor             | PIC                                                                       |

| Core Size                  | 8-Bit                                                                     |

| Speed                      | 40MHz                                                                     |

| Connectivity               | CANbus, I <sup>2</sup> C, SPI, UART/USART                                 |

| Peripherals                | Brown-out Detect/Reset, HLVD, POR, PWM, WDT                               |

| Number of I/O              | 25                                                                        |

| Program Memory Size        | 80KB (40K x 16)                                                           |

| Program Memory Type        | FLASH                                                                     |

| EEPROM Size                | 1K x 8                                                                    |

| RAM Size                   | 3.25K x 8                                                                 |

| Voltage - Supply (Vcc/Vdd) | 4.2V ~ 5.5V                                                               |

| Data Converters            | A/D 8x10b                                                                 |

| Oscillator Type            | Internal                                                                  |

| Operating Temperature      | -40°C ~ 125°C (TA)                                                        |

| Mounting Type              | Through Hole                                                              |

| Package / Case             | 28-DIP (0.300", 7.62mm)                                                   |

| Supplier Device Package    | 28-SPDIP                                                                  |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/pic18f2682-e-sp |

|                            |                                                                           |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

#### **TABLE 1-2:** PIC18F2682/2685 PINOUT I/O DESCRIPTIONS

| Pin Name              | Pin<br>Number<br>PDIP,<br>SOIC | Pin<br>Type | Buffer<br>Type | Description                                                                                                       |

|-----------------------|--------------------------------|-------------|----------------|-------------------------------------------------------------------------------------------------------------------|

| MCLR/VPP/RE3          | 1                              |             | от             | Master Clear (input) or programming voltage (input).                                                              |

| MCLR                  |                                | I           | ST             | Master Clear (Reset) input. This pin is an active-low                                                             |

| Vpp                   |                                | Р           |                | Reset to the device.                                                                                              |

| RE3                   |                                |             | ST             | Programming voltage input.<br>Digital input.                                                                      |

| -                     | -                              | 1           | 51             | 5 1                                                                                                               |

| OSC1/CLKI/RA7         | 9                              |             | от             | Oscillator crystal or external clock input.                                                                       |

| OSC1                  |                                | I           | ST             | Oscillator crystal input or external clock source input.<br>ST buffer when configured in RC mode; CMOS otherwise. |

| CLKI                  |                                | I           | CMOS           | External clock source input. Always associated with pin                                                           |

|                       |                                |             |                | function OSC1. (See related OSC2/CLKO pin.)                                                                       |

| RA7                   |                                | I/O         | TTL            | General purpose I/O pin.                                                                                          |

| OSC2/CLKO/RA6         | 10                             |             |                | Oscillator crystal or clock output.                                                                               |

| OSC2                  |                                | 0           | _              | Oscillator crystal output. Connects to crystal or resonator in                                                    |

|                       |                                |             |                | Crystal Oscillator mode.                                                                                          |

| CLKO                  |                                | 0           | —              | In RC mode, OSC2 pin outputs CLKO which has 1/4 the                                                               |

|                       |                                |             |                | frequency of OSC1 and denotes the instruction cycle rate.                                                         |

| RA6                   |                                | I/O         | TTL            | General purpose I/O pin.                                                                                          |

| Legend: TTL = TTL con | npatible in                    | put         |                | CMOS = CMOS compatible input or output                                                                            |

ST = Schmitt Trigger input with CMOS levels

O = Output

ı. . ..... . . 4

Ρ = Power

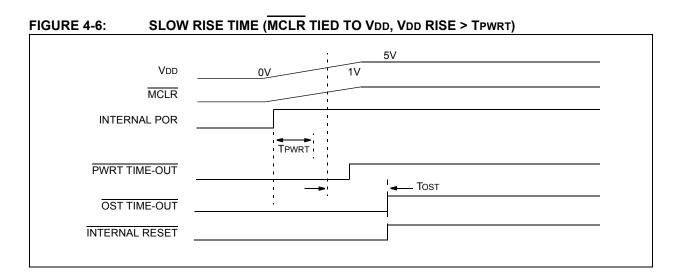

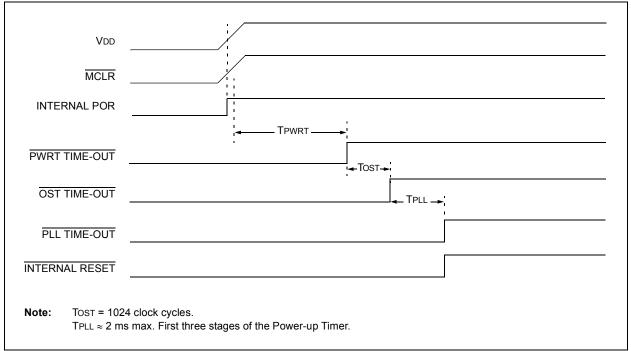

# FIGURE 4-7: TIME-OUT SEQUENCE ON POR w/PLL ENABLED (MCLR TIED TO VDD)

| File Name            | Bit 7              | Bit 6              | Bit 5               | Bit 4         | Bit 3                  | Bit 2                  | Bit 1                  | Bit 0                  | Value on<br>POR, BOR | Details<br>on page: |

|----------------------|--------------------|--------------------|---------------------|---------------|------------------------|------------------------|------------------------|------------------------|----------------------|---------------------|

| RXB1D5               | RXB1D57            | RXB1D56            | RXB1D55             | RXB1D54       | RXB1D53                | RXB1D52                | RXB1D51                | RXB1D50                | XXXX XXXX            | 55, 295             |

| RXB1D4               | RXB1D47            | RXB1D46            | RXB1D45             | RXB1D44       | RXB1D43                | RXB1D42                | RXB1D41                | RXB1D40                | XXXX XXXX            | 55, 295             |

| RXB1D3               | RXB1D37            | RXB1D36            | RXB1D35             | RXB1D34       | RXB1D33                | RXB1D32                | RXB1D31                | RXB1D30                | XXXX XXXX            | 55, 295             |

| RXB1D2               | RXB1D27            | RXB1D26            | RXB1D25             | RXB1D24       | RXB1D23                | RXB1D22                | RXB1D21                | RXB1D20                | XXXX XXXX            | 55, 295             |

| RXB1D1               | RXB1D17            | RXB1D16            | RXB1D15             | RXB1D14       | RXB1D13                | RXB1D12                | RXB1D11                | RXB1D10                | XXXX XXXX            | 55, 295             |

| RXB1D0               | RXB1D07            | RXB1D06            | RXB1D05             | RXB1D04       | RXB1D03                | RXB1D02                | RXB1D01                | RXB1D00                | XXXX XXXX            | 55, 295             |

| RXB1DLC              | _                  | RXRTR              | RB1                 | RB0           | DLC3                   | DLC2                   | DLC1                   | DLC0                   | -xxx xxxx            | 55, 295             |

| RXB1EIDL             | EID7               | EID6               | EID5                | EID4          | EID3                   | EID2                   | EID1                   | EID0                   | XXXX XXXX            | 55, 294             |

| RXB1EIDH             | EID15              | EID14              | EID13               | EID12         | EID11                  | EID10                  | EID9                   | EID8                   | XXXX XXXX            | 55, 294             |

| RXB1SIDL             | SID2               | SID1               | SID0                | SRR           | EXID                   |                        | EID17                  | EID16                  | XXXX XXXX            | 55, 294             |

| RXB1SIDH             | SID10              | SID9               | SID8                | SID7          | SID6                   | SID5                   | SID4                   | SID3                   | XXXX XXXX            | 56, 293             |

| RXB1CON<br>Mode 0    | RXFUL              | RXM1               | RXM0 <sup>(7)</sup> | (7)           | RXRTRRO <sup>(7)</sup> | FILHIT2 <sup>(7)</sup> | FILHIT1 <sup>(7)</sup> | FILHITO <sup>(7)</sup> | 000- 0000            | 56, 292             |

| RXB1CON<br>Mode 1, 2 | RXFUL              | RXM1               | RTRRO               | FILHIT4       | FILHIT3                | FILHIT2                | FILHIT1                | FILHIT0                | 0000 0000            | 56, 292             |

| TXB0D7               | TXB0D77            | TXB0D76            | TXB0D75             | TXB0D74       | TXB0D73                | TXB0D72                | TXB0D71                | TXB0D70                | XXXX XXXX            | 56, 286             |

| TXB0D6               | TXB0D67            | TXB0D66            | TXB0D65             | TXB0D64       | TXB0D63                | TXB0D62                | TXB0D61                | TXB0D60                | XXXX XXXX            | 56, 286             |

| TXB0D5               | TXB0D57            | TXB0D56            | TXB0D55             | TXB0D54       | TXB0D53                | TXB0D52                | TXB0D51                | TXB0D50                | XXXX XXXX            | 56, 286             |

| TXB0D4               | TXB0D47            | TXB0D46            | TXB0D45             | TXB0D44       | TXB0D43                | TXB0D42                | TXB0D41                | TXB0D40                | XXXX XXXX            | 56, 286             |

| TXB0D3               | TXB0D37            | TXB0D36            | TXB0D35             | TXB0D34       | TXB0D33                | TXB0D32                | TXB0D31                | TXB0D30                | XXXX XXXX            | 56, 286             |

| TXB0D2               | TXB0D27            | TXB0D26            | TXB0D25             | TXB0D24       | TXB0D23                | TXB0D22                | TXB0D21                | TXB0D20                | XXXX XXXX            | 56, 286             |

| TXB0D1               | TXB0D17            | TXB0D16            | TXB0D15             | TXB0D14       | TXB0D13                | TXB0D12                | TXB0D11                | TXB0D10                | XXXX XXXX            | 56, 286             |

| TXB0D0               | TXB0D07            | TXB0D06            | TXB0D05             | TXB0D04       | TXB0D03                | TXB0D02                | TXB0D01                | TXB0D00                | XXXX XXXX            | 56, 286             |

| TXB0DLC              |                    | TXRTR              |                     | -             | DLC3                   | DLC2                   | DLC1                   | DLC0                   | -x xxxx              | 56, 287             |

| TXB0EIDL             | EID7               | EID6               | EID5                | EID4          | EID3                   | EID2                   | EID1                   | EID0                   | XXXX XXXX            | 56, 286             |

| TXB0EIDH             | EID15              | EID14              | EID13               | EID12         | EID11                  | EID10                  | EID9                   | EID8                   | XXXX XXXX            | 56, 285             |

| TXB0SIDL             | SID2               | SID1               | SID0                | _             | EXIDE                  | _                      | EID17                  | EID16                  | xxx- x-xx            | 56, 285             |

| TXB0SIDH             | SID10              | SID9               | SID8                | SID7          | SID6                   | SID5                   | SID4                   | SID3                   | XXXX XXXX            | 56, 285             |

| TXB0CON              | TXBIF              | TXABT              | TXLARB              | TXERR         | TXREQ                  | _                      | TXPRI1                 | TXPRI0                 | 0000 0-00            | 56, 284             |

| TXB1D7               | TXB1D77            | TXB1D76            | TXB1D75             | TXB1D74       | TXB1D73                | TXB1D72                | TXB1D71                | TXB1D70                | XXXX XXXX            | 56, 286             |

| TXB1D6               | TXB1D67            | TXB1D66            | TXB1D65             | TXB1D64       | TXB1D63                | TXB1D62                | TXB1D61                | TXB1D60                | XXXX XXXX            | 56, 286             |

| TXB1D5               | TXB1D57            | TXB1D56            | TXB1D55             | TXB1D54       | TXB1D53                | TXB1D52                | TXB1D51                | TXB1D50                | XXXX XXXX            | 56, 286             |

| TXB1D4               | TXB1D47            | TXB1D46            | TXB1D45             | TXB1D44       | TXB1D43                | TXB1D42                | TXB1D41                | TXB1D40                | XXXX XXXX            | 56, 286             |

| TXB1D3               | TXB1D37            | TXB1D36            | TXB1D35             | TXB1D34       | TXB1D33                | TXB1D32                | TXB1D31                | TXB1D30                | XXXX XXXX            | 56, 286             |

| TXB1D2               | TXB1D07            | TXB1D26            | TXB1D25             | TXB1D24       | TXB1D23                | TXB1D02                | TXB1D01                | TXB1D00                | XXXX XXXX            | 56, 286             |

| TXB1D1               | TXB1D27<br>TXB1D17 | TXB1D20            | TXB1D25             | TXB1D24       | TXB1D23                | TXB1D22<br>TXB1D12     | TXB1D21                | TXB1D20                | XXXX XXXX            | 56, 286             |

| TXB1D0               | TXB1D17<br>TXB1D07 | TXB1D10<br>TXB1D06 | TXB1D15             | TXB1D14       | TXB1D13                | TXB1D12<br>TXB1D02     | TXB1D11<br>TXB1D01     | TXB1D10                | XXXX XXXX            | 56, 286             |

| TXB1DLC              | —                  | TXRTR              | —                   | -             | DLC3                   | DLC2                   | DLC1                   | DLC0                   | -x xxxx              | 56, 287             |

| TXB1EIDL             | EID7               | EID6               | EID5                | EID4          | EID3                   | EID2                   | EID1                   | EID0                   | XXXX XXXX            | 56, 286             |

| TXB1EIDE             | EID7<br>EID15      | EID14              | EID3                | EID4<br>EID12 | EID11                  | EID10                  | EID9                   | EID8                   |                      | 56, 285             |

| TXB1EIDH             | SID2               | SID14              | SID0                |               | EXIDE                  |                        | EID9<br>EID17          | EID8<br>EID16          | XXXX XXXX            | 56, 285             |

| INDIGIDE             | SIDZ               | 301                | 5100                |               |                        |                        |                        |                        | xxx- x-xx            | JU, 205             |

#### TABLE 5-2:REGISTER FILE SUMMARY (PIC18F2682/2685/4682/4685) (CONTINUED)

Legend: x = unknown, u = unchanged, - = unimplemented, q = value depends on condition. Shaded cells are unimplemented, read as '0'.

Note 1: Bit 21 of the PC is only available in Test mode and Serial Programming modes.

2: The SBOREN bit is only available when CONFIG2L<1:0> = 01; otherwise, it is disabled and reads as '0'. See Section 4.4 "Brown-out Reset (BOR)".

3: These registers and/or bits are not implemented on PIC18F2682/2685 devices and are read as '0'. Reset values are shown for PIC18F4682/4685 devices; individual unimplemented bits should be interpreted as '---'.

4: The PLLEN bit is only available in specific oscillator configurations; otherwise, it is disabled and reads as '0'. See Section 2.6.4 "PLL in INTOSC Modes".

5: The RE3 bit is only available when Master Clear Reset is disabled (CONFIG3H<7> = 0); otherwise, RE3 reads as '0'. This bit is read-only.

6: RA6/RA7 and their associated latch and direction bits are individually configured as port pins based on various primary oscillator modes. When disabled, these bits read as '0'.

7: CAN bits have multiple functions depending on the selected mode of the CAN module.

8: This register reads all '0's until the ECAN<sup>™</sup> technology is set up in Mode 1 or Mode 2.

9: These registers and/or bits are available on PIC18F4682/4685 devices only.

| TABLE 5-2                              |       | JSIERF | ILE SUM |         | 10185260 | 82/2685/46 | 82/4685) (( | JONTINUE       | .D)                  |                    |

|----------------------------------------|-------|--------|---------|---------|----------|------------|-------------|----------------|----------------------|--------------------|

| File Name                              | Bit 7 | Bit 6  | Bit 5   | Bit 4   | Bit 3    | Bit 2      | Bit 1       | Bit 0          | Value on<br>POR, BOR | Details<br>on page |

| RXF1SIDL                               | SID2  | SID1   | SID0    | _       | EXIDEN   | _          | EID17       | EID16          | xxx- x-xx            | 58, 305            |

| RXF1SIDH                               | SID10 | SID9   | SID8    | SID7    | SID6     | SID5       | SID4        | SID3           | XXXX XXXX            | 58, 306            |

| RXF0EIDL                               | EID7  | EID6   | EID5    | EID4    | EID3     | EID2       | EID1        | EID0           | XXXX XXXX            | 58, 306            |

| RXF0EIDH                               | EID15 | EID14  | EID13   | EID12   | EID11    | EID10      | EID9        | EID8           | XXXX XXXX            | 58, 306            |

| RXF0SIDL                               | SID2  | SID1   | SID0    | —       | EXIDEN   | —          | EID17       | EID16          | xxx- x-xx            | 58, 305            |

| RXF0SIDH                               | SID10 | SID9   | SID8    | SID7    | SID6     | SID5       | SID4        | SID3           | XXXX XXXX            | 58, 306            |

| B5D7 <sup>(8)</sup>                    | B5D77 | B5D76  | B5D75   | B5D74   | B5D73    | B5D72      | B5D71       | B5D70          | XXXX XXXX            | 58, 302            |

| B5D6 <sup>(8)</sup>                    | B5D67 | B5D66  | B5D65   | B5D64   | B5D63    | B5D62      | B5D61       | B5D60          | XXXX XXXX            | 58, 302            |

| B5D5 <sup>(8)</sup>                    | B5D57 | B5D56  | B5D55   | B5D54   | B5D53    | B5D52      | B5D51       | B5D50          | XXXX XXXX            | 58, 302            |

| B5D4 <sup>(8)</sup>                    | B5D47 | B5D46  | B5D45   | B5D44   | B5D43    | B5D42      | B5D41       | B5D40          | XXXX XXXX            | 58, 302            |

| B5D3 <sup>(8)</sup>                    | B5D37 | B5D36  | B5D35   | B5D34   | B5D33    | B5D32      | B5D31       | B5D30          | XXXX XXXX            | 58, 302            |

| B5D2 <sup>(8)</sup>                    | B5D27 | B5D26  | B5D25   | B5D24   | B5D23    | B5D22      | B5D21       | B5D20          | XXXX XXXX            | 58, 302            |

| B5D1 <sup>(8)</sup>                    | B5D17 | B5D16  | B5D15   | B5D14   | B5D13    | B5D12      | B5D11       | B5D10          | XXXX XXXX            | 58, 302            |

| B5D0 <sup>(8)</sup>                    | B5D07 | B5D06  | B5D05   | B5D04   | B5D03    | B5D02      | B5D01       | B5D00          | XXXX XXXX            | 58, 302            |

| B5DLC <sup>(8)</sup><br>Receive mode   |       | RXRTR  | RB1     | RB0     | DLC3     | DLC2       | DLC1        | DLC0           | -xxx xxxx            | 58, 303            |

| B5DLC <sup>(8)</sup><br>Transmit mode  |       | TXRTR  | —       | -       | DLC3     | DLC2       | DLC1        | DLC0           | -x xxxx              | 58, 304            |

| B5EIDL <sup>(8)</sup>                  | EID7  | EID6   | EID5    | EID4    | EID3     | EID2       | EID1        | EID0           | XXXX XXXX            | 58, 301            |

| B5EIDH <sup>(8)</sup>                  | EID15 | EID14  | EID13   | EID12   | EID11    | EID10      | EID9        | EID8           | XXXX XXXX            | 58, 301            |

| B5SIDL <sup>(8)</sup><br>Receive mode  | SID2  | SID1   | SID0    | SRR     | EXID     | —          | EID17       | EID16          | хххх х-хх            | 58, 300            |

| B5SIDL <sup>(8)</sup><br>Transmit mode | SID2  | SID1   | SID0    | —       | EXIDE    | _          | EID17       | EID16          | xxx- x-xx            | 58, 300            |

| B5SIDH <sup>(8)</sup>                  | SID10 | SID9   | SID8    | SID7    | SID6     | SID5       | SID4        | SID3           | xxxx x-xx            | 58, 299            |

| B5CON <sup>(8)</sup><br>Receive mode   | RXFUL | RXM1   | RXRTRRO | FILHIT4 | FILHIT3  | FILHIT2    | FILHIT1     | <b>FILHITO</b> | 0000 0000            | 58, 298            |

| B5CON <sup>(8)</sup><br>Transmit mode  | TXBIF | TXABT  | TXLARB  | TXERR   | TXREQ    | RTREN      | TXPRI1      | TXPRI0         | 0000 0000            | 58, 298            |

| B4D7 <sup>(8)</sup>                    | B4D77 | B4D76  | B4D75   | B4D74   | B4D73    | B4D72      | B4D71       | B4D70          | XXXX XXXX            | 58, 302            |

| B4D6 <sup>(8)</sup>                    | B4D67 | B4D66  | B4D65   | B4D64   | B4D63    | B4D62      | B4D61       | B4D60          | XXXX XXXX            | 58, 302            |

| B4D5 <sup>(8)</sup>                    | B4D57 | B4D56  | B4D55   | B4D54   | B4D53    | B4D52      | B4D51       | B4D50          | XXXX XXXX            | 58, 302            |

| B4D4 <sup>(8)</sup>                    | B4D47 | B4D46  | B4D45   | B4D44   | B4D43    | B4D42      | B4D41       | B4D40          | XXXX XXXX            | 59, 302            |

| B4D3 <sup>(8)</sup>                    | B4D37 | B4D36  | B4D35   | B4D34   | B4D33    | B4D32      | B4D31       | B4D30          | XXXX XXXX            | 59, 302            |

| B4D2 <sup>(8)</sup>                    | B4D27 | B4D26  | B4D25   | B4D24   | B4D23    | B4D22      | B4D21       | B4D20          | XXXX XXXX            | 59, 302            |

| B4D1 <sup>(8)</sup>                    | B4D17 | B4D16  | B4D15   | B4D14   | B4D13    | B4D12      | B4D11       | B4D10          | XXXX XXXX            | 59, 302            |

| B4D0 <sup>(8)</sup>                    | B4D07 | B4D06  | B4D05   | B4D04   | B4D03    | B4D02      | B4D01       | B4D00          | XXXX XXXX            | 58, 302            |

| B4DLC <sup>(8)</sup><br>Receive mode   |       | RXRTR  | RB1     | RB0     | DLC3     | DLC2       | DLC1        | DLC0           | -xxx xxxx            | 58, 303            |

| B4DLC <sup>(8)</sup><br>Transmit mode  | _     | TXRTR  | —       | —       | DLC3     | DLC2       | DLC1        | DLC0           | -x xxxx              | 58, 304            |

| B4EIDL <sup>(8)</sup>                  | EID7  | EID6   | EID5    | EID4    | EID3     | EID2       | EID1        | EID0           | XXXX XXXX            | 59, 301            |

| B4EIDH <sup>(8)</sup>                  | EID15 | EID14  | EID13   | EID12   | EID11    | EID10      | EID9        | EID8           | XXXX XXXX            | 59, 301            |

####

Legend: x = unknown, u = unchanged, - = unimplemented, q = value depends on condition. Shaded cells are unimplemented, read as '0'.

Note 1: Bit 21 of the PC is only available in Test mode and Serial Programming modes.

2: The SBOREN bit is only available when CONFIG2L<1:0> = 01; otherwise, it is disabled and reads as '0'. See Section 4.4 "Brown-out Reset (BOR)".

These registers and/or bits are not implemented on PIC18F2682/2685 devices and are read as '0'. Reset values are shown for PIC18F4682/4685 3: devices; individual unimplemented bits should be interpreted as '---'

The PLLEN bit is only available in specific oscillator configurations; otherwise, it is disabled and reads as '0'. See Section 2.6.4 "PLL in INTOSC 4: Modes"

The RE3 bit is only available when Master Clear Reset is disabled (CONFIG3H<7> = 0); otherwise, RE3 reads as '0'. This bit is read-only. 5:

6: RA6/RA7 and their associated latch and direction bits are individually configured as port pins based on various primary oscillator modes. When disabled, these bits read as '0'.

CAN bits have multiple functions depending on the selected mode of the CAN module. 7:

This register reads all '0's until the ECAN™ technology is set up in Mode 1 or Mode 2. 8:

9: These registers and/or bits are available on PIC18F4682/4685 devices only.

### 5.4 Data Addressing Modes

Note: The execution of some instructions in the core PIC18 instruction set are changed when the PIC18 extended instruction set is enabled. See Section 5.6 "Data Memory and the Extended Instruction Set" for more information.

While the program memory can be addressed in only one way – through the program counter – information in the data memory space can be addressed in several ways. For most instructions, the addressing mode is fixed. Other instructions may use up to three modes, depending on which operands are used and whether or not the extended instruction set is enabled.

The addressing modes are:

- Inherent

- Literal

- Direct

- Indirect

An additional addressing mode, Indexed Literal Offset, is available when the extended instruction set is enabled (XINST Configuration bit = 1). Its operation is discussed in greater detail in **Section 5.6.1 "Indexed Addressing with Literal Offset**".

# 5.4.1 INHERENT AND LITERAL ADDRESSING

Many PIC18 control instructions do not need any argument at all. They either perform an operation that globally affects the device or they operate implicitly on one register. This addressing mode is known as Inherent Addressing. Examples include SLEEP, RESET and DAW.

Other instructions work in a similar way but require an additional explicit argument in the opcode. This is known as Literal Addressing mode because they require some literal value as an argument. Examples include ADDLW and MOVLW which, respectively, add or move a literal value to the W register. Other examples include CALL and GOTO, which include a 20-bit program memory address.

#### 5.4.2 DIRECT ADDRESSING

Direct Addressing mode specifies all or part of the source and/or destination address of the operation within the opcode itself. The options are specified by the arguments accompanying the instruction.

In the core PIC18 instruction set, bit-oriented and byteoriented instructions use some version of Direct Addressing by default. All of these instructions include some 8-bit literal address as their Least Significant Byte. This address specifies either a register address in one of the banks of data RAM (Section 5.3.3 "General **Purpose Register File**") or a location in the Access Bank (Section 5.3.2 "Access Bank") as the data source for the instruction.

The Access RAM bit 'a' determines how the address is interpreted. When 'a' is '1', the contents of the BSR (Section 5.3.1 "Bank Select Register (BSR)") are used with the address to determine the complete 12-bit address of the register. When 'a' is '0', the address is interpreted as being a register in the Access Bank. Addressing that uses the Access RAM is sometimes also known as Direct Forced Addressing mode.

A few instructions, such as MOVFF, include the entire 12-bit address (either source or destination) in their opcodes. In those cases, the BSR is ignored entirely.

The destination of the operation's results is determined by the destination bit 'd'. When 'd' is '1', the results are stored back in the source register, overwriting its original contents. When 'd' is '0', the results are stored in the W register. Instructions without the 'd' argument have a destination that is implicit in the instruction. Their destination is either the target register being operated on or the W register.

# 5.4.3 INDIRECT ADDRESSING

Indirect Addressing allows the user to access a location in data memory without giving a fixed address in the instruction. This is done by using File Select Registers (FSRs) as pointers to the locations to be read or written to. Since the FSRs are themselves located in RAM as Special Function Registers, they can also be directly manipulated under program control. This makes FSRs very useful in implementing data structures, such as tables and arrays in data memory.

The registers for Indirect Addressing are also implemented with Indirect File Operands (INDFs) that permit automatic manipulation of the pointer value with auto-incrementing, auto-decrementing or offsetting with another value. This allows for efficient code, using loops, such as the example of clearing an entire RAM bank in Example 5-5.

## EXAMPLE 5-5: HOW TO CLEAR RAM (BANK 1) USING INDIRECT ADDRESSING

|         | LFSR  | FSR0,  | 100h | ; |                |

|---------|-------|--------|------|---|----------------|

| NEXT    | CLRF  | POSTIN | 20   | ; | Clear INDF     |

|         |       |        |      | ; | register then  |

|         |       |        |      | ; | inc pointer    |

|         | BTFSS | FSROH, | 1    | ; | All done with  |

|         |       |        |      | ; | Bank1?         |

|         | BRA   | NEXT   |      | ; | NO, clear next |

| CONTINU | JE    |        |      | ; | YES, continue  |

|         |       |        |      |   |                |

### REGISTER 6-1: EECON1: DATA EEPROM CONTROL REGISTER 1

| R/W-x | R/W-x | U-0 | R/W-0 | R/W-x                | R/W-0 | R/S-0 | R/S-0 |

|-------|-------|-----|-------|----------------------|-------|-------|-------|

| EEPGD | CFGS  | —   | FREE  | WRERR <sup>(1)</sup> | WREN  | WR    | RD    |

| bit 7 |       |     |       |                      |       |       | bit 0 |

| Legend:           | S = Settable bit |                       |                                    |  |  |  |

|-------------------|------------------|-----------------------|------------------------------------|--|--|--|

| R = Readable bit  | W = Writable bit | U = Unimplemented bit | U = Unimplemented bit, read as '0' |  |  |  |

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared  | x = Bit is unknown                 |  |  |  |

| bit 7   | EEPGD: Flash Program or Data EEPROM Memory Select bit                                                                                                                                                        |

|---------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|         | 1 = Access Flash program memory<br>0 = Access data EEPROM memory                                                                                                                                             |

|         | -                                                                                                                                                                                                            |

| bit 6   | CFGS: Flash Program/Data EEPROM or Configuration Select bit                                                                                                                                                  |

|         | 1 = Access Configuration registers                                                                                                                                                                           |

|         | 0 = Access Flash program or data EEPROM memory                                                                                                                                                               |

| bit 5   | Unimplemented: Read as '0'                                                                                                                                                                                   |

| bit 4   | FREE: Flash Row Erase Enable bit                                                                                                                                                                             |

|         | <ul> <li>1 = Erase the program memory row addressed by TBLPTR on the next WR command (cleared by<br/>completion of erase operation)</li> </ul>                                                               |

|         | 0 = Perform write-only                                                                                                                                                                                       |

| bit 3   | WRERR: Flash Program/Data EEPROM Error Flag bit <sup>(1)</sup>                                                                                                                                               |

|         | 1 = A write operation is prematurely terminated (any Reset during self-timed programming in normal                                                                                                           |

|         | operation or an improper write attempt)<br>0 = The write operation completed                                                                                                                                 |

| bit 2   |                                                                                                                                                                                                              |

| DIL Z   | WREN: Flash Program/Data EEPROM Write Enable bit                                                                                                                                                             |

|         | <ul> <li>1 = Allows write cycles to Flash program/data EEPROM</li> <li>0 = Inhibits write cycles to Flash program/data EEPROM</li> </ul>                                                                     |

| 1.11.4  |                                                                                                                                                                                                              |

| bit 1   | WR: Write Control bit                                                                                                                                                                                        |

|         | <ul> <li>1 = Initiates a data EEPROM erase/write cycle or a program memory erase cycle or write cycle<br/>(The operation is self-timed and the bit is cleared by hardware once write is complete.</li> </ul> |

|         | The WR bit can only be set (not cleared) in software.)<br>0 = Write cycle to the EEPROM is complete                                                                                                          |

| bit 0   | <b>RD:</b> Read Control bit                                                                                                                                                                                  |

| DIT U   | 1 = Initiates an EEPROM read (Read takes one cycle. RD is cleared in hardware. The RD bit can only                                                                                                           |

|         | be set (not cleared) in software. RD bit cannot be set when EEPGD = 1 or CFGS = 1.)                                                                                                                          |

|         | 0 = Does not initiate an EEPROM read                                                                                                                                                                         |

|         |                                                                                                                                                                                                              |

| Note 1: | When a WRERR occurs, the EEPGD and CFGS bits are not cleared. This allows tracing of the error                                                                                                               |

**Note 1:** When a WRERR occurs, the EEPGD and CFGS bits are not cleared. This allows tracing of the error condition.

# 7.3 Reading the Data EEPROM Memory

To read a data memory location, the user must write the address to the EEADRH:EEADR register pair, clear the EEPGD control bit (EECON1<7>) and then set control bit, RD (EECON1<0>). The data is available on the very next instruction cycle; therefore, the EEDATA register can be read by the next instruction. EEDATA will hold this value until another read operation, or until it is written to by the user (during a write operation).

The basic process is shown in Example 7-1.

# 7.4 Writing to the Data EEPROM Memory

To write an EEPROM data location, the address must first be written to the EEADRH:EEADR register pair and the data written to the EEDATA register. The sequence in Example 7-2 must be followed to initiate the write cycle.

The write will not begin if this sequence is not exactly followed (write 55h to EECON2, write 0AAh to EECON2, then set WR bit) for each byte. It is strongly recommended that interrupts be disabled during this code segment.

EXAMPLE 7-1: DATA EEPROM READ

Additionally, the WREN bit in EECON1 must be set to enable writes. This mechanism prevents accidental writes to data EEPROM due to unexpected code execution (i.e., runaway programs). The WREN bit should be kept clear at all times, except when updating the EEPROM. The WREN bit is not cleared by hardware.

After a write sequence has been initiated, EECON1, EEADRH:EEADR and EEDATA cannot be modified. The WR bit will be inhibited from being set unless the WREN bit is set. The WREN bit must be set on a previous instruction. Both WR and WREN cannot be set with the same instruction.

At the completion of the write cycle, the WR bit is cleared in hardware and the EEPROM Interrupt Flag bit (EEIF) is set. The user may either enable this interrupt, or poll this bit. EEIF must be cleared by software.

# 7.5 Write Verify

Depending on the application, good programming practice may dictate that the value written to the memory should be verified against the original value. This should be used in applications where excessive writes can stress bits near the specification limit.

| MOVLW<br>MOVWF<br>MOVLW<br>MOVWF | DATA_EE_ADDRH<br>EEADRH<br>DATA_EE_ADDR<br>EEADR | ;<br>; Upper bits of Data Memory Address to read<br>;<br>; Lower bits of Data Memory Address to read |

|----------------------------------|--------------------------------------------------|------------------------------------------------------------------------------------------------------|

| BCF                              | EECON1, EEPGD                                    | ; Point to DATA memory                                                                               |

| BCF                              | EECON1, CFGS                                     | ; Access EEPROM                                                                                      |

| BSF                              | EECON1, RD                                       | ; EEPROM Read                                                                                        |

| MOVF                             | EEDATA, W                                        | ; W = EEDATA                                                                                         |

| EXAMPLE 7-2: DATA EEPRC | ROM | WRITE |

|-------------------------|-----|-------|

|-------------------------|-----|-------|

|          | MOVLW | DATA_EE_ADDRH | ;                                             |

|----------|-------|---------------|-----------------------------------------------|

|          | MOVWF | EEADRH        | ; Upper bits of Data Memory Address to write  |

|          | MOVLW | DATA_EE_ADDR  | ;                                             |

|          | MOVWF | EEADR         | ; Lower bits of Data Memory Address to write  |

|          | MOVLW | DATA_EE_DATA  | ;                                             |

|          | MOVWF | EEDATA        | ; Data Memory Value to write                  |

|          | BCF   | EECON1, EPGD  | ; Point to DATA memory                        |

|          | BCF   | EECON1, CFGS  | ; Access EEPROM                               |

|          | BSF   | EECON1, WREN  | ; Enable writes                               |

|          |       |               |                                               |

|          | BCF   | INTCON, GIE   | ; Disable Interrupts                          |

|          | MOVLW | 55h           | ;                                             |

| Required | MOVWF | EECON2        | ; Write 55h                                   |

| Sequence | MOVLW | 0AAh          | ;                                             |

|          | MOVWF | EECON2        | ; Write OAAh                                  |

|          | BSF   | EECON1, WR    | ; Set WR bit to begin write                   |

|          | BSF   | INTCON, GIE   | ; Enable Interrupts                           |

|          |       |               |                                               |

|          |       |               | ; User code execution                         |

|          | BCF   | EECON1, WREN  | ; Disable writes on write complete (EEIF set) |

|          |       |               |                                               |

| Name    | Bit 7     | Bit 6         | Bit 5    | Bit 4   | Bit 3  | Bit 2  | Bit 1  | Bit 0  | Reset<br>Values<br>on page |

|---------|-----------|---------------|----------|---------|--------|--------|--------|--------|----------------------------|

| PORTB   | RB7       | RB6           | RB5      | RB4     | RB3    | RB2    | RB1    | RB0    | 54                         |

| LATB    | LATB Data | Output Regis  | ter      |         |        |        |        |        | 54                         |

| TRISB   | PORTB Dat | a Direction R | legister |         |        |        |        |        | 54                         |

| INTCON  | GIE/GIEH  | PEIE/GIEL     | TMR0IE   | INT0IE  | RBIE   | TMR0IF | INT0IF | RBIF   | 51                         |

| INTCON2 | RBPU      | INTEDG0       | INTEDG1  | INTEDG2 | _      | TMR0IP | _      | RBIP   | 51                         |

| INTCON3 | INT2IP    | INT1IP        | _        | INT2IE  | INT1IE | _      | INT2IF | INT1IF | 51                         |

| ADCON1  | —         | —             | VCFG1    | VCFG0   | PCFG3  | PCFG2  | PCFG1  | PCFG0  | 52                         |

### TABLE 10-4: SUMMARY OF REGISTERS ASSOCIATED WITH PORTB

Legend: — = unimplemented, read as '0'. Shaded cells are not used by PORTB.

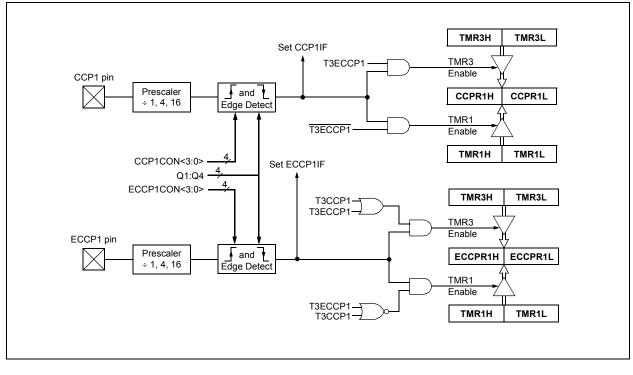

# 15.1 CCP1 Module Configuration

Each Capture/Compare/PWM module is associated with a control register (CCP1CON or ECCP1CON) and a data register (CCPR1 or ECCPR1). The data register, in turn, is comprised of two 8-bit registers: CCPR1L or ECCPR1L (low byte) and CCPR1H or ECCPR1H (high byte). All registers are both readable and writable.

#### 15.1.1 CCP1 MODULES AND TIMER RESOURCES

The CCP1 modules utilize Timers 1, 2 or 3, depending on the mode selected. Timer1 and Timer3 are available to modules in Capture or Compare modes, while Timer2 is available for modules in PWM mode.

# TABLE 15-1:CCP1 MODE – TIMER<br/>RESOURCE

| CCP1/ECCP1 Mode | Timer Resource   |

|-----------------|------------------|

| Capture         | Timer1 or Timer3 |

| Compare         | Timer1 or Timer3 |

| PWM             | Timer2           |

The assignment of a particular timer to a module is determined by the Timer to CCP1/ECCP1 enable bits in the T3CON register (Register 14-1). Both modules may be active at any given time and may share the same timer resource if they are configured to operate in the same mode (Capture/Compare or PWM) at the same time. The interactions between the two modules are summarized in Figure 15-1 and Figure 15-2.

| TABLE 15-2: INTERACTIONS BETWEEN CCP1 AND ECCP1 FOR TIMER RESOURCES |

|---------------------------------------------------------------------|

|---------------------------------------------------------------------|

| CCP1 Mode | ECCP1 Mode | Interaction                                                                                                                                                                                                                                                         |

|-----------|------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Capture   | Capture    | Each module can use TMR1 or TMR3 as the time base. Time base can be different for each CCP1.                                                                                                                                                                        |

| Capture   | Compare    | CCP1 can be configured for the Special Event Trigger to reset TMR1 or TMR3 (depending upon which time base is used). Automatic A/D conversions on trigger event can also be done. Operation of CCP1 could be affected if it is using the same timer as a time base. |

| Compare   | Capture    | CCP1 can be configured for the Special Event Trigger to reset TMR1 or TMR3 (depending upon which time base is used). Operation of CCP1 could be affected if it is using the same timer as a time base.                                                              |

| Compare   | Compare    | Either module can be configured for the Special Event Trigger to reset the time base.<br>Automatic A/D conversions on ECCP1 trigger event can be done. Conflicts may occur if<br>both modules are using the same time base.                                         |

| Capture   | PWM*       | None                                                                                                                                                                                                                                                                |

| Compare   | PWM*       | None                                                                                                                                                                                                                                                                |

| PWM*      | Capture    | None                                                                                                                                                                                                                                                                |

| PWM*      | Compare    | None                                                                                                                                                                                                                                                                |

| PWM*      | PWM        | Both PWMs will have the same frequency and update rate (TMR2 interrupt).                                                                                                                                                                                            |

\* Includes standard and Enhanced PWM operation.

# FIGURE 15-1: CAPTURE MODE OPERATION BLOCK DIAGRAM

The CCPR1H register and a 2-bit internal latch are used to double-buffer the PWM duty cycle. This double-buffering is essential for glitchless PWM operation.

When the CCPR1H and 2-bit latch match TMR2, concatenated with an internal 2-bit Q clock or 2 bits of the TMR2 prescaler, the CCP1 pin is cleared.

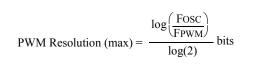

The maximum PWM resolution (bits) for a given PWM frequency is given by the equation.

# **EQUATION 15-3:**

Note: If the PWM duty cycle value is longer than the PWM period, the CCP1 pin will not be cleared.

# TABLE 15-4: EXAMPLE PWM FREQUENCIES AND RESOLUTIONS AT 40 MHz

| PWM Frequency              | 2.44 kHz | 9.77 kHz | 39.06 kHz | 156.25 kHz | 312.50 kHz | 416.67 kHz |

|----------------------------|----------|----------|-----------|------------|------------|------------|

| Timer Prescaler (1, 4, 16) | 16       | 4        | 1         | 1          | 1          | 1          |

| PR2 Value                  | FFh      | FFh      | FFh       | 3Fh        | 1Fh        | 17h        |

| Maximum Resolution (bits)  | 14       | 12       | 10        | 8          | 7          | 6.58       |

#### 15.4.3 PWM AUTO-SHUTDOWN (ECCP1 ONLY)

The PWM auto-shutdown features of the Enhanced CCP1 module are available to ECCP1 in PIC18F4682/ 4685 (40/44-pin) devices. The operation of this feature is discussed in detail in **Section 16.4.7 "Enhanced PWM Auto-Shutdown"**.

Auto-shutdown features are not available for CCP1.

# 15.4.4 SETUP FOR PWM OPERATION

The following steps should be taken when configuring the CCP1 module for PWM operation:

- 1. Set the PWM period by writing to the PR2 register.

- 2. Set the PWM duty cycle by writing to the CCPR1L register and CCP1CON<5:4> bits.

- 3. Make the CCP1 pin an output by clearing the appropriate TRIS bit.

- 4. Set the TMR2 prescale value, then enable Timer2 by writing to T2CON.

- 5. Configure the CCP1 module for PWM operation.

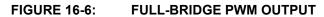

## 16.4.5 FULL-BRIDGE MODE

In Full-Bridge Output mode, four pins are used as outputs; however, only two outputs are active at a time. In the Forward mode, pin P1A is continuously active and pin P1D is modulated. In the Reverse mode, pin P1C is continuously active and pin P1B is modulated. These are illustrated in Figure 16-6. P1A, P1B, P1C and P1D outputs are multiplexed with the PORTD<4>, PORTD<5>, PORTD<6> and PORTD<7> data latches. The TRISD<4>, TRISD<5>, TRISD<6> and TRISD<7> bits must be cleared to make the P1A, P1B, P1C and P1D pins outputs.

## 16.4.9 SETUP FOR PWM OPERATION

The following steps should be taken when configuring the ECCP1 module for PWM operation:

- 1. Configure the PWM pins, P1A and P1B (and P1C and P1D, if used), as inputs by setting the corresponding TRIS bits.

- 2. Set the PWM period by loading the PR2 register.

- Configure the ECCP1 module for the desired PWM mode and configuration by loading the ECCP1CON register with the appropriate values:

- Select one of the available output configurations and direction with the EPWM1M1:EPWM1M0 bits.

- Select the polarities of the PWM output signals with the ECCP1M3:ECCP1M0 bits.

- 4. Set the PWM duty cycle by loading the ECCPR1L register and ECCP1CON<5:4> bits.

- 5. For Half-Bridge Output mode, set the deadband delay by loading ECCP1DEL<6:0> with the appropriate value.

- 6. If auto-shutdown operation is required, load the ECCP1AS register:

- Select the auto-shutdown sources using the ECCPAS2:ECCPAS0 bits.

- Select the shutdown states of the PWM output pins using PSSAC1:PSSAC0 and PSSBD1:PSSBD0 bits.

- Set the ECCPASE bit (ECCP1AS<7>).

- Configure the comparators using the CMCON register.

- Configure the comparator inputs as analog inputs.

- 7. If auto-restart operation is required, set the PRSEN bit (ECCP1DEL<7>).

- 8. Configure and start TMR2:

- Clear the TMR2 interrupt flag bit by clearing the TMR2IF bit (PIR1<1>).

- Set the TMR2 prescale value by loading the T2CKPS bits (T2CON<1:0>).

- Enable Timer2 by setting the TMR2ON bit (T2CON<2>).

- 9. Enable PWM outputs after a new PWM cycle has started:

- Wait until TMRx overflows (TMRxIF bit is set).

- Enable the ECCP1/P1A, P1B, P1C and/or P1D pin outputs by clearing the respective TRIS bits.

- Clear the ECCPASE bit (ECCP1AS<7>).

### 16.4.10 EFFECTS OF A RESET

Both Power-on Reset and subsequent Resets will force all ports to Input mode and the ECCP1 registers to their Reset states.

This forces the Enhanced CCP1 module to reset to a state compatible with the standard CCP1 module.

# 17.3.3 ENABLING SPI I/O

To enable the serial port, MSSP Enable bit, SSPEN (SSPCON1<5>), must be set. To reset or reconfigure SPI mode, clear the SSPEN bit, reinitialize the SSPCON registers and then set the SSPEN bit. This configures the SDI, SDO, SCK and SS pins as serial port pins. For the pins to behave as the serial port function, some must have their data direction bits (in the TRIS register) appropriately programmed as follows:

- · SDI is automatically controlled by the SPI module

- SDO must have TRISC<5> bit cleared

- SCK (Master mode) must have TRISC<3> bit cleared

- SCK (Slave mode) must have TRISC<3> bit set

- SS must have TRISF<7> bit set

Any serial port function that is not desired may be overridden by programming the corresponding data direction (TRIS) register to the opposite value.

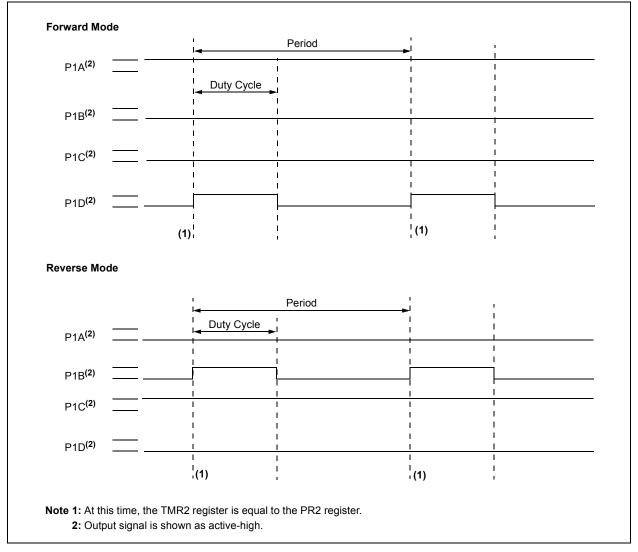

# 17.3.4 TYPICAL CONNECTION

Figure 17-2 shows a typical connection between two microcontrollers. The master controller (Processor 1) initiates the data transfer by sending the SCK signal. Data is shifted out of both shift registers on their programmed clock edge and latched on the opposite edge of the clock. Both processors should be programmed to the same Clock Polarity (CKP), then both controllers would send and receive data at the same time. Whether the data is meaningful (or dummy data) depends on the application software. This leads to three scenarios for data transmission:

- · Master sends data Slave sends dummy data

- · Master sends data Slave sends data

- · Master sends dummy data Slave sends data

#### FIGURE 17-2: SPI MASTER/SLAVE CONNECTION

# EXAMPLE 23-2: WIN AND ICODE BITS USAGE IN INTERRUPT SERVICE ROUTINE TO ACCESS TX/RX BUFFERS (CONTINUED)

| ErrorInter | rrupt                      |                                        |

|------------|----------------------------|----------------------------------------|

| BCF        | PIR3, ERRIF                | ; Clear the interrupt flag             |

|            |                            | ; Handle error.                        |

| RETFIE     | 2                          |                                        |

| TXB2Intern | rupt                       |                                        |

| BCF        | PIR3, TXB2IF               | ; Clear the interrupt flag             |

| GOTO       | AccessBuffer               |                                        |

| TXBlIntern | rupt                       |                                        |

| BCF        | PIR3, TXB1IF               | ; Clear the interrupt flag             |

| GOTO       | AccessBuffer               |                                        |

| TXB0Interr | rupt                       |                                        |

| BCF        | PIR3, TXB0IF               | ; Clear the interrupt flag             |

| GOTO       | AccessBuffer               |                                        |

| RXBlInterr | rupt                       |                                        |

| BCF        | PIR3, RXB1IF               | ; Clear the interrupt flag             |

| GOTO       | Accessbuffer               |                                        |

| RXBOIntern | rupt                       |                                        |

| BCF        | PIR3, RXB0IF               | ; Clear the interrupt flag             |

| GOTO       | AccessBuffer               |                                        |

| AccessBuff | fer                        | ; This is either TX or RX interrupt    |

| ; Copy     | CANSTAT.ICODE bits to CA   | ANCON.WIN bits                         |

| MOVF       | TempCANCON, W              | ; Clear CANCON.WIN bits before copying |

|            |                            | ; new ones.                            |

| ANDLW      | B'11110001'                | ; Use previously saved CANCON value to |

|            |                            | ; make sure same value.                |

| MOVWF      | TempCANCON                 | ; Copy masked value back to TempCANCON |

| MOVF       | TempCANSTAT, W             | ; Retrieve ICODE bits                  |

| ANDLW      | B'00001110'                | ; Use previously saved CANSTAT value   |

|            |                            | ; to make sure same value.             |

| IORWF      | TempCANCON                 | ; Copy ICODE bits to WIN bits.         |

| MOVFF      | TempCANCON, CANCON         | ; Copy the result to actual CANCON     |

| ; Acce     | ess current buffer         |                                        |

| ; User     | code                       |                                        |

| ; Rest     | ore CANCON.WIN bits        |                                        |

| MOVF       | CANCON, W                  | ; Preserve current non WIN bits        |

| ANDLW      | B'11110001'                |                                        |

| IORWF      | TempCANCON                 | ; Restore original WIN bits            |

| ; Do n     | not need to restore CANSTA | AT - it is read-only register.         |

| ; Retu     | arn from interrupt or chec | k for another module interrupt source  |

|            |                            |                                        |

| Made 0    | R/C-0                                                                                                | R/C-0                               | R-0             | R-0        | R-0            | R-0            | R-0            | R-0   |  |  |  |

|-----------|------------------------------------------------------------------------------------------------------|-------------------------------------|-----------------|------------|----------------|----------------|----------------|-------|--|--|--|

| Mode 0    | RXB00VFL                                                                                             | RXB10VFL                            | TXBO            | TXBP       | RXBP           | TXWARN         | RXWARN         | EWARN |  |  |  |

|           |                                                                                                      |                                     |                 |            |                |                |                |       |  |  |  |

| Mode 1    | R/C-0                                                                                                | R/C-0                               | R-0             | R-0        | R-0            | R-0            | R-0            | R-0   |  |  |  |

|           | —                                                                                                    | RXBnOVFL                            | TXB0            | TXBP       | RXBP           | TXWARN         | RXWARN         | EWARN |  |  |  |

|           | R/C-0                                                                                                | R/C-0                               | R-0             | R-0        | R-0            | R-0            | R-0            | R-0   |  |  |  |

| Mode 2    | FIFOEMPTY                                                                                            | RXBnOVFL                            | TXBO            | TXBP       | RXBP           | TXWARN         | RXWARN         | EWARN |  |  |  |

|           | bit 7                                                                                                |                                     |                 | ÷          |                |                |                | bit   |  |  |  |

| Legend:   |                                                                                                      |                                     |                 |            |                |                |                |       |  |  |  |

| R = Read  | able bit                                                                                             |                                     | C = Clearab     | le bit     | U = Unimpl     | emented bit, I | read as '0'    |       |  |  |  |

| -n = Valu | e at POR                                                                                             |                                     | '1' = Bit is se | et         | '0' = Bit is c | leared         | x = Bit is unk | nown  |  |  |  |

|           |                                                                                                      |                                     |                 |            |                |                |                |       |  |  |  |

| bit 7     | Mode 0:<br>RXB0OVFL:                                                                                 | Receive Buffe                       | r 0 Overflow    | bit        |                |                |                |       |  |  |  |

|           |                                                                                                      | Buffer 0 overflo                    |                 |            |                |                |                |       |  |  |  |

|           |                                                                                                      | Buffer 0 has no                     | ot overflowed   | 1          |                |                |                |       |  |  |  |

|           | Mode 1:<br>Unimplement                                                                               | nted: Read as                       | ' <b>∩'</b>     |            |                |                |                |       |  |  |  |

|           | Unimplemented: Read as '0'<br>Mode 2:                                                                |                                     |                 |            |                |                |                |       |  |  |  |

|           | FIFOEMPTY: FIFO Not Empty bit                                                                        |                                     |                 |            |                |                |                |       |  |  |  |

|           |                                                                                                      | FIFO is not em<br>FIFO is empty     | ipty            |            |                |                |                |       |  |  |  |

| bit 6     | Mode 0:<br>RXB10VFL: Receive Buffer 1 Overflow bit                                                   |                                     |                 |            |                |                |                |       |  |  |  |

|           | <ul> <li>1 = Receive Buffer 1 overflowed</li> <li>0 = Receive Buffer 1 has not overflowed</li> </ul> |                                     |                 |            |                |                |                |       |  |  |  |

|           | Mode 1, 2:<br><b>BXPROVEL</b> : Ressive Buffer & Overflow bit                                        |                                     |                 |            |                |                |                |       |  |  |  |

|           | <b>RXBnOVFL:</b> Receive Buffer n Overflow bit<br>1 = Receive Buffer n has overflowed                |                                     |                 |            |                |                |                |       |  |  |  |

|           | 0 = Receive Buffer n has overflowed                                                                  |                                     |                 |            |                |                |                |       |  |  |  |

| bit 5     | TXBO: Transmitter Bus-Off bit                                                                        |                                     |                 |            |                |                |                |       |  |  |  |

|           |                                                                                                      | error counter a                     |                 |            |                |                |                |       |  |  |  |

| bit 4     | TXBP: Transmitter Bus Passive bit                                                                    |                                     |                 |            |                |                |                |       |  |  |  |

|           |                                                                                                      | error counter a                     |                 |            |                |                |                |       |  |  |  |

| bit 3     | <b>RXBP:</b> Receiver Bus Passive bit                                                                |                                     |                 |            |                |                |                |       |  |  |  |

|           |                                                                                                      | error counter ><br>error counter ≤  |                 |            |                |                |                |       |  |  |  |

| bit 2     | TXWARN: Tr                                                                                           | ransmitter War                      | ning bit        |            |                |                |                |       |  |  |  |

|           |                                                                                                      | error counter a                     |                 |            |                |                |                |       |  |  |  |

| bit 1     | RXWARN: R                                                                                            | eceiver Warnin                      | ng bit          |            |                |                |                |       |  |  |  |

|           |                                                                                                      | eceive error cou<br>error counter ≤ |                 |            |                |                |                |       |  |  |  |

| bit 0     |                                                                                                      | or Warning bit<br>lag of the RXW    | /ARN and T>     | WARN bits. |                |                |                |       |  |  |  |

|           | 1 = The RXV                                                                                          | VARN or the T                       | XWARN bits      | are set    |                |                |                |       |  |  |  |

# REGISTER 23-4: COMSTAT: COMMUNICATION STATUS REGISTER

# REGISTER 24-9: CONFIG6H: CONFIGURATION REGISTER 6 HIGH (BYTE ADDRESS 30000Bh)

|                  |                                                                                     |                                                                                                       |                                                                          |                         | -                |            |       |

|------------------|-------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------|-------------------------|------------------|------------|-------|

| R/C-1            | R/C-1                                                                               | R-1                                                                                                   | U-0                                                                      | U-0                     | U-0              | U-0        | U-0   |

| WRTD             | WRTB                                                                                | WRTC <sup>(1)</sup>                                                                                   | —                                                                        | —                       |                  |            | —     |

| bit 7            | •                                                                                   |                                                                                                       |                                                                          |                         |                  |            | bit 0 |

|                  |                                                                                     |                                                                                                       |                                                                          |                         |                  |            |       |

| Legend:          |                                                                                     |                                                                                                       |                                                                          |                         |                  |            |       |

| R = Readable     | bit                                                                                 | C = Clearable                                                                                         | bit                                                                      | U = Unimpler            | mented bit, read | as '0'     |       |

| -n = Value whe   | en device is unp                                                                    | programmed                                                                                            |                                                                          | u = Unchang             | ed from progran  | nmed state |       |

| bit 7<br>bit 6   | 1 = Data EEP<br>0 = Data EEP<br><b>WRTB:</b> Boot<br>1 = Boot Bloc<br>0 = Boot Bloc | EEPROM Write<br>PROM not write<br>PROM write-pro<br>Block Write Pro<br>k (000000-000<br>k (000000-000 | -protected<br>tected<br>btection bit<br>7FFh) not writ<br>7FFh) write-pi | e-protected<br>rotected |                  |            |       |

| bit 5<br>bit 4-0 | 1 = Configura<br>0 = Configura                                                      | guration Regist<br>tion registers (<br>tion registers (                                               | 300000-3000F<br>300000-3000F                                             | Fh) not write-          |                  |            |       |

| DIL 4-0          | ommplemen                                                                           | ted: Read as '                                                                                        | J                                                                        |                         |                  |            |       |

|                  |                                                                                     |                                                                                                       |                                                                          |                         |                  |            |       |

**Note 1:** This bit is read-only in normal execution mode; it can be written only in Program mode.

| GOTO     | )               | Uncondit                                              | ional Bra                | anch               |                                    | INCF                      | Incremen                                           | t f                                                                        |                              |

|----------|-----------------|-------------------------------------------------------|--------------------------|--------------------|------------------------------------|---------------------------|----------------------------------------------------|----------------------------------------------------------------------------|------------------------------|

| Syntax:  |                 | GOTO k                                                |                          |                    |                                    | Syntax:                   | INCF f{,c                                          | d {,a}}                                                                    |                              |

| Operan   | nds:            | $0 \le k \le 104$                                     | 8575                     |                    |                                    | Operands:                 | $0 \leq f \leq 255$                                |                                                                            |                              |

| Operati  | ion:            | $k \rightarrow PC<20$                                 | ):1>                     |                    |                                    |                           | d ∈ [0,1]<br>a ∈ [0,1]                             |                                                                            |                              |

| Status / | Affected:       | None                                                  |                          |                    |                                    | Operation:                | $a \in [0, 1]$<br>(f) + 1 $\rightarrow$ definition | aet                                                                        |                              |

| Encodir  | ng:             |                                                       |                          |                    |                                    | Status Affected:          | $(1) + 1 \rightarrow 0$<br>C, DC, N,               |                                                                            |                              |

| 1st wor  | rd (k<7:0>)     | 1110                                                  |                          | k <sub>7</sub> kkk | kkkk <sub>0</sub>                  |                           |                                                    | -                                                                          |                              |

| 2nd wo   | ord(k<19:8>)    | 1111                                                  | k <sub>19</sub> kkk      | kkkk               | kkkk <sub>8</sub>                  | Encoding:<br>Description: | 0010                                               | 10da ff                                                                    | ff ff:                       |